# E·XFL

#### Intel - 5AGXMB3G6F40C6N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 17110                                                      |

| Number of Logic Elements/Cells | 362000                                                     |

| Total RAM Bits                 | 19822592                                                   |

| Number of I/O                  | 704                                                        |

| Number of Gates                |                                                            |

| Voltage - Supply               | 1.07V ~ 1.13V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1517-BBGA                                                  |

| Supplier Device Package        | 1517-FBGA (40x40)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agxmb3g6f40c6n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

AV-51002 2017.02.10

1-5

| Symbol                            | Description                                 | Condition          | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------|--------------------|------------------------|---------|------------------------|------|

| V                                 | V Core voltage power supply                 |                    | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CC</sub>                   | Core voltage power supply                   | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

| V                                 | Periphery circuitry, PCIe hard IP block,    | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| V <sub>CCP</sub>                  | and transceiver PCS power supply            | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

|                                   | V. Conformation aire according to           | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V                                 |                                             | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

| V <sub>CCPGM</sub>                | Configuration pins power supply             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

|                                   |                                             | 1.8 V              | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply                            | —                  | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(2)</sup> | Battery back-up power supply                | _                  | 1.2                    | _       | 3.0                    | V    |

|                                   | (For design security volatile key register) |                    |                        |         |                        |      |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V <sub>CCPD</sub> <sup>(3)</sup>  | I/O pre-driver power supply                 | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

|                                   |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

(2) If you do not use the design security feature in Arria V devices, connect V<sub>CCBAT</sub> to a 1.5-V, 2.5-V, or 3.0-V power supply. Arria V power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

<sup>&</sup>lt;sup>(3)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.  $V_{CCPD}$  must be 3.3 V when  $V_{CCIO}$  is 3.3 V.

#### **Transceiver Power Supply Operating Conditions**

| Table 1-4: Transceiver Power Supply Operating Conditions for Arria V Device | es |

|-----------------------------------------------------------------------------|----|

|-----------------------------------------------------------------------------|----|

| Symbol                | Description                                           | Minimum <sup>(5)</sup> | Typical                 | Maximum <sup>(5)</sup> | Unit |  |

|-----------------------|-------------------------------------------------------|------------------------|-------------------------|------------------------|------|--|

| V <sub>CCA_GXBL</sub> | Transceiver high voltage power (left side)            | 2.375                  | 2.500                   | 2.625                  | V    |  |

| V <sub>CCA_GXBR</sub> | Transceiver high voltage power (right side)           | 2.373                  | 2.300                   | 2.025                  | v    |  |

| V <sub>CCR_GXBL</sub> | GX and SX speed grades—receiver power (left side)     | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |  |

| V <sub>CCR_GXBR</sub> | GX and SX speed grades—receiver power (right side)    | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |  |

| V <sub>CCR_GXBL</sub> | GT and ST speed grades—receiver power (left side)     | 1.17                   | 1.20                    | 1.23                   | V    |  |

| V <sub>CCR_GXBR</sub> | GT and ST speed grades—receiver power (right side)    | 1.17                   | 1.20                    | 1.23                   | v    |  |

| V <sub>CCT_GXBL</sub> | GX and SX speed grades—transmitter power (left side)  | 1.08/1.12              | 1.1/1.15 <sup>(6)</sup> | 1.14/1.18              | V    |  |

| V <sub>CCT_GXBR</sub> | GX and SX speed grades—transmitter power (right side) | 1.00/1.12              | 1.1/1.13                | 1.14/1.10              | v    |  |

| V <sub>CCT_GXBL</sub> | GT and ST speed grades—transmitter power (left side)  | 1.17                   | 1.20                    | 1.23                   | V    |  |

| V <sub>CCT_GXBR</sub> | GT and ST speed grades—transmitter power (right side) | 1.17                   | 1.20                    | 1.23                   | V    |  |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power (left side)           | 1.425                  | 1.500                   | 1.575                  | V    |  |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power (right side)          | 1.423                  | 1.300                   | 1.373                  | v    |  |

<sup>(5)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(6)</sup> For data rate <=3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to either 1.1-V or 1.15-V power supply. For data rate >3.2 Gbps, connect V<sub>CCR\_GXBL/R</sub>, V<sub>CCT\_GXBL/R</sub>, or V<sub>CCL\_GXBL/R</sub> to a 1.15-V power supply. For details, refer to the Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines.

| Symbol | Description                         | Condition | Minimum <sup>(7)</sup> | Typical | Maximum <sup>(7)</sup> | Unit |

|--------|-------------------------------------|-----------|------------------------|---------|------------------------|------|

|        | HPS<br>auxiliary<br>power<br>supply | _         | 2.375                  | 2.5     | 2.625                  | V    |

#### **Related Information**

**Recommended Operating Conditions** on page 1-4 Provides the steady-state voltage values for the FPGA portion of the device.

#### DC Characteristics

#### Supply Current and Power Consumption

Altera offers two ways to estimate power for your design-the Excel-based Early Power Estimator (EPE) and the Quartus® Prime PowerPlay Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Quartus Prime PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-androute. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide Provides more information about power estimation tools.

- PowerPlay Power Analysis chapter, Quartus Prime Handbook Provides more information about power estimation tools.

**Altera Corporation**

<sup>&</sup>lt;sup>(7)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

|                        |                   |           | V <sub>CCIO</sub> (V) |     |       |       |      |      |     |     |     |     |     |     |      |

|------------------------|-------------------|-----------|-----------------------|-----|-------|-------|------|------|-----|-----|-----|-----|-----|-----|------|

| Parameter              | Symbol            | Condition | 1                     | .2  | 1     | .5    | 1.   | .8   | 2   | .5  | 3   | .0  | 3.  | .3  | Unit |

|                        |                   |           | Min                   | Max | Min   | Max   | Min  | Max  | Min | Max | Min | Max | Min | Max |      |

| Bus-hold<br>trip point | V <sub>TRIP</sub> | _         | 0.3                   | 0.9 | 0.375 | 1.125 | 0.68 | 1.07 | 0.7 | 1.7 | 0.8 | 2   | 0.8 | 2   | V    |

#### **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

#### Table 1-8: OCT Calibration Accuracy Specifications for Arria V Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                                                                      | Description                                                                                                                                  | Condition (V)                               | Ca         | alibration Accura | су         | Unit |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------------|------------|------|

| Symbol                                                                                      | Description                                                                                                                                  |                                             | –I3, –C4   | –I5, –C5          | -C6        | Ont  |

| 25-Ω R <sub>S</sub>                                                                         | Internal series termination with calibration (25- $\Omega$ setting)                                                                          | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>S</sub>                                                                         | Internal series termination with calibration (50- $\Omega$ setting)                                                                          | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ $R_S$                                                         | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                         | V <sub>CCIO</sub> = 1.5, 1.35, 1.25,<br>1.2 | ±15        | ±15               | ±15        | %    |

| 48- $\Omega$ , 60- $\Omega$ , and 80-<br>$\Omega$ R <sub>S</sub>                            | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ setting)                                        | $V_{CCIO} = 1.2$                            | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                         | Internal parallel termination with calibration ( $50-\Omega$ setting)                                                                        | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2      | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ ,60- $\Omega$ , and 120- $\Omega$ R <sub>T</sub> | Internal parallel termination<br>with calibration (20- $\Omega$ , 30- $\Omega$ ,<br>40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25         | -10 to +40 | -10 to +40        | -10 to +40 | %    |

# Typical TX V<sub>OD</sub> Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

| Table 1-32: Typical TX Vor | Setting for Arria V Transceive | r Channels with termination of 100 $\Omega$ |

|----------------------------|--------------------------------|---------------------------------------------|

|                            |                                |                                             |

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8(59)                                   | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| -) <b>F</b>                                          | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

| 1-44 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                           | Parameter                                                           | Condition      | Min | Тур | Max                 | Unit |

|----------------------------------|---------------------------------------------------------------------|----------------|-----|-----|---------------------|------|

|                                  |                                                                     | -3 speed grade | 5   | _   | 800 <sup>(61)</sup> | MHz  |

| f <sub>IN</sub>                  | Input clock frequency                                               | -4 speed grade | 5   | _   | 800 <sup>(61)</sup> | MHz  |

| IIN                              | input clock frequency                                               | -5 speed grade | 5   | _   | 750 <sup>(61)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade | 5   | _   | 625 <sup>(61)</sup> | MHz  |

| f <sub>INPFD</sub>               | Integer input clock frequency to the phase frequency detector (PFD) |                | 5   | _   | 325                 | MHz  |

| f <sub>FINPFD</sub>              | Fractional input clock frequency to the PFD                         | _              | 50  | _   | 160                 | MHz  |

|                                  |                                                                     | -3 speed grade | 600 | _   | 1600                | MHz  |

| f <sub>VCO</sub> <sup>(62)</sup> | PLL voltage-controlled oscillator                                   | -4 speed grade | 600 | _   | 1600                | MHz  |

| IVCO                             | (VCO) operating range                                               | -5 speed grade | 600 | _   | 1600                | MHz  |

|                                  |                                                                     | -6 speed grade | 600 | _   | 1300                | MHz  |

| t <sub>EINDUTY</sub>             | Input clock or external feedback clock input duty cycle             | _              | 40  | _   | 60                  | %    |

|                                  |                                                                     | -3 speed grade | _   | _   | 500 <sup>(63)</sup> | MHz  |

| f                                | Output frequency for internal global or                             | -4 speed grade | _   | _   | 500 <sup>(63)</sup> | MHz  |

| f <sub>OUT</sub>                 | regional clock                                                      | -5 speed grade | _   | -   | 500 <sup>(63)</sup> | MHz  |

|                                  |                                                                     | -6 speed grade | _   | _   | 400 <sup>(63)</sup> | MHz  |

<sup>&</sup>lt;sup>(61)</sup> This specification is limited in the Quartus Prime software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>&</sup>lt;sup>(62)</sup> The VCO frequency reported by the Quartus Prime software takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

<sup>&</sup>lt;sup>(63)</sup> This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

| Symbol                                                                                                           | Condition                                                                                    |     | -I3, -C4 |      | –I5, –C5 |     |      | -C6 |     |      | Unit |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|----------|------|----------|-----|------|-----|-----|------|------|

| Symbol                                                                                                           | Condition                                                                                    | Min | Тур      | Max  | Min      | Тур | Мах  | Min | Тур | Max  | Unit |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with Three                                      | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps                                        | _   | -        | 260  |          | _   | 300  | _   | _   | 350  | ps   |

| External Output Resistor<br>Network                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                                                     | —   | _        | 0.16 |          | _   | 0.18 | _   |     | 0.21 | UI   |

| t <sub>x Jitter</sub> -Emulated<br>Differential I/O<br>Standards with One<br>External Output<br>Resistor Network | _                                                                                            |     |          | 0.15 |          |     | 0.15 |     |     | 0.15 | UI   |

| t <sub>DUTY</sub>                                                                                                | TX output clock duty<br>cycle for both True<br>and Emulated<br>Differential I/O<br>Standards | 45  | 50       | 55   | 45       | 50  | 55   | 45  | 50  | 55   | %    |

|                                                                                                                  | True Differential I/O<br>Standards <sup>(82)</sup>                                           | _   | _        | 160  |          |     | 180  | _   |     | 200  | ps   |

| t <sub>RISE</sub> and t <sub>FALL</sub>                                                                          | Emulated Differential<br>I/O Standards with<br>Three External Output<br>Resistor Network     | _   |          | 250  |          |     | 250  |     |     | 300  | ps   |

|                                                                                                                  | Emulated Differential<br>I/O Standards with<br>One External Output<br>Resistor Network       |     |          | 500  |          | _   | 500  |     |     | 500  | ps   |

$<sup>^{(82)}\,</sup>$  This applies to default pre-emphasis and  $V_{OD}$  settings only.

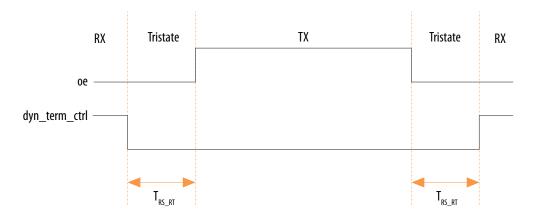

#### Figure 1-7: Timing Diagram for oe and dyn\_term\_ctrl Signals

# **Duty Cycle Distortion (DCD) Specifications**

#### Table 1-47: Worst-Case DCD on Arria V I/O Pins

The output DCD cycle only applies to the I/O buffer. It does not cover the system DCD.

| Symbol            | –I3, | -C4 | -C5, -I5 -C6 |     | Unit |     |     |

|-------------------|------|-----|--------------|-----|------|-----|-----|

| Symbol            | Min  | Мах | Min          | Мах | Min  | Мах | Ont |

| Output Duty Cycle | 45   | 55  | 45           | 55  | 45   | 55  | %   |

# **HPS Specifications**

This section provides HPS specifications and timing for Arria V devices.

For HPS reset, the minimum reset pulse widths for the HPS cold and warm reset signals (HPS\_nRST and HPS\_nPOR) are six clock cycles of HPS\_CLK1.

#### 1-62 SPI Timing Characteristics

| Symbol                 | Description                                       | Min | Мах | Unit |

|------------------------|---------------------------------------------------|-----|-----|------|

| T <sub>h</sub>         | SPI MISO hold time                                | 1   | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45  | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8   |     | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1  | 1   | ns   |

**Altera Corporation**

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(86)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx\_sample\_delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

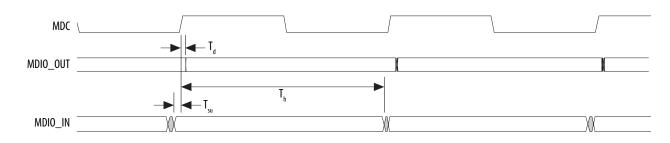

# Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

# Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standard Mode |      | Fast Mode |     | Unit |  |

|-----------------------|---------------------------------------------------|---------------|------|-----------|-----|------|--|

| Symbol                |                                                   | Min           | Max  | Min       | Max | Onit |  |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10            | —    | 2.5       | _   | μs   |  |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7           | —    | 0.6       |     | μs   |  |

| T <sub>clklow</sub>   | SCL low time                                      | 4             | _    | 1.3       |     | μs   |  |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25          | —    | 0.1       | —   | μs   |  |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0             | 3.45 | 0         | 0.9 | μs   |  |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —             | 0.2  | _         | 0.2 | μs   |  |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7           | _    | 0.6       | _   | μs   |  |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4             | —    | 0.6       | _   | μs   |  |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4             | —    | 0.6       | —   | μs   |  |

| 1-88 Glossary       |                                  |             | AV-5100<br>2017.02.1 |

|---------------------|----------------------------------|-------------|----------------------|

| Symbol              | Parameter                        | Typical     | Unit                 |

| D <sub>OUTBUF</sub> | Rising and/or falling edge delay | 0 (default) | ps                   |

|                     |                                  | 50          | ps                   |

|                     |                                  | 100         | ps                   |

|                     |                                  | 150         | ps                   |

# Glossary

# Table 1-78: Glossary

| Term                       | Definition                                                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Differential I/O standards | Receiver Input Waveforms                                                                                                    |

|                            | Single-Ended Waveform $V_{ID}$ Positive Channel (p) = $V_{IH}$ $V_{CM}$ Negative Channel (n) = $V_{IL}$ Ground       Ground |

|                            | Differential Waveform<br>$V_{ID}$<br>$V_{ID}$<br>$V_{ID}$<br>$v_{ID}$                                                       |

| Term                       | Definition                                                                                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>FALL</sub>          | Signal high-to-low transition time (80–20%)                                                                                                                           |

| t <sub>INCCJ</sub>         | Cycle-to-cycle jitter tolerance on the PLL clock input                                                                                                                |

| t <sub>OUTPJ_IO</sub>      | Period jitter on the GPIO driven by a PLL                                                                                                                             |

| t <sub>OUTPJ_DC</sub>      | Period jitter on the dedicated clock output driven by a PLL                                                                                                           |

| t <sub>RISE</sub>          | Signal low-to-high transition time (20–80%)                                                                                                                           |

| Timing Unit Interval (TUI) | The timing budget allowed for skew, propagation delays, and the data sampling window. (TUI = $1/$ (Receiver Input Clock Frequency Multiplication Factor) = $t_C/w$ )  |

| V <sub>CM(DC)</sub>        | DC common mode input voltage.                                                                                                                                         |

| V <sub>ICM</sub>           | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                 |

| V <sub>ID</sub>            | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.          |

| V <sub>DIF(AC)</sub>       | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                           |

| V <sub>DIF(DC)</sub>       | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                          |

| V <sub>IH</sub>            | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                 |

| V <sub>IH(AC)</sub>        | High-level AC input voltage                                                                                                                                           |

| V <sub>IH(DC)</sub>        | High-level DC input voltage                                                                                                                                           |

| V <sub>IL</sub>            | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                   |

| V <sub>IL(AC)</sub>        | Low-level AC input voltage                                                                                                                                            |

| V <sub>IL(DC)</sub>        | Low-level DC input voltage                                                                                                                                            |

| V <sub>OCM</sub>           | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                             |

| V <sub>OD</sub>            | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission line at the transmitter. |

| V <sub>SWING</sub>         | Differential input voltage                                                                                                                                            |

| V <sub>X</sub>             | Input differential cross point voltage                                                                                                                                |

Arria V GX, GT, SX, and ST Device Datasheet

Altera Corporation

| Symbol            | Description                    | Condition    | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-------------------|--------------------------------|--------------|--------------------------|---------|--------------------------|------|

| VI                | DC input voltage               |              | -0.5                     | _       | 3.6                      | V    |

| V <sub>O</sub>    | Output voltage                 |              | 0                        | _       | V <sub>CCIO</sub>        | V    |

| TI                | Operating in ation temperature | Commercial   | 0                        |         | 85                       | °C   |

| ıj                | Operating junction temperature | Industrial   | -40                      | _       | 100                      | °C   |

| +                 | Power supply ramp time         | Standard POR | 200 µs                   | _       | 100 ms                   | _    |

| t <sub>RAMP</sub> |                                | Fast POR     | 200 µs                   | _       | 4 ms                     | —    |

#### **Recommended Transceiver Power Supply Operating Conditions**

#### Table 2-6: Recommended Transceiver Power Supply Operating Conditions for Arria V GZ Devices

| Symbol                                                        | Description                                       | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |

|---------------------------------------------------------------|---------------------------------------------------|--------------------------|---------|--------------------------|------|

| V <sub>CCA_GXBL</sub>                                         | Transseiver shannel DLL nevver supply (left side) | 2.85                     | 3.0     | 3.15                     | V    |

| (119), (120) Transceiver channel PLL power supply (left side) | 2.375                                             | 2.5                      | 2.625   | v                        |      |

| V <sub>CCA</sub> _                                            | Transceiver channel PLL power supply (right side) | 2.85                     | 3.0     | 3.15                     | V    |

| V <sub>CCA</sub><br>GXBR <sup>(119)</sup> , <sup>(120)</sup>  |                                                   | 2.375                    | 2.5     | 2.625                    |      |

| V <sub>CCHIP_L</sub>                                          | Transceiver hard IP power supply (left side)      | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_L</sub>                                         | Transceiver PCS power supply (left side)          | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCHSSI_R</sub>                                         | Transceiver PCS power supply (right side)         | 0.82                     | 0.85    | 0.88                     | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(120)</sup> When using ATX PLLs, the supply must be 3.0 V.

<sup>(119)</sup> This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

#### **Transceiver Power Supply Requirements**

#### Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB <sup>(122)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                                   |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul>                                                                       |                                        |          |          |      |

| If ANY of the following conditions are true <sup>(123)</sup> :                                                                            | 1.0                                    | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                                        |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                                   | 2.5      |          |      |

| <ul> <li>ATX PLL is not used.</li> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                          |                                        |          |          |      |

# **DC Characteristics**

#### **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Send Feedback

<sup>&</sup>lt;sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>&</sup>lt;sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

#### **Hot Socketing**

#### Table 2-14: Hot Socketing Specifications for Arria V GZ Devices

| Symbol                    | Description                                | Maximum               |

|---------------------------|--------------------------------------------|-----------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 µA                |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(124)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA                |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA                 |

#### Internal Weak Pull-Up Resistor

#### Table 2-15: Internal Weak Pull-Up Resistor for Arria V GZ Devices

All I/O pins have an option to enable the weak pull-up resistor except the configuration, test, and JTAG pins. The internal weak pull-down feature is only available for the JTAG TCK pin. The typical value for this internal weak pull-down resistor is approximately 25 k $\Omega$ .

| Symbol          | Description                                                                                                                                                  | V <sub>CCIO</sub> Conditions (V) <sup>(125)</sup> | Value <sup>(126)</sup> | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------|------|

| K <sub>PU</sub> | Value of the I/O pin pull-up resistor<br>before and during configuration, as well as<br>user mode if you enable the<br>programmable pull-up resistor option. | 3.0 ±5%                                           | 25                     | kΩ   |

|                 |                                                                                                                                                              | 2.5 ±5%                                           | 25                     | kΩ   |

|                 |                                                                                                                                                              | 1.8 ±5%                                           | 25                     | kΩ   |

|                 |                                                                                                                                                              | 1.5 ±5%                                           | 25                     | kΩ   |

|                 |                                                                                                                                                              | 1.35 ±5%                                          | 25                     | kΩ   |

|                 |                                                                                                                                                              | 1.25 ±5%                                          | 25                     | kΩ   |

|                 |                                                                                                                                                              | 1.2 ±5%                                           | 25                     | kΩ   |

<sup>(124)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(125)}</sup>$  The pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

$<sup>^{(126)}</sup>$  These specifications are valid with a ±10% tolerance to cover changes over PVT.

| Symbol/Description                         | Conditions                                                | Transc             | eiver Speed | Grade 2 | Transce | eiver Speed | Grade 3 | Unit |

|--------------------------------------------|-----------------------------------------------------------|--------------------|-------------|---------|---------|-------------|---------|------|

| Symbol/Description                         | Conditions                                                | Min                | Тур         | Max     | Min     | Тур         | Max     | Unit |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _                  | _           | 400     | _       | _           | 400     | 20   |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |                    | _           | 400     | _       |             | 400     | ps   |

| Duty cycle                                 | —                                                         | 45                 | _           | 55      | 45      |             | 55      | %    |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30                 | _           | 33      | 30      |             | 33      | kHz  |

| Spread-spectrum downspread                 | PCIe                                                      |                    | 0 to        | _       | _       | 0 to        | —       | %    |

|                                            |                                                           |                    | -0.5        |         |         | -0.5        |         |      |

| On-chip termination resistors              | —                                                         |                    | 100         | _       | _       | 100         | _       | Ω    |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |                    | _           | 1.6     | _       |             | 1.6     | V    |

|                                            | RX reference clock pin                                    |                    | _           | 1.2     | _       | _           | 1.2     |      |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4               | _           | _       | -0.4    | _           | _       | V    |

| Peak-to-peak differential input<br>voltage | -                                                         | 200                | -           | 1600    | 200     | _           | 1600    | mV   |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 1000/900/850 (139) |             |         | 10      | mV          |         |      |

| · · · · ·                                  | RX reference clock pin                                    | 1.                 | .0/0.9/0.85 | 140)    | 1       | mV          |         |      |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250                | _           | 550     | 250     |             | 550     | mV   |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

#### 2-32 Standard PCS Data Rate

| xN (PCIe) -        | ATX PLL                   |                          |                                                                                                       |                           | CMU PLL (161)         |                                                | fPLL                      |                       |                                                      |  |

|--------------------|---------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------------------------------|---------------------------|-----------------------|------------------------------------------------------|--|

|                    | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps)    | Channel<br>Span                                                                                       | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                | Non-bonded<br>Mode (Gbps) | Bonded<br>Mode (Gbps) | Channel<br>Span                                      |  |

| xN (PCIe)          | _                         | 8.0                      | 8                                                                                                     | _                         | 5.0                   | 8                                              | _                         | _                     | _                                                    |  |

| xN (Native PHY IP) | 8.0                       | 8.0<br>8.01 to<br>9.8304 | Up to 13<br>channels<br>above and<br>below PLL<br>Up to 7<br>channels<br>above<br>and<br>below<br>PLL | 7.99                      | 7.99                  | Up to 13<br>channels<br>above and<br>below PLL | 3.125                     | 3.125                 | Up to 13<br>channels<br>above<br>and<br>below<br>PLL |  |

# Standard PCS Data Rate

#### Table 2-30: Standard PCS Approximate Maximum Date Rate (Gbps) for Arria V GZ Devices

The maximum data rate is also constrained by the transceiver speed grade. Refer to the "Commercial and Industrial Speed Grade Offering for Arria V GZ Devices" table for the transceiver speed grade.

| Mode <sup>(164)</sup> Transceiver<br>Speed Grade |                | PMA Width                   | 20  | 20  | 16   | 16   | 10  | 10  | 8    | 8    |

|--------------------------------------------------|----------------|-----------------------------|-----|-----|------|------|-----|-----|------|------|

|                                                  | PCS/Core Width | 40                          | 20  | 32  | 16   | 20   | 10  | 16  | 8    |      |

| FIFO 2<br>3                                      | 2              | C3, I3L<br>core speed grade | 9.9 | 9   | 7.84 | 7.2  | 5.3 | 4.7 | 4.24 | 3.76 |

|                                                  | 3              | C4, I4<br>core speed grade  | 8.8 | 8.2 | 7.2  | 6.56 | 4.8 | 4.3 | 3.84 | 3.44 |

<sup>(161)</sup> ATX PLL is recommended at 8 Gbps and above data rates for improved jitter performance.

<sup>(164)</sup> The Phase Compensation FIFO can be configured in FIFO mode or register mode. In the FIFO mode, the pointers are not fixed, and the latency can vary. In the register mode the pointers are fixed for low latency.

# **Core Performance Specifications**

# **Clock Tree Specifications**

#### Table 2-33: Clock Tree Performance for Arria V GZ Devices

| Symbol                    | Perfor  | Unit   |      |

|---------------------------|---------|--------|------|

|                           | C3, I3L | C4, I4 | Onit |

| Global and Regional Clock | 650     | 580    | MHz  |

| Periphery Clock           | 500     | 500    | MHz  |

# **PLL Specifications**

# Table 2-34: PLL Specifications for Arria V GZ Devices

| Symbol                           | Parameter                                               | Min | Тур | Max  | Unit |

|----------------------------------|---------------------------------------------------------|-----|-----|------|------|

| f <sub>IN</sub> <sup>(167)</sup> | Input clock frequency (C3, I3L speed grade)             | 5   | _   | 800  | MHz  |

| IIN                              | Input clock frequency (C4, I4 speed grade)              | 5   | _   | 650  | MHz  |

| f <sub>INPFD</sub>               | Input frequency to the PFD                              | 5   |     | 325  | MHz  |

| f <sub>FINPFD</sub>              | Fractional Input clock frequency to the PFD             | 50  | _   | 160  | MHz  |

| <b>f</b> (168)                   | PLL VCO operating range (C3, I3L speed grade)           | 600 |     | 1600 | MHz  |

| $f_{\rm VCO}$ (168)              | PLL VCO operating range (C4, I4 speed grade)            | 600 | _   | 1300 | MHz  |

| t <sub>EINDUTY</sub>             | Input clock or external feedback clock input duty cycle | 40  |     | 60   | %    |

<sup>(167)</sup> This specification is limited in the Quartus II software by the I/O maximum frequency. The maximum I/O frequency is different for each I/O standard.

<sup>(168)</sup> The VCO frequency reported by the Quartus II software in the **PLL Usage Summary** section of the compilation report takes into consideration the VCO post-scale counter K value. Therefore, if the counter K has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

Arria V GZ Device Datasheet

AV-51002 2017.02.10

| Symbol                                                                                               | Conditions                                   | C3, I3L |     |           |     | Unit |           |      |

|------------------------------------------------------------------------------------------------------|----------------------------------------------|---------|-----|-----------|-----|------|-----------|------|

| Symbol                                                                                               | Conditions                                   | Min     | Тур | Мах       | Min | Тур  | Max       | Onic |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) True Differential<br>I/O Standards <sup>(179)</sup> | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       | _   | 625       | 5   |      | 525       | MHz  |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       |     | 625       | 5   | _    | 525       | MHz  |

| f <sub>HSCLK_in</sub> (input clock<br>frequency) Single Ended I/O<br>Standards                       | Clock boost factor<br>W = 1 to 40 $^{(180)}$ | 5       | _   | 420       | 5   |      | 420       | MHz  |

| f <sub>HSCLK_OUT</sub> (output clock<br>frequency)                                                   | _                                            | 5       | _   | 625 (181) | 5   | —    | 525 (181) | MHz  |

#### Transmitter High-Speed I/O Specifications

#### Table 2-40: Transmitter High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

$<sup>^{(179)}\,</sup>$  This only applies to DPA and soft-CDR modes.

<sup>&</sup>lt;sup>(180)</sup> Clock Boost Factor (W) is the ratio between the input data rate to the input clock rate.

<sup>&</sup>lt;sup>(181)</sup> This is achieved by using the LVDS clock network.

#### Non DPA Mode High-Speed I/O Specifications

#### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions |     | C3, I3L |     |     | Unit |     |      |

|-----------------|------------|-----|---------|-----|-----|------|-----|------|

| Symbol          | Conditions | Min | Тур     | Max | Min | Тур  | Мах | Onic |

| Sampling Window | _          |     |         | 300 |     |      | 300 | ps   |