Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 10377                                                      |

| Number of Logic Elements/Cells | 220000                                                     |

| Total RAM Bits                 | 15282176                                                   |

| Number of I/O                  | 414                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA                                           |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agzme1h3f35c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 1-1: Absolute Maximum Ratings for Arria V Devices

| Symbol                    | Description                                                                                          | Minimum | Maximum | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------|---------|---------|------|

| $V_{CC}$                  | Core voltage power supply                                                                            | -0.50   | 1.43    | V    |

| V <sub>CCP</sub>          | Periphery circuitry, PCIe® hardIP block, and transceiver physical coding sublayer (PCS) power supply | -0.50   | 1.43    | V    |

| V <sub>CCPGM</sub>        | Configuration pins power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CC_AUX</sub>       | Auxiliary supply                                                                                     | -0.50   | 3.25    | V    |

| V <sub>CCBAT</sub>        | Battery back-up power supply for design security volatile key register                               | -0.50   | 3.90    | V    |

| V <sub>CCPD</sub>         | I/O pre-driver power supply                                                                          | -0.50   | 3.90    | V    |

| V <sub>CCIO</sub>         | I/O power supply                                                                                     | -0.50   | 3.90    | V    |

| V <sub>CCD_FPLL</sub>     | Phase-locked loop (PLL) digital power supply                                                         | -0.50   | 1.80    | V    |

| V <sub>CCA_FPLL</sub>     | PLL analog power supply                                                                              | -0.50   | 3.25    | V    |

| V <sub>CCA_GXB</sub>      | Transceiver high voltage power                                                                       | -0.50   | 3.25    | V    |

| V <sub>CCH_GXB</sub>      | Transmitter output buffer power                                                                      | -0.50   | 1.80    | V    |

| V <sub>CCR_GXB</sub>      | Receiver power                                                                                       | -0.50   | 1.50    | V    |

| V <sub>CCT_GXB</sub>      | Transmitter power                                                                                    | -0.50   | 1.50    | V    |

| V <sub>CCL_GXB</sub>      | Transceiver clock network power                                                                      | -0.50   | 1.50    | V    |

| $\overline{V_{I}}$        | DC input voltage                                                                                     | -0.50   | 3.80    | V    |

| V <sub>CC_HPS</sub>       | HPS core voltage and periphery circuitry power supply                                                | -0.50   | 1.43    | V    |

| V <sub>CCPD_HPS</sub>     | HPS I/O pre-driver power supply                                                                      | -0.50   | 3.90    | V    |

| V <sub>CCIO_HPS</sub>     | HPS I/O power supply                                                                                 | -0.50   | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub> | HPS reset and clock input pins power supply                                                          | -0.50   | 3.90    | V    |

Altera Corporation

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol                            | Description                                 | Condition          | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------------------------|--------------------|------------------------|---------|------------------------|------|

| V                                 | Cara valtaga navvar supply                  | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| $V_{CC}$                          | Core voltage power supply                   | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

| V                                 | Periphery circuitry, PCIe hard IP block,    | -C4, -I5, -C5, -C6 | 1.07                   | 1.1     | 1.13                   | V    |

| $V_{CCP}$                         | and transceiver PCS power supply            | -I3                | 1.12                   | 1.15    | 1.18                   | V    |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| V                                 | Configuration pins power supply             | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

| $V_{CCPGM}$                       | Configuration pins power supply             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

|                                   |                                             | 1.8 V              | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply                            | _                  | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(2)</sup> | Battery back-up power supply                | _                  | 1.2                    | _       | 3.0                    | V    |

|                                   | (For design security volatile key register) |                    |                        |         |                        |      |

|                                   |                                             | 3.3 V              | 3.135                  | 3.3     | 3.465                  | V    |

| $V_{CCPD}^{(3)}$                  | I/O pre-driver power supply                 | 3.0 V              | 2.85                   | 3.0     | 3.15                   | V    |

|                                   |                                             | 2.5 V              | 2.375                  | 2.5     | 2.625                  | V    |

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(2)</sup> If you do not use the design security feature in Arria V devices, connect V<sub>CCBAT</sub> to a 1.5-V, 2.5-V, or 3.0-V power supply. Arria V power-on reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

$<sup>^{(3)}</sup>$  V<sub>CCPD</sub> must be 2.5 V when V<sub>CCIO</sub> is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V. V<sub>CCPD</sub> must be 3.0 V when V<sub>CCIO</sub> is 3.0 V. V<sub>CCPD</sub> must be 3.3 V when V<sub>CCIO</sub> is 3.3 V.

## I/O Pin Leakage Current

Table 1-6: I/O Pin Leakage Current for Arria V Devices

| Symbol           | Description        | Condition                             | Min | Тур | Max | Unit |

|------------------|--------------------|---------------------------------------|-----|-----|-----|------|

| $I_{\mathrm{I}}$ | Input pin          | $V_{I} = 0 V \text{ to } V_{CCIOMAX}$ | -30 | _   | 30  | μΑ   |

| I <sub>OZ</sub>  | Tri-stated I/O pin | $V_O = 0 V \text{ to } V_{CCIOMAX}$   | -30 | _   | 30  | μΑ   |

## **Bus Hold Specifications**

### Table 1-7: Bus Hold Parameters for Arria V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

|                                             |                   |                                               | V <sub>CCIO</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|---------------------------------------------|-------------------|-----------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                     | 1                     | .2   | 1   | .5   | 1   | .8   | 2   | .5   | 3   | .0   | 3.  | .3   | Unit |

|                                             |                   |                                               | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | $V_{IN} > V_{IL}$ (max)                       | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μA   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | $V_{IN} < V_{IH}$ (min)                       | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μA   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | 0 V < V <sub>IN</sub><br>< V <sub>CCIO</sub>  | _                     | 125  | _   | 175  | _   | 200  | _   | 300  | _   | 500  | _   | 500  | μA   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub> | _                     | -125 | _   | -175 | _   | -200 | _   | -300 | _   | -500 | _   | -500 | μA   |

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol                    | Description                                  | Maximum | Unit |

|---------------------------|----------------------------------------------|---------|------|

| I <sub>XCVR-RX</sub> (DC) | DC current per transceiver receiver (RX) pin | 50      | mA   |

## **Internal Weak Pull-Up Resistor**

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

Table 1-13: Internal Weak Pull-Up Resistor Values for Arria V Devices

| Symbol      | Description | Condition (V) <sup>(11)</sup>    | Value <sup>(12)</sup> | Unit |

|-------------|-------------|----------------------------------|-----------------------|------|

|             |             | $V_{CCIO} = 3.3 \pm 5\%$         | 25                    | kΩ   |

|             |             | $V_{CCIO} = 3.0 \pm 5\%$         | 25                    | kΩ   |

|             |             | $V_{CCIO} = 2.5 \pm 5\%$         | 25                    | kΩ   |

| $ m R_{PU}$ | -           | $V_{CCIO} = 1.8 \pm 5\%$         | 25                    | kΩ   |

| КрО         |             | $V_{CCIO} = 1.5 \pm 5\%$         | 25                    | kΩ   |

|             |             | $V_{\text{CCIO}} = 1.35 \pm 5\%$ | 25                    | kΩ   |

|             |             | $V_{CCIO} = 1.25 \pm 5\%$        | 25                    | kΩ   |

|             |             | $V_{\text{CCIO}} = 1.2 \pm 5\%$  | 25                    | kΩ   |

#### **Related Information**

## Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

Arria V GX, GT, SX, and ST Device Datasheet

The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(11)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

<sup>(12)</sup> Valid with ±10% tolerances to cover changes over PVT.

## **I/O Standard Specifications**

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

### Single-Ended I/O Standards

Table 1-14: Single-Ended I/O Standards for Arria V Devices

| I/O Standard    |       | V <sub>CCIO</sub> (V) |       | 1    | V <sub>IL</sub> (V)    | V <sub>IH</sub>        | (V)                  | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)          | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |

|-----------------|-------|-----------------------|-------|------|------------------------|------------------------|----------------------|------------------------|------------------------------|---------------------------------|--------------------------------------|

| i/O Standard    | Min   | Тур                   | Max   | Min  | Max                    | Min                    | Max                  | Max                    | Min                          | (mA)                            | IOH. (IIIA)                          |

| 3.3-V<br>LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.45                   | 2.4                          | 4                               | -4                                   |

| 3.3-V<br>LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2      | 2                               | -2                                   |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.4                    | 2.4                          | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6                  | 0.2                    | V <sub>CCIO</sub> - 0.2      | 0.1                             | -0.1                                 |

| 3.0-V PCI       | 2.85  | 3                     | 3.15  | _    | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{\text{CCIO}}$ | 1.5                             | -0.5                                 |

| 3.0-V<br>PCI-X  | 2.85  | 3                     | 3.15  | _    | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{\rm CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$        | 1.5                             | -0.5                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                    | 1.7                    | 3.6                  | 0.4                    | 2                            | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> - 0.45     | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575 | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$       | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{\rm CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$       | 2                               | -2                                   |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

Arria V GX, GT, SX, and ST Device Datasheet

| Symbol/Description                       | Condition                                                     | Transc               | eiver Speed G                                                | Grade 4                        | Transceiver Speed Grade 6 |                              |                      | Unit  |

|------------------------------------------|---------------------------------------------------------------|----------------------|--------------------------------------------------------------|--------------------------------|---------------------------|------------------------------|----------------------|-------|

| 3ymbor/Description                       |                                                               | Min                  | Тур                                                          | Max                            | Min                       | Тур                          | Max                  | Offic |

| Run length                               | _                                                             | _                    | _                                                            | 200                            | _                         | _                            | 200                  | UI    |

| Programmable equalization AC and DC gain | AC gain setting = 0 to $3^{(38)}$<br>DC gain setting = 0 to 1 | Gain and<br>Response | TLE Respons<br>DC Gain for<br>at Data Rates<br>ain for Arria | r Arria V GX,<br>s ≤ 3.25 Gbps | , GT, SX, and across Supp | ST Devices a<br>orted AC Gai | nd CTLE<br>in and DC | dB    |

Table 1-23: Transmitter Specifications for Arria V GX and SX Devices

| Symbol/Description                                          | Condition                                                       | Transc | eiver Speed C | irade 4  | Transc | eiver Speed G | irade 6 | Unit  |

|-------------------------------------------------------------|-----------------------------------------------------------------|--------|---------------|----------|--------|---------------|---------|-------|

| Symbol/Description                                          | Condition                                                       | Min    | Тур           | Max      | Min    | Тур           | Max     | Offic |

| Supported I/O standards                                     |                                                                 |        |               | 1.5 V PC | ML     |               |         |       |

| Data rate                                                   | _                                                               | 611    | _             | 6553.6   | 611    | _             | 3125    | Mbps  |

| V <sub>OCM</sub> (AC coupled)                               | _                                                               | _      | 650           | _        | _      | 650           | _       | mV    |

| V <sub>OCM</sub> (DC coupled)                               | $\leq 3.2 \text{Gbps}^{(32)}$                                   | 670    | 700           | 730      | 670    | 700           | 730     | mV    |

|                                                             | 85-Ω setting                                                    | _      | 85            | _        | _      | 85            | _       | Ω     |

| Differential on-chip                                        | 100- $\Omega$ setting                                           | _      | 100           | _        | _      | 100           | _       | Ω     |

| termination resistors                                       | 120- $Ω$ setting                                                | _      | 120           | _        | _      | 120           | _       | Ω     |

|                                                             | 150- $\Omega$ setting                                           | _      | 150           | _        | _      | 150           | _       | Ω     |

| Intra-differential pair skew                                | TX V <sub>CM</sub> = 0.65 V (AC coupled) and slew rate of 15 ps | _      | _             | 15       | _      | _             | 15      | ps    |

| Intra-transceiver block transmitter channel-to-channel skew | ×6 PMA bonded mode                                              | _      | _             | 180      | _      | _             | 180     | ps    |

Arria V GX, GT, SX, and ST Device Datasheet

The rate match FIFO supports only up to ±300 parts per million (ppm).

The Quartus Prime software allows AC gain setting = 3 for design with data rate between 611 Mbps and 1.25 Gbps only.

## **DSP Block Performance Specifications**

Table 1-37: DSP Block Performance Specifications for Arria V Devices

|                               | Mode                                                     |          | Performance |     | Unit |  |

|-------------------------------|----------------------------------------------------------|----------|-------------|-----|------|--|

|                               | Wode                                                     | −I3, −C4 | −I5, −C5    | -C6 | Onit |  |

|                               | Independent 9 × 9 multiplication                         | 370      | 310         | 220 | MHz  |  |

|                               | Independent 18 × 19 multiplication                       | 370      | 310         | 220 | MHz  |  |

|                               | Independent 18 × 25 multiplication                       | 370      | 310         | 220 | MHz  |  |

| C                             | Independent 20 × 24 multiplication                       | 370      | 310         | 220 | MHz  |  |

| Block                         | Independent 27 × 27 multiplication                       | 310      | 250         | 200 | MHz  |  |

|                               | Two 18 × 19 multiplier adder mode                        | 370      | 310         | 220 | MHz  |  |

|                               | $18 \times 18$ multiplier added summed with 36-bit input | 370      | 310         | 220 | MHz  |  |

| Modes using Two<br>DSP Blocks | Complex 18 × 19 multiplication                           | 370      | 310         | 220 | MHz  |  |

## **Memory Block Performance Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to 50% output duty cycle. Use the Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in  $f_{MAX}$ .

Altera Corporation Arria V GX, GT, SX, and ST Device Datasheet

Table 1-38: Memory Block Performance Specifications for Arria V Devices

| Memory        | Mode                                                                                             | Resourc | es Used |          | Performance |              | - Unit |  |

|---------------|--------------------------------------------------------------------------------------------------|---------|---------|----------|-------------|--------------|--------|--|

| Welliory      | Mode                                                                                             | ALUTs   | Memory  | −I3, −C4 | −l5, −C5    | - <b>C</b> 6 | Offic  |  |

|               | Single port, all supported widths                                                                | 0       | 1       | 500      | 450         | 400          | MHz    |  |

| MLAB Sim      | Simple dual-port, all supported widths                                                           | 0       | 1       | 500      | 450         | 400          | MHz    |  |

|               | Simple dual-port with read and write at the same address                                         | 0       | 1       | 400      | 350         | 300          | MHz    |  |

|               | ROM, all supported width                                                                         | _       | _       | 500      | 450         | 400          | MHz    |  |

|               | Single-port, all supported widths                                                                | 0       | 1       | 400      | 350         | 285          | MHz    |  |

|               | Simple dual-port, all supported widths                                                           | 0       | 1       | 400      | 350         | 285          | MHz    |  |

| M10K<br>Block | Simple dual-port with the read-during-write option set to <b>Old Data</b> , all supported widths | 0       | 1       | 315      | 275         | 240          | MHz    |  |

|               | True dual port, all supported widths                                                             | 0       | 1       | 400      | 350         | 285          | MHz    |  |

|               | ROM, all supported widths                                                                        | 0       | 1       | 400      | 350         | 285          | MHz    |  |

## **Internal Temperature Sensing Diode Specifications**

Table 1-39: Internal Temperature Sensing Diode Specifications for Arria V Devices

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum Resolution with no<br>Missing Codes |

|-------------------|----------|-----------------------------|---------------|--------------------|------------|---------------------------------------------|

| −40 to 100°C      | ±8°C     | No                          | 1 MHz         | < 100 ms           | 8 bits     | 8 bits                                      |

## **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

Arria V GX, GT, SX, and ST Device Datasheet

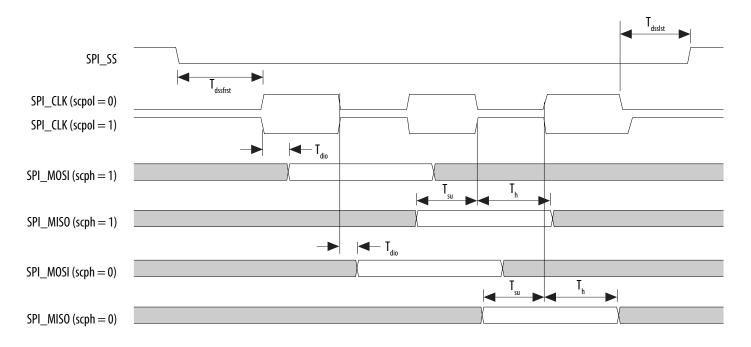

**Figure 1-9: SPI Master Timing Diagram**

Table 1-53: SPI Slave Timing Requirements for Arria V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol           | Description                                     | Min | Max | Unit |

|------------------|-------------------------------------------------|-----|-----|------|

| $T_{clk}$        | CLK clock period                                | 20  | _   | ns   |

| $T_s$            | MOSI Setup time                                 | 5   | _   | ns   |

| $T_{h}$          | MOSI Hold time                                  | 5   | _   | ns   |

| $T_{suss}$       | Setup time SPI_SS valid before first clock edge | 8   | _   | ns   |

| T <sub>hss</sub> | Hold time SPI_SS valid after last clock edge    | 8   | _   | ns   |

| $T_d$            | MISO output delay                               | _   | 6   | ns   |

Arria V GX, GT, SX, and ST Device Datasheet

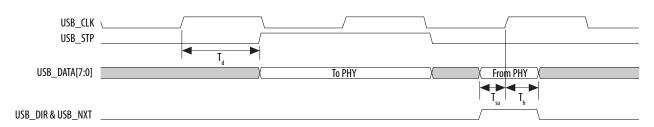

Figure 1-12: USB Timing Diagram

## **Ethernet Media Access Controller (EMAC) Timing Characteristics**

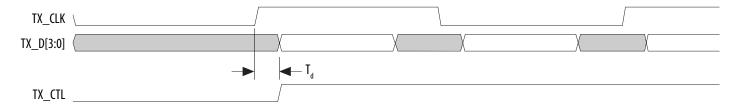

Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | _     | 40  | _    | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 | _    | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    | _   | 55   | %    |

| $T_d$                         | TX_CLK to TXD/TX_CTL output data delay | -0.85 | _   | 0.15 | ns   |

Figure 1-13: RGMII TX Timing Diagram

## **HPS JTAG Timing Specifications**

Table 1-62: HPS JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min | Max                | Unit |

|-------------------------|------------------------------------------|-----|--------------------|------|

| $t_{JCP}$               | TCK clock period                         | 30  | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14  | _                  | ns   |

| $t_{ m JCL}$            | TCK clock low time                       | 14  | _                  | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2   | _                  | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3   | _                  | ns   |

| $t_{JPH}$               | JTAG port hold time                      | 5   | _                  | ns   |

| $t_{ m JPCO}$           | JTAG port clock to output                | _   | 12 <sup>(90)</sup> | ns   |

| $t_{JPZX}$              | JTAG port high impedance to valid output | _   | $14^{(90)}$        | ns   |

| $t_{ m JPXZ}$           | JTAG port valid output to high impedance | _   | 14 <sup>(90)</sup> | ns   |

## **Configuration Specifications**

This section provides configuration specifications and timing for Arria V devices.

## **POR Specifications**

Table 1-63: Fast and Standard POR Delay Specification for Arria V Devices

| POR Delay | Minimum | Maximum            | Unit |

|-----------|---------|--------------------|------|

| Fast      | 4       | 12 <sup>(91)</sup> | ms   |

$<sup>^{(90)}</sup>$  A 1-ns adder is required for each  $V_{CCIO\_HPS}$  voltage step down from 3.0 V. For example,  $t_{JPCO}$ = 13 ns if  $V_{CCIO\_HPS}$  of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(91)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- PowerPlay Power Analysis

For more information about PowerPlay power analysis.

### **Power Consumption**

Altera offers two ways to estimate power consumption for a design—the Excel-based Early Power Estimator and the Quartus II PowerPlay Power Analyzer feature.

**Note:** You typically use the interactive Excel-based Early Power Estimator before designing the FPGA to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- PowerPlay Power Analysis

For more information about PowerPlay power analysis.

## I/O Pin Leakage Current

## Table 2-8: I/O Pin Leakage Current for Arria V GZ Devices

If  $V_O = V_{CCIO}$  to  $V_{CCIOMax}$ , 100  $\mu A$  of leakage current per I/O is expected.

| Symbol           | Description        | Conditions                                    | Min | Тур | Max | Unit |

|------------------|--------------------|-----------------------------------------------|-----|-----|-----|------|

| $I_{\mathrm{I}}$ | Input pin          | $V_{\rm I} = 0 \text{ V to } V_{\rm CCIOMAX}$ | -30 |     | 30  | μΑ   |

| $I_{OZ}$         | Tri-stated I/O pin | $V_O = 0 V \text{ to } V_{CCIOMAX}$           | -30 | _   | 30  | μΑ   |

## **I/O Standard Specifications**

The  $V_{OL}$  and  $V_{OH}$  values are valid at the corresponding  $I_{OH}$  and  $I_{OL}$ , respectively.

Table 2-16: Single-Ended I/O Standards for Arria V GZ Devices

| I/O Standard  |       | V <sub>CCIO</sub> (V) |       | V <sub>II</sub> | _(V)                       | V <sub>IH</sub>            | (V)                     | V <sub>OL</sub> (V)                                        | V <sub>OH</sub> (V)           | I <sub>OL</sub> (mA) | I <sub>OH</sub> (mA) |

|---------------|-------|-----------------------|-------|-----------------|----------------------------|----------------------------|-------------------------|------------------------------------------------------------|-------------------------------|----------------------|----------------------|

| i/O Staildaid | Min   | Тур                   | Max   | Min             | Max                        | Min                        | Max                     | Max                                                        | Min                           | IOL (IIIA)           | IOH (IIIA)           |

| LVTTL         | 2.85  | 3                     | 3.15  | -0.3            | 0.8                        | 1.7                        | 3.6                     | 0.4                                                        | 2.4                           | 2                    | -2                   |

| LVCMOS        | 2.85  | 3                     | 3.15  | -0.3            | 0.8                        | 1.7                        | 3.6                     | 0.2                                                        | V <sub>CCIO</sub> - 0.2       | 0.1                  | -0.1                 |

| 2.5 V         | 2.375 | 2.5                   | 2.625 | -0.3            | 0.7                        | 1.7                        | 3.6                     | 0.4                                                        | 2                             | 1                    | -1                   |

| 1.8 V         | 1.71  | 1.8                   | 1.89  | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | 0.45                                                       | V <sub>CCIO</sub> - 0.45      | 2                    | -2                   |

| 1.5 V         | 1.425 | 1.5                   | 1.575 | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $\begin{array}{c} 0.25 \times \\ V_{\rm CCIO} \end{array}$ | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |

| 1.2 V         | 1.14  | 1.2                   | 1.26  | -0.3            | $0.35 \times V_{\rm CCIO}$ | $0.65 \times V_{\rm CCIO}$ | V <sub>CCIO</sub> + 0.3 | $\begin{array}{c} 0.25 \times \\ V_{\rm CCIO} \end{array}$ | $0.75 \times V_{\text{CCIO}}$ | 2                    | -2                   |

Table 2-17: Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     |       | V <sub>REF</sub> (V)          |                                                           |                            | V <sub>TT</sub> (V)                                        |                |                         |  |

|------------------------|-----------------------|-----|-------|-------------------------------|-----------------------------------------------------------|----------------------------|------------------------------------------------------------|----------------|-------------------------|--|

| I/O Stallualu          | Min                   | Тур | Max   | Min                           | Тур                                                       | Max                        | Min                                                        | Тур            | Max                     |  |

| SSTL-2<br>Class I, II  | 2.375                 | 2.5 | 2.625 | $0.49 \times V_{CCIO}$        | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} \end{array}$ | $0.51 \times V_{\rm CCIO}$ | V <sub>REF</sub> - 0.04                                    | $V_{REF}$      | V <sub>REF</sub> + 0.04 |  |

| SSTL-18<br>Class I, II | 1.71                  | 1.8 | 1.89  | 0.833                         | 0.9                                                       | 0.969                      | V <sub>REF</sub> - 0.04                                    | $V_{REF}$      | V <sub>REF</sub> + 0.04 |  |

| SSTL-15<br>Class I, II | 1.425                 | 1.5 | 1.575 | $0.49 \times V_{\text{CCIO}}$ | $0.5 \times V_{\rm CCIO}$                                 | $0.51 \times V_{\rm CCIO}$ | $\begin{array}{c} 0.49 \times \\ V_{\rm CCIO} \end{array}$ | 0.5 ×<br>VCCIO | $0.51 \times V_{CCIO}$  |  |

| Symbol/Description                                 | Conditions                  | Transceiver Speed Grade 2 |          |      | Transceiver Speed Grade 3 |          |      | Unit     |

|----------------------------------------------------|-----------------------------|---------------------------|----------|------|---------------------------|----------|------|----------|

| Symbol/Description                                 | Conditions                  | Min                       | Тур      | Max  | Min                       | Тур      | Max  | Offic    |

|                                                    | 100 Hz                      | _                         | _        | -70  | _                         | _        | -70  | dBc/Hz   |

|                                                    | 1 kHz                       | _                         | _        | -90  | _                         | _        | -90  | dBc/Hz   |

| Transmitter REFCLK Phase<br>Noise (622 MHz) (141)  | 10 kHz                      | _                         | _        | -100 | _                         | _        | -100 | dBc/Hz   |

| 1,000 (022 11112)                                  | 100 kHz                     | _                         | _        | -110 | _                         | _        | -110 | dBc/Hz   |

|                                                    | ≥1 MHz                      | _                         | _        | -120 | _                         | _        | -120 | dBc/Hz   |

| Transmitter REFCLK Phase<br>Jitter (100 MHz) (142) | 10 kHz to 1.5 MHz<br>(PCIe) | _                         | _        | 3    | _                         | _        | 3    | ps (rms) |

| R <sub>REF</sub>                                   | _                           | _                         | 1800 ±1% | _    | _                         | 1800 ±1% | _    | Ω        |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

### **Transceiver Clocks**

## Table 2-23: Transceiver Clocks Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

To calculate the REFCLK phase noise requirement at frequencies other than 622 MHz, use the following formula: REFCLK phase noise at f(MHz) = REFCLK phase noise at

To calculate the REFCLK rms phase jitter requirement for PCIe at reference clock frequencies other than 100 MHz, use the following formula: REFCLK rms phase jitter at f(MHz) = REFCLK rms phase jitter at  $100 MHz \times 100/f$ .

## **Typical VOD Settings**

Table 2-32: Typical  $V_{\text{OD}}$  Setting for Arria V GZ Channel, TX Termination = 100  $\Omega$

The tolerance is +/-20% for all VOD settings except for settings 2 and below.

| Symbol                                        | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|-----------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                               | 0 (166)                 | 0                          | 32                      | 640                        |

|                                               | 1 <sup>(166)</sup>      | 20                         | 33                      | 660                        |

|                                               | 2(166)                  | 40                         | 34                      | 680                        |

|                                               | 3 <sup>(166)</sup>      | 60                         | 35                      | 700                        |

|                                               | 4 <sup>(166)</sup>      | 80                         | 36                      | 720                        |

|                                               | 5 <sup>(166)</sup>      | 100                        | 37                      | 740                        |

|                                               | 6                       | 120                        | 38                      | 760                        |

| $ m V_{OD}$ differential peak to peak typical | 7                       | 140                        | 39                      | 780                        |

|                                               | 8                       | 160                        | 40                      | 800                        |

|                                               | 9                       | 180                        | 41                      | 820                        |

|                                               | 10                      | 200                        | 42                      | 840                        |

|                                               | 11                      | 220                        | 43                      | 860                        |

|                                               | 12                      | 240                        | 44                      | 880                        |

|                                               | 13                      | 260                        | 45                      | 900                        |

|                                               | 14                      | 280                        | 46                      | 920                        |

Altera Corporation Arria V GZ Device Datasheet

<sup>(166)</sup> If TX termination resistance = 100 Ω, this VOD setting is illegal.

| Symbol                                        | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|-----------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                               | 15                      | 300                        | 47                      | 940                        |

|                                               | 16                      | 320                        | 48                      | 960                        |

|                                               | 17                      | 340                        | 49                      | 980                        |

|                                               | 18                      | 360                        | 50                      | 1000                       |

|                                               | 19                      | 380                        | 51                      | 1020                       |

|                                               | 20                      | 400                        | 52                      | 1040                       |

|                                               | 21                      | 420                        | 53                      | 1060                       |

|                                               | 22                      | 440                        | 54                      | 1080                       |

| $ m V_{OD}$ differential peak to peak typical | 23                      | 460                        | 55                      | 1100                       |

|                                               | 24                      | 480                        | 56                      | 1120                       |

|                                               | 25                      | 500                        | 57                      | 1140                       |

|                                               | 26                      | 520                        | 58                      | 1160                       |

|                                               | 27                      | 540                        | 59                      | 1180                       |

|                                               | 28                      | 560                        | 60                      | 1200                       |

|                                               | 29                      | 580                        | 61                      | 1220                       |

|                                               | 30                      | 600                        | 62                      | 1240                       |

|                                               | 31                      | 620                        | 63                      | 1260                       |

| Mode                          | Performan | ıce |     | Unit |  |

|-------------------------------|-----------|-----|-----|------|--|

| Mode                          | C3, I3L   | C4  | 14  | Onic |  |

| One sum of two $27 \times 27$ | 380       | 300 | MHz |      |  |

| One sum of two $36 \times 18$ | 380       | 30  | MHz |      |  |

| One complex 18 × 18           | 400       | 35  | MHz |      |  |

| One 36 × 36                   | 380       | 30  | MHz |      |  |

| Modes using Three DSP Blocks  |           |     |     |      |  |

| One complex 18 × 25           | 340       | 275 | 265 | MHz  |  |

| Modes using Four DSP Blocks   | •         |     |     |      |  |

| One complex $27 \times 27$    | 350       | 310 |     | MHz  |  |

## **Memory Block Specifications**

## Table 2-36: Memory Block Performance Specifications for Arria V GZ Devices

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL set to **50**% output duty cycle. Use the Quartus II software to report timing for this and other memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in  $F_{MAX}$ .

| Memory | Mode                              | Resources Used |        | Performance |     |     |     | Unit  |

|--------|-----------------------------------|----------------|--------|-------------|-----|-----|-----|-------|

|        |                                   | ALUTs          | Memory | C3          | C4  | I3L | 14  | Offic |

| MLAB   | Single port, all supported widths | 0              | 1      | 400         | 315 | 400 | 315 | MHz   |

|        | Simple dual-port, x32/x64 depth   | 0              | 1      | 400         | 315 | 400 | 315 | MHz   |

|        | Simple dual-port, x16 depth (178) | 0              | 1      | 533         | 400 | 533 | 400 | MHz   |

|        | ROM, all supported widths         | 0              | 1      | 500         | 450 | 500 | 450 | MHz   |

<sup>&</sup>lt;sup>(178)</sup> The F<sub>MAX</sub> specification is only achievable with Fitter options, **MLAB Implementation In 16-Bit Deep Mode** enabled.

Altera Corporation

Arria V GZ Device Datasheet

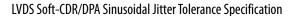

Figure 2-4: LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specification for a Data Rate ≥ 1.25 Gbps

Table 2-45: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate ≥ 1.25 Gbps

| Jitter Fred | Sinusoidal Jitter (UI) |        |  |

|-------------|------------------------|--------|--|

| F1          | 10,000                 | 25.000 |  |

| F2          | 17,565                 | 25.000 |  |

| F3          | 1,493,000              | 0.350  |  |

| F4          | 50,000,000             | 0.350  |  |

## **Passive Serial Configuration Timing**

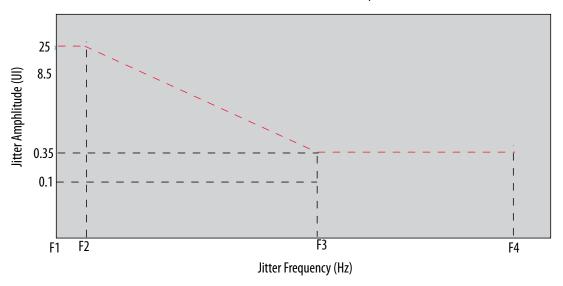

## Figure 2-10: PS Configuration Timing Waveform

Timing waveform for a passive serial (PS) configuration when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 2. After power-up, the Arria V GZ device holds nSTATUS low for the time of the POR delay.

- 3. After power-up, before and during configuration, CONF\_DONE is low.

- 4. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 5. DATA0 is available as a user I/O pin after configuration. The state of this pin depends on the dual-purpose pin settings in the Device and Pins Option.

- 6. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 7. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

| Term                               | Definition                                                                                                                                                                                                                                                              |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm C}$                        | High-speed receiver and transmitter input and output clock period.                                                                                                                                                                                                      |

| TCCS (channel-to-<br>channel-skew) | The timing difference between the fastest and slowest output edges, including $t_{\rm CO}$ variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |

| $t_{ m DUTY}$                      | High-speed I/O block—Duty cycle on the high-speed transmitter output clock.                                                                                                                                                                                             |

| $t_{ m FALL}$                      | Signal high-to-low transition time (80-20%)                                                                                                                                                                                                                             |

| t <sub>INCCJ</sub>                 | Cycle-to-cycle jitter tolerance on the PLL clock input.                                                                                                                                                                                                                 |

| t <sub>OUTPJ_IO</sub>              | Period jitter on the general purpose I/O driven by a PLL.                                                                                                                                                                                                               |

| t <sub>OUTPJ_DC</sub>              | Period jitter on the dedicated clock output driven by a PLL.                                                                                                                                                                                                            |

| t <sub>RISE</sub>                  | Signal low-to-high transition time (20-80%)                                                                                                                                                                                                                             |

| Timing Unit Interval (TUI)         | The timing budget allowed for skew, propagation delays, and the data sampling window. $(TUI = 1/(receiver input clock frequency multiplication factor) = t_C/w)$                                                                                                        |

| $V_{CM(DC)}$                       | DC common mode input voltage.                                                                                                                                                                                                                                           |

| $V_{ICM}$                          | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                                                                                                                   |

| V <sub>ID</sub>                    | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.                                                                                                            |

| V <sub>DIF(AC)</sub>               | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                                                                                                                             |

| V <sub>DIF(DC)</sub>               | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                                                                                                                            |

| $\overline{ m V_{IH}}$             | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                                                                                                                   |

| V <sub>IH(AC)</sub>                | High-level AC input voltage                                                                                                                                                                                                                                             |

| $ m V_{IH(DC)}$                    | High-level DC input voltage                                                                                                                                                                                                                                             |

| $V_{IL}$                           | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                                                                                                                     |

| V <sub>IL(AC)</sub>                | Low-level AC input voltage                                                                                                                                                                                                                                              |

| V <sub>IL(DC)</sub>                | Low-level DC input voltage                                                                                                                                                                                                                                              |