## Intel - 5AGZME3E3H29C4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 16980                                                      |

| Number of Logic Elements/Cells | 360000                                                     |

| Total RAM Bits                 | 23946240                                                   |

| Number of I/O                  | 342                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA, FCBGA                                            |

| Supplier Device Package        | 780-HBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agzme3e3h29c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                    | Description                                  | Maximum | Unit |

|---------------------------|----------------------------------------------|---------|------|

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver (RX) pin | 50      | mA   |

## Internal Weak Pull-Up Resistor

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

## Table 1-13: Internal Weak Pull-Up Resistor Values for Arria V Devices

| Symbol          | Description                                                                                       | Condition (V) <sup>(11)</sup> | Value <sup>(12)</sup> | Unit |

|-----------------|---------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|------|

|                 |                                                                                                   | $V_{CCIO} = 3.3 \pm 5\%$      | 25                    | kΩ   |

|                 |                                                                                                   | $V_{CCIO} = 3.0 \pm 5\%$      | 25                    | kΩ   |

|                 |                                                                                                   | $V_{CCIO} = 2.5 \pm 5\%$      | 25                    | kΩ   |

| R <sub>PU</sub> | configuration, as well as user mode if you have enabled the programmable pull-up resistor option. | $V_{CCIO} = 1.8 \pm 5\%$      | 25                    | kΩ   |

| Кру             |                                                                                                   | $V_{CCIO} = 1.5 \pm 5\%$      | 25                    | kΩ   |

|                 |                                                                                                   | $V_{CCIO} = 1.35 \pm 5\%$     | 25                    | kΩ   |

|                 |                                                                                                   | $V_{CCIO} = 1.25 \pm 5\%$     | 25                    | kΩ   |

|                 |                                                                                                   | $V_{CCIO} = 1.2 \pm 5\%$      | 25                    | kΩ   |

#### **Related Information**

## Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

<sup>(10)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

$<sup>^{(11)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

<sup>&</sup>lt;sup>(12)</sup> Valid with  $\pm 10\%$  tolerances to cover changes over PVT.

| Protocol                                        | Sub-protocol | Data Rate (Mbps) |

|-------------------------------------------------|--------------|------------------|

|                                                 | SONET 155    | 155.52           |

| SONET                                           | SONET 622    | 622.08           |

|                                                 | SONET 2488   | 2,488.32         |

|                                                 | GPON 155     | 155.52           |

| Gigabit-capable passive optical network (GPON)  | GPON 622     | 622.08           |

| Orgabil-Capable passive optical network (Or ON) | GPON 1244    | 1,244.16         |

|                                                 | GPON 2488    | 2,488.32         |

| QSGMII                                          | QSGMII 5000  | 5,000            |

# **Core Performance Specifications**

# **Clock Tree Specifications**

## Table 1-35: Clock Tree Specifications for Arria V Devices

| Parameter                       |          | Unit     |     |      |

|---------------------------------|----------|----------|-----|------|

|                                 | -I3, -C4 | –I5, –C5 | -C6 | Onic |

| Global clock and Regional clock | 625      | 625      | 525 | MHz  |

| Peripheral clock                | 450      | 400      | 350 | MHz  |

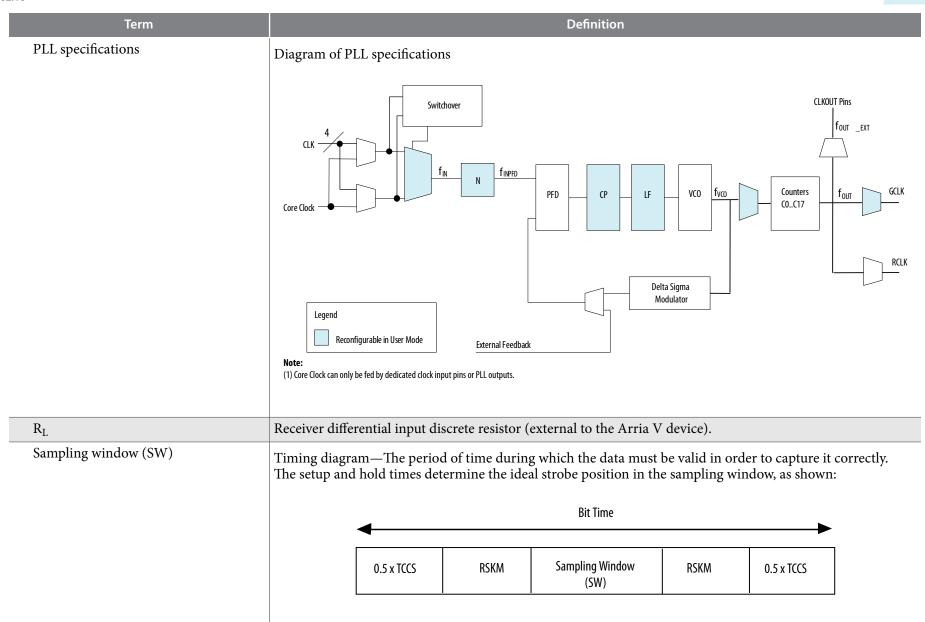

# **PLL Specifications**

## Table 1-36: PLL Specifications for Arria V Devices

This table lists the Arria V PLL block specifications. Arria V PLL block does not include HPS PLL.

| 1-46 | PLL Specifications |

|------|--------------------|

|------|--------------------|

| Symbol                                          | Parameter                                 | Condition                     | Min | Тур | Max                                       | Unit      |

|-------------------------------------------------|-------------------------------------------|-------------------------------|-----|-----|-------------------------------------------|-----------|

| + (67)                                          | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ | —   | _   | 175                                       | ps (p-p)  |

| t <sub>outpj_dc</sub> <sup>(67)</sup>           | in integer PLL                            | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 17.5                                      | mUI (p-p) |

| t(67)                                           | Period jitter for dedicated clock output  | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>FOUTPJ_DC</sub> <sup>(67)</sup>          | in fractional PLL                         | $F_{OUT} < 100 \text{ MHz}$   |     |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t                                               | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 175                                       | ps (p-p)  |

| t <sub>OUTCCJ_DC</sub> <sup>(67)</sup>          | output in integer PLL                     | $F_{OUT} < 100 \text{ MHz}$   | _   |     | 17.5                                      | mUI (p-p) |

| + (67)                                          | Cycle-to-cycle jitter for dedicated clock | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 250 <sup>(68)</sup> , 175 <sup>(69)</sup> | ps (p-p)  |

| t <sub>FOUTCCJ_DC</sub> <sup>(67)</sup>         | output in fractional PLL                  | $F_{OUT} < 100 \text{ MHz}$   | —   |     | 25 <sup>(68)</sup> , 17.5 <sup>(69)</sup> | mUI (p-p) |

| t <sub>OUTPJ_IO</sub> <sup>(67)(70)</sup>       | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| OUTPJ_IO                                        | regular I/O in integer PLL                | $F_{OUT} < 100 \text{ MHz}$   | _   | _   | 60                                        | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> <sup>(67)(68)(70)</sup>  | Period jitter for clock output on a       | $F_{OUT} \ge 100 \text{ MHz}$ | —   |     | 600                                       | ps (p-p)  |

| FOUTPJ_IO                                       | regular I/O in fractional PLL             | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

| <b>t</b> (67)(70)                               | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ |     |     | 600                                       | ps (p-p)  |

| t <sub>OUTCCJ_IO</sub> <sup>(67)(70)</sup>      | a regular I/O in integer PLL              | $F_{OUT} < 100 \text{ MHz}$   | —   | _   | 60                                        | mUI (p-p) |

| <b>t</b> (67)(68)(70)                           | Cycle-to-cycle jitter for clock output on | $F_{OUT} \ge 100 \text{ MHz}$ | _   |     | 600                                       | ps (p-p)  |

| t <sub>FOUTCCJ_IO</sub> <sup>(67)(68)(70)</sup> | a regular I/O in fractional PLL           | $F_{OUT} < 100 \text{ MHz}$   |     |     | 60                                        | mUI (p-p) |

<sup>(67)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.99999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in Memory Output Clock Jitter Specification for Arria V Devices table.

<sup>&</sup>lt;sup>(68)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>&</sup>lt;sup>(69)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>&</sup>lt;sup>(70)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in Memory Output Clock Jitter Specification for Arria V Devices table.

AV-51002 2017.02.10

| Symbol                                                                                                                                       | Condition                                                           |      | -I3, -C4 |      | –I5, –C5 |     |      | -C6  |     |      | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|----------|------|----------|-----|------|------|-----|------|------|

| Symbol                                                                                                                                       | Condition                                                           | Min  | Тур      | Max  | Min      | Тур | Max  | Min  | Тур | Max  | Unit |

|                                                                                                                                              | SERDES factor J ≥<br>8 <sup>(76)(78)</sup> , LVDS TX with<br>RX DPA | (77) |          | 1600 | (77)     |     | 1500 | (77) | _   | 1250 | Mbps |

|                                                                                                                                              | SERDES factor J = 1<br>to 2, Uses DDR<br>Registers                  | (77) |          | (79) | (77)     |     | (79) | (77) | _   | (79) | Mbps |

| Emulated Differential I/<br>O Standards with Three<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup> | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 945  | (77)     |     | 945  | (77) |     | 945  | Mbps |

| Emulated Differential I/<br>O Standards with One<br>External Output Resistor<br>Network - f <sub>HSDR</sub> (data<br>rate) <sup>(80)</sup>   | SERDES factor $J = 4$<br>to $10^{(81)}$                             | (77) |          | 200  | (77)     |     | 200  | (77) |     | 200  | Mbps |

| t <sub>x Jitter</sub> -True Differential<br>I/O Standards                                                                                    | Total Jitter for Data<br>Rate 600 Mbps – 1.25<br>Gbps               |      |          | 160  |          |     | 160  |      | _   | 160  | ps   |

|                                                                                                                                              | Total Jitter for Data<br>Rate < 600 Mbps                            |      |          | 0.1  | _        | _   | 0.1  | —    | _   | 0.1  | UI   |

$<sup>^{(78)}</sup>$  The V<sub>CC</sub> and V<sub>CCP</sub> must be on a separate power layer and a maximum load of 5 pF for chip-to-chip interface.

<sup>&</sup>lt;sup>(79)</sup> The maximum ideal data rate is the SERDES factor (J) x the PLL maximum output frequency (f<sub>OUT</sub>), provided you can close the design timing and the signal integrity simulation is clean.

<sup>&</sup>lt;sup>(80)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

<sup>&</sup>lt;sup>(81)</sup> When using True LVDS RX channels for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.

#### 1-62 SPI Timing Characteristics

| Symbol                 | Description                                       | Min | Мах | Unit |

|------------------------|---------------------------------------------------|-----|-----|------|

| T <sub>h</sub>         | SPI MISO hold time                                | 1   | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45  | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8   |     | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8   |     | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1  | 1   | ns   |

**Altera Corporation**

Arria V GX, GT, SX, and ST Device Datasheet

<sup>(86)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx\_sample\_delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

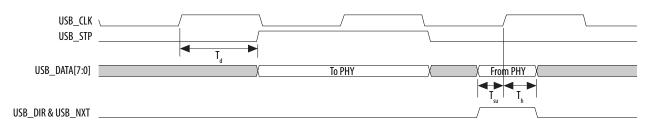

## Figure 1-12: USB Timing Diagram

## Ethernet Media Access Controller (EMAC) Timing Characteristics

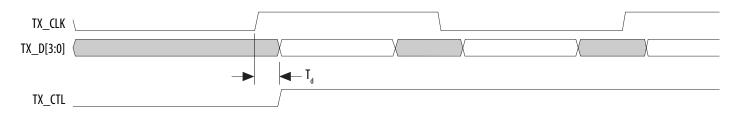

## Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | —     | 40  |      | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 |      | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    |     | 55   | %    |

| T <sub>d</sub>                | TX_CLK to TXD/TX_CTL output data delay | -0.85 |     | 0.15 | ns   |

### Figure 1-13: RGMII TX Timing Diagram

|            |             | Active Serial <sup>(108)</sup> |            |                                      | Fast Passive Parallel <sup>(109)</sup> |            |                                    |  |

|------------|-------------|--------------------------------|------------|--------------------------------------|----------------------------------------|------------|------------------------------------|--|

| Variant    | Member Code | Width                          | DCLK (MHz) | Minimum Configura-<br>tion Time (ms) | Width                                  | DCLK (MHz) | Minimum Configuration Time<br>(ms) |  |

|            | A1          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A3          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

|            | A5          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Arria V GX | A7          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia v GA | B1          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | B3          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | B5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | B7          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | C3          | 4                              | 100        | 178                                  | 16                                     | 125        | 36                                 |  |

| Arria V GT | C7          | 4                              | 100        | 255                                  | 16                                     | 125        | 51                                 |  |

| Allia v Gi | D3          | 4                              | 100        | 344                                  | 16                                     | 125        | 69                                 |  |

|            | D7          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V SX | В3          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria v SA | B5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

| Arria V ST | D3          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

|            | D5          | 4                              | 100        | 465                                  | 16                                     | 125        | 93                                 |  |

**Related Information Configuration Files** on page 1-83

(108) DCLK frequency of 100 MHz using external CLKUSR.

(109) Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

## 1-98 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.</li> <li>Updated V<sub>CC_HPS</sub> specification in Table 5.</li> <li>Added a note in Table 19: Differential inputs are powered by V<sub>CCPD</sub> which requires 2.5 V.</li> <li>Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20 and Table 21.</li> <li>Updated description in "HPS PLL Specifications" section.</li> <li>Updated VCO range maximum specification in Table 39.</li> <li>Updated T<sub>h</sub> and T<sub>h</sub> specifications in Table 45.</li> <li>Added T<sub>h</sub> specification in Table 47 and Figure 13.</li> <li>Updated a note in Figure 20, Figure 21, and Figure 23 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.</li> <li>Removed "Remote update only in AS mode" specification in Table 58.</li> <li>Added DCLK device initialization clock source specification in Table 60.</li> <li>Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.</li> <li>Removed f<sub>MAX_RU_CLK</sub> specification in Table 63.</li> </ul> |

| February 2014 | 3.7     | <ul> <li>Updated V<sub>CCRSTCLK_HPS</sub> maximum specification in Table 1.</li> <li>Added V<sub>CC_AUX_SHARED</sub> specification in Table 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| December 2013 | 3.6     | <ul> <li>Added "HPS PLL Specifications".</li> <li>Added Table 24, Table 39, and Table 40.</li> <li>Updated Table 1, Table 3, Table 5, Table 19, Table 20, Table 21, Table 38, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, Table 51, Table 55, Table 56, and Table 59.</li> <li>Updated Figure 7, Figure 13, Figure 15, Figure 16, and Figure 19.</li> <li>Removed table: GPIO Pulse Width for Arria V Devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus II software v12.0 release:</li> <li>Restructured document.</li> <li>Updated "Supply Current and Power Consumption" section.</li> <li>Updated Table 20, Table 21, Table 24, Table 25, Table 26, Table 35, Table 39, Table 43, and Table 52.</li> <li>Added Table 22, Table 23, and Table 33.</li> <li>Added Figure 1–1 and Figure 1–2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul> |

| February 2012 | 1.3     | <ul> <li>Updated Table 2–1.</li> <li>Updated Transceiver-FPGA Fabric Interface rows in Table 2–20.</li> <li>Updated V<sub>CCP</sub> description.</li> </ul>                                                                                                                                                                                                                                                                                           |

| December 2011 | 1.2     | Updated Table 2–1 and Table 2–3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2011 | 1.1     | <ul> <li>Updated Table 2–1, Table 2–19, Table 2–26, and Table 2–36.</li> <li>Added Table 2–5.</li> <li>Added Figure 2–4.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| August 2011   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

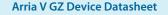

This document covers the electrical and switching characteristics for Arria V GZ devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This document also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay.

#### **Related Information**

#### Arria V Device Overview

For information regarding the densities and packages of devices in the Arria V GZ family.

# **Electrical Characteristics**

## **Operating Conditions**

When you use Arria V GZ devices, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Arria V GZ devices, you must consider the operating requirements described in this datasheet.

Arria V GZ devices are offered in commercial and industrial temperature grades.

Commercial devices are offered in -3 (fastest) and -4 core speed grades. Industrial devices are offered in -3L and -4 core speed grades. Arria V GZ devices are offered in -2 and -3 transceiver speed grades.

#### Table 2-1: Commercial and Industrial Speed Grade Offering for Arria V GZ Devices

C = Commercial temperature grade; I = Industrial temperature grade.

© 2017 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 2-2 Absolute Maximum Ratings

Lower number refers to faster speed grade.

L = Low power devices.

| Transceiver Speed Grade | Core Speed Grade |     |     |     |  |  |  |

|-------------------------|------------------|-----|-----|-----|--|--|--|

| Transceiver speeu Graue | C3               | C4  | I3L | 14  |  |  |  |

| 2                       | Yes              | _   | Yes | -   |  |  |  |

| 3                       |                  | Yes |     | Yes |  |  |  |

## **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Arria V GZ devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

**Caution:** Conditions other than those listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

#### Table 2-2: Absolute Maximum Ratings for Arria V GZ Devices

| Symbol                | Description                                                            | Minimum | Maximum | Unit |

|-----------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>       | Power supply for core voltage and periphery circuitry                  | -0.5    | 1.35    | V    |

| V <sub>CCPT</sub>     | Power supply for programmable power technology                         | -0.5    | 1.8     | V    |

| V <sub>CCPGM</sub>    | Power supply for configuration pins                                    | -0.5    | 3.9     | V    |

| V <sub>CC_AUX</sub>   | Auxiliary supply for the programmable power technology                 | -0.5    | 3.4     | V    |

| V <sub>CCBAT</sub>    | Battery back-up power supply for design security volatile key register | -0.5    | 3.9     | V    |

| V <sub>CCPD</sub>     | I/O pre-driver power supply                                            | -0.5    | 3.9     | V    |

| V <sub>CCIO</sub>     | I/O power supply                                                       | -0.5    | 3.9     | V    |

| V <sub>CCD_FPLL</sub> | PLL digital power supply                                               | -0.5    | 1.8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply                                                | -0.5    | 3.4     | V    |

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- **PowerPlay Power Analysis** ٠ For more information about PowerPlay power analysis.

#### **Power Consumption**

Altera offers two ways to estimate power consumption for a design-the Excel-based Early Power Estimator and the Quartus II PowerPlay Power Analyzer feature.

Note: You typically use the interactive Excel-based Early Power Estimator before designing the FPGA to get a magnitude estimate of the device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The PowerPlay Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- PowerPlay Early Power Estimator User Guide For more information about the EPE tool.

- PowerPlay Power Analysis For more information about PowerPlay power analysis.

#### I/O Pin Leakage Current

#### Table 2-8: I/O Pin Leakage Current for Arria V GZ Devices

If  $V_O = V_{CCIO}$  to  $V_{CCIOMax}$ , 100 µA of leakage current per I/O is expected.

| Symbol          | Description           | Conditions                     | Min | Тур | Max | Unit |

|-----------------|-----------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin             | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O<br>pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       |                        | V <sub>REF</sub> (V)     |                             | V <sub>TT</sub> (V)       |                       |                        |

|-------------------------|-------|-----------------------|-------|------------------------|--------------------------|-----------------------------|---------------------------|-----------------------|------------------------|

|                         | Min   | Тур                   | Max   | Min                    | Тур                      | Max                         | Min                       | Тур                   | Мах                    |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.418 | $0.49 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$  | $0.51 	imes V_{ m CCIO}$    | $0.49 \times V_{ m CCIO}$ | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.26  | $0.49 \times V_{CCIO}$ | $0.5 \times V_{ m CCIO}$ | $0.51 \times V_{CCIO}$      | $0.49 \times V_{ m CCIO}$ | 0.5 ×<br>VCCIO        | $0.51 \times V_{CCIO}$ |

| SSTL-12<br>Class I, II  | 1.14  | 1.20                  | 1.26  | $0.49 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$  | $0.51 \times V_{ m CCIO}$   | $0.49 \times V_{ m CCIO}$ | 0.5 ×<br>VCCIO        | $0.51 \times V_{CCIO}$ |

| HSTL-18<br>Class I, II  | 1.71  | 1.8                   | 1.89  | 0.85                   | 0.9                      | 0.95                        | _                         | V <sub>CCIO</sub> /2  | _                      |

| HSTL-15<br>Class I, II  | 1.425 | 1.5                   | 1.575 | 0.68                   | 0.75                     | 0.9                         | _                         | V <sub>CCIO</sub> /2  | _                      |

| HSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | $0.47 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$  | $0.53 \times V_{ m CCIO}$   | _                         | V <sub>CCIO</sub> /2  | _                      |

| HSUL-12                 | 1.14  | 1.2                   | 1.3   | $0.49 \times V_{CCIO}$ | $0.5 	imes V_{ m CCIO}$  | 0.51 ×<br>V <sub>CCIO</sub> | _                         | —                     | _                      |

# Table 2-18: Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Arria V GZ Devices

| I/O Standard       | V <sub>IL(D</sub> | <sub>C)</sub> (V)           | V <sub>IH(DC</sub>          | <sub>_)</sub> (V)          | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)        | l <sub>ol</sub> (mA)   | l <sub>oh</sub> (mA)              |

|--------------------|-------------------|-----------------------------|-----------------------------|----------------------------|-------------------------|-------------------------|----------------------------|----------------------------|------------------------|-----------------------------------|

|                    | Min               | Max                         | Min                         | Max                        | Мах                     | Min                     | Max                        | Min                        | י <sub>סן</sub> (וויה) | י <sub>oh</sub> (יייי <i>ב</i> י) |

| SSTL-2 Class<br>I  | -0.3              | V <sub>REF</sub> –<br>0.15  | V <sub>REF</sub> + 0.15     | V <sub>CCIO</sub><br>+ 0.3 | V <sub>REF</sub> – 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> –<br>0.608 | V <sub>TT</sub><br>+ 0.608 | 8.1                    | -8.1                              |

| SSTL-2 Class<br>II | -0.3              | V <sub>REF</sub> –<br>0.15  | V <sub>REF</sub> + 0.15     | V <sub>CCIO</sub><br>+ 0.3 | V <sub>REF</sub> – 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     | 16.2                   | -16.2                             |

| SSTL-18<br>Class I | -0.3              | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub><br>+ 0.125 | V <sub>CCIO</sub><br>+ 0.3 | V <sub>REF</sub> – 0.25 | V <sub>REF</sub> + 0.25 | V <sub>TT</sub> -<br>0.603 | V <sub>TT</sub><br>+ 0.603 | 6.7                    | -6.7                              |

| Symbol/Description                                 | Conditions              | Transceiver Speed Grade 2 |               |     | Transc | Unit          |     |      |

|----------------------------------------------------|-------------------------|---------------------------|---------------|-----|--------|---------------|-----|------|

| Symbol/Description                                 |                         | Min                       | Тур           | Max | Min    | Тур           | Max | Onit |

| fixedclk clock frequency                           | PCIe<br>Receiver Detect | -                         | 100 or<br>125 | _   | _      | 100 or<br>125 | —   | MHz  |

| Reconfiguration clock (mgmt_clk_<br>clk) frequency | —                       | 100                       | _             | 125 | 100    | _             | 125 | MHz  |

#### **Related Information**

#### Arria V Device Overview

For more information about device ordering codes.

## Receiver

## Table 2-24: Receiver Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

| Symbol/Description                                           | Conditions                                           | Transceiver Speed Grade 2 |     |       | Transc | Unit |         |      |

|--------------------------------------------------------------|------------------------------------------------------|---------------------------|-----|-------|--------|------|---------|------|

| Symbol/Description                                           | Conditions                                           | Min                       | Тур | Мах   | Min    | Тур  | Мах     |      |

| Supported I/O Standards                                      | 1.4-V PCML, 1.5-V PCML, 2.5-V PCML, LVPECL, and LVDS |                           |     |       |        |      |         |      |

| Data rate (Standard PCS) <sup>(143)</sup> , <sup>(144)</sup> | —                                                    | 600                       | _   | 9900  | 600    | _    | 8800    | Mbps |

| Data rate (10G PCS) (143), (144)                             | _                                                    | 600                       |     | 12500 | 600    | _    | 10312.5 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin $^{(145)}$             | —                                                    | _                         |     | 1.2   | _      | _    | 1.2     | V    |

| Absolute $\mathrm{V}_{\mathrm{MIN}}$ for a receiver pin      | _                                                    | -0.4                      |     |       | -0.4   | _    |         | V    |

<sup>&</sup>lt;sup>(143)</sup> The line data rate may be limited by PCS-FPGA interface speed grade.

<sup>(144)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>&</sup>lt;sup>(145)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

#### 2-44 Periphery Performance

| Description           | Min   | Тур   | Max   | Unit |

|-----------------------|-------|-------|-------|------|

| Diode ideality factor | 1.006 | 1.008 | 1.010 | —    |

# **Periphery Performance**

I/O performance supports several system interfaces, such as the **LVDS** high-speed I/O interface, external memory interface, and the **PCI/PCI-X** bus interface. General-purpose I/O standards such as 3.3-, 2.5-, 1.8-, and 1.5-**LVTTL/LVCMOS** are capable of a typical 167 MHz and 1.2-**LVCMOS** at 100 MHz interfacing frequency with a 10 pF load.

**Note:** The actual achievable frequency depends on design- and system-specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## High-Speed I/O Specification

**High-Speed Clock Specifications**

#### Table 2-39: High-Speed Clock Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

Arria V GZ devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 230 Mbps

- True mini-LVDS output standard with data rates of up to 340 Mbps

## FPP Configuration Timing when DCLK to DATA[] > 1

## Figure 2-8: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1,

t<sub>CF2ST1</sub> tcfg ;↔ nCONFIG ŤĊF2CK nSTATUS (3) 🕳 tstatus tCF2ST0 CONF\_DONE (4) TCL tCH tsT2CK ŤĊF2CD (8) DCLK (6) (7) 1 2 ••• r 2 ••• r 1  $\mathbf{D}$ (5) tCLK DATA[31..0] (8) Word 0 Word User Mode Word 3 • • • Word (n-1) tDH tDH tpsy High-Z User I/O User Mode INIT DONE (9) tCD2UM

Timing when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. To find out the DCLK-to-DATA[] ratio for your system, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 2. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 3. After power-up, the Arria V GZ device holds nSTATUS low for the time as specified by the POR delay.

- 4. After power-up, before and during configuration, CONF\_DONE is low.

- 5. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 6. "r" denotes the DCLK-to-DATA[] ratio. For the DCLK-to-DATA[] ratio based on the decompression and the design security feature enable settings, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 7. If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA[31.0] pins prior to sending the first DCLK rising edge.

- 8. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 9. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

| Symbol              | Parameter                                         | Minimum                                        | Maximum | Unit |

|---------------------|---------------------------------------------------|------------------------------------------------|---------|------|

| t <sub>CO</sub>     | DCLK falling edge to AS_DATA0/ASDO output         |                                                | 4       | ns   |

| t <sub>SU</sub>     | Data setup time before falling edge on DCLK       | 1.5                                            | —       | ns   |

| t <sub>H</sub>      | Data hold time after falling edge on DCLK         | 0                                              | —       | ns   |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (216)                 | 175                                            | 437     | μs   |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period          | _       | _    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × Clkusr<br>period) | _       | _    |

## Table 2-59: DCLK Frequency Specification in the AS Configuration Scheme

This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

The AS multi-device configuration scheme does not support  ${\tt DCLK}$  frequency of 100 MHz.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

## **Related Information**

- Passive Serial Configuration Timing on page 2-67

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(216)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

#### **Related Information**

Configuration, Design Security, and Remote System Upgrades in Arria V Devices

# Initialization

## Table 2-61: Initialization Clock Source Option and the Maximum Frequency for Arria V GZ Devices

| Initialization Clock Source | Configuration Schemes | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|-----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, FPP           | 12.5                    |                                |

| CLKUSR <sup>(222)</sup>     | PS, FPP               | 125                     | 8576                           |

|                             | AS                    | 100                     |                                |

| DCLK                        | PS, FPP               | 125                     |                                |

# **Configuration Files**

Use the following table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Quartus II software. However, for a specific version of the Quartus II software, any design targeted for the same device has the same uncompressed configuration file size.

Arria V GZ Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(221)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>(222)</sup> To enable CLKUSR as the initialization clock source, turn on the Enable user-supplied start-up clock (CLKUSR) option in the Quartus II software from the General panel of the Device and Pin Options dialog box.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| June 2016     | 2016.06.20 | <ul> <li>Changed column heading from "Value" to "Maximum" in the "Pin Capacitance for Arria V GZ Devices" table.</li> <li>Changed the minimum supported data rate range values from "1000" to "2000" in the "ATX PLL Specifications for Arria V GZ Devices" table.</li> <li>Added the supported data rates for the following output standards using true LVDS output buffer types in the "High-Speed Clock Specifications for Arria V GZ Devices" table:</li> <li>True RSDS output standard: data rates of up to 230 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 340 Mbps</li> </ul> |  |

| December 2015 | 2015.12.16 | <ul> <li>Removed the CDR ppm tolerance specification from the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Removed transmitter rise and fall time specifications from the "Transmitter Specifications for Arria V GZ Devices" table.</li> <li>Changed the .rbf sizes in the "Uncompressed .rbf Sizes for Arria V GZ Devices" table.</li> <li>Added a footnote to the "Transmitter High-Speed I/O Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                              |  |

| June 2015     | 2015.06.16 | <ul> <li>Changed the conditions for the reference clock rise and fall time and added a note to the condition in the<br/>"Reference Clock Specifications for Arria V GZ Devices" table.</li> <li>Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the<br/>"Receiver Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                           |  |

| January 2015  | 2015.01.30 | <ul> <li>Added 240-Ω to the "OCT Calibration Accuracy Specifications for Arria V GZ Devices" table.</li> <li>Changed the CDR PPM tolerance spec in the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Added additional max data rate for fPLL in the "Fractional PLL Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                                            |  |