# E·XFL

#### Intel - 5AGZME3H2F35C3N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 16980                                                      |

| Number of Logic Elements/Cells | 360000                                                     |

| Total RAM Bits                 | 23946240                                                   |

| Number of I/O                  | 414                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA                                           |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agzme3h2f35c3n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### I/O Pin Leakage Current

## Table 1-6: I/O Pin Leakage Current for Arria V Devices

| Symbol          | Description        | Condition                      | Min | Тур | Max | Unit |

|-----------------|--------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin          | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

## **Bus Hold Specifications**

#### Table 1-7: Bus Hold Parameters for Arria V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

|                                             |                   |                                                             |     | V <sub>CCIO</sub> (V) |     |      |     |      |     |      |     |      |     |      |      |

|---------------------------------------------|-------------------|-------------------------------------------------------------|-----|-----------------------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                                   | 1   | .2                    | 1   | .5   | 1   | .8   | 2   | .5   | 3   | .0   | 3.  | .3   | Unit |

|                                             |                   |                                                             | Min | Max                   | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max)                  | 8   |                       | 12  |      | 30  |      | 50  |      | 70  |      | 70  | _    | μΑ   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min)                  | -8  |                       | -12 |      | -30 |      | -50 |      | -70 |      | -70 | _    | μΑ   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{IN} \\ < V_{CCIO} \end{array}$ | _   | 125                   |     | 175  | _   | 200  |     | 300  | _   | 500  |     | 500  | μΑ   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub>               | _   | -125                  |     | -175 |     | -200 | _   | -300 |     | -500 |     | -500 | μΑ   |

Arria V GX, GT, SX, and ST Device Datasheet

| I/O Standard        | V <sub>IL</sub> | <sub>.(DC)</sub> (V)    | V <sub>IH(D</sub>       | V <sub>IH(DC)</sub> (V)  |                         | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)     | I <sub>OL</sub> <sup>(14)</sup> | I <sub>OH</sub> <sup>(14)</sup> (mA) |

|---------------------|-----------------|-------------------------|-------------------------|--------------------------|-------------------------|-------------------------|------------------------|-------------------------|---------------------------------|--------------------------------------|

|                     | Min             | Max                     | Min                     | Max                      | Max                     | Min                     | Max                    | Min                     | (mA)                            | ·OH (                                |

| HSTL-15<br>Class II | —               | V <sub>REF</sub> – 0.1  | $V_{REF} + 0.1$         | —                        | V <sub>REF</sub> – 0.2  | $V_{REF} + 0.2$         | 0.4                    | V <sub>CCIO</sub> – 0.4 | 16                              | -16                                  |

| HSTL-12<br>Class I  | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 8                               | -8                                   |

| HSTL-12<br>Class II | -0.15           | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> – 0.15 | V <sub>REF</sub> + 0.15 | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 16                              | -16                                  |

| HSUL-12             | —               | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> – 0.22 | $V_{REF} + 0.22$        | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$   |                                 | _                                    |

## **Differential SSTL I/O Standards**

Table 1-17: Differential SSTL I/O Standards for Arria V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) |       | V <sub>SW</sub> | <sub>ING(DC)</sub> (V) | V <sub>X(AC)</sub> (V)          |                      |                                 | V <sub>SWING(AC)</sub> (V)                    |                           |  |

|------------------------|-------|-----------------------|-------|-----------------|------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|--|

|                        | Min   | Тур                   | Max   | Min             | Мах                    | Min                             | Тур                  | Мах                             | Min                                           | Max                       |  |

| SSTL-2<br>Class I, II  | 2.375 | 2.5                   | 2.625 | 0.3             | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 – 0.2      | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |  |

| SSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.25            | $V_{CCIO} + 0.6$       | V <sub>CCIO</sub> /2 –<br>0.175 | _                    | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | $V_{CCIO} + 0.6$          |  |

| SSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2             | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | —                    | V <sub>CCIO</sub> /2<br>+ 0.15  | $2(V_{IH(AC)} - V_{REF})$                     | $2(V_{IL(AC)} - V_{REF})$ |  |

| SSTL-135               | 1.283 | 1.35                  | 1.45  | 0.18            | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |  |

<sup>&</sup>lt;sup>(14)</sup> To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

$<sup>^{(15)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

| I/O Standard                       |                                                                                                                                                                                                                                                                                                                              | V <sub>CCIO</sub> (V) | )     |     | V <sub>ID</sub> (mV) <sup>(16)</sup> |     |       | $V_{ICM(DC)}(V)$                |       | V <sub>OD</sub> (V) <sup>(17)</sup> |     | ١   | V <sub>OCM</sub> (V) <sup>(17)(18)</sup> |      |       |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----|--------------------------------------|-----|-------|---------------------------------|-------|-------------------------------------|-----|-----|------------------------------------------|------|-------|

|                                    | Min                                                                                                                                                                                                                                                                                                                          | Тур                   | Мах   | Min | Condition                            | Мах | Min   | Condition                       | Мах   | Min                                 | Тур | Max | Min                                      | Тур  | Max   |

| PCML                               | Transmitter, receiver, and input reference clock pins of high-speed transceivers use the PCML I/O standard. For transmitter, receiver, a<br>reference clock I/O pin specifications, refer to Transceiver Specifications for Arria V GX and SX Devices and Transceiver Specification<br>for Arria V GT and ST Devices tables. |                       |       |     |                                      |     |       |                                 |       |                                     |     |     |                                          |      |       |

| 2.5 V                              | 2.375                                                                                                                                                                                                                                                                                                                        | 2.5                   | 2.625 | 100 | V <sub>CM</sub> =                    |     | 0.05  | D <sub>MAX</sub> ≤<br>1.25 Gbps | 1.80  | 0.247                               |     | 0.6 | 1.125                                    | 1.25 | 1.375 |

| LVDS <sup>(19)</sup>               | 2.375                                                                                                                                                                                                                                                                                                                        | 2.3                   | 2.023 | 100 | 1.25 V                               |     | 1.05  | D <sub>MAX</sub> ><br>1.25 Gbps | 1.55  | 0.247                               |     | 0.0 | 1.125                                    | 1.25 | 1.575 |

| RSDS<br>(HIO) <sup>(20)</sup>      | 2.375                                                                                                                                                                                                                                                                                                                        | 2.5                   | 2.625 | 100 | V <sub>CM</sub> =<br>1.25 V          |     | 0.25  |                                 | 1.45  | 0.1                                 | 0.2 | 0.6 | 0.5                                      | 1.2  | 1.4   |

| Mini-LVDS<br>(HIO) <sup>(21)</sup> | 2.375                                                                                                                                                                                                                                                                                                                        | 2.5                   | 2.625 | 200 |                                      | 600 | 0.300 |                                 | 1.425 | 0.25                                | _   | 0.6 | 1                                        | 1.2  | 1.4   |

| LVPECL <sup>(22)</sup>             |                                                                                                                                                                                                                                                                                                                              |                       |       | 300 |                                      |     | 0.60  | D <sub>MAX</sub> ≤<br>700 Mbps  | 1.80  |                                     |     |     |                                          |      |       |

|                                    |                                                                                                                                                                                                                                                                                                                              | _                     |       | 500 |                                      |     | 1.00  | D <sub>MAX</sub> ><br>700 Mbps  | 1.60  |                                     | _   |     |                                          |      |       |

- Transceiver Specifications for Arria V GX and SX Devices on page 1-23 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

- $^{(16)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

- <sup>(17)</sup>  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

- <sup>(18)</sup> This applies to default pre-emphasis setting only.

- <sup>(19)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 1.25 Gbps and 0 V to 1.85 V for data rates below 1.25 Gbps.

- <sup>(20)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(21)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.425 V.

- <sup>(22)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

#### Table 1-21: Transceiver Clocks Specifications for Arria V GX and SX Devices

| Symbol/Description                                                                | Condition            | Transceiver Speed Grade 4 |     |     | Transc | Unit |     |      |  |

|-----------------------------------------------------------------------------------|----------------------|---------------------------|-----|-----|--------|------|-----|------|--|

| Symbol/Description                                                                | Condition            | Min                       | Тур | Мах | Min    | Тур  | Max | onic |  |

| fixedclk clock frequency                                                          | PCIe Receiver Detect | —                         | 125 | —   | —      | 125  | _   | MHz  |  |

| Transceiver Reconfigura-<br>tion Controller IP (mgmt_<br>clk_clk) clock frequency | —                    | 75                        | _   | 125 | 75     | _    | 125 | MHz  |  |

## Table 1-22: Receiver Specifications for Arria V GX and SX Devices

| Symbol/Deceription                                                                                              | Condition | Transc | eiver Speed G | irade 4     | Transc     | Unit   |      |      |

|-----------------------------------------------------------------------------------------------------------------|-----------|--------|---------------|-------------|------------|--------|------|------|

| Symbol/Description                                                                                              | Condition | Min    | Тур           | Max         | Min        | Тур    | Max  | Onit |

| Supported I/O standards                                                                                         |           | ]      | 1.5 V PCML,   | 2.5 V PCML, | LVPECL, an | d LVDS |      |      |

| Data rate <sup>(28)</sup>                                                                                       | _         | 611    | _             | 6553.6      | 611        | _      | 3125 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(29)</sup>                                                           | _         |        | _             | 1.2         | _          | _      | 1.2  | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                    | _         | -0.4   | _             | _           | -0.4       | _      | _    | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | _         |        |               | 1.6         |            |        | 1.6  | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) after device<br>configuration  | _         |        |               | 2.2         |            |        | 2.2  | V    |

<sup>&</sup>lt;sup>(28)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(29)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | de 3 | Unit |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|------|

| Symbol/Description                                                          | Condition                                                   | Min  | Тур               | Max  | Ont  |

|                                                                             | 85-Ω setting                                                | —    | 85                | —    | Ω    |

| Differential on-chip termination                                            | 100- $\Omega$ setting                                       |      | 100               |      | Ω    |

| resistors                                                                   | 120-Ω setting                                               | —    | 120               | —    | Ω    |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω    |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps   |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps   |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps   |

## Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |

|---------------------------|---------------|--------------|------|

| Symbol/Description        | Min           | Max          | Onit |

| Supported data range      | 0.611         | 10.3125      | Gbps |

| fPLL supported data range | 611           | 3125         | Mbps |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

#### Table 1-31: Transceiver-FPGA Fabric Interface Specifications for Arria V GT and ST Devices

| Symbol/Description                  | Transceiver S | peed Grade 3                                | Unit |

|-------------------------------------|---------------|---------------------------------------------|------|

| Symbol/Description                  | Min           | Мах                                         | Unit |

| Interface speed (PMA direct mode)   | 50            | 153.6 <sup>(56)</sup> , 161 <sup>(57)</sup> | MHz  |

| Interface speed (single-width mode) | 25            | 187.5                                       | MHz  |

| Interface speed (double-width mode) | 25            | 163.84                                      | MHz  |

**Related Information**

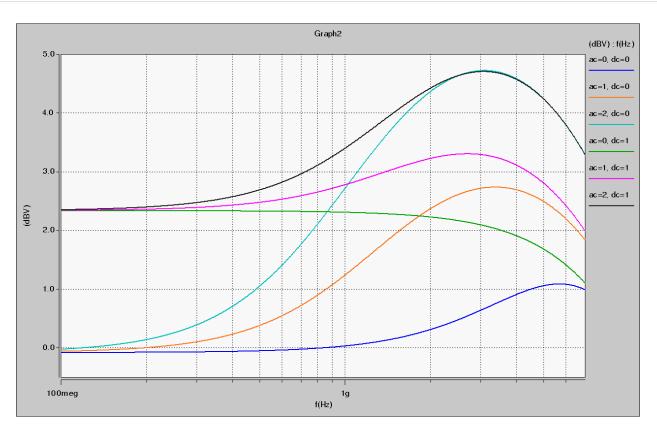

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

<sup>&</sup>lt;sup>(56)</sup> The maximum frequency when core transceiver local routing is selected.

<sup>&</sup>lt;sup>(57)</sup> The maximum frequency when core transceiver network routing (GCLK, RCLK, or PCLK) is selected.

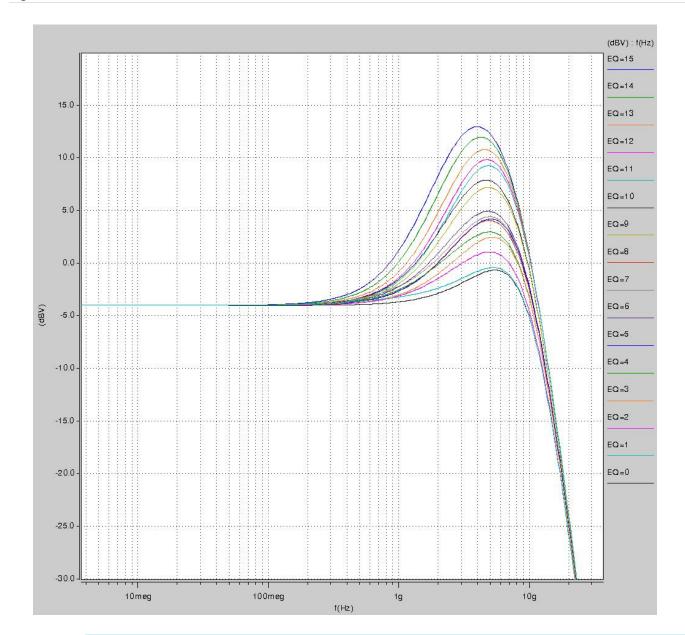

## CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-2: Continuous Time-Linear Equalizer (CTLE) Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Arria V GX, GT, SX, and ST Device Datasheet

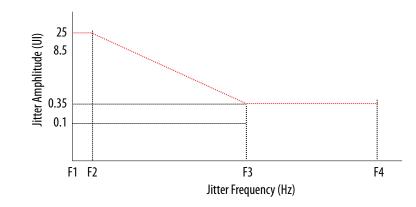

## LVDS Soft-CDR/DPA Sinusoidal Jitter Tolerance Specifications

#### Table 1-42: LVDS Soft-CDR/DPA Sinusoidal Jitter Mask Values for a Data Rate Equal to 1.25 Gbps

| Jitter Freq | uency (Hz) | Sinusoidal Jitter (UI) |

|-------------|------------|------------------------|

| F1          | 10,000     | 25.000                 |

| F2          | 17,565     | 25.000                 |

| F3          | 1,493,000  | 0.350                  |

| F4          | 50,000,000 | 0.350                  |

## **DLL Frequency Range Specifications**

#### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

## DQS Logic Block Specifications

## Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

#### **HPS PLL Input Jitter**

Use the following equation to determine the maximum input jitter (peak-to-peak) the HPS PLLs can tolerate. The divide value (N) is the value programmed into the denominator field of the VCO register for each PLL. The PLL input reference clock is divided by this value. The range of the denominator is 1 to 64.

Maximum input jitter = Input clock period × Divide value (N) × 0.02

## Table 1-50: Examples of Maximum Input Jitter

| Input Reference Clock Period | Divide Value (N) | Maximum Jitter | Unit |

|------------------------------|------------------|----------------|------|

| 40 ns                        | 1                | 0.8            | ns   |

| 40 ns                        | 2                | 1.6            | ns   |

| 40 ns                        | 4                | 3.2            | ns   |

## **Quad SPI Flash Timing Characteristics**

## Table 1-51: Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Arria V Devices

| Symbol                 | Description                                        | Min  | Тур                      | Мах                                                  | Unit |

|------------------------|----------------------------------------------------|------|--------------------------|------------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | —    | _                        | 108                                                  | MHz  |

| T <sub>qspi_clk</sub>  | QSPI_CLK clock period (Internal reference clock)   | 2.32 | _                        |                                                      | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45   |                          | 55                                                   | %    |

| T <sub>dssfrst</sub>   | Output delay QSPI_SS valid before first clock edge |      | 1/2 cycle of<br>SCLK_OUT |                                                      | ns   |

| T <sub>dsslst</sub>    | Output delay QSPI_SS valid after last clock edge   | -1   |                          | 1                                                    | ns   |

| T <sub>dio</sub>       | I/O data output delay                              | -1   |                          | 1                                                    | ns   |

| T <sub>din_start</sub> | Input data valid start                             |      |                          | $(2 + R_{delay}) \times T_{qspi\_clk} - 7.52^{(85)}$ | ns   |

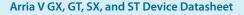

#### Figure 1-11: SD/MMC Timing Diagram

#### **Related Information**

**Booting and Configuration Chapter, Arria V Hard Processor System Technical Reference Manual** Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

#### **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

#### Table 1-55: USB Timing Requirements for Arria V Devices

| Symbol           | Description                                  | Min | Тур   | Мах | Unit |

|------------------|----------------------------------------------|-----|-------|-----|------|

| T <sub>clk</sub> | USB CLK clock period                         | _   | 16.67 | _   | ns   |

| T <sub>d</sub>   | CLK to USB_STP/USB_DATA[7:0] output delay    | 4.4 | —     | 11  | ns   |

| T <sub>su</sub>  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0] | 2   | _     |     | ns   |

| T <sub>h</sub>   | Hold time for USB_DIR/USB_NXT/USB_DATA[7:0]  | 1   | —     |     | ns   |

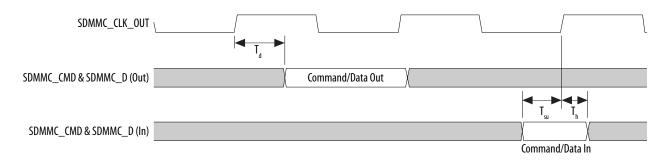

## Figure 1-18: NAND Address Latch Timing Diagram

| Symbol                            | Description                                                              | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-----------------------------------|--------------------------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| V <sub>CCPT</sub>                 | Power supply for programmable power technology                           | _         | 1.45                     | 1.50    | 1.55                     | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply for the programmable power technology                   | _         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCPD</sub> <sup>(116</sup> | I/O pre-driver (3.0 V) power supply                                      |           | 2.85                     | 3.0     | 3.15                     | V    |

| )                                 | I/O pre-driver (2.5 V) power supply                                      |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (3.0 V) power supply                                         | _         | 2.85                     | 3.0     | 3.15                     | V    |

|                                   | I/O buffers (2.5 V) power supply                                         |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (1.8 V) power supply                                         |           | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCIO</sub>                 | I/O buffers (1.5 V) power supply                                         | _         | 1.425                    | 1.5     | 1.575                    | V    |

|                                   | I/O buffers (1.35 V) power supply                                        | _         | 1.283                    | 1.35    | 1.45                     | V    |

|                                   | I/O buffers (1.25 V) power supply                                        | _         | 1.19                     | 1.25    | 1.31                     | V    |

|                                   | I/O buffers (1.2 V) power supply                                         | _         | 1.14                     | 1.2     | 1.26                     | V    |

|                                   | Configuration pins (3.0 V) power supply                                  | _         | 2.85                     | 3.0     | 3.15                     | V    |

| V <sub>CCPGM</sub>                | Configuration pins (2.5 V) power supply                                  | _         | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | Configuration pins (1.8 V) power supply                                  | _         | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCA</sub> _                | PLL analog voltage regulator power supply                                | _         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCD</sub><br>FPLL          | PLL digital voltage regulator power supply                               | _         | 1.45                     | 1.5     | 1.55                     | V    |

| V <sub>CCBAT</sub> (117           | Battery back-up power supply (For design security volatile key register) | _         | 1.2                      | —       | 3.0                      | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements.

Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(116)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.

<sup>(117)</sup> If you do not use the design security feature in Arria V GZ devices, connect V<sub>CCBAT</sub> to a 1.2- to 3.0-V power supply. Arria V GZ power-on-reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V GZ devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

AV-51002 2017.02.10

| I/O Standard            | V <sub>IL(D</sub> | <sub>C)</sub> (V)           | V <sub>IH(D0</sub>          | <sub>_)</sub> (V)           | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)         | L (m A)              | I (m A)              |

|-------------------------|-------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------|--------------------------|----------------------------|-----------------------------|----------------------|----------------------|

| I/O Standard            | Min               | Max                         | Min                         | Max                         | Max                      | Min                      | Max                        | Min                         | l <sub>ol</sub> (mA) | l <sub>oh</sub> (mA) |

| SSTL-18<br>Class II     | -0.3              | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub><br>+ 0.125 | V <sub>CCIO</sub><br>+ 0.3  | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | 0.28                       | V <sub>CCIO</sub> –<br>0.28 | 13.4                 | -13.4                |

| SSTL-15<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{ m CCIO}$   | $0.8 \times V_{ m CCIO}$    | 8                    | -8                   |

| SSTL-15<br>Class II     | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | —                           | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{\rm CCIO}$  | $0.8 \times V_{ m CCIO}$    | 16                   | -16                  |

| SSTL-135<br>Class I, II |                   | V <sub>REF</sub> –<br>0.09  | V <sub>REF</sub> + 0.09     | _                           | V <sub>REF</sub> – 0.16  | V <sub>REF</sub> + 0.16  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | —                    |

| SSTL-125<br>Class I, II | _                 | V <sub>REF</sub> –<br>0.85  | V <sub>REF</sub> + 0.85     | —                           | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | —                    |

| SSTL-12<br>Class I, II  | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | _                    |

| HSTL-18<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 8                    | -8                   |

| HSTL-18<br>Class II     |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 16                   | -16                  |

| HSTL-15<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 8                    | -8                   |

| HSTL-15<br>Class II     | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 16                   | -16                  |

| HSTL-12<br>Class I      | -0.15             | V <sub>REF</sub> –<br>0.08  | V <sub>REF</sub> + 0.08     | V <sub>CCIO</sub><br>+ 0.15 | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{\rm CCIO}$ | $0.75 \times V_{ m CCIO}$   | 8                    | -8                   |

| HSTL-12<br>Class II     | -0.15             | V <sub>REF</sub> –<br>0.08  | V <sub>REF</sub> + 0.08     | V <sub>CCIO</sub><br>+ 0.15 | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{\rm CCIO}$ | $0.75 \times V_{ m CCIO}$   | 16                   | -16                  |

| HSUL-12                 | —                 | V <sub>REF</sub> –<br>0.13  | V <sub>REF</sub> + 0.13     | —                           | V <sub>REF</sub> – 0.22  | V <sub>REF</sub> + 0.22  | $0.1 \times V_{\rm CCIO}$  | $0.9 \times V_{ m CCIO}$    | —                    | —                    |

Arria V GZ Device Datasheet

| Symbol/Description                          | Conditions                | Transceiver Speed Grade 2 |     |       | Transc | Unit |         |      |

|---------------------------------------------|---------------------------|---------------------------|-----|-------|--------|------|---------|------|

| Symbol/Description                          | Conditions                | Min                       | Тур | Max   | Min    | Тур  | Max     | Onit |

|                                             | VCO post-divider<br>L = 2 | 8000                      |     | 12500 | 8000   | _    | 10312.5 | Mbps |

| Supported data rate range                   | L = 4                     | 4000                      |     | 6600  | 4000   |      | 6600    | Mbps |

|                                             | $L = 8^{(155)}$           | 2000                      |     | 3300  | 2000   | _    | 3300    | Mbps |

| t <sub>pll_powerdown</sub> <sup>(156)</sup> | _                         | 1                         |     |       | 1      |      |         | μs   |

| t <sub>pll_lock</sub> <sup>(157)</sup>      | _                         |                           |     | 10    |        |      | 10      | μs   |

- Arria V Device Overview For more information about device ordering codes.

- Transceiver Clocking in Arria V Devices For more information about clocking ATX PLLs.

- **Dynamic Reconfiguration in Arria V Devices** For more information about reconfiguring ATX PLLs.

## **Fractional PLL**

## Table 2-28: Fractional PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the *Arria V Device Overview*.

<sup>(155)</sup> This clock can be further divided by central or local clock dividers making it possible to use ATX PLL for data rates < 1 Gbps. For more information about ATX PLLs, refer to the Transceiver Clocking in Arria V Devices chapter and the Dynamic Reconfiguration in Arria V Devices chapter.

$t_{pll_powerdown}$  is the PLL powerdown minimum pulse width.

<sup>(157)</sup>  $t_{pll \ lock}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

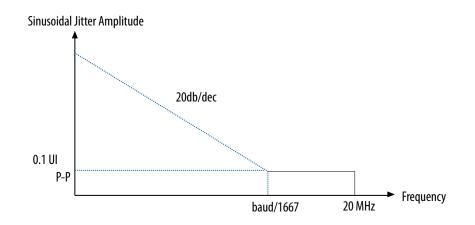

## Figure 2-2: AC Gain Curves for Arria V GZ Channels (full bandwidth)

| Symbol             | Parameter                                                     | Min    | Тур     | Мах        | Unit |

|--------------------|---------------------------------------------------------------|--------|---------|------------|------|

| k <sub>VALUE</sub> | Numerator of Fraction                                         | 128    | 8388608 | 2147483648 | _    |

| f <sub>RES</sub>   | Resolution of VCO frequency ( $f_{INPFD} = 100 \text{ MHz}$ ) | 390625 | 5.96    | 0.023      | Hz   |

- Duty Cycle Distortion (DCD) Specifications on page 2-56

- DLL Range Specifications on page 2-53

## **DSP Block Specifications**

## Table 2-35: DSP Block Performance Specifications for Arria V GZ Devices

| Mode                                                           | Performar |     | Unit |      |

|----------------------------------------------------------------|-----------|-----|------|------|

| mode                                                           | C3, I3L   | C4  | 14   | Onic |

| Modes using One DSP Block                                      |           |     |      |      |

| Three 9 × 9                                                    | 480       | 42  | 20   | MHz  |

| One 18 × 18                                                    | 480       | 420 | 400  | MHz  |

| Two partial $18 \times 18$ (or $16 \times 16$ )                | 480       | 420 | 400  | MHz  |

| One 27 × 27                                                    | 400       | 35  | 50   | MHz  |

| One 36 × 18                                                    | 400       | 35  | 350  |      |

| One sum of two $18 \times 18$ (One sum of two $16 \times 16$ ) | 400       | 35  | 50   | MHz  |

| One sum of square                                              | 400       | 35  | 50   | MHz  |

| One $18 \times 18$ plus $36 (a \times b) + c$                  | 400       | 350 |      | MHz  |

| Modes using Two DSP Blocks                                     | ·         |     |      |      |

| Three 18 × 18                                                  | 400       | 35  | 50   | MHz  |

| One sum of four 18 × 18                                        | 380       | 300 |      | MHz  |

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reconfiguration input for the ALTREMOTE\_UPDATE IP core, refer to the "User Watchdog Timer" section.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices For more information about the reset\_timer input for the ALTREMOTE\_UPDATE IP core, refer to the "Remote System Upgrade State Machine" section.

## User Watchdog Internal Oscillator Frequency Specification

#### Table 2-65: User Watchdog Internal Oscillator Frequency Specifications

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

## I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O Timing and the Quartus II Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Quartus II Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete placeand-route.

#### **Related Information**

## **Arria V Devices Documentation page**

For the Excel-based I/O Timing spreadsheet

#### Arria V GZ Device Datasheet

<sup>&</sup>lt;sup>(226)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "Remote System Upgrade State Machine" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

<sup>&</sup>lt;sup>(227)</sup> This is equivalent to strobing the reset\_timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification. For more information, refer to the "User Watchdog Timer" section in the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2016     | 2016.06.20 | <ul> <li>Changed column heading from "Value" to "Maximum" in the "Pin Capacitance for Arria V GZ Devices" table.</li> <li>Changed the minimum supported data rate range values from "1000" to "2000" in the "ATX PLL Specifications for Arria V GZ Devices" table.</li> <li>Added the supported data rates for the following output standards using true LVDS output buffer types in the "High-Speed Clock Specifications for Arria V GZ Devices" table:</li> <li>True RSDS output standard: data rates of up to 230 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 340 Mbps</li> </ul> |

| December 2015 | 2015.12.16 | <ul> <li>Removed the CDR ppm tolerance specification from the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Removed transmitter rise and fall time specifications from the "Transmitter Specifications for Arria V GZ Devices" table.</li> <li>Changed the .rbf sizes in the "Uncompressed .rbf Sizes for Arria V GZ Devices" table.</li> <li>Added a footnote to the "Transmitter High-Speed I/O Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                              |

| June 2015     | 2015.06.16 | <ul> <li>Changed the conditions for the reference clock rise and fall time and added a note to the condition in the<br/>"Reference Clock Specifications for Arria V GZ Devices" table.</li> <li>Added a note to the "Minimum differential eye opening at receiver serial input pins" specification in the<br/>"Receiver Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                           |

| January 2015  | 2015.01.30 | <ul> <li>Added 240-Ω to the "OCT Calibration Accuracy Specifications for Arria V GZ Devices" table.</li> <li>Changed the CDR PPM tolerance spec in the "Receiver Specifications for Arria V GZ Devices" table.</li> <li>Added additional max data rate for fPLL in the "Fractional PLL Specifications for Arria V GZ Devices" table.</li> </ul>                                                                                                                                                                                                                                                            |