# E·XFL

#### Intel - 5AGZME3H3F35C4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Obsolete                                                   |

|--------------------------------|------------------------------------------------------------|

| Number of LABs/CLBs            | 16980                                                      |

| Number of Logic Elements/Cells | 360000                                                     |

| Total RAM Bits                 | 23946240                                                   |

| Number of I/O                  | 414                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA                                           |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agzme3h3f35c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Transceiver Specifications for Arria V GT and ST Devices on page 1-29 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

# Switching Characteristics

This section provides performance characteristics of Arria V core and periphery blocks.

# **Transceiver Performance Specifications**

## Transceiver Specifications for Arria V GX and SX Devices

#### Table 1-20: Reference Clock Specifications for Arria V GX and SX Devices

| Symbol/Description                        | Condition                                                             | Transceiver Speed Grade 4 |               | Transc                        | irade 6        | Unit                       |                               |      |

|-------------------------------------------|-----------------------------------------------------------------------|---------------------------|---------------|-------------------------------|----------------|----------------------------|-------------------------------|------|

| Symbol/Description                        | Condition                                                             | Min                       | Тур           | Max                           | Min            | Тур                        | Max                           | onic |

| Supported I/O standards                   | 1.2 V PCM                                                             | L, 1.4 V PCN              | IL,1.5 V PCML | , 2.5 V PCMI                  | L, Differentia | l LVPECL <sup>(23)</sup> , | HCSL, and                     | LVDS |

| Input frequency from<br>REFCLK input pins | _                                                                     | 27                        |               | 710                           | 27             |                            | 710                           | MHz  |

| Rise time                                 | Measure at ±60 mV of differential signal <sup>(24)</sup>              |                           |               | 400                           |                |                            | 400                           | ps   |

| Fall time                                 | Measure at $\pm 60 \text{ mV}$ of differential signal <sup>(24)</sup> | _                         |               | 400                           |                |                            | 400                           | ps   |

| Duty cycle                                |                                                                       | 45                        | —             | 55                            | 45             | _                          | 55                            | %    |

| Peak-to-peak differential input voltage   | _                                                                     | 200                       | _             | 300 <sup>(25)</sup> /<br>2000 | 200            |                            | 300 <sup>(25)</sup> /<br>2000 | mV   |

<sup>&</sup>lt;sup>(23)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

REFCLK performance requires to meet transmitter REFCLK phase noise specification. (24)

<sup>&</sup>lt;sup>(25)</sup> The maximum peak-to peak differential input voltage of 300 mV is allowed for DC coupled link.

| Sumbol/Decovintion                                                                       | Condition                     | Transc                                        | eiver Speed G                    | irade 4 | Transc | eiver Speed G                    | Grade 6 | Unit |

|------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------|----------------------------------|---------|--------|----------------------------------|---------|------|

| Symbol/Description                                                                       | Condition                     | Min                                           | Тур                              | Max     | Min    | Тур                              | Max     | Onit |

| Minimum differential eye<br>opening at the receiver<br>serial input pins <sup>(30)</sup> | _                             | 100                                           | _                                | _       | 100    | _                                | _       | mV   |

| V <sub>ICM</sub> (AC coupled)                                                            | _                             | _                                             | 0.7/0.75/<br>0.8 <sup>(31)</sup> | _       | _      | 0.7/0.75/<br>0.8 <sup>(31)</sup> |         | mV   |

| V <sub>ICM</sub> (DC coupled)                                                            | $\leq 3.2 \text{Gbps}^{(32)}$ | 670                                           | 700                              | 730     | 670    | 700                              | 730     | mV   |

|                                                                                          | 85- $\Omega$ setting          |                                               | 85                               | —       |        | 85                               | _       | Ω    |

| Differential on-chip                                                                     | 100- $\Omega$ setting         |                                               | 100                              | _       |        | 100                              |         | Ω    |

| termination resistors                                                                    | 120-Ω setting                 |                                               | 120                              | —       |        | 120                              |         | Ω    |

|                                                                                          | 150-Ω setting                 |                                               | 150                              | _       |        | 150                              |         | Ω    |

| t <sub>LTR</sub> <sup>(33)</sup>                                                         |                               | _                                             | _                                | 10      | _      | _                                | 10      | μs   |

| $t_{LTD}^{(34)}$                                                                         | _                             | 4                                             | _                                | _       | 4      | _                                | _       | μs   |

| t <sub>LTD_manual</sub> <sup>(35)</sup>                                                  | _                             | 4                                             | _                                | —       | 4      | _                                | _       | μs   |

| t <sub>LTR_LTD_manual</sub> <sup>(36)</sup>                                              |                               | 15                                            | _                                |         | 15     |                                  |         | μs   |

| Programmable ppm<br>detector <sup>(37)</sup>                                             | _                             | ±62.5, 100, 125, 200, 250, 300, 500, and 1000 |                                  |         |        |                                  | ppm     |      |

<sup>(30)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the **Receiver Equalization** feature. If you enable the **Receiver Equalization** feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

(31) The AC coupled  $V_{ICM} = 700 \text{ mV}$  for Arria V GX and SX in PCIe mode only. The AC coupled  $V_{ICM} = 750 \text{ mV}$  for Arria V GT and ST in PCIe mode only.

<sup>(32)</sup> For standard protocol compliance, use AC coupling.

$^{(33)}$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$^{(34)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

$^{(35)}$  t<sub>LTD\_manual</sub> is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

|                  | Symbol                                                    | Condition                                               |      | -I3, -C4 |       |      | –I5, –C5 |       | -C6  |     |       | Unit |

|------------------|-----------------------------------------------------------|---------------------------------------------------------|------|----------|-------|------|----------|-------|------|-----|-------|------|

|                  | Symbol                                                    | Condition                                               | Min  | Тур      | Max   | Min  | Тур      | Мах   | Min  | Тур | Max   | Onit |

|                  | TCCS                                                      | True Differential I/O<br>Standards                      | _    | _        | 150   | _    | _        | 150   | _    | _   | 150   | ps   |

|                  | 1003                                                      | Emulated Differential<br>I/O Standards                  | _    | _        | 300   | _    | _        | 300   |      | _   | 300   | ps   |

|                  | True Differential I/O<br>Standards - f <sub>HSDRDPA</sub> | SERDES factor J =3 to $10^{(76)}$                       | 150  |          | 1250  | 150  | _        | 1250  | 150  |     | 1050  | Mbps |

|                  | (data rate)                                               | SERDES factor $J \ge 8$<br>with DPA <sup>(76)(78)</sup> | 150  | _        | 1600  | 150  | _        | 1500  | 150  | _   | 1250  | Mbps |

| Receiver         |                                                           | SERDES factor J = 3<br>to 10                            | (77) | _        | (83)  | (77) | _        | (83)  | (77) | _   | (83)  | Mbps |

|                  | f <sub>HSDR</sub> (data rate)                             | SERDES factor J = 1<br>to 2, uses DDR<br>registers      | (77) |          | (79)  | (77) |          | (79)  | (77) |     | (79)  | Mbps |

| DPA Mode         | DPA run length                                            | _                                                       | —    | _        | 10000 | _    | _        | 10000 | _    | _   | 10000 | UI   |

| Soft-CDR<br>Mode | Soft-CDR ppm tolerance                                    | _                                                       | _    | _        | 300   | _    | _        | 300   | _    | _   | 300   | ±ppm |

| Non-DPA<br>Mode  | Sampling Window                                           | _                                                       |      | _        | 300   | _    | _        | 300   |      | _   | 300   | ps   |

Arria V GX, GT, SX, and ST Device Datasheet

<sup>&</sup>lt;sup>(83)</sup> You can estimate the achievable maximum data rate for non-DPA mode by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

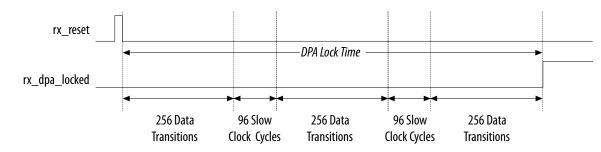

## **DPA Lock Time Specifications**

#### Figure 1-4: Dynamic Phase Alignment (DPA) Lock Time Specifications with DPA PLL Calibration Enabled

### Table 1-41: DPA Lock Time Specifications for Arria V Devices

The specifications are applicable to both commercial and industrial grades. The DPA lock time is for one channel. One data transition is defined as a 0-to-1 or 1-to-0 transition.

| Standard           | Training Pattern    | Number of Data<br>Transitions in One<br>Repetition of the Training<br>Pattern | Number of Repetitions per<br>256 Data Transitions <sup>(84)</sup> | Maximum Data Transition |

|--------------------|---------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|

| SPI-4              | 0000000001111111111 | 2                                                                             | 128                                                               | 640                     |

| Parallel Rapid I/O | 00001111            | 2                                                                             | 128                                                               | 640                     |

| r araner Rapid 1/0 | 10010000            | 4                                                                             | 64                                                                | 640                     |

| Miscellaneous      | 10101010            | 8                                                                             | 32                                                                | 640                     |

| wiscenaneous       | 01010101            | 8                                                                             | 32                                                                | 640                     |

<sup>(84)</sup> This is the number of repetitions for the stated training pattern to achieve the 256 data transitions.

## **Memory Output Clock Jitter Specifications**

#### Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -I3, | -C4 | –15, | -C5 | -(  | 6   | Unit |

|------------------------------|---------------|-----------------------|------|-----|------|-----|-----|-----|------|

| Falanietei                   |               | Symbol                | Min  | Max | Min  | Max | Min | Max | Ont  |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -41  | 41  | -50  | 50  | -55 | 55  | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | 6    | 3   | 9    | 0   | 9   | 4   | ps   |

## **OCT Calibration Block Specifications**

#### Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                           | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                              |     |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octus<br>RCLK clock cycles required for $R_S$ OCT/ $R_T$ OCT calibration                                                                    |     | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of octusrclk clock cycles required for oct code to shift out                                                                                   |     | 32   |     | Cycles |

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

The SD/MMC interface calibration support will be available in a future release of the preloader through the SoC EDS software update.

| Symbol                                              | Description                                         | Min                                                         | Мах                                                                                                  | Unit |

|-----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|

|                                                     | SDMMC_CLK clock period (Identification mode)        | 20                                                          | _                                                                                                    | ns   |

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period<br>(Default speed mode)      | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK clock period<br>(High speed mode)         | 5                                                           | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (Identification mode) | 2500                                                        | _                                                                                                    | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Default speed mode)     | 40                                                          | _                                                                                                    | ns   |

|                                                     | SDMMC_CLK_OUT clock<br>period (High speed mode)     | 20                                                          | _                                                                                                    | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                            | 45                                                          | 55                                                                                                   | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D<br>output delay                   | $\frac{(T_{sdmmc\_clk} \times drvsel)/2}{-1.23}$            | $\begin{array}{c} (\mathrm{T}_{sdmmc\_clk} \times \texttt{drvsel})/2 \\ + 1.69^{\ (87)} \end{array}$ | ns   |

| T <sub>su</sub>                                     | Input setup time                                    | $1.05 - (T_{sdmmc_clk} \times smplsel)/2^{(88)}$            |                                                                                                      | ns   |

| T <sub>h</sub>                                      | Input hold time                                     | $\frac{(T_{sdmmc\_clk} \times \texttt{smplsel})}{2^{(88)}}$ | —                                                                                                    | ns   |

<sup>&</sup>lt;sup>(87)</sup> drvsel is the drive clock phase shift select value.

<sup>&</sup>lt;sup>(88)</sup> smplsel is the sample clock phase shift select value.

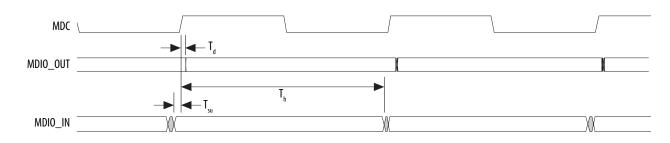

## Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

## Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Symbol Description                                |      | d Mode | Fast | Mode | – Unit |

|-----------------------|---------------------------------------------------|------|--------|------|------|--------|

| Symbol                | Description                                       | Min  | Max    | Min  | Max  | Onit   |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10   | —      | 2.5  | _    | μs     |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7  | —      | 0.6  |      | μs     |

| T <sub>clklow</sub>   | SCL low time                                      | 4    | _      | 1.3  |      | μs     |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25 | —      | 0.1  | —    | μs     |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0    | 3.45   | 0    | 0.9  | μs     |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —    | 0.2    | _    | 0.2  | μs     |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7  | _      | 0.6  | _    | μs     |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4    | —      | 0.6  | _    | μs     |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4    | —      | 0.6  | —    | μs     |

#### 1-76 FPGA JTAG Configuration Timing

| POR Delay | Minimum | Maximum | Unit |

|-----------|---------|---------|------|

| Standard  | 100     | 300     | ms   |

#### **Related Information**

#### **MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

# **FPGA JTAG Configuration Timing**

## Table 1-64: FPGA JTAG Timing Parameters and Values for Arria V Devices

| Symbol                  | Description                              | Min                            | Мах                | Unit |

|-------------------------|------------------------------------------|--------------------------------|--------------------|------|

| t <sub>JCP</sub>        | TCK clock period                         | <b>30, 167</b> <sup>(92)</sup> | _                  | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14                             |                    | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14                             |                    | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2                              |                    | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3                              |                    | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5                              |                    | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |                                | 12 <sup>(93)</sup> | ns   |

| t <sub>JPZX</sub>       | JTAG port high impedance to valid output |                                | 14 <sup>(93)</sup> | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | _                              | 14 <sup>(93)</sup> | ns   |

<sup>&</sup>lt;sup>(92)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

<sup>&</sup>lt;sup>(93)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

# **Remote System Upgrades**

#### Table 1-74: Remote System Upgrade Circuitry Timing Specifications for Arria V Devices

| Parameter                                 | Minimum | Unit |

|-------------------------------------------|---------|------|

| t <sub>RU_nCONFIG</sub> <sup>(110)</sup>  | 250     | ns   |

| t <sub>RU_nRSTIMER</sub> <sup>(111)</sup> | 250     | ns   |

#### **Related Information**

- **Remote System Upgrade State Machine** Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer Provides more information about reset\_timer (RU\_nRSTIMER) signal.

# User Watchdog Internal Oscillator Frequency Specifications

### Table 1-75: User Watchdog Internal Oscillator Frequency Specifications for Arria V Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Altera offers two ways to determine I/O timing—the Excel-based I/O timing and the Quartus Prime Timing Analyzer.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

<sup>&</sup>lt;sup>(110)</sup> This is equivalent to strobing the reconfiguration input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

<sup>&</sup>lt;sup>(111)</sup> This is equivalent to strobing the reset timer input of the ALTREMOTE\_UPDATE IP core high for the minimum timing specification.

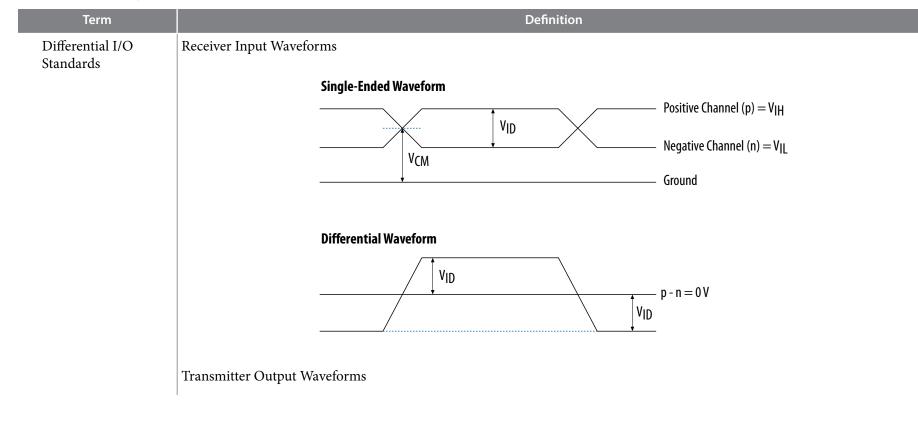

| Term                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Definition                         |                                                                                       |  |  |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Definition                         |                                                                                       |  |  |  |  |

| Single-ended voltage referenced I/O<br>standard | The JEDEC standard for the SSTL and HSTL I/O defines both the AC and DC input signal values indicate the voltage levels at which the receiver must meet its timing specifications. T indicate the voltage levels at which the final logic state of the receiver is unambiguously defireceiver input has crossed the AC value, the receiver changes to the new logic state.<br>The new logic state is then maintained as long as the input stays beyond the DC threshold. The is intended to provide predictable receiver timing in the presence of input waveform ringing Single-Ended Voltage Referenced I/O Standard |                                    |                                                                                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | V <sub>CCI0</sub>                                                                     |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                                                                                       |  |  |  |  |

|                                                 | V <sub>0Н</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>IH(A</sub>                  |                                                                                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | VIH(DC)                                                                               |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V REF                              | / V <sub>IL(DC)</sub>                                                                 |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /                                  | /<br>V il(AC )                                                                        |  |  |  |  |

|                                                 | V <sub>0L</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                                                                                       |  |  |  |  |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    | V <sub>SS</sub>                                                                       |  |  |  |  |

| t <sub>C</sub>                                  | High-speed receiver/transmitter i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nput and output clock period.      |                                                                                       |  |  |  |  |

| TCCS (channel-to-channel-skew)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ne same PLL. The clock is included | ncluding the t <sub>CO</sub> variation and clock<br>in the TCCS measurement (refer to |  |  |  |  |

| t <sub>DUTY</sub>                               | High-speed I/O block—Duty cycl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e on high-speed transmitter outpu  | t clock.                                                                              |  |  |  |  |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus II software v12.0 release:</li> <li>Restructured document.</li> <li>Updated "Supply Current and Power Consumption" section.</li> <li>Updated Table 20, Table 21, Table 24, Table 25, Table 26, Table 35, Table 39, Table 43, and Table 52.</li> <li>Added Table 22, Table 23, and Table 33.</li> <li>Added Figure 1–1 and Figure 1–2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul> |

| February 2012 | 1.3     | <ul> <li>Updated Table 2–1.</li> <li>Updated Transceiver-FPGA Fabric Interface rows in Table 2–20.</li> <li>Updated V<sub>CCP</sub> description.</li> </ul>                                                                                                                                                                                                                                                                                           |

| December 2011 | 1.2     | Updated Table 2–1 and Table 2–3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| November 2011 | 1.1     | <ul> <li>Updated Table 2–1, Table 2–19, Table 2–26, and Table 2–36.</li> <li>Added Table 2–5.</li> <li>Added Figure 2–4.</li> </ul>                                                                                                                                                                                                                                                                                                                   |

| August 2011   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **Transceiver Power Supply Requirements**

#### Table 2-7: Transceiver Power Supply Voltage Requirements for Arria V GZ Devices

| Conditions                                                                                                                                | VCCR_GXB and VCCT_GXB <sup>(122)</sup> | VCCA_GXB | VCCH_GXB | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                                                                                             | 1.05                                   |          |          |      |

| <ul> <li>Data rate &gt; 10.3 Gbps.</li> <li>DFE is used.</li> </ul>                                                                       |                                        |          |          |      |

| If ANY of the following conditions are true <sup>(123)</sup> :                                                                            | 1.0                                    | 3.0      |          |      |

| <ul> <li>ATX PLL is used.</li> <li>Data rate &gt; 6.5Gbps.</li> <li>DFE (data rate ≤ 10.3 Gbps), AEQ, or EyeQ feature is used.</li> </ul> |                                        |          | 1.5      | V    |

| If ALL of the following conditions are true:                                                                                              | 0.85                                   | 2.5      |          |      |

| <ul> <li>ATX PLL is not used.</li> <li>Data rate ≤ 6.5Gbps.</li> <li>DFE, AEQ, and EyeQ are not used.</li> </ul>                          |                                        |          |          |      |

## **DC Characteristics**

#### **Supply Current**

Standby current is the current drawn from the respective power rails used for power budgeting.

Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

Send Feedback

<sup>&</sup>lt;sup>(122)</sup> If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to 0.85 V, they can be shared with the VCC core supply.

<sup>&</sup>lt;sup>(123)</sup> Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

#### Table 2-19: Differential SSTL I/O Standards for Arria V GZ Devices

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       | V <sub>SWIN</sub> | <sub>G(DC)</sub> (V)       | V <sub>X(AC)</sub> (V)          |                      |                                 |                                               | V <sub>SWING(AC)</sub> (V) |  |

|-------------------------|-------|-----------------------|-------|-------------------|----------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|----------------------------|--|

|                         | Min   | Тур                   | Max   | Min               | Max                        | Min                             | Тур                  | Max                             | Min                                           | Мах                        |  |

| SSTL-2 Class I,<br>II   | 2.375 | 2.5                   | 2.625 | 0.3               | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.2   | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$           |  |

| SSTL-18 Class I,<br>II  | 1.71  | 1.8                   | 1.89  | 0.25              | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.175 |                      | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | V <sub>CCIO</sub> + 0.6    |  |

| SSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  |                      | V <sub>CCIO</sub> /2<br>+ 0.15  | 0.35                                          | _                          |  |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.45  | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$  |  |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.31  | 0.18              | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | _                          |  |

| SSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | 0.18              | —                          | V <sub>REF</sub><br>-0.15       | V <sub>CCIO</sub> /2 | V <sub>REF</sub><br>+ 0.15      | -0.30                                         | 0.30                       |  |

## Table 2-20: Differential HSTL and HSUL I/O Standards for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |     |     | $V_{X(AC)}(V)$ |     | V <sub>CM(DC)</sub> (V) |      |     | V <sub>DIF(AC)</sub> (V) |     |     |

|------------------------|-----------------------|-----|--------------------------|-----|-----|----------------|-----|-------------------------|------|-----|--------------------------|-----|-----|

|                        | Min                   | Тур | Max                      | Min | Max | Min            | Тур | Max                     | Min  | Тур | Max                      | Min | Max |

| HSTL-18 Class<br>I, II | 1.71                  | 1.8 | 1.89                     | 0.2 | _   | 0.78           |     | 1.12                    | 0.78 | _   | 1.12                     | 0.4 | _   |

| HSTL-15 Class<br>I, II | 1.425                 | 1.5 | 1.575                    | 0.2 | _   | 0.68           |     | 0.9                     | 0.68 | _   | 0.9                      | 0.4 | —   |

$<sup>^{(127)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

| Symbol/Description                         | Conditions                                                | Transc | eiver Speed   | Grade 2 | Transce | eiver Speed   | Grade 3 | Unit |

|--------------------------------------------|-----------------------------------------------------------|--------|---------------|---------|---------|---------------|---------|------|

| Symbol/Description                         | Conditions                                                | Min    | Тур           | Max     | Min     | Тур           | Мах     | Unit |

| Rise time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> | _      | _             | 400     | _       | _             | 400     | 20   |

| Fall time                                  | Measure at ±60 mV of differential signal <sup>(138)</sup> |        | _             | 400     |         |               | 400     | ps   |

| Duty cycle                                 | —                                                         | 45     | _             | 55      | 45      |               | 55      | %    |

| Spread-spectrum modulating clock frequency | PCI Express <sup>®</sup> (PCIe)                           | 30     | _             | 33      | 30      |               | 33      | kHz  |

| Spread-spectrum downspread                 | PCIe                                                      |        | 0 to          | _       | _       | 0 to          | —       | %    |

|                                            |                                                           |        | -0.5          |         |         | -0.5          |         |      |

| On-chip termination resistors              | —                                                         |        | 100           | _       |         | 100           |         | Ω    |

| Absolute V <sub>MAX</sub>                  | Dedicated reference clock pin                             |        | _             | 1.6     |         |               | 1.6     | V    |

|                                            | RX reference clock pin                                    |        | _             | 1.2     |         |               | 1.2     |      |

| Absolute V <sub>MIN</sub>                  | —                                                         | -0.4   | _             | _       | -0.4    |               |         | V    |

| Peak-to-peak differential input<br>voltage | -                                                         | 200    | -             | 1600    | 200     |               | 1600    | mV   |

| V <sub>ICM</sub> (AC coupled)              | Dedicated reference clock pin                             | 10     | 00/900/850    | (139)   | 10      | mV            |         |      |

| · • ·                                      | RX reference clock pin                                    | 1.     | .0/0.9/0.85 ( | 140)    | 1.      | .0/0.9/0.85(1 | 40)     | mV   |

| V <sub>ICM</sub> (DC coupled)              | HCSL I/O standard for<br>PCIe reference clock             | 250    | _             | 550     | 250     |               | 550     | mV   |

<sup>(138)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

(139) The reference clock common mode voltage is equal to the V<sub>CCR\_GXB</sub> power supply level.

(140) This supply follows VCCR\_GXB

AV-51002 2017.02.10

| Symbol/Description                                                                              | Conditions                                  | Trans | ceiver Spee  | d Grade 2 | Transc | Unit         |     |    |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------|-------|--------------|-----------|--------|--------------|-----|----|--|

| Symbol/Description                                                                              | Conditions                                  | Min   | Тур          | Мах       | Min    | Тур          | Max |    |  |

| Maximum peak-to-peak differential input voltage $V_{ID}$ (diff p-p) before device configuration | _                                           | _     | _            | 1.6       | _      | _            | 1.6 | V  |  |

| Maximum peak-to-peak differential input voltage V <sub>ID</sub> (diff p-p) after                | $V_{CCR\_GXB} = 1.0 V$ $(V_{ICM} = 0.75 V)$ | _     | _            | 1.8       | _      |              | 1.8 | V  |  |

| device configuration <sup>(146)</sup>                                                           | $V_{CCR\_GXB} = 0.85 V$ $(V_{ICM} = 0.6 V)$ |       | _            | 2.4       | _      | _            | 2.4 | V  |  |

| Minimum differential eye opening at receiver serial input pins <sup>(147)(148)</sup>            | _                                           | 85    | _            | _         | 85     | _            |     | mV |  |

|                                                                                                 | 85– $\Omega$ setting                        |       | 85 ± 30%     | _         | _      | 85<br>± 30%  | _   | Ω  |  |

| Differential on-chip termination                                                                | 100– $\Omega$ setting                       |       | 100<br>± 30% |           | _      | 100<br>± 30% |     | Ω  |  |

| resistors                                                                                       | 120– $\Omega$ setting                       | —     | 120<br>± 30% |           | —      | 120<br>± 30% |     | Ω  |  |

|                                                                                                 | 150– $\Omega$ setting                       | _     | 150<br>± 30% |           | _      | 150<br>± 30% |     | Ω  |  |

<sup>&</sup>lt;sup>(146)</sup> The maximum peak to peak differential input voltage  $V_{ID}$  after device configuration is equal to 4 × (absolute  $V_{MAX}$  for receiver pin -  $V_{ICM}$ ).

<sup>&</sup>lt;sup>(147)</sup> The differential eye opening specification at the receiver input pins assumes that **Receiver Equalization** is disabled. If you enable **Receiver Equalization**, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>&</sup>lt;sup>(148)</sup> Minimum eye opening of 85 mV is only for the unstressed input eye condition.

| Symbol/Description                           | Conditions                                              | Trans | ceiver Spee | d Grade 2 | Transc | ed Grade 3 | Unit |    |

|----------------------------------------------|---------------------------------------------------------|-------|-------------|-----------|--------|------------|------|----|

| Symbol/Description                           | Conditions                                              | Min   | Тур         | Мах       | Min    | Тур        | Мах  |    |

|                                              | $V_{CCR\_GXB} = 0.85 V$<br>full bandwidth               | _     | 600         | _         | _      | 600        | _    | mV |

| V (AC and DC coupled)                        | $V_{CCR_{GXB}} = 0.85 V$<br>half bandwidth              | _     | 600         |           | _      | 600        | _    | mV |

| $\rm V_{ICM}$ (AC and DC coupled)            | $V_{CCR_{GXB}} = 1.0 V$<br>full bandwidth               |       | 700         | _         |        | 700        | _    | mV |

|                                              | $V_{CCR_{GXB}} = 1.0 V$<br>half bandwidth               |       | 700         | _         |        | 700        | _    | mV |

| t <sub>LTR</sub> <sup>(149)</sup>            | —                                                       | _     | _           | 10        | _      | _          | 10   | μs |

| t <sub>LTD</sub> <sup>(150)</sup>            | _                                                       | 4     |             |           | 4      | _          |      | μs |

| t <sub>LTD_manual</sub> <sup>(151)</sup>     | —                                                       | 4     | _           |           | 4      | _          |      | μs |

| t <sub>LTR_LTD_manual</sub> <sup>(152)</sup> | _                                                       | 15    |             |           | 15     | _          |      | μs |

| Programmable equalization<br>(AC Gain)       | Full bandwidth (6.25 GHz)<br>Half bandwidth (3.125 GHz) |       |             | 16        |        | _          | 16   | dB |

2-26

Receiver

$<sup>^{(149)}</sup>$  t<sub>LTR</sub> is the time required for the receive CDR to lock to the input reference clock frequency after coming out of reset.

$<sup>^{(150)}</sup>$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

<sup>(151)</sup>  $t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

$t_{\text{LTR\_LTD\_manual}}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

#### 2-64 FPP Configuration Timing when DCLK to DATA[] > 1

| Symbol              | Parameter                                         | Minimum                                    | Maximum | Unit |

|---------------------|---------------------------------------------------|--------------------------------------------|---------|------|

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period      | —       | —    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) (215) | —       | —    |

#### **Related Information**

- DCLK-to-DATA[] Ratio (r) for FPP Configuration on page 2-57

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(215)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on these pins, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

| Symbol              | Parameter                                         | Minimum                                        | Maximum | Unit |

|---------------------|---------------------------------------------------|------------------------------------------------|---------|------|

| t <sub>CO</sub>     | DCLK falling edge to AS_DATA0/ASDO output         |                                                | 4       | ns   |

| t <sub>SU</sub>     | Data setup time before falling edge on DCLK       | 1.5                                            | —       | ns   |

| t <sub>H</sub>      | Data hold time after falling edge on DCLK         | 0                                              | —       | ns   |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode (216)                 | 175                                            | 437     | μs   |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period          | _       | _    |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on | t <sub>CD2CU</sub> + (8576 × Clkusr<br>period) | _       | _    |

#### Table 2-59: DCLK Frequency Specification in the AS Configuration Scheme

This applies to the DCLK frequency specification when using the internal oscillator as the configuration clock source.

The AS multi-device configuration scheme does not support  ${\tt DCLK}$  frequency of 100 MHz.

| Minimum | Typical | Maximum | Unit |

|---------|---------|---------|------|

| 5.3     | 7.9     | 12.5    | MHz  |

| 10.6    | 15.7    | 25.0    | MHz  |

| 21.3    | 31.4    | 50.0    | MHz  |

| 42.6    | 62.9    | 100.0   | MHz  |

#### **Related Information**

- Passive Serial Configuration Timing on page 2-67

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

<sup>&</sup>lt;sup>(216)</sup> To enable the CLKUSR pin as the initialization clock source and to obtain the maximum frequency specification on this pin, refer to the "Initialization" section of the *Configuration, Design Security, and Remote System Upgrades in Arria V Devices* chapter.

# Glossary

#### Table 2-68: Glossary

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| July 2014     | 3.8     | <ul> <li>Updated Table 21.</li> <li>Updated Table 22 V<sub>OCM</sub> (DC Coupled) condition.</li> <li>Updated the DCLK note to Figure 6, Figure 7, and Figure 9.</li> <li>Added note to Table 5 and Table 6.</li> <li>Added the DCLK specification to Table 50.</li> <li>Added note to Table 51.</li> <li>Updated the list of parameters in Table 53.</li> </ul> |  |

| February 2014 | 3.7     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |  |

| December 2013 | 3.6     | <ul> <li>Updated Table 2, Table 13, Table 18, Table 19, Table 22, Table 30, Table 33, Table 37, Table 38, Table 45, Table 46, Table 47, Table 56, Table 49.</li> <li>Updated "PLL Specifications".</li> </ul>                                                                                                                                                    |  |

| August 2013   | 3.5     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |  |

| August 2013   | 3.4     | <ul> <li>Removed Preliminary tags for Table 2, Table 4, Table 5, Table 14, Table 27, Table 28, Table 29, Table 31, Table 32, Table 43, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, and Table 54.</li> <li>Updated Table 2 and Table 28.</li> </ul>                                                                                               |  |

| June 2013     | 3.3     | Updated Table 23, Table 28, Table 51, and Table 55.                                                                                                                                                                                                                                                                                                              |  |

| May 2013      | 3.2     | <ul> <li>Added Table 23.</li> <li>Updated Table 5, Table 22, Table 26, and Table 57.</li> <li>Updated Figure 6, Figure 7, Figure 8, and Figure 9.</li> </ul>                                                                                                                                                                                                     |  |

| March 2013    | 3.1     | <ul> <li>Updated Table 2, Table 6, Table 7, Table 8, Table 19, Table 22, Table 26, Table 29, Table 52.</li> <li>Updated "Maximum Allowed Overshoot and Undershoot Voltage".</li> </ul>                                                                                                                                                                           |  |

| December 2012 | 3.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                 |  |