# E·XFL

#### Intel - 5AGZME5H3F35C4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 18870                                                      |

| Number of Logic Elements/Cells | 400000                                                     |

| Total RAM Bits                 | 34322432                                                   |

| Number of I/O                  | 534                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 0.82V ~ 0.88V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1152-BBGA, FCBGA                                           |

| Supplier Device Package        | 1152-FBGA (35x35)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/5agzme5h3f35c4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Typical TX V<sub>OD</sub> Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

| Table 1-32: Typical TX Vor | Setting for Arria V Transceive | r Channels with termination of 100 $\Omega$ |

|----------------------------|--------------------------------|---------------------------------------------|

|                            |                                |                                             |

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8(59)                                   | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| -) <b>F</b>                                          | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

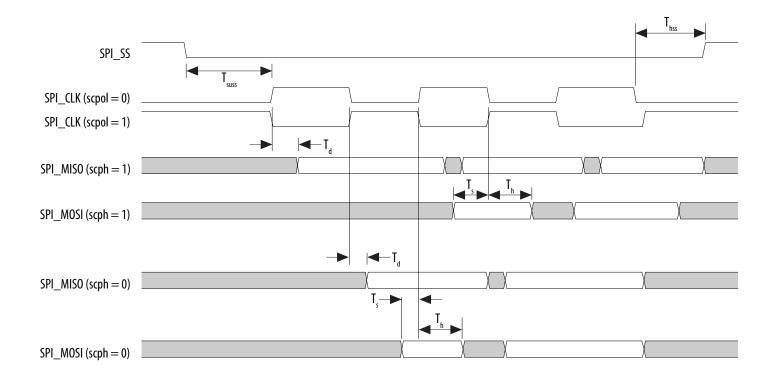

#### Figure 1-10: SPI Slave Timing Diagram

#### **Related Information**

#### SPI Controller, Arria V Hard Processor System Technical Reference Manual

Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

#### Table 1-54: Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Arria V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

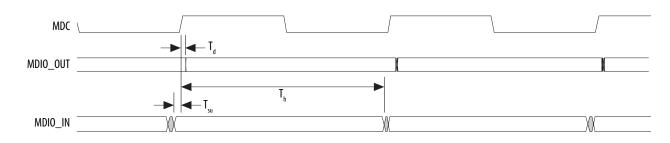

# Figure 1-15: MDIO Timing Diagram

# I<sup>2</sup>C Timing Characteristics

# Table 1-59: I<sup>2</sup>C Timing Requirements for Arria V Devices

| Symbol                | Description                                       | Standar | d Mode | Fast | Mode | Unit |  |

|-----------------------|---------------------------------------------------|---------|--------|------|------|------|--|

| Symbol                |                                                   | Min     | Max    | Min  | Max  | Onic |  |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10      | —      | 2.5  | _    | μs   |  |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7     | —      | 0.6  |      | μs   |  |

| T <sub>clklow</sub>   | SCL low time                                      | 4       | _      | 1.3  |      | μs   |  |

| T <sub>s</sub>        | Setup time for serial data line (SDA) data to SCL | 0.25    | —      | 0.1  | —    | μs   |  |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0       | 3.45   | 0    | 0.9  | μs   |  |

| T <sub>d</sub>        | SCL to SDA output data delay                      | —       | 0.2    | _    | 0.2  | μs   |  |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7     | _      | 0.6  | _    | μs   |  |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4       | —      | 0.6  | _    | μs   |  |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4       | —      | 0.6  | —    | μs   |  |

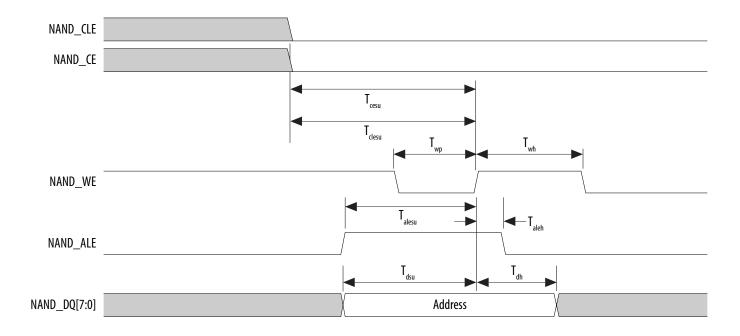

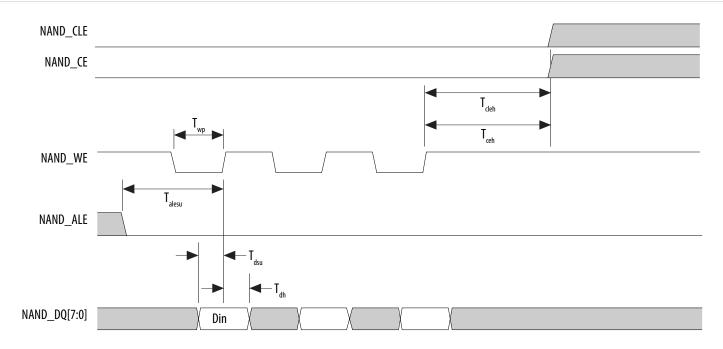

# Figure 1-18: NAND Address Latch Timing Diagram

# Figure 1-19: NAND Data Write Timing Diagram

#### 1-80 AS Configuration Timing

| Symbol              | Parameter                                                 | Minimum                                     | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|---------------------------------------------|---------|--------|

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLк period                     | _       |        |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU}$ + ( $T_{init}$ × CLKUSR period) |         | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                       |         | Cycles |

#### **Related Information**

#### **FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

# **AS Configuration Timing**

#### Table 1-68: AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2CD}$ ,  $t_{CF2ST0}$ ,  $t_{CFG}$ ,  $t_{STATUS}$ , and  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Arria V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding nSTATUS low.

| Symbol              | Parameter                                                 | Minimum                                     | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|---------------------------------------------|---------|--------|

| t <sub>CO</sub>     | DCLK falling edge to the AS_DATA0/ASDO output             |                                             | 2       | ns     |

| t <sub>SU</sub>     | Data setup time before the falling edge on DCLK           | 1.5                                         | _       | ns     |

| t <sub>DH</sub>     | Data hold time after the falling edge on DCLK             | 0                                           |         | ns     |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode                               | 175                                         | 437     | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                     | _       | _      |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU}$ + ( $T_{init}$ × Clkusr period) |         | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                       |         | Cycles |

| Variant    | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) |

|------------|-------------|--------------------------------|------------------------|

|            | A1          | 71,015,712                     | 439,960                |

|            | A3          | 71,015,712                     | 439,960                |

|            | A5          | 101,740,800                    | 446,360                |

| Arria V GX | A7          | 101,740,800                    | 446,360                |

| Allia V GA | B1          | 137,785,088                    | 457,368                |

|            | B3          | 137,785,088                    | 457,368                |

|            | B5          | 185,915,808                    | 463,128                |

|            | B7          | 185,915,808                    | 463,128                |

|            | C3          | 71,015,712                     | 439,960                |

| Arria V GT | C7          | 101,740,800                    | 446,360                |

| Allia v GI | D3          | 137,785,088                    | 457,368                |

|            | D7          | 185,915,808                    | 463,128                |

| Arria V SX | B3          | 185,903,680                    | 450,968                |

| Arria V SX | B5          | 185,903,680                    | 450,968                |

| Arria V ST | D3          | 185,903,680                    | 450,968                |

|            | D5          | 185,903,680                    | 450,968                |

# **Minimum Configuration Time Estimation**

### Table 1-73: Minimum Configuration Time Estimation for Arria V Devices

The estimated values are based on the configuration .rbf sizes in Uncompressed .rbf Sizes for Arria V Devices table.

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

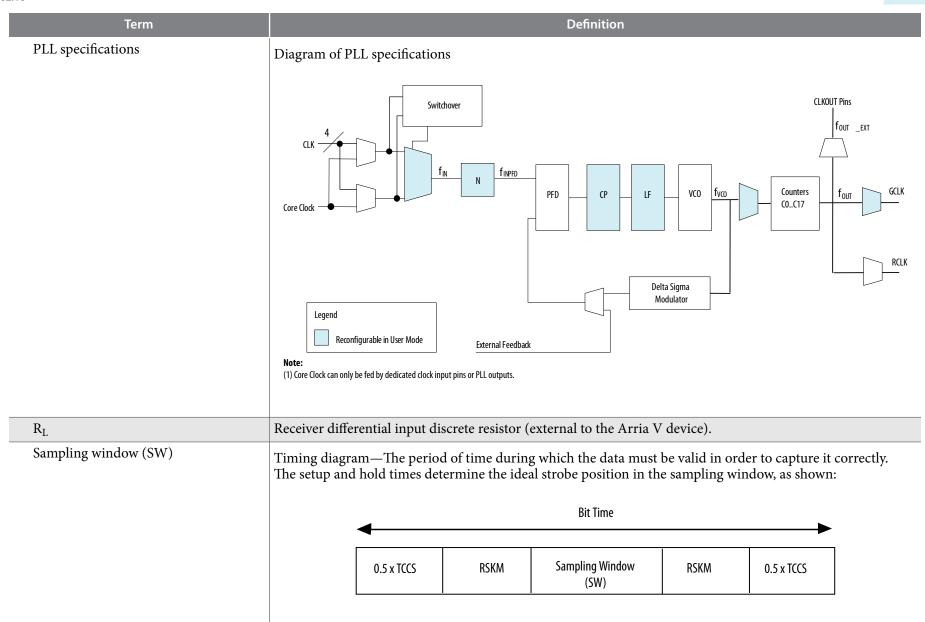

| Term                       | Definition                                                                                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>FALL</sub>          | Signal high-to-low transition time (80–20%)                                                                                                                           |

| t <sub>INCCJ</sub>         | Cycle-to-cycle jitter tolerance on the PLL clock input                                                                                                                |

| t <sub>OUTPJ_IO</sub>      | Period jitter on the GPIO driven by a PLL                                                                                                                             |

| t <sub>OUTPJ_DC</sub>      | Period jitter on the dedicated clock output driven by a PLL                                                                                                           |

| t <sub>RISE</sub>          | Signal low-to-high transition time (20–80%)                                                                                                                           |

| Timing Unit Interval (TUI) | The timing budget allowed for skew, propagation delays, and the data sampling window. (TUI = $1/$ (Receiver Input Clock Frequency Multiplication Factor) = $t_C/w$ )  |

| V <sub>CM(DC)</sub>        | DC common mode input voltage.                                                                                                                                         |

| V <sub>ICM</sub>           | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                 |

| V <sub>ID</sub>            | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.          |

| V <sub>DIF(AC)</sub>       | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                           |

| V <sub>DIF(DC)</sub>       | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                          |

| V <sub>IH</sub>            | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                 |

| V <sub>IH(AC)</sub>        | High-level AC input voltage                                                                                                                                           |

| V <sub>IH(DC)</sub>        | High-level DC input voltage                                                                                                                                           |

| V <sub>IL</sub>            | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                   |

| V <sub>IL(AC)</sub>        | Low-level AC input voltage                                                                                                                                            |

| V <sub>IL(DC)</sub>        | Low-level DC input voltage                                                                                                                                            |

| V <sub>OCM</sub>           | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                             |

| V <sub>OD</sub>            | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission line at the transmitter. |

| V <sub>SWING</sub>         | Differential input voltage                                                                                                                                            |

| V <sub>X</sub>             | Input differential cross point voltage                                                                                                                                |

Arria V GX, GT, SX, and ST Device Datasheet

Altera Corporation

#### 1-96 Document Revision History

| Date      | Version    | Changes                                                                                                                                                                                                                                                                                                                                 |

|-----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2015 | 2015.06.16 | • Added the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Arria V Devices table:                                                                                                                                                                 |

|           |            | True RSDS output standard: data rates of up to 360 Mbps                                                                                                                                                                                                                                                                                 |

|           |            | True mini-LVDS output standard: data rates of up to 400 Mbps                                                                                                                                                                                                                                                                            |

|           |            | <ul> <li>Added note in the condition for Transmitter—Emulated Differential I/O Standards f<sub>HSDR</sub> data rate parameter<br/>in the High-Speed I/O Specifications for Arria V Devices table. Note: When using True LVDS RX channels<br/>for emulated LVDS TX channel, only serialization factors 1 and 2 are supported.</li> </ul> |

|           |            | Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.                                                                                                                                                                                                                                      |

|           |            | Updated T <sub>h</sub> location in I <sup>2</sup> C Timing Diagram.                                                                                                                                                                                                                                                                     |

|           |            | Updared T <sub>wp</sub> location in NAND Address Latch Timing Diagram.                                                                                                                                                                                                                                                                  |

|           |            | <ul> <li>Corrected the unit for t<sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for<br/>Arria V Devices table.</li> </ul>                                                                                                                                                                       |

|           |            | • Updated the maximum value for t <sub>CO</sub> from 4 ns to 2 ns in AS Timing Parameters for AS ×1 and ×4 Configurations in Arria V Devices table.                                                                                                                                                                                     |

|           |            | • Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Arria V Devices chapter.                                                                                                                                                                                                     |

|           |            | FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1                                                                                                                                                                                                                                                                        |

|           |            | • FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is >1                                                                                                                                                                                                                                                                     |

|           |            | AS Configuration Timing Waveform                                                                                                                                                                                                                                                                                                        |

|           |            | PS Configuration Timing Waveform                                                                                                                                                                                                                                                                                                        |

| Symbol                            | Description                                                              | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-----------------------------------|--------------------------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| V <sub>CCPT</sub>                 | Power supply for programmable power technology                           | _         | 1.45                     | 1.50    | 1.55                     | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply for the programmable power technology                   | -         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCPD</sub> <sup>(116</sup> | I/O pre-driver (3.0 V) power supply                                      | _         | 2.85                     | 3.0     | 3.15                     | V    |

| )                                 | I/O pre-driver (2.5 V) power supply                                      | _         | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (3.0 V) power supply                                         |           | 2.85                     | 3.0     | 3.15                     | V    |

|                                   | I/O buffers (2.5 V) power supply                                         |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | I/O buffers (1.8 V) power supply                                         | _         | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCIO</sub>                 | I/O buffers (1.5 V) power supply                                         |           | 1.425                    | 1.5     | 1.575                    | V    |

|                                   | I/O buffers (1.35 V) power supply                                        |           | 1.283                    | 1.35    | 1.45                     | V    |

|                                   | I/O buffers (1.25 V) power supply                                        |           | 1.19                     | 1.25    | 1.31                     | V    |

|                                   | I/O buffers (1.2 V) power supply                                         |           | 1.14                     | 1.2     | 1.26                     | V    |

|                                   | Configuration pins (3.0 V) power supply                                  |           | 2.85                     | 3.0     | 3.15                     | V    |

| V <sub>CCPGM</sub>                | Configuration pins (2.5 V) power supply                                  |           | 2.375                    | 2.5     | 2.625                    | V    |

|                                   | Configuration pins (1.8 V) power supply                                  | _         | 1.71                     | 1.8     | 1.89                     | V    |

| V <sub>CCA</sub> _                | PLL analog voltage regulator power supply                                | -         | 2.375                    | 2.5     | 2.625                    | V    |

| V <sub>CCD</sub><br>FPLL          | PLL digital voltage regulator power supply                               | _         | 1.45                     | 1.5     | 1.55                     | V    |

| V <sub>CCBAT</sub> (117           | Battery back-up power supply (For design security volatile key register) | _         | 1.2                      | —       | 3.0                      | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements.

Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(116)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.

<sup>(117)</sup> If you do not use the design security feature in Arria V GZ devices, connect V<sub>CCBAT</sub> to a 1.2- to 3.0-V power supply. Arria V GZ power-on-reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V GZ devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

| Symbol                                 | Description                                         | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |

|----------------------------------------|-----------------------------------------------------|--------------------------|---------|--------------------------|------|

|                                        | Receiver analog power supply (left side)            | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCR_GXBL</sub> <sup>(121)</sup> |                                                     | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCR_GXBR</sub> <sup>(121)</sup> | Receiver analog power supply (right side)           | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        | Transmitter analog power supply (left side)         | 0.82                     | 0.85    | 0.88                     | V    |

| V <sub>CCT_GXBL</sub> <sup>(121)</sup> |                                                     | 0.97                     | 1.0     | 1.03                     |      |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

|                                        | Transmitter analog power supply (right side)        | 0.82                     | 0.85    | 0.88                     |      |

| V <sub>CCT_GXBR</sub> <sup>(121)</sup> |                                                     | 0.97                     | 1.0     | 1.03                     | V    |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |

| V <sub>CCH_GXBL</sub>                  | Transmitter output buffer power supply (left side)  | 1.425                    | 1.5     | 1.575                    | V    |

| V <sub>CCH_GXBR</sub>                  | Transmitter output buffer power supply (right side) | 1.425                    | 1.5     | 1.575                    | V    |

<sup>&</sup>lt;sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(121)</sup> This supply must be connected to 1.0 V if the transceiver is configured at a data rate > 6.5 Gbps, and to 1.05 V if configured at a data rate > 10.3 Gbps when DFE is used. For data rate up to 6.5 Gbps, you can connect this supply to 0.85 V.

| Symbol                                                                                    | Description                                                                                                                        | Conditions                                    | Calibration Accuracy |               | Unit |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------|---------------|------|

| Symbol                                                                                    | Description                                                                                                                        | Conditions                                    | C3, I3L              | C4, I4        | Onic |

| 25-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (25- $\Omega$ setting)                                                                | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15                  | ±15           | %    |

| 50-Ω R <sub>S</sub>                                                                       | Internal series termination with calibration (50- $\Omega$ setting)                                                                | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15                  | ±15           | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>                                              | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                               | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2 V    | ±15                  | ±15           | %    |

| 48-Ω, 60-Ω, 80-Ω, and<br>240-Ω R <sub>S</sub>                                             | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)              | $V_{CCIO} = 1.2 V$                            | ±15                  | ±15           | %    |

| 50-Ω R <sub>T</sub>                                                                       | Internal parallel termination with calibration (50- $\Omega$ setting)                                                              | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2 V      | -10 to +40           | -10 to<br>+40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ $R_{\rm T}$ | Internal parallel termination with calibration ( $20-\Omega$ , $30-\Omega$ , $40-\Omega$ , $60-\Omega$ , and $120-\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25 V         | -10 to +40           | -10 to<br>+40 | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_{\rm T}$                                                | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                            | $V_{CCIO} = 1.2$                              | -10 to +40           | -10 to<br>+40 | %    |

| 25- $\Omega R_{S\_left\_shift}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                           | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 V | ±15                  | ±15           | %    |

# Table 2-11: OCT Without Calibration Resistance Tolerance Specifications for Arria V GZ Devices

| Symbol | Description                                                            | Conditions                        | Resistance Tolerance |        | - Unit |

|--------|------------------------------------------------------------------------|-----------------------------------|----------------------|--------|--------|

|        | Description                                                            | Conditions                        | C3, I3L              | C4, I4 | Onit   |

| - 8    | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0 and 2.5 V | ±40                  | ±40    | %      |

| Symbol                                                       | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |

|--------------------------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|

|                                                              | 15                      | 300                        | 47                      | 940                        |

|                                                              | 16                      | 320                        | 48                      | 960                        |

|                                                              | 17                      | 340                        | 49                      | 980                        |

|                                                              | 18                      | 360                        | 50                      | 1000                       |

|                                                              | 19                      | 380                        | 51                      | 1020                       |

|                                                              | 20                      | 400                        | 52                      | 1040                       |

|                                                              | 21                      | 420                        | 53                      | 1060                       |

|                                                              | 22                      | 440                        | 54                      | 1080                       |

| $\mathrm{V}_{\mathrm{OD}}$ differential peak to peak typical | 23                      | 460                        | 55                      | 1100                       |

|                                                              | 24                      | 480                        | 56                      | 1120                       |

|                                                              | 25                      | 500                        | 57                      | 1140                       |

|                                                              | 26                      | 520                        | 58                      | 1160                       |

|                                                              | 27                      | 540                        | 59                      | 1180                       |

|                                                              | 28                      | 560                        | 60                      | 1200                       |

|                                                              | 29                      | 580                        | 61                      | 1220                       |

|                                                              | 30                      | 600                        | 62                      | 1240                       |

|                                                              | 31                      | 620                        | 63                      | 1260                       |

#### 2-44 Periphery Performance

| Description           | Min   | Тур   | Max   | Unit |

|-----------------------|-------|-------|-------|------|

| Diode ideality factor | 1.006 | 1.008 | 1.010 | —    |

# **Periphery Performance**

I/O performance supports several system interfaces, such as the **LVDS** high-speed I/O interface, external memory interface, and the **PCI/PCI-X** bus interface. General-purpose I/O standards such as 3.3-, 2.5-, 1.8-, and 1.5-**LVTTL/LVCMOS** are capable of a typical 167 MHz and 1.2-**LVCMOS** at 100 MHz interfacing frequency with a 10 pF load.

**Note:** The actual achievable frequency depends on design- and system-specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

### High-Speed I/O Specification

**High-Speed Clock Specifications**

#### Table 2-39: High-Speed Clock Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

Arria V GZ devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 230 Mbps

- True mini-LVDS output standard with data rates of up to 340 Mbps

#### 2-50 Soft CDR Mode High-Speed I/O Specifications

| Standard           | Training Pattern | Number of Data Transitions<br>in One Repetition of the<br>Training Pattern | Number of Repetitions per 256 Data Transitions (201) | Maximum              |

|--------------------|------------------|----------------------------------------------------------------------------|------------------------------------------------------|----------------------|

| Parallel Rapid I/O | 00001111         | 2                                                                          | 128                                                  | 640 data transitions |

| r araner Rapid 1/0 | 10010000         | 4                                                                          | 64                                                   | 640 data transitions |

| Miscellaneous      | 10101010         | 8                                                                          | 32                                                   | 640 data transitions |

|                    | 01010101         | 8                                                                          | 32                                                   | 640 data transitions |

## Soft CDR Mode High-Speed I/O Specifications

#### Table 2-44: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol                 | Conditions | C3, I3L |     |     | C4, I4 |     |     | Unit  |

|------------------------|------------|---------|-----|-----|--------|-----|-----|-------|

|                        | Conditions | Min     | Тур | Мах | Min    | Тур | Мах | Onic  |

| Soft-CDR ppm tolerance | —          |         | _   | 300 |        | —   | 300 | ± ppm |

<sup>&</sup>lt;sup>(201)</sup> This is the number of repetitions for the stated training pattern to achieve the 256 data transitions.

# FPP Configuration Timing when DCLK to DATA[] > 1

#### Figure 2-8: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1,

t<sub>CF2ST1</sub> tcfg ;↔ nCONFIG ŤĊF2CK nSTATUS (3) 🕳 tstatus tCF2ST0 CONF\_DONE (4) TCL tCH tsT2CK ŤĊF2CD (8) DCLK (6) (7) 1 2 ••• r 2 ••• r 1  $\mathbf{D}$ (5) tCLK DATA[31..0] (8) Word 0 Word User Mode Word 3 • • • Word (n-1) tDH tDH tpsy High-Z User I/O User Mode INIT DONE (9) tCD2UM

Timing when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. To find out the DCLK-to-DATA[] ratio for your system, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 2. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 3. After power-up, the Arria V GZ device holds nSTATUS low for the time as specified by the POR delay.

- 4. After power-up, before and during configuration, CONF\_DONE is low.

- 5. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 6. "r" denotes the DCLK-to-DATA[] ratio. For the DCLK-to-DATA[] ratio based on the decompression and the design security feature enable settings, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 7. If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA[31.0] pins prior to sending the first DCLK rising edge.

- 8. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 9. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.

#### Table 2-57: FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is >1

Use these timing parameters when you use the decompression and design security features.

| Symbol                              | Parameter                                    | Minimum                                | Maximum     | Unit |

|-------------------------------------|----------------------------------------------|----------------------------------------|-------------|------|

| t <sub>CF2CD</sub>                  | nconfig low to conf_done low                 | -                                      | 600         | ns   |

| t <sub>CF2ST0</sub>                 | nconfig low to nstatus low                   | -                                      | 600         | ns   |

| t <sub>CFG</sub>                    | nCONFIG low pulse width                      | 2                                      | _           | μs   |

| t <sub>STATUS</sub>                 | nSTATUS low pulse width                      | 268                                    | 1,506 (210) | μs   |

| t <sub>CF2ST1</sub>                 | nCONFIG high to nSTATUS high                 | —                                      | 1,506 (211) | μs   |

| t <sub>CF2CK</sub> <sup>(212)</sup> | nCONFIG high to first rising edge on DCLK    | 1,506                                  |             | μs   |

| t <sub>ST2CK</sub> <sup>(212)</sup> | nSTATUS high to first rising edge of DCLK    | 2                                      | _           | μs   |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK | 5.5                                    |             | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK   | N-1/f <sub>DCLK</sub> <sup>(213)</sup> | _           | S    |

| t <sub>CH</sub>                     | DCLK high time                               | $0.45 	imes 1/f_{MAX}$                 | _           | S    |

| t <sub>CL</sub>                     | DCLK low time                                | $0.45 \times 1/f_{MAX}$                | _           | S    |

| t <sub>CLK</sub>                    | DCLK period                                  | 1/f <sub>MAX</sub>                     |             | S    |

| £                                   | DCLK frequency (FPP ×8/×16)                  | -                                      | 125         | MHz  |

| $f_{MAX}$                           | DCLK frequency (FPP ×32)                     | -                                      | 100         | MHz  |

| t <sub>R</sub>                      | Input rise time                              | -                                      | 40          | ns   |

| t <sub>F</sub>                      | Input fall time                              | -                                      | 40          | ns   |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(214)</sup> | 175                                    | 437         | μs   |

<sup>(210)</sup> You can obtain this value if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>(211)</sup> You can obtain this value if you do not delay configuration by externally holding the nSTATUS low.

$^{(212)}$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

$^{(213)}$  N is the DCLK-to-DATA ratio and  $f_{DCLK}$  is the DCLK frequency the system is operating.

<sup>(214)</sup> The minimum and maximum numbers apply only if you use the internal oscillator as the clock source for initializing the device.

Arria V GZ Device Datasheet

**Altera Corporation**

#### Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                      | Parameter                                         | Minimum                                    | Maximum     | Unit |

|-----------------------------|---------------------------------------------------|--------------------------------------------|-------------|------|

| t <sub>CF2CD</sub>          | nCONFIG low to CONF_DONE low                      | —                                          | 600         | ns   |

| t <sub>CF2ST0</sub>         | nCONFIG low to nSTATUS low                        | _                                          | 600         | ns   |

| t <sub>CFG</sub>            | nCONFIG low pulse width                           | 2                                          |             | μs   |

| t <sub>STATUS</sub>         | nSTATUS low pulse width                           | 268                                        | 1,506 (217) | μs   |

| t <sub>CF2ST1</sub>         | nCONFIG high to nSTATUS high                      | _                                          | 1,506 (218) | μs   |

| t <sub>CF2CK</sub><br>(219) | nCONFIG high to first rising edge on DCLK         | 1,506                                      | _           | μs   |

| t <sub>ST2CK</sub> (219)    | nSTATUS high to first rising edge of DCLK         | 2                                          |             | μs   |

| t <sub>DSU</sub>            | DATA[] setup time before rising edge on DCLK      | 5.5                                        |             | ns   |

| t <sub>DH</sub>             | DATA[] hold time after rising edge on DCLK        | 0                                          | _           | ns   |

| t <sub>CH</sub>             | DCLK high time                                    | $0.45 	imes 1/f_{MAX}$                     |             | s    |

| t <sub>CL</sub>             | DCLK low time                                     | $0.45 	imes 1/f_{MAX}$                     | —           | S    |

| t <sub>CLK</sub>            | DCLK period                                       | 1/f <sub>MAX</sub>                         |             | s    |

| f <sub>MAX</sub>            | DCLK frequency                                    | _                                          | 125         | MHz  |

| t <sub>CD2UM</sub>          | CONF_DONE high to user mode <sup>(220)</sup>      | 175                                        | 437         | μs   |

| t <sub>CD2CU</sub>          | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period      | _           |      |

| t <sub>CD2UMC</sub>         | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) (221) | _           | —    |

<sup>&</sup>lt;sup>(217)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>&</sup>lt;sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

| Term               | Definition                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OCM</sub>   | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                        |

| V <sub>OD</sub>    | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the transmitter. |

| V <sub>SWING</sub> | Differential input voltage                                                                                                                                       |

| V <sub>X</sub>     | Input differential cross point voltage                                                                                                                           |

| V <sub>OX</sub>    | Output differential cross point voltage                                                                                                                          |

| W                  | High-speed I/O block—clock boost factor                                                                                                                          |

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                      |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2017 | 2017.02.10 | • Changed the minimum value for t <sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the DCLK-to-DATA[] Ratio is 1" table.                          |

|               |            | <ul> <li>Changed the minimum value for t<sub>CD2UMC</sub> in the "FPP Timing Parameters for Arria V GZ Devices When the<br/>DCLK-to-DATA[] Ratio is &gt;1" table.</li> </ul> |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "AS Timing Parameters for AS x1 and AS x4 Configurations in Arria V GZ Devices" table.                            |

|               |            | • Changed the minimum value for t <sub>CD2UMC</sub> in the "PS Timing Parameters for Arria V GZ Devices" table.                                                              |

|               |            | <ul> <li>Changed the minimum number of clock cycles value in the "Initialization Clock Source Option and the<br/>Maximum Frequency for Arria V GZ Devices" table.</li> </ul> |