# E·XFL

## Intel - 5ASTFD5K3F40I3NES Datasheet

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Obsolete                                                                   |

|-------------------------|----------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup>       |

| Flash Size              | -                                                                          |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 1.05GHz                                                                    |

| Primary Attributes      | FPGA - 462K Logic Elements                                                 |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                         |

| Package / Case          | 1517-BBGA, FCBGA                                                           |

| Supplier Device Package | 1517-FBGA, FC (40x40)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5astfd5k3f40i3nes               |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Arria V GX, GT, SX, and ST Device Datasheet

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Arria® V devices.

Arria V devices are offered in commercial and industrial grades. Commercial devices are offered in -C4 (fastest), -C5, and -C6 speed grades. Industrial grade devices are offered in the -I3 and -I5 speed grades.

#### **Related Information**

#### Arria V Device Overview

Provides more information about the densities and packages of devices in the Arria V family.

# **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Arria V devices.

## **Operating Conditions**

Arria V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Arria V devices, you must consider the operating requirements described in this section.

## **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Arria V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

<sup>©</sup> 2017 Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, NIOS, Quartus and Stratix words and logos are trademarks of Intel Corporation in the US and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Symbol                     | Description                    | Minimum | Maximum | Unit |

|----------------------------|--------------------------------|---------|---------|------|

| V <sub>CCPLL_HPS</sub>     | HPS PLL analog power supply    | -0.50   | 3.25    | V    |

| V <sub>CC_AUX_SHARED</sub> | HPS auxiliary power supply     | -0.50   | 3.25    | V    |

| I <sub>OUT</sub>           | DC output current per pin      | -25     | 40      | mA   |

| T <sub>J</sub>             | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub>           | Storage temperature (no bias)  | -65     | 150     | °C   |

## Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for ~15% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

#### Table 1-2: Maximum Allowed Overshoot During Transitions for Arria V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

1-3

#### 1-4 Recommended Operating Conditions

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit |

|---------|------------------|---------------|--------------------------------------|------|

|         |                  | 3.8           | 100                                  | %    |

|         |                  | 3.85          | 68                                   | %    |

|         |                  | 3.9           | 45                                   | %    |

|         |                  | 3.95          | 28                                   | %    |

|         |                  | 4             | 15                                   | %    |

|         |                  | 4.05          | 13                                   | %    |

|         |                  | 4.1           | 11                                   | %    |

|         |                  | 4.15          | 9                                    | %    |

| Vi (AC) | AC input voltage | 4.2           | 8                                    | %    |

|         |                  | 4.25          | 7                                    | %    |

|         |                  | 4.3           | 5.4                                  | %    |

|         |                  | 4.35          | 3.2                                  | %    |

|         |                  | 4.4           | 1.9                                  | %    |

|         |                  | 4.45          | 1.1                                  | %    |

|         |                  | 4.5           | 0.6                                  | %    |

|         |                  | 4.55          | 0.4                                  | %    |

|         |                  | 4.6           | 0.2                                  | %    |

## **Recommended Operating Conditions**

This section lists the functional operation limits for the AC and DC parameters for Arria V devices.

#### **Recommended Operating Conditions**

### Table 1-3: Recommended Operating Conditions for Arria V Devices

This table lists the steady-state voltage values expected from Arria V devices. Power supply ramps must all be strictly monotonic, without plateaus.

#### I/O Pin Leakage Current

## Table 1-6: I/O Pin Leakage Current for Arria V Devices

| Symbol          | Description        | Condition                      | Min | Тур | Max | Unit |

|-----------------|--------------------|--------------------------------|-----|-----|-----|------|

| II              | Input pin          | $V_{I} = 0 V$ to $V_{CCIOMAX}$ | -30 | —   | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$ | -30 |     | 30  | μΑ   |

### **Bus Hold Specifications**

#### Table 1-7: Bus Hold Parameters for Arria V Devices

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

|                                             |                   |                                                             |     |      | 1   | 0    |     | V <sub>CCI</sub> | <sub>D</sub> (V) |      |     |      |     |      |      |

|---------------------------------------------|-------------------|-------------------------------------------------------------|-----|------|-----|------|-----|------------------|------------------|------|-----|------|-----|------|------|

| Parameter                                   | Symbol            | Condition                                                   | 1   | .2   | 1   | .5   | 1   | .8               | 2                | .5   | 3   | .0   | 3.  | .3   | Unit |

|                                             |                   |                                                             | Min | Max  | Min | Max  | Min | Max              | Min              | Max  | Min | Max  | Min | Max  |      |

| Bus-hold,<br>low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max)                  | 8   |      | 12  |      | 30  |                  | 50               |      | 70  |      | 70  | _    | μΑ   |

| Bus-hold,<br>high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min)                  | -8  |      | -12 |      | -30 |                  | -50              |      | -70 |      | -70 | _    | μΑ   |

| Bus-hold,<br>low,<br>overdrive<br>current   | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{IN} \\ < V_{CCIO} \end{array}$ | _   | 125  |     | 175  | _   | 200              |                  | 300  | _   | 500  |     | 500  | μΑ   |

| Bus-hold,<br>high,<br>overdrive<br>current  | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub>               | _   | -125 |     | -175 |     | -200             | _                | -300 |     | -500 |     | -500 | μΑ   |

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

AV-51002 2017.02.10

## I/O Standard Specifications

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

## Single-Ended I/O Standards

| I/O Standard    |       | V <sub>CCIO</sub> (V) |       |      | V <sub>IL</sub> (V)    | V <sub>IH</sub>        | (V)              | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |

|-----------------|-------|-----------------------|-------|------|------------------------|------------------------|------------------|------------------------|--------------------------|---------------------------------|--------------------------------------|

| I/O Stanuaru    | Min   | Тур                   | Max   | Min  | Мах                    | Min                    | Max              | Мах                    | Min                      | (mA)                            | IOH, (IIIA)                          |

| 3.3-V<br>LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.45                   | 2.4                      | 4                               | -4                                   |

| 3.3-V<br>LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 2                               | -2                                   |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.4                    | 2.4                      | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 0.1                             | -0.1                                 |

| 3.0-V PCI       | 2.85  | 3                     | 3.15  | _    | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 3.0-V<br>PCI-X  | 2.85  | 3                     | 3.15  |      | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                    | 1.7                    | 3.6              | 0.4                    | 2                        | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> – 0.45 | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575 | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

Table 1-14: Single-Ended I/O Standards for Arria V Devices

(13) To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

| I/O Standard | V <sub>CCIO</sub> (V) V <sub>SWING(I</sub> |      | <sub>ING(DC)</sub> (V) |      | V <sub>X(AC)</sub> (V) | V <sub>SWING(AC)</sub> (V)     |                      |                                |                                               |                           |

|--------------|--------------------------------------------|------|------------------------|------|------------------------|--------------------------------|----------------------|--------------------------------|-----------------------------------------------|---------------------------|

|              | Min                                        | Тур  | Max                    | Min  | Мах                    | Min                            | Тур                  | Мах                            | Min                                           | Max                       |

| SSTL-125     | 1.19                                       | 1.25 | 1.31                   | 0.18 | (15)                   | V <sub>CCIO</sub> /2 –<br>0.15 | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15 | 2(V <sub>IH(AC)</sub> –<br>V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |

## **Differential HSTL and HSUL I/O Standards**

## Table 1-18: Differential HSTL and HSUL I/O Standards for Arria V Devices

| I/O Standard           |       |     | )     | V <sub>DIF(DC)</sub> (V) |                            | V <sub>X(AC)</sub> (V)                                              |                          |                              |                           | $V_{CM(DC)}(V)$          | V <sub>DIF(AC)</sub> (V)   |      |                          |

|------------------------|-------|-----|-------|--------------------------|----------------------------|---------------------------------------------------------------------|--------------------------|------------------------------|---------------------------|--------------------------|----------------------------|------|--------------------------|

|                        | Min   | Тур | Max   | Min                      | Max                        | Min                                                                 | Тур                      | Max                          | Min                       | Тур                      | Max                        | Min  | Max                      |

| HSTL-18<br>Class I, II | 1.71  | 1.8 | 1.89  | 0.2                      | _                          | 0.78                                                                | —                        | 1.12                         | 0.78                      |                          | 1.12                       | 0.4  |                          |

| HSTL-15<br>Class I, II | 1.425 | 1.5 | 1.575 | 0.2                      | _                          | 0.68                                                                | —                        | 0.9                          | 0.68                      |                          | 0.9                        | 0.4  |                          |

| HSTL-12<br>Class I, II | 1.14  | 1.2 | 1.26  | 0.16                     | V <sub>CCIO</sub><br>+ 0.3 |                                                                     | $0.5 \times V_{ m CCIO}$ | _                            | $0.4 \times V_{ m CCIO}$  | $0.5 \times V_{ m CCIO}$ | $0.6 \times V_{ m CCIO}$   | 0.3  | V <sub>CCIO</sub> + 0.48 |

| HSUL-12                | 1.14  | 1.2 | 1.3   | 0.26                     | 0.26                       | $\begin{array}{c} 0.5 \times \\ V_{\rm CCIO} - \\ 0.12 \end{array}$ | $0.5 	imes V_{ m CCIO}$  | $0.5 \times V_{CCIO} + 0.12$ | $0.4 \times V_{\rm CCIO}$ | $0.5 \times V_{ m CCIO}$ | 0.6 ×<br>V <sub>CCIO</sub> | 0.44 | 0.44                     |

## **Differential I/O Standard Specifications**

## Table 1-19: Differential I/O Standard Specifications for Arria V Devices

Differential inputs are powered by  $V_{CCPD}$  which requires 2.5 V.

| I/O Standard                       |                                                                                                                                                                                                                                             |     | )     |         | V <sub>ID</sub> (mV) <sup>(16)</sup> |      |                                | $V_{ICM(DC)}(V)$                |       | V <sub>OD</sub> (V) <sup>(17)</sup> |     |     | V <sub>OCM</sub> (V) <sup>(17)(18)</sup> |      |       |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------|--------------------------------------|------|--------------------------------|---------------------------------|-------|-------------------------------------|-----|-----|------------------------------------------|------|-------|

|                                    | Min                                                                                                                                                                                                                                         | Тур | Мах   | Min     | Condition                            | Мах  | Min                            | Condition                       | Мах   | Min                                 | Тур | Max | Min                                      | Тур  | Max   |

| PCML                               | Transmitter, receiver, and input reference clock pins of high-speed transceivers use the PCML I/O reference clock I/O pin specifications, refer to Transceiver Specifications for Arria V GX and SX I for Arria V GT and ST Devices tables. |     |       |         |                                      |      |                                |                                 |       |                                     |     |     |                                          |      |       |

| 2.5 V                              | 2.375                                                                                                                                                                                                                                       | 2.5 | 2.625 | 100     | V <sub>CM</sub> =                    |      | 0.05                           | D <sub>MAX</sub> ≤<br>1.25 Gbps | 1.80  | 0.247                               |     | 0.6 | 1.125                                    | 1.25 | 1.375 |

| LVDS <sup>(19)</sup>               | 2.375                                                                                                                                                                                                                                       | 2.3 | 2.023 | 100     | 1.25 V                               |      | 1.05                           | D <sub>MAX</sub> ><br>1.25 Gbps | 1.55  | 0.217                               |     | 0.0 | 1.123                                    | 1.25 | 1.575 |

| RSDS<br>(HIO) <sup>(20)</sup>      | 2.375                                                                                                                                                                                                                                       | 2.5 | 2.625 | 100     | V <sub>CM</sub> =<br>1.25 V          |      | 0.25                           |                                 | 1.45  | 0.1                                 | 0.2 | 0.6 | 0.5                                      | 1.2  | 1.4   |

| Mini-LVDS<br>(HIO) <sup>(21)</sup> | 2.375                                                                                                                                                                                                                                       | 2.5 | 2.625 | 200     |                                      | 600  | 0.300                          |                                 | 1.425 | 0.25                                | _   | 0.6 | 1                                        | 1.2  | 1.4   |

| LVPECL <sup>(22)</sup>             |                                                                                                                                                                                                                                             |     |       | 300     |                                      |      | 0.60                           | D <sub>MAX</sub> ≤<br>700 Mbps  | 1.80  |                                     |     |     |                                          |      |       |

|                                    |                                                                                                                                                                                                                                             |     |       | 500 — — |                                      | 1.00 | D <sub>MAX</sub> ><br>700 Mbps | 1.60                            |       | _                                   |     |     |                                          |      |       |

#### **Related Information**

- Transceiver Specifications for Arria V GX and SX Devices on page 1-23 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

- $^{(16)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

- <sup>(17)</sup>  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

- <sup>(18)</sup> This applies to default pre-emphasis setting only.

- <sup>(19)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 1.25 Gbps and 0 V to 1.85 V for data rates below 1.25 Gbps.

- <sup>(20)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(21)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.425 V.

- <sup>(22)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

| Symbol/Description                                                                 | Condition -        | Transc | eiver Speed G | irade 4 | Transc | Unit |     |      |

|------------------------------------------------------------------------------------|--------------------|--------|---------------|---------|--------|------|-----|------|

|                                                                                    |                    | Min    | Тур           | Max     | Min    | Тур  | Max | Unit |

| Inter-transceiver block<br>transmitter channel-to-<br>channel skew <sup>(39)</sup> | ×N PMA bonded mode | _      | _             | 500     | _      | _    | 500 | ps   |

#### Table 1-24: CMU PLL Specifications for Arria V GX and SX Devices

| Symbol/Description        | Transceiver S | peed Grade 4 | Transceiver S | peed Grade 6 | Unit |

|---------------------------|---------------|--------------|---------------|--------------|------|

| Symbol/Description        | Min           | Мах          | Min           | Мах          | Onit |

| Supported data range      | 611           | 6553.6       | 611           | 3125         | Mbps |

| fPLL supported data range | 611           | 3125         | 611           | 3125         | Mbps |

## Table 1-25: Transceiver-FPGA Fabric Interface Specifications for Arria V GX and SX Devices

| Symbol/Description                  | Transceiver Spee | ed Grade 4 and 6 | Unit |

|-------------------------------------|------------------|------------------|------|

| Symbol/Description                  | Min              | Мах              | Unit |

| Interface speed (single-width mode) | 25               | 187.5            | MHz  |

| Interface speed (double-width mode) | 25               | 163.84           | MHz  |

#### **Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates  $\leq$  3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

- Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines Provides more information about the power supply connection for different data rates.

<sup>&</sup>lt;sup>(39)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

## **Memory Output Clock Jitter Specifications**

#### Table 1-45: Memory Output Clock Jitter Specifications for Arria V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard. The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER)  $10^{-12}$ , equivalent to 14 sigma. Altera recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -I3, | -C4 | –15, | -C5 | -(  | 6   | Unit |

|------------------------------|---------------|-----------------------|------|-----|------|-----|-----|-----|------|

|                              |               | Symbol                | Min  | Max | Min  | Max | Min | Max | Unit |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -41  | 41  | -50  | 50  | -55 | 55  | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | 63   |     | 9    | 0   | 94  |     | ps   |

## **OCT Calibration Block Specifications**

### Table 1-46: OCT Calibration Block Specifications for Arria V Devices

| Symbol                | Description                                                                                                                                           | Min | Тур  | Max | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by OCT calibration blocks                                                                                                              |     |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of octus<br>RCLK clock cycles required for $R_S$ OCT/ $R_T$ OCT calibration                                                                    |     | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of octusrclk clock cycles required for oct code to shift out                                                                                   |     | 32   |     | Cycles |

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between $R_S$ OCT and $R_T$ OCT | _   | 2.5  | _   | ns     |

AV-51002 2017.02.10

The Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

#### Arria V I/O Timing Spreadsheet

Provides the Arria V Excel-based I/O timing spreadsheet.

## Programmable IOE Delay

| Parameter <sup>(112</sup> Available<br>) Settings | Available Minimum |                         | Fast Model |            | Slow Model |       |       |       | - Unit |      |

|---------------------------------------------------|-------------------|-------------------------|------------|------------|------------|-------|-------|-------|--------|------|

|                                                   | Settings          | Offset <sup>(113)</sup> | Industrial | Commercial | -C4        | -C5   | -C6   | -13   | -15    | Onit |

| D1                                                | 32                | 0                       | 0.508      | 0.517      | 0.870      | 1.063 | 1.063 | 0.872 | 1.057  | ns   |

| D3                                                | 8                 | 0                       | 1.763      | 1.795      | 2.999      | 3.496 | 3.571 | 3.031 | 3.643  | ns   |

| D4                                                | 32                | 0                       | 0.508      | 0.518      | 0.869      | 1.063 | 1.063 | 1.063 | 1.057  | ns   |

| D5                                                | 32                | 0                       | 0.508      | 0.517      | 0.870      | 1.063 | 1.063 | 0.872 | 1.057  | ns   |

## Table 1-76: I/O element (IOE) Programmable Delay for Arria V Devices

# Programmable Output Buffer Delay

## Table 1-77: Programmable Output Buffer Delay for Arria V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

<sup>&</sup>lt;sup>(112)</sup> You can set this value in the Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of **Assignment Editor**.

<sup>&</sup>lt;sup>(113)</sup> Minimum offset does not include the intrinsic delay.

| Symbol           | Description                    | Minimum | Maximum | Unit |

|------------------|--------------------------------|---------|---------|------|

| VI               | DC input voltage               | -0.5    | 3.8     | V    |

| T <sub>J</sub>   | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub> | Storage temperature (No bias)  | -65     | 150     | °C   |

| I <sub>OUT</sub> | DC output current per pin      | -25     | 40      | mA   |

## Table 2-3: Transceiver Power Supply Absolute Conditions for Arria V GZ Devices

| Symbol                | Description                                         | Minimum | Maximum | Unit |

|-----------------------|-----------------------------------------------------|---------|---------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)    | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)   | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)        | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)        | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)  | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side) | -0.5    | 1.8     | V    |

## Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage shown in the following table. They may also undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Symbol                            | Description                                                              | Condition | Minimum <sup>(114)</sup> | Typical                                       | Maximum <sup>(114)</sup>                                                                                                                                                                                                                                                                                                                                          | Unit |

|-----------------------------------|--------------------------------------------------------------------------|-----------|--------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>CCPT</sub>                 | Power supply for programmable power technology                           | _         | 1.45                     | 1.50                                          | 1.55                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>CC_AUX</sub>               | Auxiliary supply for the programmable power technology                   | _         | 2.375                    | 2.5                                           | 2.625                                                                                                                                                                                                                                                                                                                                                             | V    |

| V <sub>CCPD</sub> <sup>(116</sup> | I/O pre-driver (3.0 V) power supply                                      |           | 2.85                     | 3.0                                           | 3.15                                                                                                                                                                                                                                                                                                                                                              | V    |

| )                                 | I/O pre-driver (2.5 V) power supply                                      |           | 2.375                    | 1.50         1.55           2.5         2.625 | V                                                                                                                                                                                                                                                                                                                                                                 |      |

|                                   | I/O buffers (3.0 V) power supply                                         | _         | 2.85                     | 3.0                                           | 3.15                                                                                                                                                                                                                                                                                                                                                              | V    |

|                                   | I/O buffers (2.5 V) power supply                                         |           | 2.375                    | 2.5                                           | 2.625                                                                                                                                                                                                                                                                                                                                                             | V    |

|                                   | I/O buffers (1.8 V) power supply                                         |           | 1.71                     | 1.8                                           | 1.89                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>CCIO</sub>                 | I/O buffers (1.5 V) power supply                                         | _         | 1.425                    | 1.5                                           | 1.575                                                                                                                                                                                                                                                                                                                                                             | V    |

|                                   | I/O buffers (1.35 V) power supply                                        | _         | 1.283                    | 1.35                                          | 1.45                                                                                                                                                                                                                                                                                                                                                              | V    |

|                                   | I/O buffers (1.25 V) power supply                                        | _         | 1.19                     | 1.25                                          | 1.31                                                                                                                                                                                                                                                                                                                                                              | V    |

|                                   | I/O buffers (1.2 V) power supply                                         | _         | 1.14                     | 1.2                                           | 1.55         2.625         3.15         2.625         3.15         2.625         3.15         2.625         1.89         1.575         1.45         1.31         1.26         3.15         2.625         1.89         1.26         3.15         2.625         1.89         2.625         1.89         2.625         1.89         2.625         1.89         2.625 | V    |

|                                   | Configuration pins (3.0 V) power supply                                  | _         | 2.85                     | 3.0                                           | 3.15                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>CCPGM</sub>                | Configuration pins (2.5 V) power supply                                  | _         | 2.375                    | 2.5                                           | 2.625                                                                                                                                                                                                                                                                                                                                                             | V    |

|                                   | Configuration pins (1.8 V) power supply                                  | _         | 1.71                     | 1.8                                           | 1.89                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>CCA</sub> _                | PLL analog voltage regulator power supply                                | _         | 2.375                    | 2.5                                           | 2.625                                                                                                                                                                                                                                                                                                                                                             | V    |

| V <sub>CCD</sub><br>FPLL          | PLL digital voltage regulator power supply                               | _         | 1.45                     | 1.5                                           | 1.55                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>CCBAT</sub> (117           | Battery back-up power supply (For design security volatile key register) | _         | 1.2                      | —                                             | 3.0                                                                                                                                                                                                                                                                                                                                                               | V    |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements.

Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(116)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.

<sup>(117)</sup> If you do not use the design security feature in Arria V GZ devices, connect V<sub>CCBAT</sub> to a 1.2- to 3.0-V power supply. Arria V GZ power-on-reset (POR) circuitry monitors V<sub>CCBAT</sub>. Arria V GZ devices do not exit POR if V<sub>CCBAT</sub> is not powered up.

| Symbol            | Description                    | Condition    | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-------------------|--------------------------------|--------------|--------------------------|---------|--------------------------|------|

| VI                | DC input voltage               |              | -0.5                     | _       | 3.6                      | V    |

| V <sub>O</sub>    | Output voltage                 |              | 0                        | _       | V <sub>CCIO</sub>        | V    |

| TI                | Operating junction temperature | Commercial   | 0                        |         | 85                       | °C   |

| ıj                | Operating junction temperature | Industrial   | -40                      | _       | 100                      | °C   |

| t                 | Power supply ramp time         | Standard POR | 200 µs                   | _       | 100 ms                   | _    |

| t <sub>RAMP</sub> |                                | Fast POR     | 200 µs                   | _       | 4 ms                     | —    |

#### **Recommended Transceiver Power Supply Operating Conditions**

#### Table 2-6: Recommended Transceiver Power Supply Operating Conditions for Arria V GZ Devices

| Symbol                                                       | Description                                       | Minimum <sup>(118)</sup> | Typical       | Maximum <sup>(118)</sup> | Unit |  |

|--------------------------------------------------------------|---------------------------------------------------|--------------------------|---------------|--------------------------|------|--|

| V <sub>CCA_GXBL</sub>                                        | Transceiver channel PLL power supply (left side)  | 2.85                     | 3.0           | 3.15                     | V    |  |

| (119), (120)                                                 | Transcerver channel PLL power supply (left side)  | 2.375                    | 2.5           | 2.625                    |      |  |

| V <sub>CCA</sub> _                                           | Transceiver channel PLL power supply (right side) | 2.85                     | 2.85 3.0 3.15 |                          | V    |  |

| V <sub>CCA</sub><br>GXBR <sup>(119)</sup> , <sup>(120)</sup> | Transcerver channel PLL power supply (fight side) | 2.375                    | 2.5           | 2.625                    | v    |  |

| V <sub>CCHIP_L</sub>                                         | Transceiver hard IP power supply (left side)      | 0.82                     | 0.85          | 0.88                     | V    |  |

| V <sub>CCHSSI_L</sub>                                        | Transceiver PCS power supply (left side)          | 0.82                     | 0.85          | 0.88                     | V    |  |

| V <sub>CCHSSI_R</sub>                                        | Transceiver PCS power supply (right side)         | 0.82                     | 0.85          | 0.88                     | V    |  |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(120)</sup> When using ATX PLLs, the supply must be 3.0 V.

<sup>(119)</sup> This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

| Symbol               | Description                                                            | Conditions                 | Resistance | - Unit |      |  |

|----------------------|------------------------------------------------------------------------|----------------------------|------------|--------|------|--|

| Symbol               | Description                                                            | Conditions                 | C3, I3L    | C4, I4 | Onit |  |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | %    |  |

| 25-Ω R <sub>S</sub>  | Internal series termination without calibration (25- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | %    |  |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO}$ = 1.8 and 1.5 V | ±40        | ±40    | %    |  |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | $V_{CCIO} = 1.2 V$         | ±50        | ±50    | %    |  |

| 100-Ω R <sub>D</sub> | Internal differential termination (100- $\Omega$ setting)              | $V_{CCIO} = 2.5 V$         | ±25        | ±25    | %    |  |

#### Figure 2-1: OCT Variation Without Re-Calibration for Arria V GZ Devices

$$\mathbf{R}_{\text{OCT}} = \mathbf{R}_{\text{SCAL}} \left( 1 + \left( \frac{dR}{dT} \times \bigtriangleup T \right) \pm \left( \frac{dR}{dV} \times \bigtriangleup V \right) \right)$$

Notes:

1. The  $R_{oct}$  value shows the range of OCT resistance with the variation of temperature and  $V_{ccio}$ . 2.  $R_{scAL}$  is the OCT resistance value at power-up. 3.  $\Delta T$  is the variation of temperature with respect to the temperature at power-up. 4.  $\Delta V$  is the variation of voltage with respect to the  $V_{ccio}$  at power-up. 5. dR/dT is the percentage change of  $R_{scAL}$  with temperature. 6. dR/dV is the percentage change of  $R_{scAL}$  with voltage

6. dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

## Table 2-12: OCT Variation after Power-Up Calibration for Arria V GZ Devices

Valid for a V<sub>CCIO</sub> range of  $\pm$ 5% and a temperature range of 0° to 85°C.

AV-51002 2017.02.10

| I/O Standard            | V <sub>IL(D</sub> | <sub>C)</sub> (V)           | V <sub>IH(D0</sub>          | <sub>_)</sub> (V)           | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)         | L (m A)              | I (m A)              |

|-------------------------|-------------------|-----------------------------|-----------------------------|-----------------------------|--------------------------|--------------------------|----------------------------|-----------------------------|----------------------|----------------------|

| I/O Standard            | Min               | Max                         | Min                         | Max                         | Max                      | Min                      | Max                        | Min                         | l <sub>ol</sub> (mA) | l <sub>oh</sub> (mA) |

| SSTL-18<br>Class II     | -0.3              | V <sub>REF</sub> –<br>0.125 | V <sub>REF</sub><br>+ 0.125 | V <sub>CCIO</sub><br>+ 0.3  | V <sub>REF</sub> – 0.25  | V <sub>REF</sub> + 0.25  | 0.28                       | V <sub>CCIO</sub> –<br>0.28 | 13.4                 | -13.4                |

| SSTL-15<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{ m CCIO}$   | $0.8 \times V_{ m CCIO}$    | 8                    | -8                   |

| SSTL-15<br>Class II     | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | —                           | V <sub>REF</sub> – 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{\rm CCIO}$  | $0.8 \times V_{ m CCIO}$    | 16                   | -16                  |

| SSTL-135<br>Class I, II |                   | V <sub>REF</sub> –<br>0.09  | V <sub>REF</sub> + 0.09     | _                           | V <sub>REF</sub> – 0.16  | V <sub>REF</sub> + 0.16  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | —                    |

| SSTL-125<br>Class I, II | _                 | V <sub>REF</sub> –<br>0.85  | V <sub>REF</sub> + 0.85     | —                           | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | —                    |

| SSTL-12<br>Class I, II  | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | 0.2 * V <sub>CCIO</sub>    | 0.8 * V <sub>CCIO</sub>     | —                    | _                    |

| HSTL-18<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 8                    | -8                   |

| HSTL-18<br>Class II     |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 16                   | -16                  |

| HSTL-15<br>Class I      |                   | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 8                    | -8                   |

| HSTL-15<br>Class II     | _                 | V <sub>REF</sub> – 0.1      | V <sub>REF</sub> + 0.1      | _                           | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2   | 0.4                        | V <sub>CCIO</sub> – 0.4     | 16                   | -16                  |

| HSTL-12<br>Class I      | -0.15             | V <sub>REF</sub> –<br>0.08  | V <sub>REF</sub> + 0.08     | V <sub>CCIO</sub><br>+ 0.15 | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{\rm CCIO}$ | $0.75 \times V_{ m CCIO}$   | 8                    | -8                   |

| HSTL-12<br>Class II     | -0.15             | V <sub>REF</sub> –<br>0.08  | V <sub>REF</sub> + 0.08     | V <sub>CCIO</sub><br>+ 0.15 | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{\rm CCIO}$ | $0.75 \times V_{ m CCIO}$   | 16                   | -16                  |

| HSUL-12                 | —                 | V <sub>REF</sub> –<br>0.13  | V <sub>REF</sub> + 0.13     | —                           | V <sub>REF</sub> – 0.22  | V <sub>REF</sub> + 0.22  | $0.1 \times V_{\rm CCIO}$  | $0.9 \times V_{ m CCIO}$    | —                    | —                    |

Arria V GZ Device Datasheet

Altera Corporation

## **Typical VOD Settings**

| The tolerance is +/-20% for all VOD settings except for settings 2 and below. |                         |                            |                         |                            |  |  |  |  |

|-------------------------------------------------------------------------------|-------------------------|----------------------------|-------------------------|----------------------------|--|--|--|--|

| Symbol                                                                        | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting | V <sub>OD</sub> Value (mV) |  |  |  |  |

|                                                                               | 0 (166)                 | 0                          | 32                      | 640                        |  |  |  |  |

|                                                                               | 1 <sup>(166)</sup>      | 20                         | 33                      | 660                        |  |  |  |  |

|                                                                               | 2(166)                  | 40                         | 34                      | 680                        |  |  |  |  |

|                                                                               | 3(166)                  | 60                         | 35                      | 700                        |  |  |  |  |

|                                                                               | 4 <sup>(166)</sup>      | 80                         | 36                      | 720                        |  |  |  |  |

|                                                                               | 5 <sup>(166)</sup>      | 100                        | 37                      | 740                        |  |  |  |  |

|                                                                               | 6                       | 120                        | 38                      | 760                        |  |  |  |  |

| $ m V_{OD}$ differential peak to peak typical                                 | 7                       | 140                        | 39                      | 780                        |  |  |  |  |

|                                                                               | 8                       | 160                        | 40                      | 800                        |  |  |  |  |

|                                                                               | 9                       | 180                        | 41                      | 820                        |  |  |  |  |

|                                                                               | 10                      | 200                        | 42                      | 840                        |  |  |  |  |

|                                                                               | 11                      | 220                        | 43                      | 860                        |  |  |  |  |

|                                                                               | 12                      | 240                        | 44                      | 880                        |  |  |  |  |

|                                                                               | 13                      | 260                        | 45                      | 900                        |  |  |  |  |

|                                                                               | 14                      | 280                        | 46                      | 920                        |  |  |  |  |

<sup>(166)</sup> If TX termination resistance = 100  $\Omega$ , this VOD setting is illegal.

#### 2-44 Periphery Performance

| Description           | Min   | Тур   | Max   | Unit |

|-----------------------|-------|-------|-------|------|

| Diode ideality factor | 1.006 | 1.008 | 1.010 | —    |

## **Periphery Performance**

I/O performance supports several system interfaces, such as the **LVDS** high-speed I/O interface, external memory interface, and the **PCI/PCI-X** bus interface. General-purpose I/O standards such as 3.3-, 2.5-, 1.8-, and 1.5-**LVTTL/LVCMOS** are capable of a typical 167 MHz and 1.2-**LVCMOS** at 100 MHz interfacing frequency with a 10 pF load.

**Note:** The actual achievable frequency depends on design- and system-specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

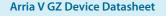

#### High-Speed I/O Specification

**High-Speed Clock Specifications**

#### Table 2-39: High-Speed Clock Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

For LVDS applications, you must use the PLLs in integer PLL mode.

Arria V GZ devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 230 Mbps

- True mini-LVDS output standard with data rates of up to 340 Mbps

### Non DPA Mode High-Speed I/O Specifications

#### Table 2-46: High-Speed I/O Specifications for Arria V GZ Devices

When J = 3 to 10, use the serializer/deserializer (SERDES) block.

When J = 1 or 2, bypass the SERDES block.

| Symbol          | Conditions | C3, I3L |     |     | C4, I4 |     |     | Unit |

|-----------------|------------|---------|-----|-----|--------|-----|-----|------|

|                 |            | Min     | Тур | Max | Min    | Тур | Мах | Onic |

| Sampling Window | _          |         |     | 300 |        |     | 300 | ps   |

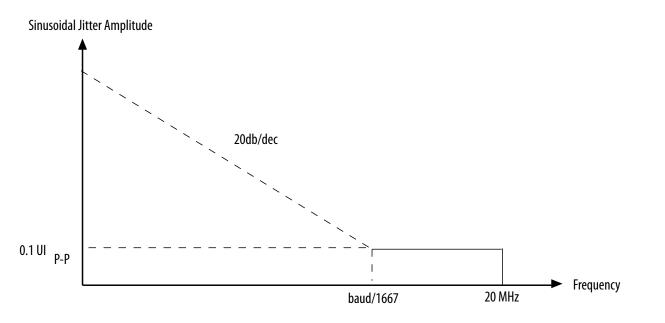

## **OCT Calibration Block Specifications**

## Table 2-51: OCT Calibration Block Specifications for Arria V GZ Devices

| Symbol                | Description                                                                                                                                                               | Min | Тур  | Мах | Unit   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| OCTUSRCLK             | Clock required by the OCT calibration blocks                                                                                                                              |     |      | 20  | MHz    |

| T <sub>OCTCAL</sub>   | Number of OCTUSRCLK clock cycles required for OCT R <sub>S</sub> /R <sub>T</sub> calibration                                                                              |     | 1000 |     | Cycles |

| T <sub>OCTSHIFT</sub> | Number of OCTUSRCLK clock cycles required for the OCT code to shift out                                                                                                   |     | 32   |     | Cycles |

| T <sub>RS_RT</sub>    | Time required between the dyn_term_ctrl and oe signal transitions in a bidirectional I/O buffer to dynamically switch between OCT $R_S$ and $R_T$ (See the figure below.) |     | 2.5  |     | ns     |

## Figure 2-6: Timing Diagram for oe and dyn\_term\_ctrl Signals

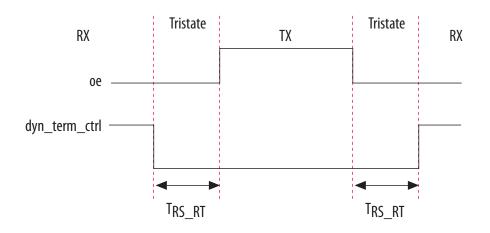

## FPP Configuration Timing when DCLK to DATA[] > 1

#### Figure 2-8: FPP Configuration Timing Waveform When the DCLK-to-DATA[] Ratio is >1,

t<sub>CF2ST1</sub> tcfg ;↔ nCONFIG ŤĊF2CK nSTATUS (3) 🕳 tstatus tCF2ST0 CONF\_DONE (4) TCL tCH tsT2CK ŤĊF2CD (8) DCLK (6) (7) 1 2 ••• r 2 ••• r 1  $\mathbf{D}$ (5) tCLK DATA[31..0] (8) Word 0 Word User Mode Word 3 • • • Word (n-1) tDH tDH tpsy High-Z User I/O User Mode INIT DONE (9) tCD2UM

Timing when using a MAX II device, MAX V device, or microprocessor as an external host.

#### Notes:

- 1. To find out the DCLK-to-DATA[] ratio for your system, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 2. The beginning of this waveform shows the device in user mode. In user mode, nCONFIG, nSTATUS, and CONF\_DONE are at logic high levels. When nCONFIG is pulled low, a reconfiguration cycle begins.

- 3. After power-up, the Arria V GZ device holds nSTATUS low for the time as specified by the POR delay.

- 4. After power-up, before and during configuration, CONF\_DONE is low.

- 5. Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.

- 6. "r" denotes the DCLK-to-DATA[] ratio. For the DCLK-to-DATA[] ratio based on the decompression and the design security feature enable settings, refer to the "DCLK-to-DATA[] Ratio for Arria V GZ Devices" table.

- 7. If needed, pause DCLK by holding it low. When DCLK restarts, the external host must provide data on the DATA[31.0] pins prior to sending the first DCLK rising edge.

- 8. To ensure a successful configuration, send the entire configuration data to the Arria V GZ device. CONF\_DONE is released high after the Arria V GZ device receives all the configuration data successfully. After CONF\_DONE goes high, send two additional falling edges on DCLK to begin initialization and enter user mode.

- 9. After the option bit to enable the INIT\_DONE pin is configured into the device, the INIT\_DONE goes low.