# E·XFL

## Intel - 5ASXFB5H4F40C6NES Datasheet

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| 2 0 0 0 0 0             |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                   |

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup>       |

| Flash Size              | -                                                                          |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 700MHz                                                                     |

| Primary Attributes      | FPGA - 462K Logic Elements                                                 |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                            |

| Package / Case          | 1517-BBGA, FCBGA                                                           |

| Supplier Device Package | 1517-FBGA, FC (40x40)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5asxfb5h4f40c6nes               |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                     | Description                    | Minimum | Maximum | Unit |

|----------------------------|--------------------------------|---------|---------|------|

| V <sub>CCPLL_HPS</sub>     | HPS PLL analog power supply    | -0.50   | 3.25    | V    |

| V <sub>CC_AUX_SHARED</sub> | HPS auxiliary power supply     | -0.50   | 3.25    | V    |

| I <sub>OUT</sub>           | DC output current per pin      | -25     | 40      | mA   |

| T <sub>J</sub>             | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub>           | Storage temperature (no bias)  | -65     | 150     | °C   |

## Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for ~15% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

#### Table 1-2: Maximum Allowed Overshoot During Transitions for Arria V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

1-3

| Parameter Symbo        |                   | l Condition |     | V <sub>CCIO</sub> (V) |       |       |      |      |     |     |     |     |     |     |      |

|------------------------|-------------------|-------------|-----|-----------------------|-------|-------|------|------|-----|-----|-----|-----|-----|-----|------|

|                        | Symbol            |             | 1.2 |                       | 1.5   |       | 1.8  |      | 2.5 |     | 3.0 |     | 3.3 |     | Unit |

|                        |                   |             | Min | Max                   | Min   | Max   | Min  | Max  | Min | Max | Min | Max | Min | Max |      |

| Bus-hold<br>trip point | V <sub>TRIP</sub> | _           | 0.3 | 0.9                   | 0.375 | 1.125 | 0.68 | 1.07 | 0.7 | 1.7 | 0.8 | 2   | 0.8 | 2   | V    |

#### **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

#### Table 1-8: OCT Calibration Accuracy Specifications for Arria V Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                                                                      | Description                                                                                                                                  | Condition (V)                               | Ca         | alibration Accura | су         | Unit |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------------|------------|------|

| Symbol                                                                                      | Description                                                                                                                                  |                                             | –I3, –C4   | –I5, –C5          | -C6        | Ont  |

| 25-Ω R <sub>S</sub>                                                                         | Internal series termination with calibration (25- $\Omega$ setting)                                                                          | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>S</sub>                                                                         | Internal series termination with calibration (50- $\Omega$ setting)                                                                          | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ $R_S$                                                         | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                         | V <sub>CCIO</sub> = 1.5, 1.35, 1.25,<br>1.2 | ±15        | ±15               | ±15        | %    |

| 48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ R <sub>S</sub>                               | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ setting)                                        | $V_{CCIO} = 1.2$                            | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                         | Internal parallel termination with calibration ( $50-\Omega$ setting)                                                                        | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2      | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ ,60- $\Omega$ , and 120- $\Omega$ R <sub>T</sub> | Internal parallel termination<br>with calibration (20- $\Omega$ , 30- $\Omega$ ,<br>40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25         | -10 to +40 | -10 to +40        | -10 to +40 | %    |

#### Figure 1-1: Equation for OCT Variation Without Recalibration

$$R_{OCT} = R_{SCAL} \left( 1 + \left( \frac{dR}{dT} \times \Delta T \right) \pm \left( \frac{dR}{dV} \times \Delta V \right) \right)$$

The definitions for the equation are as follows:

- The R<sub>OCT</sub> value calculated shows the range of OCT resistance with the variation of temperature and V<sub>CCIO</sub>.

- R<sub>SCAL</sub> is the OCT resistance value at power-up.

- $\Delta T$  is the variation of temperature with respect to the temperature at power up.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

#### OCT Variation after Power-Up Calibration

#### Table 1-10: OCT Variation after Power-Up Calibration for Arria V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{CCIO}$  range of  $\pm 5\%$  and a temperature range of 0°C to 85°C.

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|--------------------------------------------------|-----------------------|-------|------|

|        |                                                  | 3.0                   | 0.100 |      |

|        |                                                  | 2.5                   | 0.100 |      |

|        |                                                  | 1.8                   | 0.100 |      |

| dR/dV  | OCT variation with voltage without recalibration | 1.5                   | 0.100 | %/mV |

|        |                                                  | 1.35                  | 0.150 |      |

|        |                                                  | 1.25                  | 0.150 |      |

|        |                                                  | 1.2                   | 0.150 |      |

AV-51002 2017.02.10

## I/O Standard Specifications

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Arria V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

## Single-Ended I/O Standards

| I/O Standard    |       | V <sub>CCIO</sub> (V) |       |      | V <sub>IL</sub> (V)    | V <sub>IH</sub>        | (V)              | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)      | I <sub>OL</sub> <sup>(13)</sup> | I <sub>OH</sub> <sup>(13)</sup> (mA) |

|-----------------|-------|-----------------------|-------|------|------------------------|------------------------|------------------|------------------------|--------------------------|---------------------------------|--------------------------------------|

| I/O Stanuaru    | Min   | Тур                   | Max   | Min  | Мах                    | Min                    | Max              | Мах                    | Min                      | (mA)                            | IOH, (IIIA)                          |

| 3.3-V<br>LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.45                   | 2.4                      | 4                               | -4                                   |

| 3.3-V<br>LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 2                               | -2                                   |

| 3.0-V<br>LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.4                    | 2.4                      | 2                               | -2                                   |

| 3.0-V<br>LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                    | 1.7                    | 3.6              | 0.2                    | V <sub>CCIO</sub> – 0.2  | 0.1                             | -0.1                                 |

| 3.0-V PCI       | 2.85  | 3                     | 3.15  | _    | $0.3 \times V_{CCIO}$  | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 3.0-V<br>PCI-X  | 2.85  | 3                     | 3.15  |      | $0.35 \times V_{CCIO}$ | $0.5 \times V_{CCIO}$  | $V_{CCIO} + 0.3$ | $0.1 \times V_{CCIO}$  | $0.9 \times V_{CCIO}$    | 1.5                             | -0.5                                 |

| 2.5 V           | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                    | 1.7                    | 3.6              | 0.4                    | 2                        | 1                               | -1                                   |

| 1.8 V           | 1.71  | 1.8                   | 1.89  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | 0.45                   | V <sub>CCIO</sub> – 0.45 | 2                               | -2                                   |

| 1.5 V           | 1.425 | 1.5                   | 1.575 | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

| 1.2 V           | 1.14  | 1.2                   | 1.26  | -0.3 | $0.35 \times V_{CCIO}$ | $0.65 \times V_{CCIO}$ | $V_{CCIO} + 0.3$ | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$   | 2                               | -2                                   |

Table 1-14: Single-Ended I/O Standards for Arria V Devices

(13) To meet the I<sub>OL</sub> and I<sub>OH</sub> specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the I<sub>OL</sub> and I<sub>OH</sub> specifications in the datasheet.

| I/O Standard                       | Standard V <sub>CCIO</sub> (V)                                                                                                                                                                                                  |     | )                                                      |     | V <sub>ID</sub> (mV) <sup>(16)</sup> |     |       | V <sub>ICM(DC)</sub> (V)        |       | V <sub>OD</sub> (V) <sup>(17)</sup> |       |       | V <sub>OCM</sub> (V) <sup>(17)(18)</sup> |      |       |       |      |       |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------|-----|--------------------------------------|-----|-------|---------------------------------|-------|-------------------------------------|-------|-------|------------------------------------------|------|-------|-------|------|-------|

|                                    | Min                                                                                                                                                                                                                             | Тур | Мах                                                    | Min | Condition                            | Мах | Min   | Condition                       | Мах   | Min                                 | Тур   | Max   | Min                                      | Тур  | Max   |       |      |       |

| PCML                               | Transmitter, receiver, and input reference clock pins of high-speed transceivers use the PCI reference clock I/O pin specifications, refer to Transceiver Specifications for Arria V GX a for Arria V GT and ST Devices tables. |     |                                                        |     |                                      |     |       |                                 |       |                                     |       |       |                                          |      |       |       |      |       |

| 2.5 V                              | 2.375                                                                                                                                                                                                                           | 2.5 | 2.625                                                  | 100 | V <sub>CM</sub> =                    |     | 0.05  | D <sub>MAX</sub> ≤<br>1.25 Gbps | 1.80  | 0.247                               | 0.247 | 0.247 | .247 —                                   |      | 0.6   | 1.125 | 1.25 | 1.375 |

| LVDS <sup>(19)</sup>               | 2.375                                                                                                                                                                                                                           | 2.3 | 2.023                                                  | 100 | 1.25 V                               |     | 1.05  | D <sub>MAX</sub> ><br>1.25 Gbps | 1.55  | 0.247                               |       | 0.0   | 1.125                                    | 1.25 | 1.575 |       |      |       |

| RSDS<br>(HIO) <sup>(20)</sup>      | 2.375                                                                                                                                                                                                                           | 2.5 | 2.625                                                  | 100 | V <sub>CM</sub> =<br>1.25 V          |     | 0.25  |                                 | 1.45  | 0.1                                 | 0.2   | 0.6   | 0.5                                      | 1.2  | 1.4   |       |      |       |

| Mini-LVDS<br>(HIO) <sup>(21)</sup> | 2.375                                                                                                                                                                                                                           | 2.5 | 2.625                                                  | 200 |                                      | 600 | 0.300 |                                 | 1.425 | 0.25                                | _     | 0.6   | 1                                        | 1.2  | 1.4   |       |      |       |

| LVPECL <sup>(22)</sup>             |                                                                                                                                                                                                                                 |     |                                                        | 300 |                                      |     | 0.60  | D <sub>MAX</sub> ≤<br>700 Mbps  | 1.80  |                                     |       |       |                                          |      |       |       |      |       |

|                                    |                                                                                                                                                                                                                                 | _   | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |     |                                      |     |       |                                 |       |                                     |       |       |                                          |      |       |       |      |       |

#### **Related Information**

- Transceiver Specifications for Arria V GX and SX Devices on page 1-23 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

- $^{(16)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

- <sup>(17)</sup>  $R_{\rm L}$  range:  $90 \le R_{\rm L} \le 110 \ \Omega$ .

- <sup>(18)</sup> This applies to default pre-emphasis setting only.

- <sup>(19)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rates above 1.25 Gbps and 0 V to 1.85 V for data rates below 1.25 Gbps.

- <sup>(20)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(21)</sup> For optimized Mini-LVDS receiver performance, the receiver voltage input range must be within 0.3 V to 1.425 V.

- <sup>(22)</sup> For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rates above 700 Mbps and 0.45 V to 1.95 V for data rates below 700 Mbps.

| Symbol/Description                                                                 | Condition          | Transc | eiver Speed G | irade 4 | Transc | Unit |     |      |

|------------------------------------------------------------------------------------|--------------------|--------|---------------|---------|--------|------|-----|------|

|                                                                                    |                    | Min    | Тур           | Max     | Min    | Тур  | Max | Onit |

| Inter-transceiver block<br>transmitter channel-to-<br>channel skew <sup>(39)</sup> | ×N PMA bonded mode | _      | _             | 500     | _      | _    | 500 | ps   |

#### Table 1-24: CMU PLL Specifications for Arria V GX and SX Devices

| Symbol/Description        | Transceiver S | peed Grade 4 | Transceiver S | peed Grade 6 | Unit |

|---------------------------|---------------|--------------|---------------|--------------|------|

| Symbol/Description        | Min           | Мах          | Min           | Мах          | Onit |

| Supported data range      | 611           | 6553.6       | 611           | 3125         | Mbps |

| fPLL supported data range | 611           | 3125         | 611           | 3125         | Mbps |

## Table 1-25: Transceiver-FPGA Fabric Interface Specifications for Arria V GX and SX Devices

| Symbol/Description                  | Transceiver Spee | ed Grade 4 and 6 | Unit |

|-------------------------------------|------------------|------------------|------|

| Symbol/Description                  | Min              | Мах              | Unit |

| Interface speed (single-width mode) | 25               | 187.5            | MHz  |

| Interface speed (double-width mode) | 25               | 163.84           | MHz  |

#### **Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 1-35

- CTLE Response at Data Rates  $\leq$  3.25 Gbps across Supported AC Gain and DC Gain on page 1-36

- Arria V GT, GX, ST, and SX Device Family Pin Connection Guidelines Provides more information about the power supply connection for different data rates.

<sup>&</sup>lt;sup>(39)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

## Typical TX V<sub>OD</sub> Setting for Arria V Transceiver Channels with termination of 100 $\Omega$

| Table 1-32: Typical TX Vor | Setting for Arria V Transceive | r Channels with termination of 100 $\Omega$ |

|----------------------------|--------------------------------|---------------------------------------------|

|                            |                                |                                             |

| Symbol                                               | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(58)</sup> | V <sub>OD</sub> Value (mV) |

|------------------------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|                                                      | 6 <sup>(59)</sup>                       | 120                        | 34                                      | 680                        |

|                                                      | 7 <sup>(59)</sup>                       | 140                        | 35                                      | 700                        |

|                                                      | 8(59)                                   | 160                        | 36                                      | 720                        |

|                                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                                      | 14                                      | 280                        | 42                                      | 840                        |

| V <sub>OD</sub> differential peak-to-peak<br>typical | 15                                      | 300                        | 43                                      | 860                        |

| -) <b>F</b>                                          | 16                                      | 320                        | 44                                      | 880                        |

|                                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                                      | 24                                      | 480                        | 52                                      | 1040                       |

<sup>(58)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(59)</sup> Only valid for data rates  $\leq$  5 Gbps.

| Protocol                                        | Sub-protocol | Data Rate (Mbps) |

|-------------------------------------------------|--------------|------------------|

|                                                 | SONET 155    | 155.52           |

| SONET                                           | SONET 622    | 622.08           |

|                                                 | SONET 2488   | 2,488.32         |

|                                                 | GPON 155     | 155.52           |

| Gigabit-capable passive optical network (GPON)  | GPON 622     | 622.08           |

| Orgabil-Capable passive optical network (Or ON) | GPON 1244    | 1,244.16         |

|                                                 | GPON 2488    | 2,488.32         |

| QSGMII                                          | QSGMII 5000  | 5,000            |

# **Core Performance Specifications**

## **Clock Tree Specifications**

## Table 1-35: Clock Tree Specifications for Arria V Devices

| Parameter                       |          | Unit     |     |      |

|---------------------------------|----------|----------|-----|------|

| Falanetei                       | -I3, -C4 | –I5, –C5 | -C6 | Onic |

| Global clock and Regional clock | 625      | 625      | 525 | MHz  |

| Peripheral clock                | 450      | 400      | 350 | MHz  |

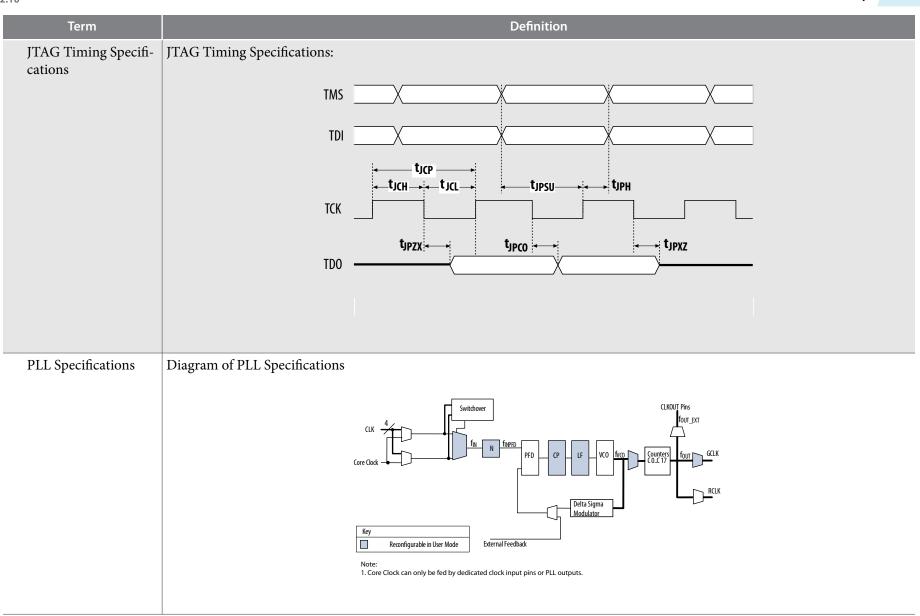

## **PLL Specifications**

## Table 1-36: PLL Specifications for Arria V Devices

This table lists the Arria V PLL block specifications. Arria V PLL block does not include HPS PLL.

## **DLL Frequency Range Specifications**

#### Table 1-43: DLL Frequency Range Specifications for Arria V Devices

| Parameter                     | -I3, -C4  | -I5, -C5  | -C6       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 200 - 667 | 200 - 667 | 200 - 667 | MHz  |

## DQS Logic Block Specifications

## Table 1-44: DQS Phase Shift Error Specifications for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Arria V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -I3, -C4 | –I5, –C5 | -C6 | Unit |

|----------------------------|----------|----------|-----|------|

| 2                          | 40       | 80       | 80  | ps   |

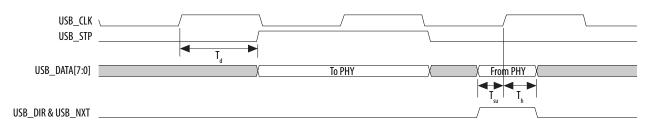

#### Figure 1-12: USB Timing Diagram

## Ethernet Media Access Controller (EMAC) Timing Characteristics

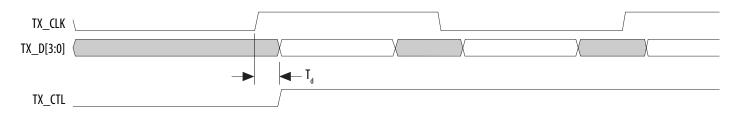

## Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | —     | 40  |      | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 |      | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    |     | 55   | %    |

| T <sub>d</sub>                | TX_CLK to TXD/TX_CTL output data delay | -0.85 |     | 0.15 | ns   |

#### Figure 1-13: RGMII TX Timing Diagram

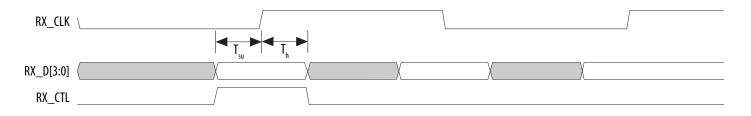

#### Table 1-57: RGMII RX Timing Requirements for Arria V Devices

| Symbol                        | Description            | Min | Тур | Unit |

|-------------------------------|------------------------|-----|-----|------|

| T <sub>clk</sub> (1000Base-T) | RX_CLK clock period    |     | 8   | ns   |

| T <sub>clk</sub> (100Base-T)  | RX_CLK clock period    |     | 40  | ns   |

| T <sub>clk</sub> (10Base-T)   | RX_CLK clock period    |     | 400 | ns   |

| T <sub>su</sub>               | RX_D/RX_CTL setup time | 1   |     | ns   |

| T <sub>h</sub>                | RX_D/RX_CTL hold time  | 1   | —   | ns   |

## Figure 1-14: RGMII RX Timing Diagram

## Table 1-58: Management Data Input/Output (MDIO) Timing Requirements for Arria V Devices

| Symbol           | Description                   | Min | Тур | Мах | Unit |

|------------------|-------------------------------|-----|-----|-----|------|

| T <sub>clk</sub> | MDC clock period              | _   | 400 | _   | ns   |

| T <sub>d</sub>   | MDC to MDIO output data delay | 10  |     | 20  | ns   |

| T <sub>s</sub>   | Setup time for MDIO data      | 10  |     | _   | ns   |

| T <sub>h</sub>   | Hold time for MDIO data       | 0   | _   |     | ns   |

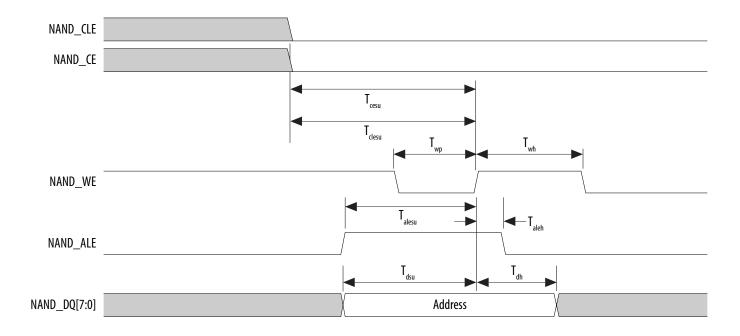

## Figure 1-18: NAND Address Latch Timing Diagram

#### **Related Information**

- PS Configuration Timing on page 1-81

- AS Configuration Timing

Provides the AS configuration timing waveform.

# **DCLK Frequency Specification in the AS Configuration Scheme**

#### Table 1-69: DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                 | Minimum | Typical | Maximum | Unit |

|-------------------------------------------|---------|---------|---------|------|

| DCLK frequency in AS configuration scheme | 5.3     | 7.9     | 12.5    | MHz  |

|                                           | 10.6    | 15.7    | 25.0    | MHz  |

|                                           | 21.3    | 31.4    | 50.0    | MHz  |

|                                           | 42.6    | 62.9    | 100.0   | MHz  |

# **PS Configuration Timing**

#### Table 1-70: PS Timing Parameters for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum               | Unit |

|---------------------|------------------------------|---------|-----------------------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600                   | ns   |

| t <sub>CF2ST0</sub> | nconfig low to nstatus low   |         | 600                   | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs   |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 1506 <sup>(103)</sup> | μs   |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | _       | 1506(104)             | μs   |

$<sup>^{(103)}\,</sup>$  You can obtain this value if you do not delay configuration by extending the <code>nCONFIG</code> or <code>nSTATUS</code> low pulse width.

<sup>&</sup>lt;sup>(104)</sup> You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

| Symbol           | Description                    | Minimum | Maximum | Unit |

|------------------|--------------------------------|---------|---------|------|

| V <sub>I</sub>   | DC input voltage               | -0.5    | 3.8     | V    |

| T <sub>J</sub>   | Operating junction temperature | -55     | 125     | °C   |

| T <sub>STG</sub> | Storage temperature (No bias)  | -65     | 150     | °C   |

| I <sub>OUT</sub> | DC output current per pin      | -25     | 40      | mA   |

## Table 2-3: Transceiver Power Supply Absolute Conditions for Arria V GZ Devices

| Symbol                | Description                                         | Minimum | Maximum | Unit |

|-----------------------|-----------------------------------------------------|---------|---------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)    | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)   | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)        | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)            | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)           | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)        | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)  | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side) | -0.5    | 1.8     | V    |

## Maximum Allowed Overshoot and Undershoot Voltage

During transitions, input signals may overshoot to the voltage shown in the following table. They may also undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

#### 2-4 Recommended Operating Conditions

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle.

For example, a signal that overshoots to 3.95 V can be at 3.95 V for only  $\sim 21\%$  over the lifetime of the device; for a device lifetime of 10 years, the overshoot duration amounts to  $\sim 2$  years.

| Table 2-4: Maximum Allowed Overshoot During Transitions for Arria V GZ Devices |

|--------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------|

| Symbol  | Description      | Condition (V) | Overshoot Duration as $\% @ T_J = 100^{\circ}C$ | Unit |

|---------|------------------|---------------|-------------------------------------------------|------|

|         | AC input voltage | 3.8           | 100                                             | %    |

|         |                  | 3.85          | 64                                              | %    |

|         |                  | 3.9           | 36                                              | %    |

|         |                  | 3.95          | 21                                              | %    |

| Vi (AC) |                  | 4             | 12                                              | %    |

|         |                  | 4.05          | 7                                               | %    |

|         |                  | 4.1           | 4                                               | %    |

|         |                  | 4.15          | 2                                               | %    |

|         |                  | 4.2           | 1                                               | %    |

## **Recommended Operating Conditions**

#### Table 2-5: Recommended Operating Conditions for Arria V GZ Devices

Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol          | Description                                             | Condition | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-----------------|---------------------------------------------------------|-----------|--------------------------|---------|--------------------------|------|

| V <sub>CC</sub> | Core voltage and periphery circuitry power supply (115) | _         | 0.82                     | 0.85    | 0.88                     | V    |

<sup>&</sup>lt;sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(115)</sup> The V<sub>CC</sub> core supply must be set to 0.9 V if the Partial Reconfiguration (PR) feature is used.

| Symbol                                 | Description                                         | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |  |

|----------------------------------------|-----------------------------------------------------|--------------------------|---------|--------------------------|------|--|

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |  |

| V <sub>CCR_GXBL</sub> <sup>(121)</sup> | Receiver analog power supply (left side)            | 0.97                     | 1.0     | 1.03                     | V    |  |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |  |

|                                        |                                                     | 0.82                     | 0.85    | 0.88                     |      |  |

| V <sub>CCR_GXBR</sub> <sup>(121)</sup> | Receiver analog power supply (right side)           | 0.97                     | 1.0     | 1.03                     | V    |  |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |  |

|                                        | Transmitter analog power supply (left side)         | 0.82                     | 0.85    | 0.88                     | V    |  |

| $V_{CCT\_GXBL}^{(121)}$                |                                                     | 0.97                     | 1.0     | 1.03                     |      |  |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |  |

|                                        | Transmitter analog power supply (right side)        | 0.82                     | 0.85    | 0.88                     |      |  |

| V <sub>CCT_GXBR</sub> <sup>(121)</sup> |                                                     | 0.97                     | 1.0     | 1.03                     | V    |  |

|                                        |                                                     | 1.03                     | 1.05    | 1.07                     |      |  |

| V <sub>CCH_GXBL</sub>                  | Transmitter output buffer power supply (left side)  | 1.425                    | 1.5     | 1.575                    | V    |  |

| V <sub>CCH_GXBR</sub>                  | Transmitter output buffer power supply (right side) | 1.425                    | 1.5     | 1.575                    | V    |  |

<sup>&</sup>lt;sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(121)</sup> This supply must be connected to 1.0 V if the transceiver is configured at a data rate > 6.5 Gbps, and to 1.05 V if configured at a data rate > 10.3 Gbps when DFE is used. For data rate up to 6.5 Gbps, you can connect this supply to 0.85 V.

AV-51002 2017.02.10

| Symbol                                                 | Parameter                                                                                              | Min  | Тур | Мах                                            | Unit      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------------------------------------------------|-----------|

| t <sub>INCCJ</sub> <sup>(171)</sup> , <sup>(172)</sup> | Input clock cycle-to-cycle jitter ( $f_{REF} \ge 100 \text{ MHz}$ )                                    | —    | _   | 0.15                                           | UI (p-p)  |

| 'INCCJ , , , , ,                                       | Input clock cycle-to-cycle jitter ( $f_{REF} < 100 \text{ MHz}$ )                                      | -750 |     | +750                                           | ps (p-p)  |

| (173)                                                  | Period Jitter for dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )              | _    | _   | 175                                            | ps (p-p)  |

| t <sub>OUTPJ_DC</sub> <sup>(173)</sup>                 | Period Jitter for dedicated clock output in integer<br>PLL (f <sub>OUT</sub> < 100 Mhz)                | _    |     | 17.5                                           | mUI (p-p) |

| t(173)                                                 | Period Jitter for dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )           | _    |     | $250^{(176)}, \\ 175^{(174)}$                  | ps (p-p)  |

| t <sub>FOUTPJ_DC</sub> <sup>(173)</sup>                | Period Jitter for dedicated clock output in fractional<br>PLL (f <sub>OUT</sub> < 100 MHz)             | _    | _   | $25^{(176)},$<br>17.5 <sup>(174)</sup>         | mUI (p-p) |

| (173)                                                  | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL ( $f_{OUT} \ge 100 \text{ MHz}$ )    | _    | _   | 175                                            | ps (p-p)  |

| t <sub>OUTCCJ_DC</sub> <sup>(173)</sup>                | Cycle-to-cycle Jitter for a dedicated clock output in integer PLL (f <sub>OUT</sub> < 100 MHz)         | _    |     | 17.5                                           | mUI (p-p) |

| <b>t</b> (173)                                         | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} \ge 100 \text{ MHz}$ ) | —    |     | 250 <sup>(176)</sup> ,<br>175 <sup>(174)</sup> | ps (p-p)  |

| t <sub>FOUTCCJ_DC</sub> <sup>(173)</sup>               | Cycle-to-cycle Jitter for a dedicated clock output in fractional PLL ( $f_{OUT} < 100 \text{ MHz}$ )   |      |     | $25^{(176)}, \\17.5^{(174)}$                   | mUI (p-p) |

<sup>(171)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps. <sup>(172)</sup> The  $f_{REF}$  is fIN/N specification applies when N = 1.

<sup>(174)</sup> This specification only covered fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

<sup>(173)</sup> Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in the "Worst-Case DCD on Arria V GZ I/O Pins" table.

# **JTAG Configuration Specifications**

| Symbol                  | Description                              | Min       | Max      | Unit |

|-------------------------|------------------------------------------|-----------|----------|------|

| t <sub>JCP</sub>        | TCK clock period                         | 30        |          | ns   |

| t <sub>JCP</sub>        | TCK clock period                         | 167 (203) |          | ns   |

| t <sub>JCH</sub>        | TCK clock high time                      | 14        |          | ns   |

| t <sub>JCL</sub>        | TCK clock low time                       | 14        |          | ns   |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time                 | 2         | _        | ns   |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time                 | 3         |          | ns   |

| t <sub>JPH</sub>        | JTAG port hold time                      | 5         | _        | ns   |

| t <sub>JPCO</sub>       | JTAG port clock to output                |           | 11 (204) | ns   |

| $t_{JPZX}$              | JTAG port high impedance to valid output |           | 14 (204) | ns   |

| t <sub>JPXZ</sub>       | JTAG port valid output to high impedance | —         | 14 (204) | ns   |

# Fast Passive Parallel (FPP) Configuration Timing

## DCLK-to-DATA[] Ratio (r) for FPP Configuration

FPP configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Arria V GZ Device Datasheet

**Altera Corporation**

<sup>&</sup>lt;sup>(203)</sup> The minimum TCK clock period is 167 ns if VCCBAT is within the range 1.2V-1.5V when you perform the volatile key programming.

<sup>(204)</sup> A 1-ns adder is required for each  $V_{CCIO}$  voltage step down from 3.0 V. For example,  $t_{IPCO} = 12$  ns if  $V_{CCIO}$  of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.8     | <ul> <li>Updated Table 21.</li> <li>Updated Table 22 V<sub>OCM</sub> (DC Coupled) condition.</li> <li>Updated the DCLK note to Figure 6, Figure 7, and Figure 9.</li> <li>Added note to Table 5 and Table 6.</li> <li>Added the DCLK specification to Table 50.</li> <li>Added note to Table 51.</li> <li>Updated the list of parameters in Table 53.</li> </ul> |

| February 2014 | 3.7     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| December 2013 | 3.6     | <ul> <li>Updated Table 2, Table 13, Table 18, Table 19, Table 22, Table 30, Table 33, Table 37, Table 38, Table 45, Table 46, Table 47, Table 56, Table 49.</li> <li>Updated "PLL Specifications".</li> </ul>                                                                                                                                                    |

| August 2013   | 3.5     | Updated Table 28.                                                                                                                                                                                                                                                                                                                                                |

| August 2013   | 3.4     | <ul> <li>Removed Preliminary tags for Table 2, Table 4, Table 5, Table 14, Table 27, Table 28, Table 29, Table 31, Table 32, Table 43, Table 45, Table 46, Table 47, Table 48, Table 49, Table 50, and Table 54.</li> <li>Updated Table 2 and Table 28.</li> </ul>                                                                                               |

| June 2013     | 3.3     | Updated Table 23, Table 28, Table 51, and Table 55.                                                                                                                                                                                                                                                                                                              |

| May 2013      | 3.2     | <ul> <li>Added Table 23.</li> <li>Updated Table 5, Table 22, Table 26, and Table 57.</li> <li>Updated Figure 6, Figure 7, Figure 8, and Figure 9.</li> </ul>                                                                                                                                                                                                     |

| March 2013    | 3.1     | <ul> <li>Updated Table 2, Table 6, Table 7, Table 8, Table 19, Table 22, Table 26, Table 29, Table 52.</li> <li>Updated "Maximum Allowed Overshoot and Undershoot Voltage".</li> </ul>                                                                                                                                                                           |

| December 2012 | 3.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                 |