### Intel - 5ASXMB3E4F31I3N Datasheet

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Details                 |                                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                                      |

| Architecture            | MCU, FPGA                                                                                     |

| Core Processor          | Dual ARM <sup>®</sup> Cortex <sup>®</sup> -A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup> |

| Flash Size              | -                                                                                             |

| RAM Size                | 64KB                                                                                          |

| Peripherals             | DMA, POR, WDT                                                                                 |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG                    |

| Speed                   | 800MHz                                                                                        |

| Primary Attributes      | FPGA - 350K Logic Elements                                                                    |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                                            |

| Package / Case          | 896-BBGA, FCBGA                                                                               |

| Supplier Device Package | 896-FBGA, FC (31x31)                                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5asxmb3e4f31i3n                                    |

|                         |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol                           | Description                                | Condition    | Minimum <sup>(1)</sup> | Typical | Maximum <sup>(1)</sup> | Unit |

|----------------------------------|--------------------------------------------|--------------|------------------------|---------|------------------------|------|

|                                  |                                            | 3.3 V        | 3.135                  | 3.3     | 3.465                  | V    |

|                                  |                                            | 3.0 V        | 2.85                   | 3.0     | 3.15                   | V    |

|                                  |                                            | 2.5 V        | 2.375                  | 2.5     | 2.625                  | V    |

| V                                | I/O buffers power supply                   | 1.8 V        | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCIO</sub>                | 1/O builets power supply                   | 1.5 V        | 1.425                  | 1.5     | 1.575                  | V    |

|                                  |                                            | 1.35 V       | 1.283                  | 1.35    | 1.418                  | V    |

|                                  |                                            | 1.25 V       | 1.19                   | 1.25    | 1.31                   | V    |

|                                  |                                            | 1.2 V        | 1.14                   | 1.2     | 1.26                   | V    |

| V <sub>CCD_FPLL</sub>            | PLL digital voltage regulator power supply | _            | 1.425                  | 1.5     | 1.575                  | V    |

| V <sub>CCA_FPLL</sub>            | PLL analog voltage regulator power supply  | _            | 2.375                  | 2.5     | 2.625                  | V    |

| VI                               | DC input voltage                           | —            | -0.5                   |         | 3.6                    | V    |

| V <sub>O</sub>                   | Output voltage                             | —            | 0                      |         | V <sub>CCIO</sub>      | V    |

|                                  | Operating junction temperature             | Commercial   | 0                      |         | 85                     | °C   |

| TJ                               |                                            | Industrial   | -40                    |         | 100                    | °C   |

| <b>t</b> (4)                     | Power supply ramp time                     | Standard POR | 200 µs                 |         | 100 ms                 | _    |

| t <sub>RAMP</sub> <sup>(4)</sup> |                                            | Fast POR     | 200 µs                 |         | 4 ms                   |      |

<sup>&</sup>lt;sup>(1)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(4)</sup> This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS\_PORSEL = 1.

### Table 1-21: Transceiver Clocks Specifications for Arria V GX and SX Devices

| Symbol/Description                                                                | Condition            | Transceiver Speed Grade 4 |     |     | Transceiver Speed Grade 6 |     |     | Unit |

|-----------------------------------------------------------------------------------|----------------------|---------------------------|-----|-----|---------------------------|-----|-----|------|

| Symbol/Description                                                                | Condition            | Min                       | Тур | Мах | Min                       | Тур | Max | Onit |

| fixedclk clock frequency                                                          | PCIe Receiver Detect | —                         | 125 | —   | —                         | 125 | _   | MHz  |

| Transceiver Reconfigura-<br>tion Controller IP (mgmt_<br>clk_clk) clock frequency | —                    | 75                        | _   | 125 | 75                        | _   | 125 | MHz  |

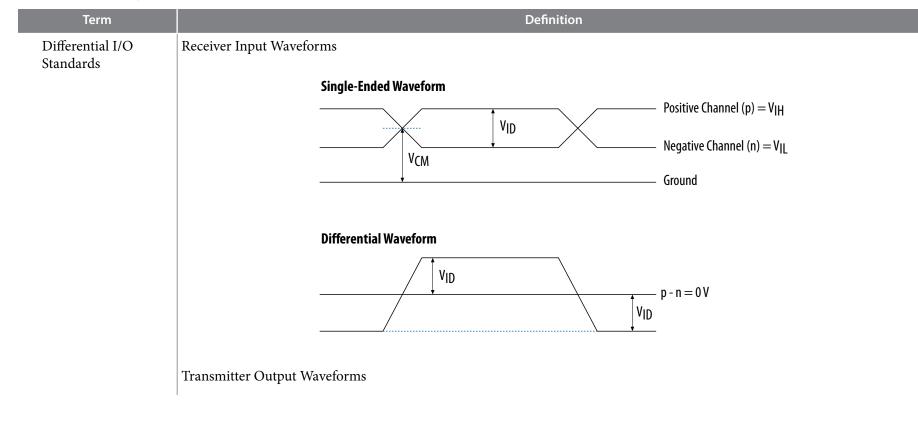

## Table 1-22: Receiver Specifications for Arria V GX and SX Devices

| Symbol/Deceription                                                                                              | Condition | Transceiver Speed Grade 4 |             |             | Transceiver Speed Grade 6 |        |      | Unit |

|-----------------------------------------------------------------------------------------------------------------|-----------|---------------------------|-------------|-------------|---------------------------|--------|------|------|

| Symbol/Description                                                                                              | Condition | Min                       | Тур         | Max         | Min                       | Тур    | Max  | Onit |

| Supported I/O standards                                                                                         |           | ]                         | 1.5 V PCML, | 2.5 V PCML, | LVPECL, an                | d LVDS |      |      |

| Data rate <sup>(28)</sup>                                                                                       | _         | 611                       | _           | 6553.6      | 611                       | _      | 3125 | Mbps |

| Absolute $V_{MAX}$ for a receiver pin <sup>(29)</sup>                                                           | _         |                           |             | 1.2         | _                         | _      | 1.2  | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                                    | _         | -0.4                      | _           | _           | -0.4                      | _      | _    | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) before device<br>configuration | _         |                           |             | 1.6         |                           |        | 1.6  | V    |

| Maximum peak-to-peak<br>differential input voltage<br>V <sub>ID</sub> (diff p-p) after device<br>configuration  | _         |                           |             | 2.2         |                           |        | 2.2  | V    |

<sup>&</sup>lt;sup>(28)</sup> To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

<sup>(29)</sup> The device cannot tolerate prolonged operation at this absolute maximum.

| Symbol/Description                                                          | Condition                                                   | Tran | sceiver Speed Gra | Unit |     |

|-----------------------------------------------------------------------------|-------------------------------------------------------------|------|-------------------|------|-----|

| Symbol/Description                                                          | Condition                                                   | Min  | Тур               | Max  | Ont |

|                                                                             | 85-Ω setting                                                | —    | 85                | —    | Ω   |

| Differential on-chip termination                                            | 100- $\Omega$ setting                                       |      | 100               |      | Ω   |

| resistors                                                                   | 120-Ω setting                                               | —    | 120               |      | Ω   |

|                                                                             | 150-Ω setting                                               |      | 150               |      | Ω   |

| Intra-differential pair skew                                                | TX $V_{CM}$ = 0.65 V (AC coupled)<br>and slew rate of 15 ps |      |                   | 15   | ps  |

| Intra-transceiver block transmitter channel-to-channel skew                 | ×6 PMA bonded mode                                          |      |                   | 180  | ps  |

| Inter-transceiver block transmitter channel-to-channel skew <sup>(55)</sup> | × <i>N</i> PMA bonded mode                                  |      |                   | 500  | ps  |

## Table 1-30: CMU PLL Specifications for Arria V GT and ST Devices

| Symbol/Description        | Transceiver S | peed Grade 3 | Unit |  |

|---------------------------|---------------|--------------|------|--|

| Symbol/Description        | Min           | Max          |      |  |

| Supported data range      | 0.611         | 10.3125      | Gbps |  |

| fPLL supported data range | 611           | 3125         | Mbps |  |

<sup>(55)</sup> This specification is only applicable to channels on one side of the device across two transceiver banks.

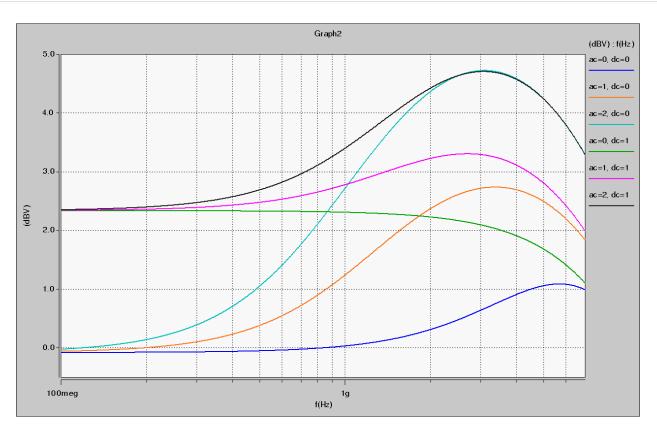

## CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain

Figure 1-2: Continuous Time-Linear Equalizer (CTLE) Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain for Arria V GX, GT, SX, and ST Devices

Arria V GX, GT, SX, and ST Device Datasheet

**Altera Corporation**

## Table 1-34: Transceiver Compliance Specification for All Supported Protocol for Arria V GX, GT, SX, and ST Devices

| Protocol                           | Sub-protocol | Data Rate (Mbps) |  |  |

|------------------------------------|--------------|------------------|--|--|

|                                    | PCIe Gen1    | 2,500            |  |  |

| PCIe                               | PCIe Gen2    | 5,000            |  |  |

|                                    | PCIe Cable   | 2,500            |  |  |

| XAUI                               | XAUI 2135    | 3,125            |  |  |

|                                    | SRIO 1250 SR | 1,250            |  |  |

|                                    | SRIO 1250 LR | 1,250            |  |  |

|                                    | SRIO 2500 SR | 2,500            |  |  |

|                                    | SRIO 2500 LR | 2,500            |  |  |

|                                    | SRIO 3125 SR | 3,125            |  |  |

| Serial RapidIO <sup>®</sup> (SRIO) | SRIO 3125 LR | 3,125            |  |  |

| Serial Rapidio (SRIO)              | SRIO 5000 SR | 5,000            |  |  |

|                                    | SRIO 5000 MR | 5,000            |  |  |

|                                    | SRIO 5000 LR | 5,000            |  |  |

|                                    | SRIO_6250_SR | 6,250            |  |  |

|                                    | SRIO_6250_MR | 6,250            |  |  |

|                                    | SRIO_6250_LR | 6,250            |  |  |

| Protocol                                        | Sub-protocol | Data Rate (Mbps) |

|-------------------------------------------------|--------------|------------------|

|                                                 | SONET 155    | 155.52           |

| SONET                                           | SONET 622    | 622.08           |

|                                                 | SONET 2488   | 2,488.32         |

|                                                 | GPON 155     | 155.52           |

| Gigabit-capable passive optical network (GPON)  | GPON 622     | 622.08           |

| Orgabil-Capable passive optical network (Or ON) | GPON 1244    | 1,244.16         |

|                                                 | GPON 2488    | 2,488.32         |

| QSGMII                                          | QSGMII 5000  | 5,000            |

# **Core Performance Specifications**

## **Clock Tree Specifications**

### Table 1-35: Clock Tree Specifications for Arria V Devices

| Parameter                       |          | Performance | Unit |      |

|---------------------------------|----------|-------------|------|------|

| Parameter                       | –I3, –C4 | –I5, –C5    | -C6  | Onic |

| Global clock and Regional clock | 625      | 625         | 525  | MHz  |

| Peripheral clock                | 450      | 400         | 350  | MHz  |

## **PLL Specifications**

### Table 1-36: PLL Specifications for Arria V Devices

This table lists the Arria V PLL block specifications. Arria V PLL block does not include HPS PLL.

| Symbol                                 | Parameter                                                                                                      | Condition                     | Min | Тур | Max                 | Unit     |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|---------------------|----------|

|                                        |                                                                                                                | -3 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f                                      | Output frequency for external clock                                                                            | -4 speed grade                | _   | _   | 670 <sup>(63)</sup> | MHz      |

| f <sub>out_ext</sub>                   | output                                                                                                         | –5 speed grade                | _   | _   | 622 <sup>(63)</sup> | MHz      |

|                                        |                                                                                                                | -6 speed grade                |     |     | 500 <sup>(63)</sup> | MHz      |

| t <sub>OUTDUTY</sub>                   | Duty cycle for external clock output<br>(when set to 50%)                                                      |                               | 45  | 50  | 55                  | %        |

| t <sub>FCOMP</sub>                     | External feedback clock compensation time                                                                      | _                             | _   | _   | 10                  | ns       |

| t <sub>DYCONFIGCLK</sub>               | Dynamic configuration clock for mgmt_<br>clk and scanclk                                                       | _                             | _   | _   | 100                 | MHz      |

| t <sub>LOCK</sub>                      | Time required to lock from end-of-<br>device configuration or deassertion of<br>areset                         | _                             | _   |     | 1                   | ms       |

| t <sub>DLOCK</sub>                     | Time required to lock dynamically<br>(after switchover or reconfiguring any<br>non-post-scale counters/delays) | _                             |     |     | 1                   | ms       |

|                                        |                                                                                                                | Low                           | _   | 0.3 | _                   | MHz      |

| f <sub>CLBW</sub>                      | PLL closed-loop bandwidth                                                                                      | Medium                        | _   | 1.5 | _                   | MHz      |

|                                        |                                                                                                                | High <sup>(64)</sup>          | _   | 4   | _                   | MHz      |

| t <sub>PLL_PSERR</sub>                 | Accuracy of PLL phase shift                                                                                    | —                             | _   | _   | ±50                 | ps       |

| t <sub>ARESET</sub>                    | Minimum pulse width on the areset signal                                                                       | _                             | 10  | _   | _                   | ns       |

| + (65)(66)                             | Input dock and to and ittar                                                                                    | $F_{REF} \ge 100 \text{ MHz}$ | _   | _   | 0.15                | UI (p-p) |

| t <sub>INCCJ</sub> <sup>(65)(66)</sup> | Input clock cycle-to-cycle jitter                                                                              | $F_{REF} < 100 \text{ MHz}$   | _   | _   | ±750                | ps (p-p) |

<sup>&</sup>lt;sup>(64)</sup> High bandwidth PLL settings are not supported in external feedback mode.

<sup>&</sup>lt;sup>(65)</sup> A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.

<sup>&</sup>lt;sup>(66)</sup>  $F_{\text{REF}}$  is  $f_{\text{IN}}/N$ , specification applies when N = 1.

### Table 1-38: Memory Block Performance Specifications for Arria V Devices

| Memory        | Mode                                                                                                    | Resourc | es Used | Performance |          |     | Unit |

|---------------|---------------------------------------------------------------------------------------------------------|---------|---------|-------------|----------|-----|------|

| Memory        | Mode                                                                                                    | ALUTs   | Memory  | -I3, -C4    | –I5, –C5 | -C6 | Onit |

|               | Single port, all supported widths                                                                       | 0       | 1       | 500         | 450      | 400 | MHz  |

|               | Simple dual-port, all supported widths                                                                  | 0       | 1       | 500         | 450      | 400 | MHz  |

| MLAB          | Simple dual-port with read and write at the same address                                                | 0       | 1       | 400         | 350      | 300 | MHz  |

|               | ROM, all supported width                                                                                | —       |         | 500         | 450      | 400 | MHz  |

|               | Single-port, all supported widths                                                                       | 0       | 1       | 400         | 350      | 285 | MHz  |

|               | Simple dual-port, all supported widths                                                                  | 0       | 1       | 400         | 350      | 285 | MHz  |

| M10K<br>Block | Simple dual-port with the read-during-<br>write option set to <b>Old Data</b> , all supported<br>widths | 0       | 1       | 315         | 275      | 240 | MHz  |

|               | True dual port, all supported widths                                                                    | 0       | 1       | 400         | 350      | 285 | MHz  |

|               | ROM, all supported widths                                                                               | 0       | 1       | 400         | 350      | 285 | MHz  |

### **Internal Temperature Sensing Diode Specifications**

### Table 1-39: Internal Temperature Sensing Diode Specifications for Arria V Devices

| Temperature Range | Accuracy | Offset Calibrated<br>Option | Sampling Rate | Conversion<br>Time | Resolution | Minimum Resolution with no<br>Missing Codes |

|-------------------|----------|-----------------------------|---------------|--------------------|------------|---------------------------------------------|

| -40 to 100°C      | ±8°C     | No                          | 1 MHz         | < 100 ms           | 8 bits     | 8 bits                                      |

## **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

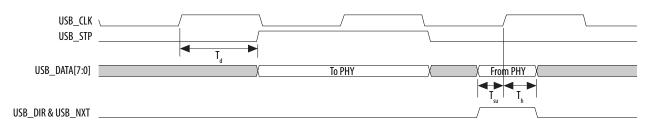

### Figure 1-12: USB Timing Diagram

## Ethernet Media Access Controller (EMAC) Timing Characteristics

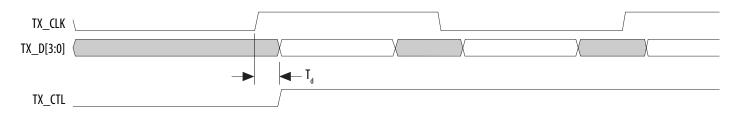

### Table 1-56: Reduced Gigabit Media Independent Interface (RGMII) TX Timing Requirements for Arria V Devices

| Symbol                        | Description                            | Min   | Тур | Max  | Unit |

|-------------------------------|----------------------------------------|-------|-----|------|------|

| T <sub>clk</sub> (1000Base-T) | TX_CLK clock period                    | _     | 8   | _    | ns   |

| T <sub>clk</sub> (100Base-T)  | TX_CLK clock period                    | —     | 40  |      | ns   |

| T <sub>clk</sub> (10Base-T)   | TX_CLK clock period                    | _     | 400 |      | ns   |

| T <sub>dutycycle</sub>        | TX_CLK duty cycle                      | 45    |     | 55   | %    |

| T <sub>d</sub>                | TX_CLK to TXD/TX_CTL output data delay | -0.85 |     | 0.15 | ns   |

### Figure 1-13: RGMII TX Timing Diagram

| Symbol                          | Description                        | Min | Мах | Unit |

|---------------------------------|------------------------------------|-----|-----|------|

| T <sub>dh</sub> <sup>(89)</sup> | Data to write enable hold time     | 5   | —   | ns   |

| T <sub>cea</sub>                | Chip enable to data access time    |     | 25  | ns   |

| T <sub>rea</sub>                | Read enable to data access time    |     | 16  | ns   |

| T <sub>rhz</sub>                | Read enable to data high impedance |     | 100 | ns   |

| T <sub>rr</sub>                 | Ready to read enable low           | 20  |     | ns   |

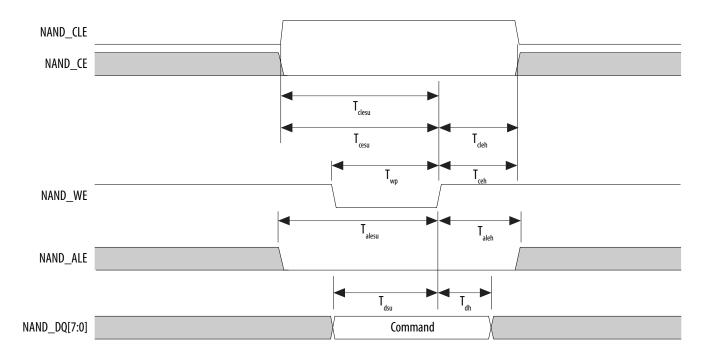

# Figure 1-17: NAND Command Latch Timing Diagram

#### **Related Information**

- PS Configuration Timing on page 1-81

- AS Configuration Timing

Provides the AS configuration timing waveform.

## **DCLK Frequency Specification in the AS Configuration Scheme**

### Table 1-69: DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                  | Minimum | Typical | Maximum | Unit |

|--------------------------------------------|---------|---------|---------|------|

|                                            | 5.3     | 7.9     | 12.5    | MHz  |

| DCLK frequency in AS configuration scheme  | 10.6    | 15.7    | 25.0    | MHz  |

| Bellk frequency in AS configuration scheme | 21.3    | 31.4    | 50.0    | MHz  |

|                                            | 42.6    | 62.9    | 100.0   | MHz  |

## **PS Configuration Timing**

### Table 1-70: PS Timing Parameters for Arria V Devices

| Symbol              | Parameter                    | Minimum | Maximum               | Unit |

|---------------------|------------------------------|---------|-----------------------|------|

| t <sub>CF2CD</sub>  | nCONFIG low to CONF_DONE low | _       | 600                   | ns   |

| t <sub>CF2ST0</sub> | nCONFIG low to nSTATUS low   |         | 600                   | ns   |

| t <sub>CFG</sub>    | nCONFIG low pulse width      | 2       | _                     | μs   |

| t <sub>STATUS</sub> | nSTATUS low pulse width      | 268     | 1506 <sup>(103)</sup> | μs   |

| t <sub>CF2ST1</sub> | nCONFIG high to nSTATUS high | _       | 1506(104)             | μs   |

$<sup>^{(103)}\,</sup>$  You can obtain this value if you do not delay configuration by extending the <code>nCONFIG</code> or <code>nSTATUS</code> low pulse width.

<sup>&</sup>lt;sup>(104)</sup> You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

|            |             |       | Active Seria | <b> </b> (108)                       | Fast Passive Parallel <sup>(109)</sup> |            |                                    |  |  |

|------------|-------------|-------|--------------|--------------------------------------|----------------------------------------|------------|------------------------------------|--|--|

| Variant    | Member Code | Width | DCLK (MHz)   | Minimum Configura-<br>tion Time (ms) | Width                                  | DCLK (MHz) | Minimum Configuration Time<br>(ms) |  |  |

|            | A1          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |  |

|            | A3          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |  |

|            | A5          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |  |

| Arria V GX | A7          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |  |

| Allia v GA | B1          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |  |

|            | B3          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |  |

|            | B5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

|            | B7          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

|            | C3          | 4     | 100          | 178                                  | 16                                     | 125        | 36                                 |  |  |

| Arria V GT | C7          | 4     | 100          | 255                                  | 16                                     | 125        | 51                                 |  |  |

| Allia v Gi | D3          | 4     | 100          | 344                                  | 16                                     | 125        | 69                                 |  |  |

|            | D7          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

| Arria V SX | В3          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

| Allia V SA | B5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

| Arria V ST | D3          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

|            | D5          | 4     | 100          | 465                                  | 16                                     | 125        | 93                                 |  |  |

**Related Information Configuration Files** on page 1-83

(108) DCLK frequency of 100 MHz using external CLKUSR.

(109) Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

### 1-100 Document Revision History

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| November 2012 | 3.0     | <ul> <li>Updated Table 2, Table 4, Table 9, Table 14, Table 16, Table 17, Table 20, Table 21, Table 25, Table 29, Table 36, Table 56, Table 57, and Table 60.</li> <li>Removed table: Transceiver Block Jitter Specifications for Arria V Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, Table 48, Table 49, and Table 50.</li> <li>Added Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, Figure 16, Figure 17, Figure 18, and Figure 19.</li> <li>Updated Table 3 and Table 5.</li> </ul> </li> </ul> |

| October 2012  | 2.4     | <ul> <li>Updated Arria V GX V<sub>CCR_GXBL/R</sub>, V<sub>CCT_GXBL/R</sub>, and V<sub>CCL_GXBL/R</sub> minimum and maximum values, and data rate in Table 4.</li> <li>Added receiver V<sub>ICM</sub> (AC coupled) and V<sub>ICM</sub> (DC coupled) values, and transmitter V<sub>OCM</sub> (AC coupled) and V<sub>OCM</sub> (DC coupled) values in Table 20 and Table 21.</li> </ul>                                                                                                                                                                                                                                                                                                                             |

| August 2012   | 2.3     | Updated the SERDES factor condition in Table 30.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| July 2012     | 2.2     | <ul> <li>Updated the maximum voltage for V<sub>I</sub> (DC input voltage) in Table 1.</li> <li>Updated Table 20 to include the Arria V GX -I3 speed grade.</li> <li>Updated the minimum value of the fixedclk clock frequency in Table 20 and Table 21.</li> <li>Updated the SERDES factor condition in Table 30.</li> <li>Updated Table 50 to include the IOE programmable delay settings for the Arria V GX -I3 speed grade.</li> </ul>                                                                                                                                                                                                                                                                        |

| June 2012     | 2.1     | Updated $V_{CCR\_GXBL/R}$ , $V_{CCT\_GXBL/R}$ , and $V_{CCL\_GXBL/R}$ values in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Symbol            | Description                    | Condition    | Minimum <sup>(114)</sup> | Typical | Maximum <sup>(114)</sup> | Unit |

|-------------------|--------------------------------|--------------|--------------------------|---------|--------------------------|------|

| VI                | DC input voltage               |              | -0.5                     | _       | 3.6                      | V    |

| V <sub>O</sub>    | Output voltage                 |              | 0                        | _       | V <sub>CCIO</sub>        | V    |

| TI                | Operating junction temperature | Commercial   | 0                        |         | 85                       | °C   |

| ıj                | Operating junction temperature | Industrial   | -40                      | _       | 100                      | °C   |

| t                 | Derver sumply men time         | Standard POR | 200 µs                   | _       | 100 ms                   | _    |

| t <sub>RAMP</sub> | Power supply ramp time         | Fast POR     | 200 µs                   | _       | 4 ms                     | —    |

### **Recommended Transceiver Power Supply Operating Conditions**

### Table 2-6: Recommended Transceiver Power Supply Operating Conditions for Arria V GZ Devices

| Symbol                                                       | Description                                       | Minimum <sup>(118)</sup> | Typical | Maximum <sup>(118)</sup> | Unit |  |

|--------------------------------------------------------------|---------------------------------------------------|--------------------------|---------|--------------------------|------|--|

| V <sub>CCA_GXBL</sub>                                        | Transceiver channel PLL power supply (left side)  | 2.85                     | 3.0     | 3.15                     | V    |  |

| (119), (120)                                                 | Transcerver channel PLL power supply (left side)  | 2.375                    | 2.5     | 2.625                    | v    |  |

| V <sub>CCA</sub> _                                           | Transceiver channel PLL power supply (right side) | 2.85                     | 3.0     | 3.15                     | V    |  |

| V <sub>CCA</sub><br>GXBR <sup>(119)</sup> , <sup>(120)</sup> | Transcerver channel PLL power supply (fight side) | 2.375                    | 2.5     | 2.625                    | v    |  |

| V <sub>CCHIP_L</sub>                                         | Transceiver hard IP power supply (left side)      | 0.82                     | 0.85    | 0.88                     | V    |  |

| V <sub>CCHSSI_L</sub>                                        | Transceiver PCS power supply (left side)          | 0.82                     | 0.85    | 0.88                     | V    |  |

| V <sub>CCHSSI_R</sub>                                        | Transceiver PCS power supply (right side)         | 0.82                     | 0.85    | 0.88                     | V    |  |

<sup>(114)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(120)</sup> When using ATX PLLs, the supply must be 3.0 V.

<sup>(119)</sup> This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

| Symbol                                 | Description                                         | Minimum <sup>(118)</sup>                                                                                                                                                                                                                                                                                                                                                                        | Typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Maximum <sup>(118)</sup> | Unit |

|----------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|

|                                        |                                                     | 0.82                                                                                                                                                                                                                                                                                                                                                                                            | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.88                     |      |

| V <sub>CCR_GXBL</sub> <sup>(121)</sup> | Receiver analog power supply (left side)            | 0.97                                                                                                                                                                                                                                                                                                                                                                                            | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.03                     | V    |

|                                        |                                                     | 1.03                                                                                                                                                                                                                                                                                                                                                                                            | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.07                     |      |

|                                        |                                                     | 0.82                                                                                                                                                                                                                                                                                                                                                                                            | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.88                     |      |

| V <sub>CCR_GXBR</sub> <sup>(121)</sup> | Receiver analog power supply (right side)           | 0.97                                                                                                                                                                                                                                                                                                                                                                                            | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.03                     | V    |

|                                        |                                                     | le) $0.97$ $1.0$ $1.03$ V $1.03$ $1.05$ $1.07$ $1.03$ $0.82$ $0.85$ $0.88$ $0.97$ $1.0$ $1.03$ V $1.03$ $1.05$ $1.07$                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |      |

|                                        |                                                     | 0.82                                                                                                                                                                                                                                                                                                                                                                                            | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.88                     |      |

| V <sub>CCT_GXBL</sub> <sup>(121)</sup> | Transmitter analog power supply (left side)         | 0.97                                                                                                                                                                                                                                                                                                                                                                                            | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.03                     | V    |

|                                        |                                                     | $\frac{1.03}{1.03} \frac{1.05}{0.82}$ nalog power supply (right side)<br>er analog power supply (left side)<br>er analog power supply (left side)<br>er analog power supply (right side)<br>er analog power supply (right side)<br>er output buffer power supply (left side)<br>$\frac{0.82}{0.97} \frac{0.82}{0.85}$ $\frac{0.82}{0.97} \frac{0.85}{1.0}$ $\frac{0.82}{0.97} \frac{0.85}{1.0}$ | 1.07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |      |

|                                        |                                                     | 0.82                                                                                                                                                                                                                                                                                                                                                                                            | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.88                     |      |

| V <sub>CCT_GXBR</sub> <sup>(121)</sup> | Transmitter analog power supply (right side)        | 0.97                                                                                                                                                                                                                                                                                                                                                                                            | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.03                     | V    |

|                                        |                                                     | 1.03                                                                                                                                                                                                                                                                                                                                                                                            | 0.85         0.88           1.0         1.03         V           1.05         1.07         V           0.85         0.88         V           1.0         1.03         V           1.05         1.07         V           0.85         0.88         V           1.05         1.03         V           1.05         1.07         V           1.05         1.07         V           1.05         1.07         V           1.05         1.07         V           1.05         0.88         V           1.05         1.03         V           1.05         1.03         V |                          |      |

| V <sub>CCH_GXBL</sub>                  | Transmitter output buffer power supply (left side)  | 1.425                                                                                                                                                                                                                                                                                                                                                                                           | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.575                    | V    |

| V <sub>CCH_GXBR</sub>                  | Transmitter output buffer power supply (right side) | 1.425                                                                                                                                                                                                                                                                                                                                                                                           | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.575                    | V    |

<sup>&</sup>lt;sup>(118)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>&</sup>lt;sup>(121)</sup> This supply must be connected to 1.0 V if the transceiver is configured at a data rate > 6.5 Gbps, and to 1.05 V if configured at a data rate > 10.3 Gbps when DFE is used. For data rate up to 6.5 Gbps, you can connect this supply to 0.85 V.

#### Table 2-19: Differential SSTL I/O Standards for Arria V GZ Devices

| I/O Standard            | V <sub>CCIO</sub> (V) |      |       | V <sub>SWIN</sub> | V <sub>SWING(DC)</sub> (V) |                                 | $V_{X(AC)}(V)$       |                                 | V <sub>SWING(AC)</sub> (V)                    |                           |  |

|-------------------------|-----------------------|------|-------|-------------------|----------------------------|---------------------------------|----------------------|---------------------------------|-----------------------------------------------|---------------------------|--|

|                         | Min                   | Тур  | Max   | Min               | Max                        | Min                             | Тур                  | Max                             | Min                                           | Мах                       |  |

| SSTL-2 Class I,<br>II   | 2.375                 | 2.5  | 2.625 | 0.3               | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.2   | _                    | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.62                                          | $V_{CCIO} + 0.6$          |  |

| SSTL-18 Class I,<br>II  | 1.71                  | 1.8  | 1.89  | 0.25              | V <sub>CCIO</sub><br>+ 0.6 | V <sub>CCIO</sub> /2<br>- 0.175 |                      | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5                                           | V <sub>CCIO</sub> + 0.6   |  |

| SSTL-15 Class I,<br>II  | 1.425                 | 1.5  | 1.575 | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  |                      | V <sub>CCIO</sub> /2<br>+ 0.15  | 0.35                                          | _                         |  |

| SSTL-135<br>Class I, II | 1.283                 | 1.35 | 1.45  | 0.2               | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | $2(V_{IL(AC)} - V_{REF})$ |  |

| SSTL-125<br>Class I, II | 1.19                  | 1.25 | 1.31  | 0.18              | (127)                      | V <sub>CCIO</sub> /2<br>- 0.15  | V <sub>CCIO</sub> /2 | V <sub>CCIO</sub> /2<br>+ 0.15  | 2(V <sub>IH(AC)</sub><br>- V <sub>REF</sub> ) | _                         |  |

| SSTL-12<br>Class I, II  | 1.14                  | 1.2  | 1.26  | 0.18              | —                          | V <sub>REF</sub><br>-0.15       | V <sub>CCIO</sub> /2 | V <sub>REF</sub><br>+ 0.15      | -0.30                                         | 0.30                      |  |

## Table 2-20: Differential HSTL and HSUL I/O Standards for Arria V GZ Devices

| I/O Standard           | V <sub>CCIO</sub> (V) |     | V <sub>DIF(DC)</sub> (V) |     | $V_{X(AC)}(V)$ |      |     | V <sub>CM(DC)</sub> (V) |      |     | V <sub>DIF(AC)</sub> (V) |     |     |

|------------------------|-----------------------|-----|--------------------------|-----|----------------|------|-----|-------------------------|------|-----|--------------------------|-----|-----|

|                        | Min                   | Тур | Max                      | Min | Max            | Min  | Тур | Max                     | Min  | Тур | Max                      | Min | Max |

| HSTL-18 Class<br>I, II | 1.71                  | 1.8 | 1.89                     | 0.2 | _              | 0.78 |     | 1.12                    | 0.78 | _   | 1.12                     | 0.4 | _   |

| HSTL-15 Class<br>I, II | 1.425                 | 1.5 | 1.575                    | 0.2 | _              | 0.68 |     | 0.9                     | 0.68 | _   | 0.9                      | 0.4 | —   |

$<sup>^{(127)}</sup>$  The maximum value for  $V_{SWING(DC)}$  is not defined. However, each single-ended signal needs to be within the respective single-ended limits ( $V_{IH(DC)}$  and  $V_{IL(DC)}$ ).

### Table 2-26: CMU PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

| Symbol/Description                          | Conditions | Trans | ceiver Spee | d Grade 2 | Transc | Unit |         |      |

|---------------------------------------------|------------|-------|-------------|-----------|--------|------|---------|------|

|                                             | Conditions | Min   | Тур         | Max       | Min    | Тур  | Мах     |      |

| Supported data range                        | _          | 600   | _           | 12500     | 600    | _    | 10312.5 | Mbps |

| t <sub>pll_powerdown</sub> <sup>(153)</sup> | _          | 1     | _           |           | 1      | _    |         | μs   |

| t <sub>pll_lock</sub> <sup>(154)</sup>      | _          |       | —           | 10        | _      |      | 10      | μs   |

#### **Related Information**

### Arria V Device Overview

For more information about device ordering codes.

## ATX PLL

### Table 2-27: ATX PLL Specifications for Arria V GZ Devices

Speed grades shown refer to the PMA Speed Grade in the device ordering code. The maximum data rate could be restricted by the Core/PCS speed grade. Contact your Altera Sales Representative for the maximum data rate specifications in each speed grade combination offered. For more information about device ordering codes, refer to the Arria V Device Overview.

Arria V GZ Device Datasheet

**Altera Corporation**

$t_{pll\_powerdown}$  is the PLL powerdown minimum pulse width. (153)

<sup>(154)</sup>  $t_{\text{pll} \text{ lock}}$  is the time required for the transmitter CMU/ATX PLL to lock to the input reference clock frequency after coming out of reset.

### Table 2-60: PS Timing Parameters for Arria V GZ Devices

| Symbol                              | Parameter                                         | Minimum                                               | Maximum     | Unit |

|-------------------------------------|---------------------------------------------------|-------------------------------------------------------|-------------|------|

| t <sub>CF2CD</sub>                  | nCONFIG low to CONF_DONE low                      | —                                                     | 600         | ns   |

| t <sub>CF2ST0</sub>                 | nCONFIG low to nSTATUS low                        | _                                                     | 600         | ns   |

| t <sub>CFG</sub>                    | nCONFIG low pulse width                           | 2                                                     |             | μs   |

| t <sub>STATUS</sub>                 | nSTATUS low pulse width                           | 268                                                   | 1,506 (217) | μs   |

| t <sub>CF2ST1</sub>                 | nCONFIG high to nSTATUS high                      | _                                                     | 1,506 (218) | μs   |

| t <sub>CF2CK</sub><br>(219)         | nCONFIG high to first rising edge on DCLK         | 1,506                                                 | _           | μs   |

| t <sub>ST2CK</sub> <sup>(219)</sup> | nSTATUS high to first rising edge of DCLK         | 2                                                     |             | μs   |

| t <sub>DSU</sub>                    | DATA[] setup time before rising edge on DCLK      | 5.5                                                   |             | ns   |

| t <sub>DH</sub>                     | DATA[] hold time after rising edge on DCLK        | 0                                                     | _           | ns   |

| t <sub>CH</sub>                     | DCLK high time                                    | $0.45 	imes 1/f_{MAX}$                                |             | S    |

| t <sub>CL</sub>                     | DCLK low time                                     | $0.45 	imes 1/f_{MAX}$                                | —           | S    |

| t <sub>CLK</sub>                    | DCLK period                                       | 1/f <sub>MAX</sub>                                    |             | S    |

| f <sub>MAX</sub>                    | DCLK frequency                                    | _                                                     | 125         | MHz  |

| t <sub>CD2UM</sub>                  | CONF_DONE high to user mode <sup>(220)</sup>      | 175                                                   | 437         | μs   |

| t <sub>CD2CU</sub>                  | CONF_DONE high to CLKUSR enabled                  | $4 \times \text{maximum DCLK}$ period                 | _           |      |

| t <sub>CD2UMC</sub>                 | CONF_DONE high to user mode with CLKUSR option on | $t_{CD2CU}$ + (8576 × CLKUSR period) <sup>(221)</sup> | _           | _    |

<sup>&</sup>lt;sup>(217)</sup> This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

<sup>&</sup>lt;sup>(218)</sup> This value is applicable if you do not delay configuration by externally holding the nSTATUS low.

<sup>&</sup>lt;sup>(219)</sup> If nSTATUS is monitored, follow the t<sub>ST2CK</sub> specification. If nSTATUS is not monitored, follow the t<sub>CF2CK</sub> specification.

<sup>&</sup>lt;sup>(220)</sup> The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for initializing the device.

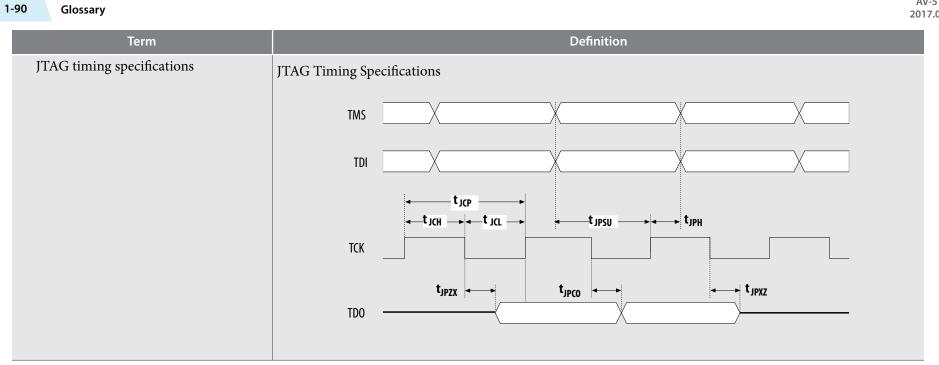

# Glossary

### Table 2-68: Glossary