Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 100MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 24kB                                                                    |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 3.30V                                                                   |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-LBGA                                                                |

| Supplier Device Package | 196-LBGA (15x15)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56303vf100r2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.3 Clock

Table 1-4. Clock Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                           |

|-------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input  | Input                 | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                   |

| XTAL        | Output | Chip-driven           | Crystal Output—Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

### 1.4 PLL

Table 1-5. Phase-Locked Loop Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                               |

|-------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT      | Output | Chip-driven           | Clock Output—Provides an output clock synchronized to the internal core clock phase.                                                                                                             |

|             |        |                       | If the PLL is enabled and both the multiplication and division factors equal one, then CLKOUT is also synchronized to EXTAL.                                                                     |

|             |        |                       | If the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.                                                                                                                     |

| PCAP        | Input  | Input                 | PLL Capacitor—An input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to V <sub>CCP</sub> .                                   |

|             |        |                       | If the PLL is not used, PCAP can be tied to $V_{CC}$ , GND, or left floating.                                                                                                                    |

| PINIT       | Input  | Input                 | PLL Initial—During assertion of RESET, the value of PINIT is written into the PLL enable (PEN) bit of the PLL control (PCTL) register, determining whether the PLL is enabled or disabled.       |

| NMI         | Input  |                       | Nonmaskable Interrupt—After RESET deassertion and during normal instruction processing, this Schmitt-trigger input is the negative-edge-triggered NMI request internally synchronized to CLKOUT. |

|             |        |                       | Note: PINIT/NMI can tolerate 5 V.                                                                                                                                                                |

# 1.5 External Memory Expansion Port (Port A)

**Note:** When the DSP56303 enters a low-power standby mode (stop or wait), it releases bus mastership and tristates the relevant Port A signals: A[0–17], D[0–23], AA0/RAS0–AA3/RAS3, RD, WR, BB, CAS.

### 1.5.1 External Address Bus

Table 1-6. External Address Bus Signals

| Signal Name | Туре   | State During<br>Reset, Stop, or<br>Wait | Signal Description                                                                                                                                                                                                                                                                                        |

|-------------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

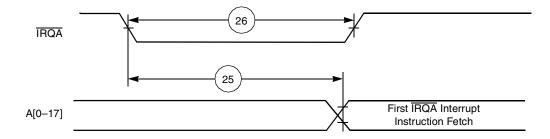

| A[0-17]     | Output | Tri-stated                              | Address Bus—When the DSP is the bus master, A[0–17] are active-high outputs that specify the address for external program and data memory accesses. Otherwise, the signals are tri-stated. To minimize power dissipation, A[0–17] do not change state when external memory spaces are not being accessed. |

DSP56303 Technical Data, Rev. 11

1-4 Freescale Semiconductor

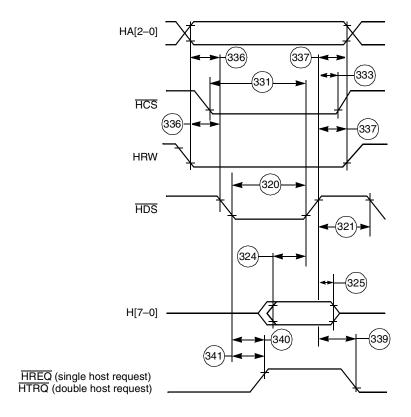

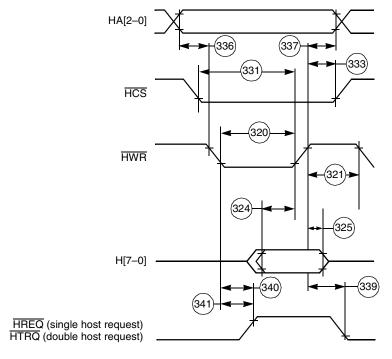

Table 1-11. Host Interface (Continued)

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDS/HDS     | Input           | Ignored Input                        | Host Data Strobe—When the HI08 is programmed to interface with a single-data-strobe host bus and the HI function is selected, this signal is the host data strobe (HDS) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HDS) following reset.                                                                             |

| HWR/HWR     | Input           |                                      | Host Write Data—When the HI08 is programmed to interface with a double-data-strobe host bus and the HI function is selected, this signal is the host write data strobe (HWR) Schmitt-trigger input. The polarity of the data strobe is programmable but is configured as active-low (HWR) following reset.                                                                        |

| PB12        | Input or Output |                                      | Port B 12—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                                      |

| HREQ/HREQ   | Output          | Ignored Input                        | Host Request—When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host request (HREQ) output. The polarity of the host request is programmable but is configured as active-low (HREQ) following reset. The host request may be programmed as a driven or open-drain output.                           |

| HTRQ/HTRQ   | Output          |                                      | <b>Transmit Host Request</b> —When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the transmit host request (HTRQ) output. The polarity of the host request is programmable but is configured as active-low (HTRQ) following reset. The host request may be programmed as a driven or open-drain output. |

| PB14        | Input or Output |                                      | Port B 14—When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                                      |

| HACK/HACK   | Input           | Ignored Input                        | Host Acknowledge—When the HI08 is programmed to interface with a single host request host bus and the HI function is selected, this signal is the host acknowledge (HACK) Schmitt-trigger input. The polarity of the host acknowledge is programmable but is configured as active-low (HACK) after reset.                                                                         |

| HRRQ/HRRQ   | Output          |                                      | Receive Host Request—When the HI08 is programmed to interface with a double host request host bus and the HI function is selected, this signal is the receive host request (HRRQ) output. The polarity of the host request is programmable but is configured as active-low (HRRQ) after reset. The host request may be programmed as a driven or open-drain output.               |

| PB15        | Input or Output |                                      | <b>Port B 15</b> —When the HI08 is configured as GPIO through the HI08 Port Control Register, this signal is individually programmed as an input or output through the HI08 Data Direction Register.                                                                                                                                                                              |

Notes:

- 1. In the Stop state, the signal maintains the last state as follows:

- If the last state is input, the signal is an ignored input.

- If the last state is output, the signal is tri-stated.

- 2. The Wait processing state does not affect the signal state.

- 3. All inputs are 5 V tolerant.

1-10 Freescale Semiconductor

Table 1-13. Enhanced Serial Synchronous Interface 1 (Continued)

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK1        | Input/Output    | Ignored Input                        | Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK1 is a clock input or output used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                            |

|             |                 |                                      | Although an external serial clock can be independent of and asynchronous to the DSP system clock, it must exceed the minimum clock cycle time of 6T (that is, the system clock frequency must be at least three times the external ESSI clock frequency). The ESSI needs at least three DSP phases inside each half of the serial clock. |

| PD3         | Input or Output |                                      | Port D 3—The default configuration following reset is GPIO input PD3. When configured as PD3, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SCK1 through the Port D Control Register.                                                                             |

| SRD1        | Input           | Ignored Input                        | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD1 is an input when data is being received.                                                                                                                                                                                        |

| PD4         | Input or Output |                                      | Port D 4—The default configuration following reset is GPIO input PD4. When configured as PD4, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal SRD1 through the Port D Control Register.                                                                             |

| STD1        | Output          | Ignored Input                        | Serial Transmit Data—Transmits data from the Serial Transmit Shift Register. STD1 is an output when data is being transmitted.                                                                                                                                                                                                           |

| PD5         | Input or Output |                                      | Port D 5—The default configuration following reset is GPIO input PD5. When configured as PD5, signal direction is controlled through the Port D Direction Register. The signal can be configured as an ESSI signal STD1 through the Port D Control Register.                                                                             |

Notes:

- 1. In the Stop state, the signal maintains the last state as follows:

- If the last state is input, the signal is an ignored input.

- If the last state is output, the signal is tri-stated.

- 2. The Wait processing state does not affect the signal state.

- 3. All inputs are 5 V tolerant.

Freescale Semiconductor 1-13

Table 2-4. Internal Clocks, CLKOUT (Continued)

| Characteristics                                        | Symbol           | Expression <sup>1, 2</sup> |                     |     |  |

|--------------------------------------------------------|------------------|----------------------------|---------------------|-----|--|

| Citalacteristics                                       | Symbol           | Min                        | Тур                 | Мах |  |

| Internal clock and CLKOUT cycle time with PLL disabled | T <sub>C</sub>   | _                          | 2 × ET <sub>C</sub> | _   |  |

| Instruction cycle time                                 | I <sub>CYC</sub> | _                          | T <sub>C</sub>      | _   |  |

Notes: 1. DF = Division Factor; Ef = External frequency; ET<sub>C</sub> = External clock cycle; MF = Multiplication Factor; PDF = Predivision Factor; T<sub>C</sub> = internal clock cycle

2. See the PLL and Clock Generation section in the DSP56300 Family Manual for a detailed discussion of the PLL.

#### 2.5.2 External Clock Operation

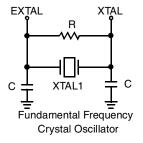

The DSP56303 system clock is derived from the on-chip oscillator or is externally supplied. To use the on-chip oscillator, connect a crystal and associated resistor/capacitor components to EXTAL and XTAL; examples are shown in **Figure 2-1**.

**Note:** Make sure that in the PCTL Register:

- XTLD (bit 16) = 0

- If f<sub>OSC</sub> > 200 kHz, XTLR (bit 15) = 0

#### **Suggested Component Values:**

$$\begin{split} &f_{OSC} = 4 \text{ MHz} \\ &R = 680 \text{ } k\Omega \pm 10\% \\ &C = 56 \text{ } pF \pm 20\% \end{split} \qquad \begin{aligned} &f_{OSC} = 20 \text{ MHz} \\ &R = 680 \text{ } k\Omega \pm 10\% \\ &C = 22 \text{ } pF \pm 20\% \end{aligned}$$

Calculations were done for a 4/20 MHz crystal with the following parameters:

- C<sub>L</sub>of 30/20 pF,

- C<sub>0</sub> of 7/6 pF,

- series resistance of 100/20  $\Omega$ , and

- · drive level of 2 mW.

Figure 2-1. Crystal Oscillator Circuits

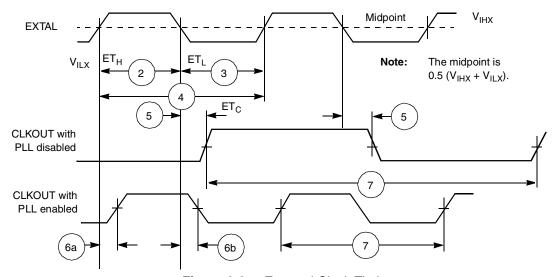

If an externally-supplied square wave voltage source is used, disable the internal oscillator circuit during bootup by setting XTLD (PCTL Register bit 16 = 1—see the *DSP56303 User's Manual*). The external square wave source connects to EXTAL; XTAL is not physically connected to the board or socket. **Figure 2-2** shows the relationship between the EXTAL input and the internal clock and CLKOUT.

Figure 2-2. External Clock Timing

DSP56303 Technical Data, Rev. 11

2-4 Freescale Semiconductor

Table 2-5. Clock Operation

| No. | Characteristics                                                                                                                                                   | Symbol           | 100 MHz              |               |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|---------------|--|

| NO. | Cital acteristics                                                                                                                                                 | Symbol           | Min                  | Max           |  |

| 1   | Frequency of EXTAL (EXTAL Pin Frequency) The rise and fall time of this external clock should be 3 ns maximum.                                                    | Ef               | 0                    | 100.0         |  |

| 2   | EXTAL input high <sup>1, 2</sup> • With PLL disabled (46.7%–53.3% duty cycle <sup>6</sup> ) • With PLL enabled (42.5%–57.5% duty cycle <sup>6</sup> )             | ET <sub>H</sub>  | 4.67 ns<br>4.25 ns   | ∞<br>157.0 μs |  |

| 3   | EXTAL input low <sup>1, 2</sup> • With PLL disabled (46.7%–53.3% duty cycle <sup>6</sup> ) • With PLL enabled (42.5%–57.5% duty cycle <sup>6</sup> )              | ETL              | 4.67 ns<br>4.25 ns   | ∞<br>157.0 μs |  |

| 4   | EXTAL cycle time <sup>2</sup> • With PLL disabled  • With PLL enabled                                                                                             | ET <sub>C</sub>  | 10.00 ns<br>10.00 ns | ∞<br>273.1 μs |  |

| 5   | Internal clock change from EXTAL fall with PLL disabled                                                                                                           |                  | 4.3 ns               | 11.0 ns       |  |

| 6   | a.Internal clock rising edge from EXTAL rising edge with PLL enabled (MF = 1 or 2 or 4, PDF = 1, Ef > 15 MHz) $^{3,5}$                                            |                  | 0.0 ns               | 1.8 ns        |  |

|     | b. Internal clock falling edge from EXTAL falling edge with PLL enabled (MF $\leq\!\!4$ , PDF $\neq$ 1, $\;$ Ef / PDF > 15 MHz)^3.5                               |                  | 0.0 ns               | 1.8 ns        |  |

| 7   | Instruction cycle time = I <sub>CYC</sub> = T <sub>C</sub> <sup>4</sup> (see <b>Table 2-4</b> ) (46.7%–53.3% duty cycle)  • With PLL disabled  • With PLL enabled | I <sub>CYC</sub> | 20.0 ns<br>10.00 ns  | ∞<br>8.53 μs  |  |

#### Notes:

- 1. Measured at 50 percent of the input transition.

- 2. The maximum value for PLL enabled is given for minimum VCO frequency (see Table 2-4) and maximum MF.

- 3. Periodically sampled and not 100 percent tested.

- 4. The maximum value for PLL enabled is given for minimum VCO frequency and maximum DF.

- 5. The skew is not guaranteed for any other MF value.

- 6. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time required for correction operation, however, remains the same at lower operating frequencies; therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time requirements are met.

## 2.5.3 Phase Lock Loop (PLL) Characteristics

Table 2-6. PLL Characteristics

| Characteristics                                                                                                 | 100                         | 100 MHz                      |          |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------|----------|--|--|

| Characteristics                                                                                                 | Min Max                     |                              | Unit     |  |  |

| Voltage Controlled Oscillator (VCO) frequency when PLL enabled (MF $\times$ E <sub>f</sub> $\times$ 2/PDF)      | 30                          | 200                          | MHz      |  |  |

| PLL external capacitor (PCAP pin to V <sub>CCP</sub> ) (C <sub>PCAP</sub> <sup>1</sup> )  • @ MF ≤4  • @ MF > 4 | (580 × MF) –100<br>830 × MF | (780 × MF) –140<br>1470 × MF | pF<br>pF |  |  |

**Note:** C<sub>PCAP</sub> is the value of the PLL capacitor (connected between the PCAP pin and V<sub>CCP</sub>) computed using the appropriate expression listed above.

Freescale Semiconductor 2-5

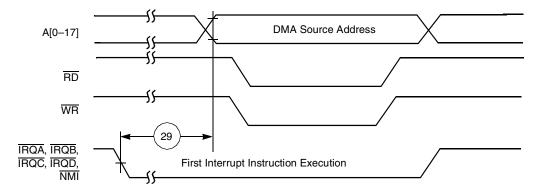

Figure 2-9. Recovery from Stop State Using IRQA

Figure 2-10. Recovery from Stop State Using IRQA Interrupt Service

Figure 2-11. External Memory Access (DMA Source) Timing

# 2.5.5 External Memory Expansion Port (Port A)

## 2.5.5.1 SRAM Timing

Table 2-8. SRAM Read and Write Accesses

|     |                                                               |                                    | - · 1                                                                            | 100          | MHz  |          |

|-----|---------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------|--------------|------|----------|

| No. | Characteristics                                               | Symbol                             | Expression <sup>1</sup>                                                          | Min          | Max  | Unit     |

| 100 | Address valid and AA assertion pulse width <sup>2</sup>       | t <sub>RC</sub> , t <sub>WC</sub>  | $(WS + 1) \times T_C - 4.0$<br>$[1 \le WS \le 3]$<br>$(WS + 2) \times T_C - 4.0$ | 16.0<br>56.0 | _    | ns<br>ns |

|     |                                                               |                                    | [4 $\leq$ WS $\leq$ 7]<br>(WS + 3) $\times$ T <sub>C</sub> -4.0<br>[WS $\geq$ 8] | 106.0        | _    | ns       |

| 101 | Address and AA valid to WR assertion                          | t <sub>AS</sub>                    | 0.25 × T <sub>C</sub> –2.0<br>[WS = 1]                                           | 0.5          | _    | ns       |

|     |                                                               |                                    | 0.75 × T <sub>C</sub> −2.0<br>[2 ≤WS ≤3]                                         | 5.5          | _    | ns       |

|     |                                                               |                                    | $1.25 \times T_{C} - 2.0$ [WS $\geq 4$ ]                                         | 10.5         | _    | ns       |

| 102 | WR assertion pulse width                                      | t <sub>WP</sub>                    | $1.5 \times T_{C} - 4.0$ [WS = 1]                                                | 11.0         | _    | ns       |

|     |                                                               |                                    | WS × T <sub>C</sub> −4.0<br>[2 ≤WS ≤3]                                           | 16.0         | _    | ns       |

|     |                                                               |                                    | $(WS - 0.5) \times T_C - 4.0$<br>$[WS \ge 4]$                                    | 31.0         | _    | ns       |

| 103 | WR deassertion to address not valid                           | t <sub>WR</sub>                    | 0.25 × T <sub>C</sub> −2.0<br>[1 ≤WS ≤3]                                         | 0.5          | _    | ns       |

|     |                                                               |                                    | 1.25 × T <sub>C</sub> −4.0<br>[4 ≤WS ≤7]                                         | 8.5          | _    | ns       |

|     |                                                               |                                    | $2.25 \times T_{C} - 4.0$ [WS $\geq$ 8]                                          | 18.5         | _    | ns       |

| 104 | Address and AA valid to input data valid                      | t <sub>AA</sub> , t <sub>AC</sub>  | $(WS + 0.75) \times T_C -5.0$<br>$[WS \ge 1]$                                    | _            | 12.5 | ns       |

| 105 | RD assertion to input data valid                              | t <sub>OE</sub>                    | $(WS + 0.25) \times T_C - 5.0$ $[WS \ge 1]$                                      | _            | 7.5  | ns       |

| 106 | RD deassertion to data not valid (data hold time)             | t <sub>OHZ</sub>                   |                                                                                  | 0.0          | _    | ns       |

| 107 | Address valid to $\overline{\rm WR}$ deassertion <sup>2</sup> | t <sub>AW</sub>                    | $(WS + 0.75) \times T_C -4.0$<br>[WS \ge 1]                                      | 13.5         | _    | ns       |

| 108 | Data valid to WR deassertion (data setup time)                | t <sub>DS</sub> (t <sub>DW</sub> ) | $(WS -0.25) \times T_C -3.0$ $[WS \ge 1]$                                        | 4.5          |      | ns       |

| 109 | Data hold time from WR deassertion                            | t <sub>DH</sub>                    | 0.25 × T <sub>C</sub> −2.0<br>[1 ≤WS ≤3]                                         | 0.5          | _    | ns       |

|     |                                                               |                                    | 1.25 × T <sub>C</sub> −2.0<br>[4 ≤WS ≤7]                                         | 10.5         | _    | ns       |

|     |                                                               |                                    | $2.25 \times T_{C} - 2.0$ [WS $\geq 8$ ]                                         | 20.5         | _    | ns       |

| 110 | WR assertion to data active                                   | _                                  | $0.75 \times T_{C} - 3.7$ [WS = 1]                                               | 3.8          |      | ns       |

|     |                                                               |                                    | 0.25 × T <sub>C</sub> − 3.7<br>[2 ⊴WS ≤3]                                        | -1.2         | _    | ns       |

|     |                                                               |                                    | $-0.25 \times T_{C} -3.7$ [WS $\geq 4$ ]                                         | -6.2         | _    | ns       |

## 2.5.5.4 Arbitration Timings

**Table 2-14.** Arbitration Bus Timings<sup>1</sup>

| <b>.</b> | Characteristics                                      | F2                                   | 100 | 11 !** |      |

|----------|------------------------------------------------------|--------------------------------------|-----|--------|------|

| No.      | Characteristics                                      | Expression <sup>2</sup>              | Min | Max    | Unit |

| 212      | CLKOUT high to BR assertion/deassertion <sup>3</sup> |                                      | 0.0 | 4.0    | ns   |

| 213      | BG asserted/deasserted to CLKOUT high (setup)        |                                      | 4.0 | _      | ns   |

| 214      | CLKOUT high to BG deasserted/asserted (hold)         |                                      | 0.0 | _      | ns   |

| 215      | BB deassertion to CLKOUT high (input set-up)         |                                      | 4.0 | _      | ns   |

| 216      | CLKOUT high to BB assertion (input hold)             |                                      | 0.0 | _      | ns   |

| 217      | CLKOUT high to BB assertion (output)                 |                                      | 0.0 | 4.0    | ns   |

| 218      | CLKOUT high to BB deassertion (output)               |                                      | 0.0 | 4.0    | ns   |

| 219      | BB high to BB high impedance (output)                |                                      | _   | 4.5    | ns   |

| 220      | CLKOUT high to address and controls active           | 0.25 × T <sub>C</sub>                | 2.5 | _      | ns   |

| 221      | CLKOUT high to address and controls high impedance   | 0.75 × T <sub>C</sub>                | _   | 7.5    | ns   |

| 222      | CLKOUT high to AA active                             | 0.25 × T <sub>C</sub>                | 2.5 | _      | ns   |

| 223      | CLKOUT high to AA deassertion                        | maximum: 0.25 × T <sub>C</sub> + 4.0 | 2.0 | 6.5    | ns   |

| 224      | CLKOUT high to AA high impedance                     | 0.75 × T <sub>C</sub>                | _   | 7.5    | ns   |

#### Notes:

- 1. Synchronous bus arbitration is not recommended. Use Asynchronous mode whenever possible.

- 2. An expression is used to compute the maximum or minimum value listed, as appropriate. For timing 223, the minimum is an absolute value.

- 3. T212 is valid for Address Trace mode when the ATE bit in the Operating Mode Register is set. BR is deasserted for internal accesses and asserted for external accesses.

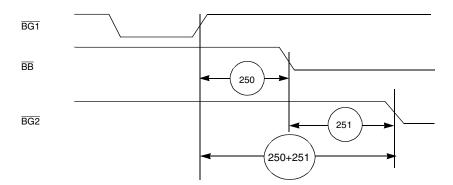

#### 2.5.5.5 Asynchronous Bus Arbitration Timings

**Table 2-15.** Asynchronous Bus Timings<sup>1, 2</sup>

| No.  | Characteristics                                                                | Expression <sup>3</sup> | 100 MHz <sup>4</sup> |     | Unit  |

|------|--------------------------------------------------------------------------------|-------------------------|----------------------|-----|-------|

| 140. | Characteristics                                                                | Expression              | Min                  | Max | Oiiit |

| 250  | BB assertion window from BG input deassertion <sup>5</sup>                     | 2.5 × Tc + 5            |                      | 30  | ns    |

| 251  | Delay from $\overline{BB}$ assertion to $\overline{BG}$ assertion <sup>5</sup> | 2 × Tc + 5              | 25                   | _   | ns    |

Notes:

- . Bit 13 in the Operating Mode Register must be set to enter Asynchronous Arbitration mode.

- 2. If Asynchronous Arbitration mode is active, none of the timings in Table 2-14 is required.

- 3. An expression is used to compute the maximum or minimum value listed, as appropriate.

- 4. Asynchronous Arbitration mode is recommended for operation at 100 MHz.

- 5. In order to guarantee timings 250, and 251, BG inputs must be asserted to different DSP56300 devices on the same bus in the non-overlap manner shown in Figure 2-26.

Figure 2-26. Asynchronous Bus Arbitration Timing

The asynchronous bus arbitration is enabled by internal synchronization circuits on  $\overline{BG}$  and  $\overline{BB}$  inputs. These synchronization circuits add delay from the external signal until it is exposed to internal logic. As a result of this delay, a DSP56300 part may assume mastership and assert  $\overline{BB}$ , for some time after  $\overline{BG}$  is deasserted. This is the reason for timing 250.

Once  $\overline{BB}$  is asserted, there is a synchronization delay from  $\overline{BB}$  assertion to the time this assertion is exposed to other DSP56300 components that are potential masters on the same bus. If  $\overline{BG}$  input is asserted before that time, and  $\overline{BG}$  is asserted and  $\overline{BB}$  is deasserted, another DSP56300 component may assume mastership at the same time.

Therefore, some non-overlap period between one BG input active to another BG input active is required. Timing 251 ensures that overlaps are avoided.

Freescale Semiconductor 2-29

2-33

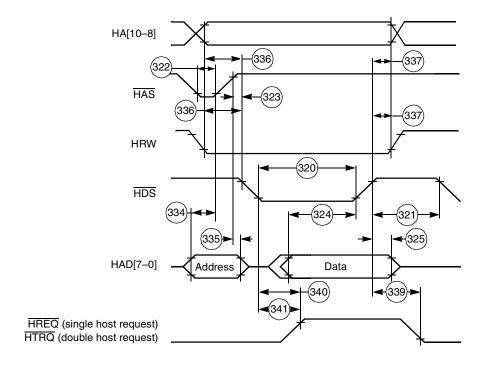

Figure 2-30. Write Timing Diagram, Non-Multiplexed Bus, Single Data Strobe

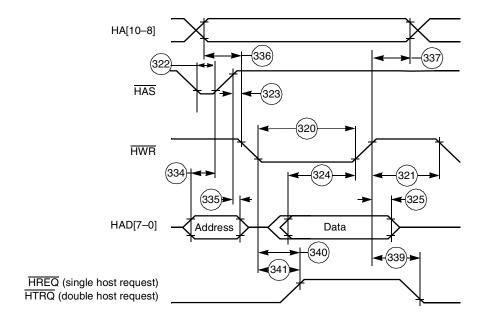

Figure 2-31. Write Timing Diagram, Non-Multiplexed Bus, Double Data Strobe

Freescale Semiconductor

Figure 2-34. Write Timing Diagram, Multiplexed Bus, Single Data Strobe

Figure 2-35. Write Timing Diagram, Multiplexed Bus, Double Data Strobe

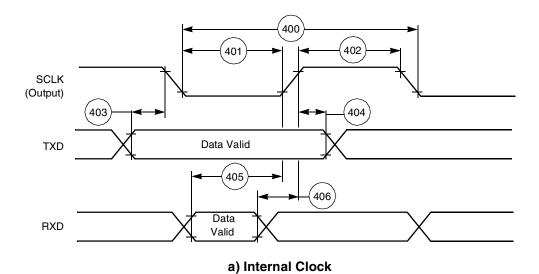

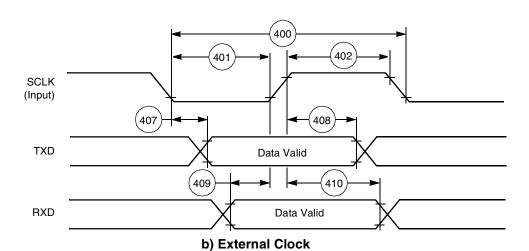

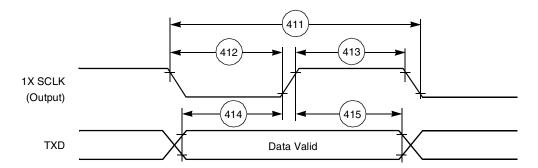

Figure 2-36. SCI Synchronous Mode Timing

Figure 2-37. SCI Asynchronous Mode Timing

# 2.5.8 ESSI0/ESSI1 Timing

Table 2-18. ESSI Timings

| No.  | Characteristics <sup>4, 5, 7</sup>                                        | Symbol             | Expression <sup>9</sup>                                   | 100          | MHz          | Cond-              | Unit     |

|------|---------------------------------------------------------------------------|--------------------|-----------------------------------------------------------|--------------|--------------|--------------------|----------|

| 140. |                                                                           |                    | Expression                                                | Min          | Max          | ition <sup>5</sup> |          |

| 430  | Clock cycle <sup>1</sup>                                                  | t <sub>ssicc</sub> | $\begin{array}{c} 3\times T_C \\ 4\times T_C \end{array}$ | 30.0<br>40.0 |              | x ck<br>i ck       | ns       |

| 431  | Clock high period  For internal clock  For external clock                 |                    | 2 × T <sub>C</sub> - 10.0<br>1.5 × T <sub>C</sub>         | 10.0<br>15.0 | _            |                    | ns<br>ns |

| 432  | Clock low period  For internal clock  For external clock                  |                    | $2 \times T_{C} - 10.0$ $1.5 \times T_{C}$                | 10.0<br>15.0 | _<br>_       |                    | ns<br>ns |

| 433  | RXC rising edge to FSR out (bit-length) high                              |                    |                                                           |              | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 434  | RXC rising edge to FSR out (bit-length) low                               |                    |                                                           | _            | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 435  | RXC rising edge to FSR out (word-length-relative) high <sup>2</sup>       |                    |                                                           | _<br>_       | 39.0<br>37.0 | x ck<br>i ck a     | ns       |

| 436  | RXC rising edge to FSR out (word-length-relative) low <sup>2</sup>        |                    |                                                           | _            | 39.0<br>37.0 | x ck<br>i ck a     | ns       |

| 437  | RXC rising edge to FSR out (word-length) high                             |                    |                                                           | _<br>_       | 36.0<br>21.0 | x ck<br>i ck a     | ns       |

| 438  | RXC rising edge to FSR out (word-length) low                              |                    |                                                           | _            | 37.0<br>22.0 | x ck<br>i ck a     | ns       |

| 439  | Data in set-up time before RXC (SCK in Synchronous mode) falling edge     |                    |                                                           | 10.0<br>19.0 | _            | x ck<br>i ck       | ns       |

| 440  | Data in hold time after RXC falling edge                                  |                    |                                                           | 5.0<br>3.0   | _            | x ck<br>i ck       | ns       |

| 441  | FSR input (bl, wr) <sup>7</sup> high before RXC falling edge <sup>2</sup> |                    |                                                           | 1.0<br>23.0  | _            | x ck<br>i ck a     | ns       |

| 442  | FSR input (wl) <sup>7</sup> high before RXC falling edge                  |                    |                                                           | 3.5<br>23.0  | _<br>_       | x ck<br>i ck a     | ns       |

| 443  | FSR input hold time after RXC falling edge                                |                    |                                                           | 3.0<br>0.0   | _<br>_       | x ck<br>i ck a     | ns       |

| 444  | Flags input set-up before RXC falling edge                                |                    |                                                           | 5.5<br>19.0  | _            | x ck<br>i ck s     | ns       |

| 445  | Flags input hold time after RXC falling edge                              |                    |                                                           | 6.0<br>0.0   | _            | x ck<br>i ck s     | ns       |

| 446  | TXC rising edge to FST out (bit-length) high                              |                    |                                                           | _            | 29.0<br>15.0 | x ck<br>i ck       | ns       |

| 447  | TXC rising edge to FST out (bit-length) low                               |                    |                                                           | _            | 31.0<br>17.0 | x ck<br>i ck       | ns       |

| 448  | TXC rising edge to FST out (word-length-relative) high <sup>2</sup>       |                    |                                                           | _<br>_       | 31.0<br>17.0 | x ck<br>i ck       | ns       |

| 449  | TXC rising edge to FST out (word-length-relative) low <sup>2</sup>        |                    |                                                           | _<br>_       | 33.0<br>19.0 | x ck<br>i ck       | ns       |

| 450  | TXC rising edge to FST out (word-length) high                             |                    |                                                           | _<br>_       | 30.0<br>16.0 | x ck<br>i ck       | ns       |

| 451  | TXC rising edge to FST out (word-length) low                              |                    |                                                           |              | 31.0<br>17.0 | x ck<br>i ck       | ns       |

| 452  | TXC rising edge to data out enable from high impedance                    |                    |                                                           |              | 31.0<br>17.0 | x ck<br>i ck       | ns       |

2-38 Freescale Semiconductor

Table 3-1. DSP56303 TQFP Signal Identification by Pin Number (Continued)

| Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name      |

|------------|------------------|------------|------------------|------------|------------------|

| 76         | A2               | 99         | A17              | 122        | D16              |

| 77         | A3               | 100        | D0               | 123        | D17              |

| 78         | A4               | 101        | D1               | 124        | D18              |

| 79         | A5               | 102        | D2               | 125        | D19              |

| 80         | V <sub>CCA</sub> | 103        | V <sub>CCD</sub> | 126        | V <sub>CCQ</sub> |

| 81         | GND <sub>A</sub> | 104        | GND <sub>D</sub> | 127        | GND <sub>Q</sub> |

| 82         | A6               | 105        | D3               | 128        | D20              |

| 83         | A7               | 106        | D4               | 129        | V <sub>CCD</sub> |

| 84         | A8               | 107        | D5               | 130        | GND <sub>D</sub> |

| 85         | A9               | 108        | D6               | 131        | D21              |

| 86         | V <sub>CCA</sub> | 109        | D7               | 132        | D22              |

| 87         | GND <sub>A</sub> | 110        | D8               | 133        | D23              |

| 88         | A10              | 111        | V <sub>CCD</sub> | 134        | MODD/IRQD        |

| 89         | A11              | 112        | GND <sub>D</sub> | 135        | MODC/IRQC        |

| 90         | GND <sub>Q</sub> | 113        | D9               | 136        | MODB/IRQB        |

| 91         | V <sub>CCQ</sub> | 114        | D10              | 137        | MODA/IRQA        |

| 92         | A12              | 115        | D11              | 138        | TRST             |

| 93         | A13              | 116        | D12              | 139        | TDO              |

| 94         | A14              | 117        | D13              | 140        | TDI              |

| 95         | V <sub>CCA</sub> | 118        | D14              | 141        | тск              |

| 96         | GND <sub>A</sub> | 119        | V <sub>CCD</sub> | 142        | TMS              |

| 97         | A15              | 120        | GND <sub>D</sub> | 143        | SC12 or PD2      |

| 98         | A16              | 121        | D15              | 144        | SC11 or PD1      |

Notes: Signal names are based on configured functionality. Most pins supply a single signal. Some pins provide a signal with dual functionality, such as the MODx/IRQx pins that select an operating mode after RESET is deasserted but act as interrupt lines during operation. Some signals have configurable polarity; these names are shown with and without overbars, such as HAS/HAS. Some pins have two or more configurable functions; names assigned to these pins indicate the function for a specific configuration. For example, Pin 34 is data line H7 in non-multiplexed bus mode, data/address line HAD7 in multiplexed bus mode, or GPIO line PB7 when the GPIO function is enabled for this pin.

Freescale Semiconductor 3-5

Table 3-3.

DSP56303 MAP-BGA Signal Identification by Pin Number (Continued)

| Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name                      | Pin<br>No. | Signal Name                      |

|------------|------------------|------------|----------------------------------|------------|----------------------------------|

| F6         | GND              | Н3         | SCK0 or PC3                      | J14        | A9                               |

| F7         | GND              | H4         | GND                              | K1         | V <sub>CCS</sub>                 |

| F8         | GND              | H5         | GND                              | K2         | HREQ/HREQ,<br>HTRQ/HTRQ, or PB14 |

| F9         | GND              | Н6         | GND                              | К3         | TIO2                             |

| F10        | GND              | H7         | GND                              | K4         | GND                              |

| F11        | GND              | Н8         | GND                              | K5         | GND                              |

| F12        | V <sub>CCA</sub> | Н9         | GND                              | K6         | GND                              |

| F13        | A14              | H10        | GND                              | K7         | GND                              |

| F14        | A15              | H11        | GND                              | K8         | GND                              |

| G1         | SCK1 or PD3      | H12        | V <sub>CCA</sub>                 | K9         | GND                              |

| G2         | SCLK or PE2      | H13        | A10                              | K10        | GND                              |

| G3         | TXD or PE1       | H14        | A11                              | K11        | GND                              |

| G4         | GND              | J1         | HACK/HACK,<br>HRRQ/HRRQ, or PB15 | K12        | V <sub>CCA</sub>                 |

| G5         | GND              | J2         | HRW, HRD/HRD, or PB11            | K13        | A5                               |

| G6         | GND              | J3         | HDS/HDS, HWR/HWR, or PB12        | K14        | A6                               |

| G7         | GND              | J4         | GND                              | L1         | HCS/HCS, HA10, or PB13           |

| G8         | GND              | J5         | GND                              | L2         | TIO1                             |

| G9         | GND              | J6         | GND                              | L3         | TIO0                             |

| G10        | GND              | J7         | GND                              | L4         | GND                              |

| G11        | GND              | J8         | GND                              | L5         | GND                              |

| G12        | A13              | J9         | GND                              | L6         | GND                              |

| G13        | V <sub>CCQ</sub> | J10        | GND                              | L7         | GND                              |

| G14        | A12              | J11        | GND                              | L8         | GND                              |

| H1         | NC               | J12        | A8                               | L9         | GND                              |

| H2         | V <sub>CCQ</sub> | J13        | A7                               | L10        | GND                              |

| L11        | GND              | M13        | A1                               | P1         | NC                               |

| L12        | V <sub>CCA</sub> | M14        | A2                               | P2         | H5, HAD5, or PB5                 |

| L13        | А3               | N1         | H6, HAD6, or PB6                 | Р3         | H3, HAD3, or PB3                 |

| L14        | A4               | N2         | H7, HAD7, or PB7                 | P4         | H1, HAD1, or PB1                 |

DSP56303 Technical Data, Rev. 11

Freescale Semiconductor 3-13

DSP56303 MAP-BGA Signal Identification by Pin Number (Continued) **Table 3-3.**

| Pin<br>No. | Signal Name          | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name       |

|------------|----------------------|------------|------------------|------------|-------------------|

| M1         | HA1, HA8, or PB9     | N3         | H4, HAD4, or PB4 | P5         | PCAP              |

| M2         | HA2, HA9, or PB10    | N4         | H2, HAD2, or PB2 | P6         | GND <sub>P1</sub> |

| МЗ         | HA0, HAS/HAS, or PB8 | N5         | RESET            | P7         | AA2/RAS2          |

| M4         | V <sub>CCH</sub>     | N6         | GND <sub>P</sub> | P8         | XTAL              |

| M5         | H0, HAD0, or PB0     | N7         | AA3/RAS3         | P9         | V <sub>CCC</sub>  |

| M6         | V <sub>CCP</sub>     | N8         | CAS              | P10        | TA                |

| M7         | NC                   | N9         | V <sub>CCQ</sub> | P11        | BB                |

| M8         | EXTAL                | N10        | BCLK             | P12        | AA1/RAS1          |

| M9         | CLKOUT               | N11        | BR               | P13        | BG                |

| M10        | BCLK                 | N12        | V <sub>CCC</sub> | P14        | NC                |

| M11        | WR                   | N13        | AA0/RAS0         |            |                   |

| M12        | RD                   | N14        | Α0               |            |                   |

Signal names are based on configured functionality. Most connections supply a single signal. Some connections provide a signal with dual functionality, such as the MODx/IRQx pins that select an operating mode after RESET is deasserted but act as interrupt lines during operation. Some signals have configurable polarity; these names are shown with and without overbars, such as HAS/HAS. Some connections have two or more configurable functions; names assigned to these connections indicate the function for a specific configuration. For example, connection N2 is data line H7 in non-multiplexed bus mode, data/address line HAD7 in multiplexed bus mode, or GPIO line PB7 when the GPIO function is enabled for this pin. Unlike in the TQFP package, most of the GND pins are connected internally in the center of the connection array and act as heat sink for the chip. Therefore, except for GNDP and GND<sub>P1</sub> that support the PLL, other GND signals do not support individual subsystems in the chip.

3-14 Freescale Semiconductor

Table 3-4. DSP56303 MAP-BGA Signal Identification by Name (Continued)

| Signal Name      | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name      | Pin<br>No. |

|------------------|------------|------------------|------------|------------------|------------|

| TDO              | A4         | V <sub>CCA</sub> | K12        | V <sub>CCP</sub> | M6         |

| TIO0             | L3         | V <sub>CCA</sub> | L12        | V <sub>CCQ</sub> | C7         |

| TIO1             | L2         | V <sub>ccc</sub> | N12        | V <sub>CCQ</sub> | G13        |

| TIO2             | К3         | V <sub>CCC</sub> | P9         | V <sub>CCQ</sub> | H2         |

| TMS              | А3         | V <sub>CCD</sub> | A7         | V <sub>CCQ</sub> | N9         |

| TRST             | B4         | V <sub>CCD</sub> | С9         | V <sub>CCS</sub> | E2         |

| TXD              | G3         | V <sub>CCD</sub> | C11        | V <sub>CCS</sub> | K1         |

| V <sub>CCA</sub> | F12        | V <sub>CCD</sub> | D14        | WR               | M11        |

| V <sub>CCA</sub> | H12        | V <sub>CCH</sub> | M4         | XTAL             | P8         |

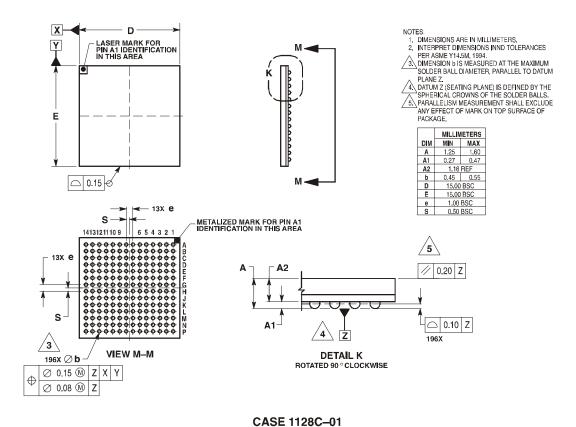

## 3.4 MAP-BGA Package Mechanical Drawing

Figure 3-6. DSP56303 Mechanical Information, 196-pin MAP-BGA Package

**DATE 07/28/98**

**ISSUE 0**

DSP56303 Technical Data, Rev. 11

3-18 Freescale Semiconductor

- Consider all device loads as well as parasitic capacitance due to PCB traces when you calculate

capacitance. This is especially critical in systems with higher capacitive loads that could create higher

transient currents in the V<sub>CC</sub> and GND circuits.

- All inputs must be terminated (that is, not allowed to float) by CMOS levels except for the three pins with internal pull-up resistors (TRST, TMS, DE).

- Take special care to minimize noise levels on the V<sub>CCP</sub>, GND<sub>P</sub>, and GND<sub>P1</sub> pins.

- The following pins must be asserted after power-up: RESET and TRST.

- If multiple DSP devices are on the same board, check for cross-talk or excessive spikes on the supplies due to synchronous operation of the devices.

- RESET must be asserted when the chip is powered up. A stable EXTAL signal should be supplied before deassertion of RESET.

- At power-up, ensure that the voltage difference between the 5 V tolerant pins and the chip V<sub>CC</sub> never exceeds 3.5 V.

## 4.3 Power Consumption Considerations

Power dissipation is a key issue in portable DSP applications. Some of the factors affecting current consumption are described in this section. Most of the current consumed by CMOS devices is alternating current (ac), which is charging and discharging the capacitances of the pins and internal nodes.

Current consumption is described by this formula:

**Equation 3:**

$$I = C \times V \times f$$

Where:

C = node/pin capacitance

V = voltage swing

f = frequency of node/pin toggle

#### Example 4-1. Current Consumption

For a Port A address pin loaded with 50 pF capacitance, operating at 3.3 V, with a 66 MHz clock, toggling at its maximum possible rate (33 MHz), the current consumption is expressed in **Equation 4**.

**Equation 4:**

$$I = 50 \times 10^{-12} \times 3.3 \times 33 \times 10^{6} = 5.48 \text{ mA}$$

The maximum internal current ( $I_{CCI}$ max) value reflects the typical possible switching of the internal buses on best-case operation conditions—not necessarily a real application case. The typical internal current ( $I_{CCItyp}$ ) value reflects the average switching of the internal buses on typical operating conditions.

Perform the following steps for applications that require very low current consumption:

- 1. Set the EBD bit when you are not accessing external memory.

- 2. Minimize external memory accesses, and use internal memory accesses.

- **3.** Minimize the number of pins that are switching.

- **4.** Minimize the capacitive load on the pins.

- **5.** Connect the unused inputs to pull-up or pull-down resistors.

DSP56303 Technical Data, Rev. 11

Freescale Semiconductor 4-3

# 4.5 Input (EXTAL) Jitter Requirements

The allowed jitter on the frequency of EXTAL is 0.5 percent. If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the allowed jitter can be 2 percent. The phase and frequency jitter performance results are valid only if the input jitter is less than the prescribed values.

Freescale Semiconductor 4-5

```

$6162BC

dc

dс

$E4A245

YDAT_END

EQUATES for DSP56303 I/O registers and ports

Last update: June 11 1995

page 132,55,0,0,0

opt

mex

ioequ ident 1,0

;-----

EQUATES for I/O Port Programming

;------

; Register Addresses

; Host port GPIO data Register

M_HDR EQU $FFFFC9

; Host port GPIO direction Register

M_HDDR EQU $FFFFC8

; Port C Control Register

M_PCRC EQU $FFFFBF

; Port C Direction Register

M_PRRC EQU $FFFFBE

; Port C GPIO Data Register

M_PDRC EQU $FFFFBD

M_PCRD EQU $FFFFAF

; Port D Control register

M_PRRD EQU $FFFFAE

; Port D Direction Data Register

M_PDRD EQU $FFFFAD

; Port D GPIO Data Register

M_PCRE EQU $FFFF9F

; Port E Control register

; Port E Direction Register

M_PRRE EQU $FFFF9E

M_PDRE EQU $FFFF9D

; Port E Data Register

M_OGDB EQU $FFFFFC

; OnCE GDB Register

;-----

EQUATES for Host Interface

;-----

Register Addresses

; Host Control Register

M_HCR EQU $FFFFC2

; Host Status Register

M_HSR EQU $FFFFC3

; Host Polarity Control Register

M_HPCR EQU $FFFFC4

; Host Base Address Register

M_HBAR EQU $FFFFC5

; Host Receive Register

M_HRX EQU $FFFFC6

M_HTX EQU $FFFFC7

; Host Transmit Register

HCR bits definition

M_HRIE EQU $0

; Host Receive interrupts Enable

; Host Transmit Interrupt Enable

M_HTIE EQU $1

M_HCIE EQU $2

; Host Command Interrupt Enable

M_HF2 EQU $3

; Host Flag 2

M_HF3 EQU $4

; Host Flag 3

```

DSP56303 Technical Data, Rev. 11

Freescale Semiconductor A-5