#### NXP USA Inc. - DSP56303VL100B1 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

| Details | 5 |

|---------|---|

|---------|---|

| Detalls                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 100MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 24kB                                                                    |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 3.30V                                                                   |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-LBGA                                                                |

| Supplier Device Package | 196-LBGA (15x15)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56303vl100b1 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|           |       | Data Sheet Conventions                          | ii   |

|-----------|-------|-------------------------------------------------|------|

|           |       | Features                                        |      |

|           |       | Target Applications                             | iv   |

|           |       | Product Documentation                           | iv   |

| Chapter 1 | Signa | als/Connections                                 |      |

|           | 1.1   | Power                                           | 1-3  |

|           | 1.2   | Ground                                          |      |

|           | 1.3   | Clock                                           | 1-4  |

|           | 1.5   | External Memory Expansion Port (Port A)         | 1-4  |

|           | 1.6   | Interrupt and Mode Control                      | 1-7  |

|           | 1.7   | Host Interface (HI08)                           |      |

|           | 1.8   | Enhanced Synchronous Serial Interface 0 (ESSI0) | 1-11 |

|           | 1.9   | Enhanced Synchronous Serial Interface 1 (ESSI1) | 1-12 |

|           | 1.10  | Serial Communication Interface (SCI)            | 1-14 |

|           | 1.11  | Timers                                          | 1-15 |

|           | 1.12  | JTAG and OnCE Interface                         | 1-16 |

| Chapter 2 | Spec  | ifications                                      |      |

|           | 2.1   | Maximum Ratings                                 | 2-1  |

|           | 2.3   | Thermal Characteristics                         | 2-2  |

|           | 2.4   | DC Electrical Characteristics                   | 2-2  |

|           | 2.5   | AC Electrical Characteristics                   | 2-3  |

| Chapter 3 | Packa | aging                                           |      |

|           | 3.1   | TQFP Package Description                        |      |

|           | 3.2   | TQFP Package Mechanical Drawing                 |      |

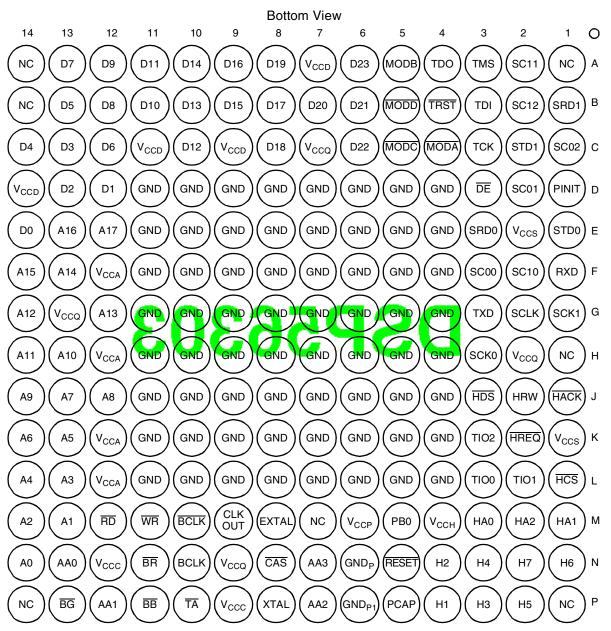

|           | 3.3   | MAP-BGA Package Description                     |      |

|           | 3.4   | MAP-BGA Package Mechanical Drawing              |      |

| Chapter 4 | Desig | gn Considerations                               |      |

|           | 4.1   | Thermal Design Considerations                   | 4-1  |

|           | 4.2   | Electrical Design Considerations                | 4-2  |

|           | 4.3   | Power Consumption Considerations                | 4-3  |

|           | 4.4   | PLL Performance Issues                          | 4-4  |

|           | 4.5   | Input (EXTAL) Jitter Requirements               | 4-5  |

|           |       |                                                 |      |

Appendix A Power Consumption Benchmark

## **Data Sheet Conventions**

| OVERBAR      | Indicates a signal that is active when pulled low (For example, the $\overline{RESET}$ pin is active when low.) |                             |                                 |                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|----------------------------------|

| "asserted"   | Means that a high true                                                                                          | e (active high) signal is l | nigh or that a low true (active | low) signal is low               |

| "deasserted" | Means that a high true                                                                                          | e (active high) signal is l | ow or that a low true (active l | ow) signal is high               |

|              |                                                                                                                 |                             |                                 |                                  |

| Examples:    | Signal/Symbol                                                                                                   | Logic State                 | Signal State                    | Voltage                          |

|              | PIN                                                                                                             | True                        | Asserted                        | V <sub>IL</sub> /V <sub>OL</sub> |

|              | PIN                                                                                                             | False                       | Deasserted                      | V <sub>IH</sub> /V <sub>OH</sub> |

|              | PIN                                                                                                             | True                        | Asserted                        | V <sub>IH</sub> /V <sub>OH</sub> |

|              |                                                                                                                 | 1100                        | 110001000                       |                                  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

## **Target Applications**

Examples include:

- Multi-line voice/data/fax processing

- Video conferencing

- Audio applications

- Control

# **Product Documentation**

The documents listed in **Table 2** are required for a complete description of the DSP56303 device and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Semiconductor Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back cover of this document.

| Name                      | Description                                                                                               | Order Number                     |

|---------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------|

| DSP56303<br>User's Manual | Detailed functional description of the DSP56303 memory configuration, operation, and register programming | DSP56303UM                       |

| DSP56300 Family<br>Manual | Detailed description of the DSP56300 family processor core and instruction set                            | DSP56300FM                       |

| Application Notes         | Documents describing specific applications or optimized device operation including code examples          | See the DSP56303 product website |

#### Table 2. DSP56303 Documentation

### 1.5.2 External Data Bus

| Table 1-7.         External Data Bus Signals |  |

|----------------------------------------------|--|

|----------------------------------------------|--|

| Signal<br>Name | Туре          | State<br>During<br>Reset | State<br>During Stop<br>or Wait                                        | Signal Description                                                                                                                                                                                                              |

|----------------|---------------|--------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0-23]        | Input/ Output | Ignored Input            | Last state:<br><i>Input</i> : Ignored<br><i>Output</i> :<br>Tri-stated | <b>Data Bus</b> —When the DSP is the bus master, D[0–23] are active-high, bidirectional input/outputs that provide the bidirectional data bus for external program and data memory accesses. Otherwise, D[0–23] are tri-stated. |

### 1.5.3 External Bus Control

| Table 1-8. | External Bus Control Signals  |

|------------|-------------------------------|

|            | External Bac Control Orginalo |

| Signal<br>Name | Туре   | State During Reset,<br>Stop, or Wait                                                                                                                                                                            | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA[0-3]        | Output | Tri-stated                                                                                                                                                                                                      | Address Attribute—When defined as AA, these signals can be used as chip selects or additional address lines. The default use defines a priority scheme under which only one AA signal can be asserted at a time. Setting the AA priority disable (APD) bit (Bit 14) of the Operating Mode Register, the priority mechanism is disabled and the lines can be used together as four external lines that can be decoded externally into 16 chip select signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RAS[0-3]       | Output |                                                                                                                                                                                                                 | <b>Row Address Strobe</b> —When defined as $\overline{RAS}$ , these signals can be used as $\overline{RAS}$ for DRAM interface. These signals are tri-statable outputs with programmable polarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RD             | Output | Tri-stated                                                                                                                                                                                                      | <b>Read Enable</b> —When the DSP is the bus master, $\overline{RD}$ is an active-low output that is asserted to read external memory on the data bus (D[0–23]). Otherwise, $\overline{RD}$ is tristated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WR             | Output | Tri-stated                                                                                                                                                                                                      | <b>Write Enable</b> —When the DSP is the bus master, $\overline{WR}$ is an active-low output that is asserted to write external memory on the data bus (D[0–23]). Otherwise, the signals are tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ΤΑ             | Input  | Ignored Input                                                                                                                                                                                                   | <b>Transfer Acknowledge</b> —If the DSP56303 is the bus master and there is no external bus activity, or the DSP56303 is not the bus master, the TA input is ignored. The TA input is a data transfer acknowledge (DTACK) function that can extend an external bus cycle indefinitely. Any number of wait states (1, 2 infinity) can be added to the wait states inserted by the bus control register (BCR) by keeping TA deasserted. In typical operation, TA is deasserted at the start of a bus cycle, is asserted to enable completion of the bus cycle, and is deasserted before the next bus cycle. The current bus cycle completes one clock period after TA is asserted synchronous to CLKOUT. The number of wait states is determined by the TA input or by the BCR, whichever is longer. The BCR can be used to set the minimum number of wait states in external bus cycles.                                                                                |

| BR             | Output | Reset: Output<br>(deasserted)<br>State during Stop/Wait<br>depends on BRH bit<br>setting:<br>• BRH = 0: Output,<br>deasserted<br>• BRH = 1: Maintains last<br>state (that is, if asserted,<br>remains asserted) | <b>Bus Request</b> —Asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independently of whether the DSP56303 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56303 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is affected only by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

## 1.8 Enhanced Synchronous Serial Interface 0 (ESSI0)

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for serial communication with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and peripherals that implement the serial peripheral interface (SPI).

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC00        | Input or Output | Ignored Input                        | <b>Serial Control 0</b> —For asynchronous mode, this signal is used for the receive clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used either for transmitter 1 output or for serial I/O flag 0.                                                                                                                                                                                 |

| PC0         | Input or Output |                                      | <b>Port C 0</b> —The default configuration following reset is GPIO input PC0. When configured as PC0, signal direction is controlled through the Port C Direction Register. The signal can be configured as ESSI signal SC00 through the Port C Control Register.                                                                                                                                          |

| SC01        | Input/Output    | Ignored Input                        | <b>Serial Control 1</b> —For asynchronous mode, this signal is the receiver frame sync I/O. For synchronous mode, this signal is used either for transmitter 2 output or for serial I/O flag 1.                                                                                                                                                                                                            |

| PC1         | Input or Output |                                      | <b>Port C 1</b> —The default configuration following reset is GPIO input PC1. When configured as PC1, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC01 through the Port C Control Register.                                                                                                                                       |

| SC02        | Input/Output    | Ignored Input                        | Serial Control Signal 2—The frame sync for both the transmitter and receiver<br>in synchronous mode, and for the transmitter only in asynchronous mode. When<br>configured as an output, this signal is the internally generated frame sync signal.<br>When configured as an input, this signal receives an external frame sync signal<br>for the transmitter (and the receiver in synchronous operation). |

| PC2         | Input or Output |                                      | <b>Port C 2</b> —The default configuration following reset is GPIO input PC2. When configured as PC2, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SC02 through the Port C Control Register.                                                                                                                                       |

| SCK0        | Input/Output    | Ignored Input                        | <b>Serial Clock</b> —Provides the serial bit rate clock for the ESSI. The SCK0 is a clock input or output, used by both the transmitter and receiver in synchronous modes or by the transmitter in asynchronous modes.                                                                                                                                                                                     |

|             |                 |                                      | Although an external serial clock can be independent of and asynchronous to<br>the DSP system clock, it must exceed the minimum clock cycle time of 6T (that<br>is, the system clock frequency must be at least three times the external ESSI<br>clock frequency). The ESSI needs at least three DSP phases inside each half of<br>the serial clock.                                                       |

| PC3         | Input or Output |                                      | <b>Port C 3</b> —The default configuration following reset is GPIO input PC3. When configured as PC3, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SCK0 through the Port C Control Register.                                                                                                                                       |

| SRD0        | Input           | Ignored Input                        | Serial Receive Data—Receives serial data and transfers the data to the ESSI Receive Shift Register. SRD0 is an input when data is received.                                                                                                                                                                                                                                                                |

| PC4         | Input or Output |                                      | <b>Port C 4</b> —The default configuration following reset is GPIO input PC4. When configured as PC4, signal direction is controlled through the Port C Direction Register. The signal can be configured as an ESSI signal SRD0 through the Port C Control Register.                                                                                                                                       |

| Table 1-12. | Enhanced Synchronous Serial Interface ( | ) |

|-------------|-----------------------------------------|---|

|             |                                         | - |

# 1.10 Serial Communication Interface (SCI)

The SCI provides a full duplex port for serial communication with other DSPs, microprocessors, or peripherals such as modems.

| Signal Name                                                                                                                                                                                                                                                                                                                                                | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD                                                                                                                                                                                                                                                                                                                                                        | Input           | Ignored Input                        | Serial Receive Data—Receives byte-oriented serial data and transfers it to the SCI Receive Shift Register.                                                                                                                                                          |

| PE0                                                                                                                                                                                                                                                                                                                                                        | Input or Output |                                      | <b>Port E 0</b> —The default configuration following reset is GPIO input PE0. When configured as PE0, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal RXD through the Port E Control Register.  |

| TXD                                                                                                                                                                                                                                                                                                                                                        | Output          | Ignored Input                        | Serial Transmit Data—Transmits data from the SCI Transmit Data Register.                                                                                                                                                                                            |

| PE1                                                                                                                                                                                                                                                                                                                                                        | Input or Output |                                      | <b>Port E 1</b> —The default configuration following reset is GPIO input PE1. When configured as PE1, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal TXD through the Port E Control Register.  |

| SCLK                                                                                                                                                                                                                                                                                                                                                       | Input/Output    | Ignored Input                        | <b>Serial Clock</b> —Provides the input or output clock used by the transmitter and/or the receiver.                                                                                                                                                                |

| PE2                                                                                                                                                                                                                                                                                                                                                        | Input or Output |                                      | <b>Port E 2</b> —The default configuration following reset is GPIO input PE2. When configured as PE2, signal direction is controlled through the Port E Direction Register. The signal can be configured as an SCI signal SCLK through the Port E Control Register. |

| <ol> <li>In the Stop state, the signal maintains the last state as follows:         <ul> <li>If the last state is input, the signal is an ignored input.</li> <li>If the last state is output, the signal is tri-stated.</li> </ul> </li> <li>The Wait processing state does not affect the signal state.</li> <li>All inputs are 5 V tolerant.</li> </ol> |                 |                                      |                                                                                                                                                                                                                                                                     |

| Table 1-14. Senai Communication internace | Table 1-14. | Serial Communication | Interface |

|-------------------------------------------|-------------|----------------------|-----------|

|-------------------------------------------|-------------|----------------------|-----------|

# 2.3 Thermal Characteristics

| Characteristic                                                                                                                                                    | Symbol                           | TQFP Value | MAP-BGA <sup>3</sup><br>Value | MAP-BGA <sup>4</sup><br>Value | Unit |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|-------------------------------|-------------------------------|------|--|--|--|

| Junction-to-ambient thermal resistance <sup>1</sup>                                                                                                               | $R_{\theta JA}$ or $\theta_{JA}$ | 56         | 57                            | 28                            | °C/W |  |  |  |

| Junction-to-case thermal resistance <sup>2</sup>                                                                                                                  | $R_{\theta JC}$ or $\theta_{JC}$ | 11         | 15                            | _                             | °C/W |  |  |  |

| Thermal characterization parameter                                                                                                                                | $\Psi_{\rm JT}$                  | 7          | 8                             | _                             | °C/W |  |  |  |

| Notes: 1. Junction-to-ambient thermal resistance is based on measurements on a horizontal single-sided printed circuit board per<br>JEDEC Specification JESD51-3. |                                  |            |                               |                               |      |  |  |  |

Table 2-2. Thermal Characteristics

2. Junction-to-case thermal resistance is based on measurements using a cold plate per SEMI G30-88, with the exception that

the cold plate temperature is used for the case temperature.

3. These are simulated values. See note 1 for test board conditions.

4. These are simulated values. The test board has two 2-ounce signal layers and two 1-ounce solid ground planes internal to the test board.

# 2.4 DC Electrical Characteristics

| Characteristics                                                                                                                                                         | Symbol                                                   | Min                                 | Тур               | Max                                        | Unit           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|-------------------|--------------------------------------------|----------------|

| Supply voltage                                                                                                                                                          | V <sub>CC</sub>                                          | 3.0                                 | 3.3               | 3.6                                        | V              |

| Input high voltage<br>• D[0–23], BG, BB, TA<br>• MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>8</sup> | V <sub>IH</sub><br>V <sub>IHP</sub><br>V <sub>IHX</sub>  | 2.0<br>2.0<br>0.8 × V <sub>CC</sub> |                   | V <sub>CC</sub><br>5.25<br>V <sub>CC</sub> | v<br>v<br>v    |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI08 pins<br>• EXTAL <sup>8</sup>            | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub>  | -0.3<br>-0.3<br>-0.3                |                   | 0.8<br>0.8<br>0.2 × V <sub>CC</sub>        | V<br>V<br>V    |

| Input leakage current                                                                                                                                                   | I <sub>IN</sub>                                          | -10                                 | _                 | 10                                         | μA             |

| High impedance (off-state) input current (@ 2.4 V / 0.4 V)                                                                                                              | I <sub>TSI</sub>                                         | -10                                 | _                 | 10                                         | μA             |

| Output high voltage<br>• TTL $(I_{OH} = -0.4 \text{ mA})^{5,7}$<br>• CMOS $(I_{OH} = -10 \mu \text{A})^5$                                                               | V <sub>OH</sub>                                          | 2.4<br>V <sub>CC</sub> – 0.01       |                   |                                            | V<br>V         |

| Output low voltage<br>• TTL ( $I_{OL} = 1.6$ mA, open-drain pins $I_{OL} = 6.7$ mA) <sup>5,7</sup><br>• CMOS ( $I_{OL} = 10 \mu A$ ) <sup>5</sup>                       | V <sub>OL</sub>                                          |                                     |                   | 0.4<br>0.01                                | V<br>V         |

| Internal supply current <sup>2</sup> : <ul> <li>In Normal mode</li> <li>In Wait mode<sup>3</sup></li> <li>In Stop mode<sup>4</sup></li> </ul>                           | I <sub>CCI</sub><br>I <sub>CCW</sub><br>I <sub>CCS</sub> |                                     | 127<br>7.5<br>100 |                                            | mA<br>mA<br>μA |

| PLL supply current                                                                                                                                                      |                                                          | _                                   | 1                 | 2.5                                        | mA             |

| Input capacitance <sup>5</sup>                                                                                                                                          | C <sub>IN</sub>                                          |                                     |                   | 10                                         | pF             |

Table 2-3.

DC Electrical Characteristics<sup>6</sup>

Table 2-3.

DC Electrical Characteristics<sup>6</sup> (Continued)

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol   | Min     | Тур           | Max                | Unit  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---------------|--------------------|-------|--|--|

| Notes: | 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | D pins. |               |                    |       |  |  |

|        | 2. Section 4.3 provides a formula to compute the estimated current requirements in Normal mode. In order to obtain these results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks (see Appendix A). The power consumption numbers in this specification are 90 percent of the measured results benchmark. This reflects typical DSP applications. Typical internal supply current is measured with V <sub>CC</sub> = 3.3 V at T 100°C. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |         |               |                    |       |  |  |

|        | 3.<br>4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | In order to obtain these results, all inputs must be terminated (that is, not allowed to float).<br>In order to obtain these results, all inputs that are not disconnected at Stop mode must be terminated (that is, not allowed to float).<br>Float). PLL and XTAL signals are disabled during Stop state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |         |               |                    |       |  |  |

|        | 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Periodically sampled and not 100 percent tested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         |               |                    |       |  |  |

|        | 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}; T_{J} = -40^{\circ}\text{C} \text{ to} + 100^{\circ}\text{C}, C_{L} = 50 \text{ pF}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |         |               |                    |       |  |  |

|        | 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | This characteristic does not apply to XTAL and PCAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |         |               |                    |       |  |  |

|        | 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Driving EXTAL to the low V <sub>IHX</sub> or the high V <sub>ILX</sub> value map ower consumption, the minimum V <sub>IHX</sub> should be no low 0.9 × V <sub>CC</sub> and the maximum V <sub>ILX</sub> should be no higher the | ver than |         | nsumption (DC | C current). To min | imize |  |  |

### 2.5 AC Electrical Characteristics

The timing waveforms shown in the AC electrical characteristics section are tested with a  $V_{IL}$  maximum of 0.3 V and a  $V_{IH}$  minimum of 2.4 V for all pins except EXTAL, which is tested using the input levels shown in Note 6 of the previous table. AC timing specifications, which are referenced to a device input signal, are measured in production with respect to the 50 percent point of the respective input signal transition. DSP56303 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.4 V and 2.4 V, respectively.

**Note:** Although the minimum value for the frequency of EXTAL is 0 MHz, the device AC test conditions are 15 MHz and rated speed.

#### 2.5.1 Internal Clocks

| Characteristics                                                                                                                                                  | Symbol         |                                                                                                                                                                                      | Expression <sup>1, 2</sup>       |                                                                                                                                                                                      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Characteristics                                                                                                                                                  | Symbol         | Min                                                                                                                                                                                  | Тур                              | Мах                                                                                                                                                                                  |  |  |

| Internal operation frequency and CLKOUT with PLL enabled                                                                                                         | f              | _                                                                                                                                                                                    | $(Ef \times MF)/$<br>(PDF × DF)  | _                                                                                                                                                                                    |  |  |

| Internal operation frequency and CLKOUT with PLL disabled                                                                                                        | f              |                                                                                                                                                                                      | Ef/2                             | —                                                                                                                                                                                    |  |  |

| <ul> <li>Internal clock and CLKOUT high period</li> <li>With PLL disabled</li> <li>With PLL enabled and MF ≤4</li> <li>With PLL enabled and MF &gt; 4</li> </ul> | Т <sub>Н</sub> | $\begin{array}{c}\\ 0.49 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF}\\ 0.47 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF} \end{array}$ | ет <sub>с</sub><br>—<br>—        | $\begin{array}{c}\\ 0.51 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF}\\ 0.53 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF} \end{array}$ |  |  |

| <ul> <li>Internal clock and CLKOUT low period</li> <li>With PLL disabled</li> <li>With PLL enabled and MF ≤4</li> <li>With PLL enabled and MF &gt; 4</li> </ul>  | TL             | $\begin{array}{c}\\ 0.49 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF}\\ 0.47 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF} \end{array}$ | ET <sub>C</sub><br>—<br>—        | $\begin{array}{c}\\ 0.51 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF}\\ 0.53 \times \text{ET}_{\text{C}} \times\\ \text{PDF} \times \text{DF/MF} \end{array}$ |  |  |

| Internal clock and CLKOUT cycle time with PLL enabled                                                                                                            | т <sub>с</sub> | _                                                                                                                                                                                    | ET <sub>C</sub> × PDF ×<br>DF/MF | —                                                                                                                                                                                    |  |  |

Table 2-4. Internal Clocks, CLKOUT

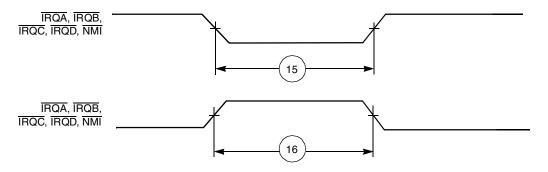

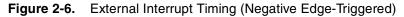

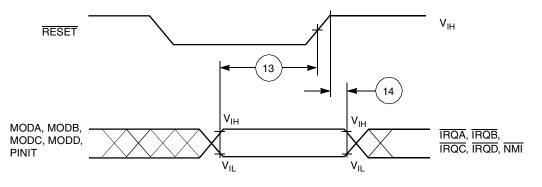

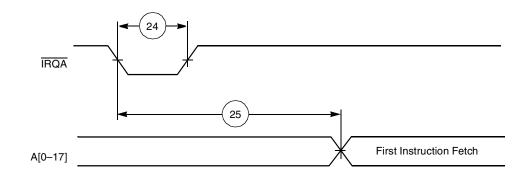

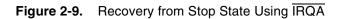

# 2.5.4 Reset, Stop, Mode Select, and Interrupt Timing

| Ne  | Characteristics                                                                                                                                                                                                                                                                                                                                               | Everencian                                                                                                                                                                                                                                      | 100                                           | MHz                                  | l la it                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------|----------------------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                                               | Expression                                                                                                                                                                                                                                      | Min                                           | Max                                  | Unit                             |

| 8   | Delay from RESET assertion to all pins at reset value <sup>3</sup>                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                               |                                               | 26.0                                 | ns                               |

| 9   | <ul> <li>Required RESET duration<sup>4</sup></li> <li>Power on, external clock generator, PLL disabled</li> <li>Power on, external clock generator, PLL enabled</li> <li>Power on, internal oscillator</li> <li>During STOP, XTAL disabled (PCTL Bit 16 = 0)</li> <li>During STOP, XTAL enabled (PCTL Bit 16 = 1)</li> <li>During normal operation</li> </ul> | $\begin{array}{c} 50 \times \text{ET}_{\text{C}} \\ 1000 \times \text{ET}_{\text{C}} \\ 75000 \times \text{ET}_{\text{C}} \\ 75000 \times \text{ET}_{\text{C}} \\ 2.5 \times \text{T}_{\text{C}} \\ 2.5 \times \text{T}_{\text{C}} \end{array}$ | 500.0<br>10.0<br>0.75<br>0.75<br>25.0<br>25.0 |                                      | ns<br>μs<br>ms<br>ms<br>ns<br>ns |

| 10  | <ul> <li>Delay from asynchronous RESET deassertion to first external address output (internal reset deassertion)<sup>5</sup></li> <li>Minimum</li> <li>Maximum</li> </ul>                                                                                                                                                                                     | $3.25 \times T_{C} + 2.0$<br>$20.25 \times T_{C} + 10$                                                                                                                                                                                          | 34.5<br>—                                     | <br>212.5                            | ns<br>ns                         |

| 11  | Synchronous reset set-up time from RESET deassertion to CLKOUT<br>Transition 1<br>• Minimum<br>• Maximum                                                                                                                                                                                                                                                      | т <sub>с</sub>                                                                                                                                                                                                                                  | 5.9<br>—                                      | <br>10.0                             | ns<br>ns                         |

| 12  | Synchronous reset deasserted, delay time from the CLKOUT Transition<br>1 to the first external address output<br>• Minimum<br>• Maximum                                                                                                                                                                                                                       | $3.25 \times T_{C} + 1.0$<br>$20.25 \times T_{C} + 1.0$                                                                                                                                                                                         | 33.5<br>—                                     | <br>203.5                            | ns<br>ns                         |

| 13  | Mode select setup time                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                 | 30.0                                          |                                      | ns                               |

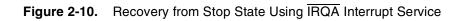

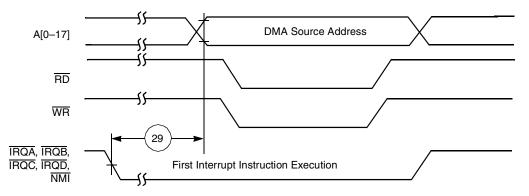

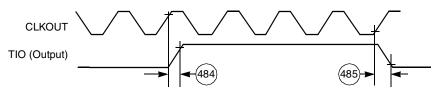

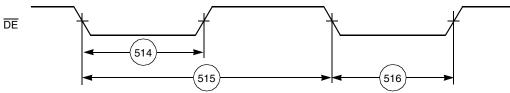

| 14  | Mode select hold time                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                 | 0.0                                           | —                                    | ns                               |