# Microchip Technology - PIC16F1614-E/P Datasheet

# E·XFL

### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1614-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ŋ   | 20-Pin PDIP, SOIC, SSOP | 20-Pin UQFN | A/D  | Reference | Comparator       | Timers                                      | ССР                 | CWG                                | ZCD    | CLC                   | EUSART              | SMT                    | Angular Timer       | MSSP                 | MWG | High Current I/O | Interrupt  | Bull-up | Basic       |

|-----|-------------------------|-------------|------|-----------|------------------|---------------------------------------------|---------------------|------------------------------------|--------|-----------------------|---------------------|------------------------|---------------------|----------------------|-----|------------------|------------|---------|-------------|

| RA0 | 19                      | 16          | AN0  | DAC10UT   | C1IN+            | —                                           | _                   | _                                  | _      | _                     |                     | _                      |                     | _                    |     | —                | IOC        | Y       | ICSPDAT     |

| RA1 | 18                      | 15          | AN1  | VREF+     | C1IN0-<br>C2IN0- | —                                           | —                   | —                                  | —      | —                     | _                   | —                      | —                   | —                    | _   | -                | IOC        | Y       | ICSPCLK     |

| RA2 | 17                      | 14          | AN2  | -         |                  | T0CKI <sup>(1)</sup>                        |                     | CWG1IN <sup>(1)</sup>              | ZCD1IN | Ι                     |                     | —                      | -                   |                      | -   |                  | INT<br>IOC | Y       | —           |

| RA3 | 4                       | 1           | —    | -         |                  | T6IN <sup>(1)</sup>                         | —                   | _                                  | _      | _                     |                     | SMTWIN2 <sup>(1)</sup> | —                   | —                    |     | -                | IOC        | Y       | MCLR<br>VPP |

| RA4 | 3                       | 20          | AN3  | _         | _                | T1G <sup>(1)</sup>                          | _                   | _                                  | _      | _                     | _                   | SMTSIG1(1)             | _                   | _                    | _   | _                | IOC        | Y       | CLKOUT      |

| RA5 | 2                       | 19          | —    | -         |                  | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> | —                   | _                                  | —      | CLCIN3 <sup>(1)</sup> |                     | SMTWIN1 <sup>(1)</sup> | —                   | —                    | _   | —                | IOC        | Y       | CLKIN       |

| RB4 | 13                      | 10          | AN10 | _         | _                | _                                           | _                   | _                                  | _      | _                     | _                   | _                      | _                   | SDI(1)               | _   | _                | IOC        | Y       | _           |

| RB5 | 12                      | 9           | AN11 | _         | _                | _                                           | _                   | _                                  | _      | _                     | RX <sup>(1,3)</sup> | _                      | _                   | _                    |     | -                | IOC        | Y       | _           |

| RB6 | 11                      | 8           | _    | _         | -                | _                                           | _                   | _                                  | —      | —                     | _                   | _                      | _                   | SCK <sup>(1,3)</sup> | _   | _                | IOC        | Y       | _           |

| RB7 | 10                      | 7           | _    | _         |                  | —                                           |                     | _                                  | _      | _                     | CK <sup>(1)</sup>   | _                      |                     | _                    | -   | _                | IOC        | Y       | —           |

| RC0 | 16                      | 13          | AN4  | —         | C2IN+            | T5CKI <sup>(1)</sup>                        | _                   | -                                  | _      | -                     | _                   | -                      | _                   | _                    | —   | _                | IOC        | Y       | —           |

| RC1 | 15                      | 12          | AN5  | —         | C1IN1-<br>C2IN1- | T4IN <sup>(1)</sup>                         |                     | -                                  | -      | CLCIN2 <sup>(2)</sup> | _                   | SMTSIG2 <sup>(1)</sup> | _                   | —                    | _   | -                | IOC        | Y       | —           |

| RC2 | 14                      | 11          | AN6  | _         | C1IN2-<br>C2IN2- | —                                           | -                   | -                                  | -      | -                     | _                   | —                      | -                   | —                    | _   | -                | IOC        | Y       | —           |

| RC3 | 7                       | 4           | AN7  | _         | C1IN3-<br>C2IN3- | T5G <sup>(1)</sup>                          | CCP2 <sup>(1)</sup> | -                                  | _      | CLCIN0 <sup>(1)</sup> | _                   | —                      | ATCC <sup>(1)</sup> | _                    | _   | -                | IOC        | Y       | —           |

| RC4 | 6                       | 3           | _    | _         |                  | T3G <sup>(1)</sup>                          | _                   | _                                  |        | CLCIN1 <sup>(1)</sup> |                     | _                      |                     |                      | _   | HIC4             | IOC        | Y       | —           |

| RC5 | 5                       | 2           | —    | _         | _                | T3CKI <sup>(1)</sup>                        | CCP1 <sup>(1)</sup> | _                                  | _      | _                     | _                   | _                      | ATIN <sup>(1)</sup> | _                    | _   | HIC5             | IOC        | Y       | —           |

| RC6 | 8                       | 5           | AN8  | _         |                  | _                                           | _                   | _                                  | —      | _                     | —                   | _                      | _                   | SS <sup>(1)</sup>    | _   | _                | IOC        | Y       | _           |

| RC7 | 9                       | 6           | AN9  |           |                  | —                                           | _                   | _                                  | _      | _                     |                     | _                      | _                   | _                    | ļ   | _                | IOC        | Y       | —           |

| Vdd | 1                       | 18          | _    | _         |                  | _                                           | _                   | _                                  | _      | _                     | _                   | _                      |                     | _                    |     | _                | _          | _       | _           |

| Vss | 20                      | 17          | _    | _         |                  | —                                           | _                   | _                                  | _      | _                     |                     | _                      | _                   | _                    |     | —                |            | _       | —           |

|     |                         |             |      |           |                  |                                             |                     | vith the PPS ir<br>cted as a digit |        |                       | e PPS out           | tput selection re      | gisters.            |                      |     |                  |            |         | _           |

### TABLE 4: 20-PIN ALLOCATION TABLE (PIC16(L)F1618)

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections. 3:

# PIC16(L)F1614/8

### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section5.3 "Clock Switching"for more information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase Lock Loop, HFPLL that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase Lock Loop, HFPLL. The frequency of the HFINTOSC can be useradjusted via software using the OSCTUNE register (Register 5-3).

- 2. The **MFINTOSC** (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section5.2.2.8 "Internal Oscillator Clock Switch Timing**" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast start-up oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section5.2.2.8 "Internal Oscillator Clock Switch Timing**" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

### 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), and peripherals, are *not* affected by the change in frequency.

## 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See Section5.2.2.8 "Internal Oscillator Clock Switch Timing" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<1:0> = 00, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running.

## 5.2.2.5 FRC

The FRC clock is an uncalibrated, nominal 600 kHz peripheral clock source.

The FRC is automatically turned on by the peripherals requesting the FRC clock.

The FRC clock will continue to run during Sleep.

### 5.2.2.6 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The postscaler outputs of the 16 MHz HFINTOSC, 500 kHz MFINTOSC, and 31 kHz LFINTOSC output connect to a multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

Note: Following any Reset, the IRCF<3:0> bits of the OSCCON register are set to '0111' and the frequency selection is set to 500 kHz. The user can modify the IRCF bits to select a different frequency.

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

# 9.7 Register Definitions: Windowed Watchdog Timer Control

| U-0          | U-0                          | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>                           | R/W <sup>(3)</sup> -q/q | <sup>(2)</sup> R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0    |  |  |  |  |  |

|--------------|------------------------------|------------------------------------------------------------------|-------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------|------------|--|--|--|--|--|

| —            | —                            |                                                                  |                         | WDTPS<4:0>(1)                                         |                                        |                                        | SEN        |  |  |  |  |  |

| bit 7        |                              |                                                                  |                         |                                                       |                                        |                                        | bit (      |  |  |  |  |  |

| Legend:      |                              |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

| R = Reada    | able bit                     | W = Writable I                                                   | bit                     | U = Unimplem                                          | ented bit, read                        | l as '0'                               |            |  |  |  |  |  |

| u = Bit is u | inchanged                    | x = Bit is unkn                                                  | iown                    | -n/n = Value a                                        | t POR and BO                           | R/Value at all ot                      | ner Resets |  |  |  |  |  |

| '1' = Bit is | set                          | '0' = Bit is clea                                                | ared                    | q = Value dep                                         | ends on condit                         | ion                                    |            |  |  |  |  |  |

| bit 7-6      | Unimpleme                    | ented: Read as '                                                 | 0'                      |                                                       |                                        |                                        |            |  |  |  |  |  |

| bit 5-1      | WDTPS<4:                     | WDTPS<4:0>: Watchdog Timer Prescale Select bits <sup>(1)</sup>   |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | Bit Value =                  | Prescale Rate                                                    |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 11111 = F                    | Reserved. Results                                                | s in minimum            | n interval (1:32)                                     |                                        |                                        |            |  |  |  |  |  |

|              | •                            |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | •                            |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 10011 = F                    | Reserved. Results                                                | s in minimum            | n interval (1:32)                                     |                                        |                                        |            |  |  |  |  |  |

|              | 10010 = <b>1</b>             | :8388608 (2 <sup>23</sup> ) (I                                   | Interval 256s           | nominal)                                              |                                        |                                        |            |  |  |  |  |  |

|              | 10001 <b>= 1</b>             | :4194304 (2 <sup>22</sup> ) (I                                   | Interval 128s           | nominal)                                              |                                        |                                        |            |  |  |  |  |  |

|              |                              | :2097152 (2 <sup>21</sup> ) (I                                   |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 01111 = 1                    | :1048576 (2 <sup>20</sup> ) (I                                   | Interval 32s i          | nominal)                                              |                                        |                                        |            |  |  |  |  |  |

|              | 01110 = 1<br>01101 = 1       | :524288 (2 <sup>19</sup> ) (In                                   | iterval 8s noi          | minal)                                                |                                        |                                        |            |  |  |  |  |  |

|              | 01100 = 1                    | :262144 (2 <sup>18</sup> ) (In<br>:131072 (2 <sup>17</sup> ) (In | iterval 4s noi          | minal)                                                |                                        |                                        |            |  |  |  |  |  |

|              |                              | :65536 (Interval 2                                               |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 01010 = <b>1</b>             | :32768 (Interval                                                 | 1s nominal)             |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | :16384 (Interval §                                               |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | :8192 (Interval 2                                                |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | :4096 (Interval 12                                               |                         | ,                                                     |                                        |                                        |            |  |  |  |  |  |

|              |                              | :2048 (Interval 64<br>:1024 (Interval 32                         |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | :512 (Interval 16                                                |                         | ,                                                     |                                        |                                        |            |  |  |  |  |  |

|              |                              | :256 (Interval 8 n                                               |                         | ,<br>,                                                |                                        |                                        |            |  |  |  |  |  |

|              |                              | :128 (Interval 4 n                                               | ,                       |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | 00001 = 1:64 (Interval 2 ms nominal)                             |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              |                              | :32 (Interval 1 ms                                               |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

| bit 0        |                              | are Enable/Disat                                                 | ble for Watch           | idog Timer bit                                        |                                        |                                        |            |  |  |  |  |  |

|              | If WDTE<1                    |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | This bit is ig<br>If WDTE<1: |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 1 = WDT is                   |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | 0 = WDT is                   |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | If WDTE<1:                   |                                                                  |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

|              | This bit is ig               | nored.                                                           |                         |                                                       |                                        |                                        |            |  |  |  |  |  |

| Note 1:      | Times are appr               | oximate. WDT tin                                                 | ne is based             | on 31 kHz LFINTO                                      | DSC.                                   |                                        |            |  |  |  |  |  |

# REGISTER 9-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

- Note 1: Times are approximate. WDT time is based on 31 kHz LFINTOSC.

- 2: When WDTCPS <4:0> in CONFIG3 = 11111, the Reset value of WDTPS<4:0> is 01011. Otherwise, the Reset value of WDTPS<4:0> is equal to WDTCPS<4:0> in CONFIG3.

- 3: When WDTCPS <4:0> in CONFIG3  $\neq$  11111, these bits are read-only.

| TABLE 12-2: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|-------------|--------------------------------------------|

|             |                                            |

| Name       | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|------------|-------|--------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELA     | _     |        | —       | ANSA4   |         | ANSA2   | ANSA1   | ANSA0   | 152                 |

| INLVLA     | —     | _      | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 154                 |

| LATA       | _     | _      | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   | 152                 |

| ODCONA     | —     | _      | ODA5    | ODA4    | _       | ODA2    | ODA1    | ODA0    | 153                 |

| OPTION_REG | WPUEN | INTEDG | TMR0CS  | TMR0SE  | PSA     | PS<2:0> |         |         | 222                 |

| PORTA      | _     | _      | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 151                 |

| SLRCONA    | —     | _      | SLRA5   | SLRA4   | _       | SLRA2   | SLRA1   | SLRA0   | 154                 |

| TRISA      | _     | _      | TRISA5  | TRISA4  | (1)     | TRISA2  | TRISA1  | TRISA0  | 151                 |

| WPUA       | _     | _      | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 153                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.**Note 1:**Unimplemented, read as '1'.

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0 | Register<br>on Page |  |

|---------|------|---------|---------|----------|----------|----------|----------|----------|---------|---------------------|--|

|         | 13:8 |         |         | _        | _        | CLKOUTEN | BOREI    | N<1:0> — |         | 07                  |  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    |          | _        | — FOSC   |          | <1:0>   | 67                  |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

### 12.3.7 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3       | Bit 2    | Bit 1 | Bit 0       | Register<br>on page |  |  |  |  |  |  |  |

|-----------------------|-------|-------|-------|-------------|-------------|----------|-------|-------------|---------------------|--|--|--|--|--|--|--|

| RC1PPS                | —     | -     | _     | RC1PPS<4:0> |             |          |       | RC1PPS<4:0> |                     |  |  |  |  |  |  |  |

| RC2PPS                | —     | _     | _     |             | RC2PPS<4:0> |          |       |             |                     |  |  |  |  |  |  |  |

| RC3PPS                | —     | -     | _     |             | RC3PPS<4:0> |          |       |             |                     |  |  |  |  |  |  |  |

| RC4PPS                | —     | -     | _     |             |             | RC4PPS<4 | :0>   |             | 172                 |  |  |  |  |  |  |  |

| RC5PPS                | —     | _     | _     |             | RC5PPS<4:0> |          |       |             |                     |  |  |  |  |  |  |  |

| RC6PPS <sup>(1)</sup> | —     | _     | _     |             | 172         |          |       |             |                     |  |  |  |  |  |  |  |

| RC7PPS <sup>(1)</sup> | —     | _     |       |             |             | RC7PPS<4 | :0>   |             | 172                 |  |  |  |  |  |  |  |

Note 1: PIC16(L)F1618 only.

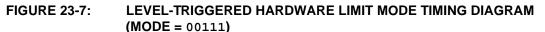

### 23.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 23-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

|                              | Rev. 10-000368<br>500/2014                                                                                                                                                                                                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                         | 0600111                                                                                                                                                                                                                                                                         |

| TMRx_clk                     |                                                                                                                                                                                                                                                                                 |

| PRx                          | 5                                                                                                                                                                                                                                                                               |

| Instruction <sup>(1)</sup> - | BSF BSF                                                                                                                                                                                                                                                                         |

| ON                           |                                                                                                                                                                                                                                                                                 |

| TMRx_ers                     |                                                                                                                                                                                                                                                                                 |

| TMRx                         | 0  1  2  0  1  2  3  4  5  0  1  2  3  4  5  0  1  2  3  4  5  0  1  2  3  4  5  0  1  1  2  3  4  5  0  1  1  2  3  4  5  0  1  1  2  3  4  5  0  1  1  1  2  3  4  5  0  1  1  1  2  3  4  5  0  1  1  1  2  1  3  4  5  0  1  1  1  2  3  4  5  0  1  1  1  1  1  1  1  1  1 |

| TMRx_postscaled              |                                                                                                                                                                                                                                                                                 |

| PWM Duty                     | 3                                                                                                                                                                                                                                                                               |

| Cycle                        | 3                                                                                                                                                                                                                                                                               |

| PWM Output                   |                                                                                                                                                                                                                                                                                 |

|                              | : BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the CPU to<br>set or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input.                                                                                        |

### 24.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 24-1 shows the block diagram of the MSSP module when operating in SPI mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 24-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 24-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on

its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After eight bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

# 24.4 I<sup>2</sup>C MODE OPERATION

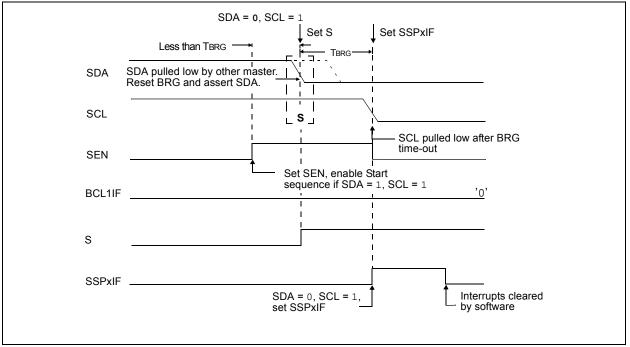

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

### 24.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

### 24.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

### 24.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

- Note 1: Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

- 2: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

### 24.4.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT bit of the SSPxCON3 register. Hold time is the time SDA is held valid after the falling edge of SCL. Setting the SDAHT bit selects a longer 300 ns minimum hold time and may help on buses with large capacitance.

## TABLE 24-2: I<sup>2</sup>C BUS TERMS

| TABLE 24-2: I <sup>2</sup> C BUS TERMS |                                                                                                                                                                                                  |  |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| TERM                                   | Description                                                                                                                                                                                      |  |  |  |  |  |  |

| Transmitter                            | The device which shifts data out onto the bus.                                                                                                                                                   |  |  |  |  |  |  |

| Receiver                               | The device which shifts data in from the bus.                                                                                                                                                    |  |  |  |  |  |  |

| Master                                 | The device that initiates a transfer, generates clock signals and termi-<br>nates a transfer.                                                                                                    |  |  |  |  |  |  |

| Slave                                  | The device addressed by the master.                                                                                                                                                              |  |  |  |  |  |  |

| Multi-master                           | A bus with more than one device that can initiate data transfers.                                                                                                                                |  |  |  |  |  |  |

| Arbitration                            | Procedure to ensure that only one master at a time controls the bus. Winning arbitration ensures that the message is not corrupted.                                                              |  |  |  |  |  |  |

| Synchronization                        | Procedure to synchronize the clocks of two or more devices on the bus.                                                                                                                           |  |  |  |  |  |  |

| Idle                                   | No master is controlling the bus,<br>and both SDA and SCL lines are<br>high.                                                                                                                     |  |  |  |  |  |  |

| Active                                 | Any time one or more master devices are controlling the bus.                                                                                                                                     |  |  |  |  |  |  |

| Addressed<br>Slave                     | Slave device that has received a matching address and is actively being clocked by a master.                                                                                                     |  |  |  |  |  |  |

| Matching<br>Address                    | Address byte that is clocked into a slave that matches the value stored in SSPxADD.                                                                                                              |  |  |  |  |  |  |

| Write Request                          | Slave receives a matching<br>address with R/W bit clear, and is<br>ready to clock in data.                                                                                                       |  |  |  |  |  |  |

| Read Request                           | Master sends an address byte with the $R/\overline{W}$ bit set, indicating that it wishes to clock data out of the Slave. This data is the next and all following bytes until a Restart or Stop. |  |  |  |  |  |  |

| Clock Stretching                       | When a device on the bus holds SCL low to stall communication.                                                                                                                                   |  |  |  |  |  |  |

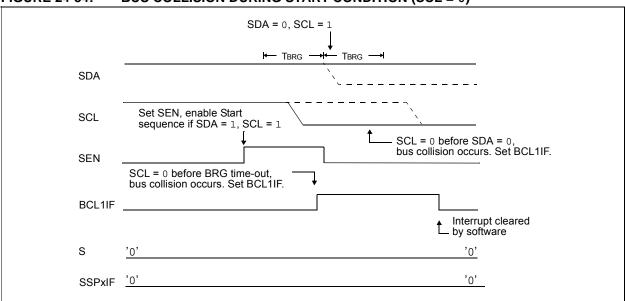

| Bus Collision                          | Any time the SDA line is sampled<br>low by the module while it is out-<br>putting and expected high state.                                                                                       |  |  |  |  |  |  |

© 2014-2016 Microchip Technology Inc.

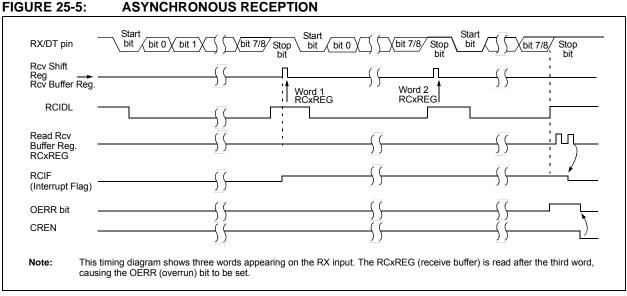

### 25.1.2.8 Asynchronous Reception Set-up

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- If 9-bit reception is desired, set the RX9 bit. 5.

- Enable reception by setting the CREN bit. 6.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags 8. and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- Enable the serial port by setting the SPEN bit. 3. The SYNC bit must be clear for asynchronous operation.

- 4 If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN 6. bit.

- Enable reception by setting the CREN bit. 7.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags. 9. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

| R/W-0/0          | R/W-0/0                                                                                                                                            | R/W-0/0                                          | R/W-0/0                                                           | R/W-0/0         | R-0/0            | R-0/0            | R-0/0       |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------|-----------------|------------------|------------------|-------------|--|--|--|--|--|

| SPEN             | RX9                                                                                                                                                | SREN                                             | CREN                                                              | ADDEN           | FERR             | OERR             | RX9D        |  |  |  |  |  |

| bit 7            | •                                                                                                                                                  |                                                  |                                                                   |                 |                  | •                | bit (       |  |  |  |  |  |

|                  |                                                                                                                                                    |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| Legend:          |                                                                                                                                                    |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| R = Readable     |                                                                                                                                                    | W = Writable                                     |                                                                   |                 | mented bit, read |                  |             |  |  |  |  |  |

| u = Bit is unch  | 0                                                                                                                                                  |                                                  | c = Bit is unknown -n/n = Value at POR and BOR/Value at all other |                 |                  |                  |             |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                    | '0' = Bit is cle                                 | ared                                                              |                 |                  |                  |             |  |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                                                                        | l Port Enable b                                  | it                                                                |                 |                  |                  |             |  |  |  |  |  |

| Sit 7            | 1 = Serial port enabled                                                                                                                            |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | 0 = Serial port disabled (held in Reset)                                                                                                           |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                                                                                                                                | eceive Enable                                    | bit                                                               |                 |                  |                  |             |  |  |  |  |  |

|                  | 1 = Selects 9-bit reception                                                                                                                        |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | 0 = Selects                                                                                                                                        | 8-bit reception                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 5            | -                                                                                                                                                  | e Receive Ena                                    | ole bit                                                           |                 |                  |                  |             |  |  |  |  |  |

|                  | <u>Asynchronous mode</u> :<br>Don't care                                                                                                           |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                    | s mode – Maste                                   | \ <b>r</b> .                                                      |                 |                  |                  |             |  |  |  |  |  |

|                  | -                                                                                                                                                  | single receive                                   | <u>.</u> .                                                        |                 |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                    | single receive                                   |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | This bit is cle                                                                                                                                    | This bit is cleared after reception is complete. |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | Synchronous mode – Slave                                                                                                                           |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | Don't care                                                                                                                                         |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 4            | CREN: Continuous Receive Enable bit                                                                                                                |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | Asynchronous mode:                                                                                                                                 |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | 1 = Enables receiver<br>0 = Disables receiver                                                                                                      |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | 0 = Disables receiver<br>Synchronous mode:                                                                                                         |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 3            |                                                                                                                                                    |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | ADDEN: Address Detect Enable bit<br>Asynchronous mode 9-bit (RX9 = 1):                                                                             |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | -                                                                                                                                                  | -                                                | -                                                                 | terrupt and loa | d the receive bu | uffer when RSF   | R<8> is set |  |  |  |  |  |

|                  |                                                                                                                                                    |                                                  |                                                                   | are received a  | nd ninth bit can | be used as pa    | rity bit    |  |  |  |  |  |

|                  |                                                                                                                                                    | <u>is mode 8-bit (F</u>                          | RX9 = <u>0)</u> :                                                 |                 |                  |                  |             |  |  |  |  |  |

|                  | Don't care                                                                                                                                         |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 2            | FERR: Fram                                                                                                                                         | •                                                |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | 1 = Framing<br>0 = No frami                                                                                                                        |                                                  | ipdated by rea                                                    | ading RCxREG    | register and re  | ceive next valio | l byte)     |  |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                         | run Error bit                                    |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  | <ul> <li>1 = Overrun error (can be cleared by clearing bit CREN)</li> <li>0 = No overrun error</li> </ul>                                          |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

| bit 0            | 0 = No overrun error<br>RX9D: Ninth bit of Received Data                                                                                           |                                                  |                                                                   |                 |                  |                  |             |  |  |  |  |  |

|                  |                                                                                                                                                    | DIL UI RECEIVEL                                  | IDala                                                             |                 |                  |                  |             |  |  |  |  |  |

### REGISTER 25-2: RC1STA: RECEIVE STATUS AND CONTROL REGISTER

# TABLE 25-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4      | Bit 3          | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|------------|----------------|------------|--------|--------|---------------------|

| ANSELA                | —                     | _                     |        | ANSA4      | —              | ANSA2      | ANSA1  | ANSA0  | 152                 |

| ANSELB <sup>(1)</sup> | _                     | _                     | ANSB5  | ANSB4      | _              | _          | _      | _      | 159                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | _      |            | ANSC3          | ANSC2      | ANSC1  | ANSC0  | 166                 |

| BAUD1CON              | ABDOVF                | RCIDL                 |        | SCKP       | BRG16          | _          | WUE    | ABDEN  | 323                 |

| INTCON                | GIE                   | PEIE                  | TMR0IE | INTE       | IOCIE          | TMR0IF     | INTF   | IOCIF  | 97                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE   | TXIE       | SSP1IE         | CCP1IE     | TMR2IE | TMR1IE | 98                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF   | TXIF       | SSP1IF         | CCP1IF     | TMR2IF | TMR1IF | 103                 |

| RC1STA                | SPEN                  | RX9                   | SREN   | CREN       | ADDEN          | FERR       | OERR   | RX9D   | 322                 |

| RxyPPS                | —                     | _                     | _      |            | F              | RxyPPS<4:0 | >      |        | 172                 |

| SP1BRGL               |                       |                       |        | BRG<       | :7:0>          |            |        |        | 324                 |

| SP1BRGH               |                       |                       |        | BRG<       | 15:8>          |            |        |        | 324                 |

| TRISA                 | —                     | _                     | TRISA5 | TRISA4     | (2)            | TRISA2     | TRISA1 | TRISA0 | 151                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4     | —              |            | —      | —      | 158                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4     | TRISC3         | TRISC2     | TRISC1 | TRISC0 | 165                 |

| TX1REG                |                       |                       | EUS    | ART Transm | nit Data Regis | ter        |        |        | 313*                |

| TX1STA                | CSRC                  | TX9                   | TXEN   | SYNC       | SENDB          | BRGH       | TRMT   | TX9D   | 321                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master transmission. \* Page provides register information.

Note 1: PIC16(L)F1618 only.

**2:** Unimplemented, read as '1'.

| TADLE 20-1. EXAMIFLE FWW FREQUENCIES AND RESOLUTIONS (FUSC = 20 MITZ) | TABLE 26-1: | <b>EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (I</b> | Fosc = 20 MHz) |

|-----------------------------------------------------------------------|-------------|---------------------------------------------------|----------------|

|-----------------------------------------------------------------------|-------------|---------------------------------------------------|----------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6         |

### TABLE 26-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 26.4.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section5.0 "Oscillator Module"** for additional details.

### 26.4.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 26.4.7 PWM OUTPUT

The output of the CCP in PWM mode is the PWM signal generated by the module and described above. This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an external Reset signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module. In addition, the CCPx pin output can be mapped to output pins through the use of PPS (see Section13.2 "PPS Outputs").

# PIC16(L)F1614/8

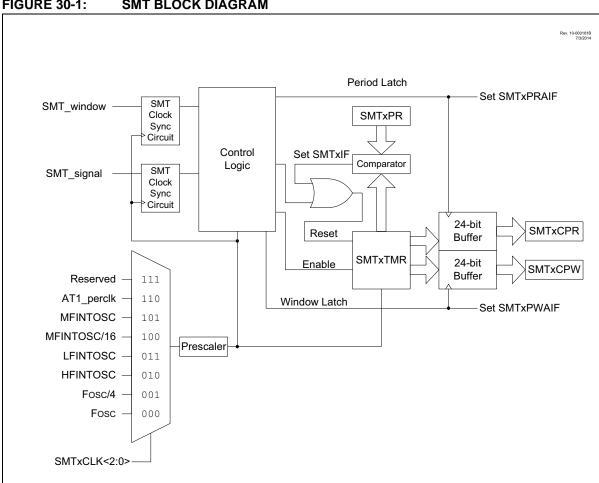

FIGURE 30-1: SMT BLOCK DIAGRAM

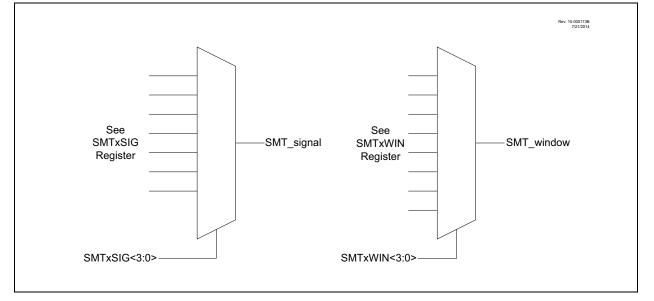

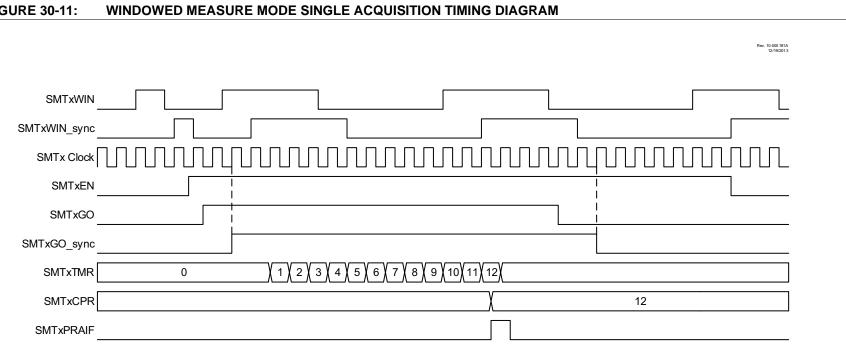

# FIGURE 30-11:

### REGISTER 32-6: PIDxK1H: PID K1 HIGH REGISTER

| R/W-0/0           | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0                        | R/W-0/0            | R/W-0/0             | R/W-0/0 |  |

|-------------------|---------|---------------------|---------|--------------------------------|--------------------|---------------------|---------|--|

|                   |         |                     | K1<     | 15:8>                          |                    |                     |         |  |

| bit 7             |         |                     |         |                                |                    |                     | bit 0   |  |

|                   |         |                     |         |                                |                    |                     |         |  |

| Legend:           |         |                     |         |                                |                    |                     |         |  |

| R = Readable bi   | t       | W = Writable bit    | :       | U = Unimpleme                  | ented bit, read as | ʻ0'                 |         |  |

| u = Bit is unchan | nged    | x = Bit is unknow   | wn      | -n/n = Value at                | POR and BOR/V      | alue at all other I | Resets  |  |

| '1' = Bit is set  |         | '0' = Bit is cleare | ed      | q = Value depends on condition |                    |                     |         |  |

bit 7-0

K1<15:8>: K1 upper eight bits. K1 is the 16-bit user-controlled coefficient calculated from Kp + Ki + Kd

### REGISTER 32-7: PIDxK1L: PID K1 LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | K1<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |