#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

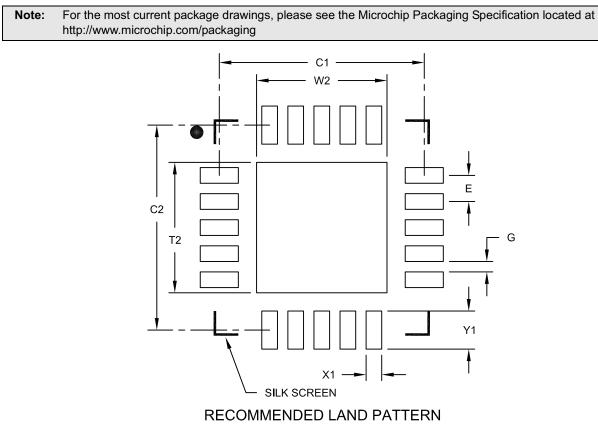

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1614t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PIN ALLOCATION TABLES**

## TABLE 3: 14/16-PIN ALLOCATION TABLE (PIC16(L)F1614)

| I/O                | 14-Pin PDIP, SOIC, TSSOP | 16-Pin UQFN      | A/D | Reference | Comparator       | Timers                                      | e cc P              | CWG                   | ZCD     | CLC                   | EUSART              | SMT                    | Angular Timer                               | dssm                 | MMd     | High Current I/O | Interrupt  | Pull-up    | Basic    |

|--------------------|--------------------------|------------------|-----|-----------|------------------|---------------------------------------------|---------------------|-----------------------|---------|-----------------------|---------------------|------------------------|---------------------------------------------|----------------------|---------|------------------|------------|------------|----------|

| RA0                | 13                       | 12               | AN0 | DAC1OUT1  | C1IN+            | —                                           | —                   | —                     | —       | —                     | —                   | —                      | —                                           | —                    | —       | —                | IOC        | Y          | ICSPDAT  |

| RA1                | 12                       | 11               | AN1 | VREF+     | C1IN0-<br>C2IN0- | -                                           | —                   | —                     | —       | —                     | —                   | —                      | —                                           | —                    | —       | —                | IOC        | Y          | ICSPCLK  |

| RA2                | 11                       | 10               | AN2 | —         | -                | T0CKI <sup>(1)</sup>                        | _                   | CWG1IN <sup>(1)</sup> | ZCD1IN  | —                     | —                   | —                      | —                                           | _                    | _       | _                | INT<br>IOC | Y          | —        |

| RA3                | 4                        | 3                | -   | -         | —                | T6IN <sup>(1)</sup>                         | —                   | —                     | —       | —                     |                     | SMTWIN2 <sup>(1)</sup> | —                                           | —                    | —       |                  | IOC        | Y          | MCLR/VPP |

| RA4                | 3                        | 2                | AN3 | —         | —                | T1G <sup>(1)</sup>                          | _                   | _                     | _       | _                     |                     | SMTSIG1 <sup>(1)</sup> | _                                           | _                    | _       | _                | IOC        | Y          | CLKOUT   |

| RA5                | 2                        | 1                | -   | _         | -                | T1CKI <sup>(1)</sup><br>T2IN <sup>(1)</sup> | -                   | -                     | -       | —                     | —                   | SMTWIN1 <sup>(1)</sup> | —                                           | —                    | —       | -                | IOC        | Y          | CLKIN    |

| RC0                | 10                       | 9                | AN4 | —         | C2IN+            | T5CKI <sup>(1)</sup>                        | _                   | _                     | —       | _                     |                     |                        | _                                           | SCK <sup>(1,3)</sup> | _       | _                | IOC        | Y          | _        |

| RC1                | 9                        | 8                | AN5 | —         | C1IN1-<br>C2IN1- | T4IN <sup>(1)</sup>                         | -                   | -                     | -       | —                     | —                   | SMTSIG2 <sup>(1)</sup> | —                                           | SDI(1)               | —       | -                | IOC        | Y          | -        |

| RC2                | 8                        | 7                | AN6 | —         | C1IN2-<br>C2IN2- | —                                           | —                   | —                     | —       | —                     | —                   | —                      | —                                           | —                    | _       | —                | IOC        | Y          | —        |

| RC3                | 7                        | 6                | AN7 | —         | C1IN3-<br>C2IN3- | T5G <sup>(1)</sup>                          | CCP2 <sup>(1)</sup> | —                     | —       | CLCIN0 <sup>(1)</sup> |                     | —                      | ATCC1 <sup>(1)</sup>                        | <u>SS</u> (1)        | _       | —                | IOC        | Y          | -        |

| RC4                | 6                        | 5                | -   | —         | —                | T3G <sup>(1)</sup>                          | —                   | _                     | —       | CLCIN1 <sup>(1)</sup> | CK <sup>(1)</sup>   | _                      | ATCC2 <sup>(1)</sup>                        | —                    | _       | HIC4             | IOC        | Y          | _        |

| RC5                | 5                        | 4                | -   | -         | -                | T3CKI <sup>(1)</sup>                        | CCP1 <sup>(1)</sup> | -                     | —       | —                     | RX <sup>(1,3)</sup> | —                      | ATIN <sup>(1)</sup><br>ATCC3 <sup>(1)</sup> | —                    | —       | HIC5             | IOC        | Y          | -        |

| VDD                | 1                        | 16               | _   | —         | —                | _                                           | —                   | _                     | —       | _                     | —                   | —                      | _                                           | _                    | _       | —                | —          | —          | Vdd      |

| Vss                | 14                       | 13               | -   | _         | _                | _                                           |                     | _                     | _       | _                     | _                   | _                      | _                                           | _                    | _       | _                | _          | _          | Vss      |

|                    | _                        | [ - ]            | _   | _         | C1OUT            |                                             | CCP1                | CWG1A                 | ZCD10UT | CLC1OUT               | DT <sup>(3)</sup>   | _                      | _                                           | SDO                  | PWM3OUT | _                | —          | —          | _        |

| OUT <sup>(2)</sup> |                          | $\overline{ - }$ | —   | —         | C2OUT            | _                                           | CCP2                | CWG1B                 | _       | CLC2OUT               | СК                  | _                      | _                                           | SCK <sup>(3)</sup>   | PWM4OUT | —                | _          | —          | _        |

|                    | _                        | _                | —   | _         | —                | _                                           | _                   | CWG1C                 | _       | _                     | ТХ                  | _                      | _                                           | _                    | _       | —                | —          | —          | _        |

|                    | I                        | <u> </u>         | -   | _         | —                | —                                           | —                   | CWG1D                 | _       | _                     | !                   | _                      | —                                           | _                    |         |                  |            | $\Box = '$ | —        |

**Note** 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

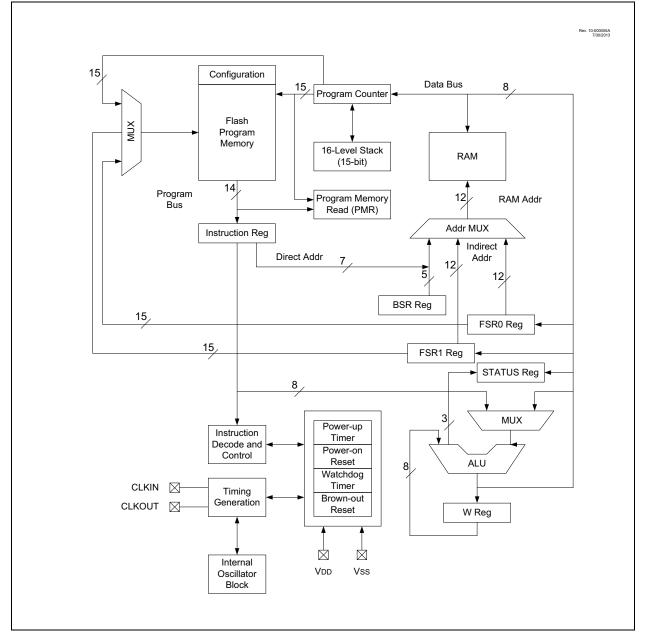

## 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- · 16-level Stack with Overflow and Underflow

- · File Select Registers

- Instruction Set

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

## REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 34.0 "Instruction Set Summary"**).

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

| U-0                                     | U-0 | U-0          | R-1/q | R-1/q                                                 | R/W-0/u | R/W-0/u           | R/W-0/u          |  |  |  |

|-----------------------------------------|-----|--------------|-------|-------------------------------------------------------|---------|-------------------|------------------|--|--|--|

| _                                       | _   | —            | TO    | PD                                                    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |

| bit 7                                   |     | ·            |       | ÷                                                     |         | •                 | bit 0            |  |  |  |

|                                         |     |              |       |                                                       |         |                   |                  |  |  |  |

| Legend:                                 |     |              |       |                                                       |         |                   |                  |  |  |  |

| R = Readable b                          | bit | W = Writable | bit   | U = Unimplemented bit, read as '0'                    |         |                   |                  |  |  |  |

| u = Bit is unchanged x = Bit is unknown |     |              |       | -n/n = Value at POR and BOR/Value at all other Resets |         |                   |                  |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |     |              |       | q = Value depends on condition                        |         |                   |                  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1. | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

## TABLE 3-2: PIC16(L)F1614 MEMORY MAP, BANK 0-7

|      | BANK 0                        |              | BANK 1                        |              | BANK 2                        |              | BANK 3                        |              | BANK 4                        |              | BANK 5                        |       | BANK 6                        |        | BANK 7                        |

|------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|-------|-------------------------------|--------|-------------------------------|

| 000h | Core Registers<br>(Table 3-1) | 080h         | Core Registers<br>(Table 3-1) | 100h         | Core Registers<br>(Table 3-1) | 180h         | Core Registers<br>(Table 3-1) | 200h         | Core Registers<br>(Table 3-1) | 280h         | Core Registers<br>(Table 3-1) | 300h  | Core Registers<br>(Table 3-1) | 380h   | Core Registers<br>(Table 3-1) |

| 00Bh |                               | 08Bh         |                               | 10Bh         |                               | 18Bh         |                               | 20Bh         |                               | 28Bh         |                               | 30Bh  |                               | 38Bh   |                               |

| 00Ch | PORTA                         | 08Ch         | TRISA                         | 10Ch         | LATA                          | 18Ch         | ANSELA                        | 20Ch         | WPUA                          | 28Ch         | ODCONA                        | 30Ch  | SLRCONA                       | 38Ch   | INLVLA                        |

| 00Dh |                               | 08Dh         |                               | 10Dh         |                               | 18Dh         |                               | 20Dh         |                               | 28Dh         | _                             | 30Dh  |                               | 38Dh   |                               |

| 00Eh | PORTC                         | 08Eh         | TRISC                         | 10Eh         | LATC                          | 18Eh         | ANSELC                        | 20Eh         | WPUC                          | 28Eh         | ODCONC                        | 30Eh  | SLRCONC                       | 38Eh   | INLVLC                        |

| 00Fh |                               | 08Fh         |                               | 10Fh         | _                             | 18Fh         | _                             | 20Fh         | —                             | 28Fh         | _                             | 30Fh  | —                             | 38Fh   | —                             |

| 010h | PIR1                          | 090h         | PIE1                          | 110h         |                               | 190h         |                               | 210h         | —                             | 290h         |                               | 310h  | _                             | 390h   | _                             |

| 011h | PIR2                          | 091h         | PIE2                          | 111h         | CM1CON0                       | 191h         | PMADRL                        | 211h         | SSP1BUF                       | 291h         | CCP1RL                        | 311h  | —                             | 391h   | IOCAP                         |

| 012h | PIR3                          | 092h         | PIE3                          | 112h         | CM1CON1                       | 192h         | PMADRH                        | 212h         | SSP1ADD                       | 292h         | CCP1RH                        | 312h  | —                             | 392h   | IOCAN                         |

| 013h | PIR4                          | 093h         | PIE4                          | 113h         | CM2CON0                       | 193h         | PMDATL                        | 213h         | SSP1MSK                       | 293h         | CCP1CON                       | 313h  | —                             | 393h   | IOCAF                         |

| 014h | PIR5                          | 094h         | PIE5                          | 114h         | CM2CON1                       | 194h         | PMDATH                        | 214h         | SSP1STAT                      | 294h         | CCP1CAP                       | 314h  | —                             | 394h   | _                             |

| 015h | TMR0                          | 095h         | OPTION_REG                    | 115h         | CMOUT                         | 195h         | PMCON1                        | 215h         | SSP1CON                       | 295h         | _                             | 315h  | —                             | 395h   |                               |

| 016h | TMR1L                         | 096h         | PCON                          | 116h         | BORCON                        | 196h         | PMCON2                        | 216h         | SSP1CON2                      | 296h         | —                             | 316h  | _                             | 396h   | —                             |

| 017h | TMR1H                         | 097h         | —                             | 117h         | FVRCON                        | 197h         | VREGCON                       | 217h         | SSP1CON3                      | 297h         | _                             | 317h  | —                             | 397h   | IOCCP                         |

| 018h | T1CON                         | 098h         | OSCTUNE                       | 118h         | DAC1CON0                      | 198h         | —                             | 218h         | —                             | 298h         | CCP2RL                        | 318h  | —                             | 398h   | IOCCN                         |

| 019h | T1GCON                        | 099h         | OSCCON                        | 119h         | DAC1CON1                      | 199h         | RC1REG                        | 219h         | —                             | 299h         | CCP2RH                        | 319h  | —                             | 399h   | IOCCF                         |

| 01Ah | TMR2                          | 09Ah         | OSCSTAT                       | 11Ah         | —                             | 19Ah         | TX1REG                        | 21Ah         | —                             | 29Ah         | CCP2CON                       | 31Ah  | —                             | 39Ah   | —                             |

| 01Bh | PR2                           | 09Bh         | ADRESL                        | 11Bh         | —                             | 19Bh         | SP1BRGL                       | 21Bh         | —                             | 29Bh         | CCP2CAP                       | 31Bh  | _                             | 39Bh   | _                             |

| 01Ch | T2CON                         | 09Ch         | ADRESH                        | 11Ch         | ZCD1CON                       | 19Ch         | SP1BRGH                       | 21Ch         | —                             | 29Ch         | —                             | 31Ch  | _                             | 39Ch   |                               |

| 01Dh | T2HLT                         | 09Dh         | ADCON0                        | 11Dh         | _                             | 19Dh         | RC1STA                        | 21Dh         | —                             | 29Dh         | _                             | 31Dh  | _                             | 39Dh   | _                             |

| 01Eh | T2CLKCON                      | 09Eh         | ADCON1                        | 11Eh         | _                             | 19Eh         | TX1STA                        | 21Eh         |                               | 29Eh         | CCPTMRS                       | 31Eh  | _                             | 39Eh   |                               |

| 01Fh | T2RST                         | 09Fh         | ADCON2                        | 11Fh         |                               | 19Fh         | BAUD1CON                      | 21Fh         | _                             | 29Fh         | _                             | 31Fh  | _                             | 39Fh   |                               |

| 020h |                               | 0A0h         |                               | 120h         |                               | 1A0h         |                               | 220h         |                               | 2A0h         |                               | 320h  | General Purpose<br>Register   | 3A0h   |                               |

|      |                               |              | General                       | 32Fh  | 16 Bytes                      |        |                               |

|      |                               |              | Purpose                       | 330h  |                               |        | Unimplemented                 |

|      | General                       |              | Register<br>80 Bytes          | 00011 | Unimplemented                 |        | Read as '0'                   |

|      | Purpose                       |              | oo bytes                      |       | Read as '0'                   |        |                               |

|      | Register<br>96 Bytes          | 0EFh         |                               |              |                               |              |                               | 005          |                               | 0            |                               | 36Fh  |                               | 3EFh   |                               |

|      | 00 Dy(00                      | 0EFn<br>0F0h |                               | 16Fh<br>170h |                               | 1EFh<br>1F0h |                               | 26Fh<br>270h |                               | 2EFh<br>2F0h |                               |       |                               | 3F0h   |                               |

|      |                               | 01.011       | Common RAM                    | 17011        | Common RAM                    | 11.011       | Common RAM                    | 21011        | Common RAM                    | 21.011       | Common RAM                    | 370h  | A                             | 51 011 | Common RAM                    |

|      |                               |              | (Accesses                     |       | Accesses<br>70h – 7Fh         |        | (Accesses                     |

| 0755 |                               | OFER         | 70h – 7Fh)                    | 175h         | 70h – 7Fh)                    | 1556         | 70h – 7Fh)                    | 27Eh         | 70h – 7Fh)                    | 2FFh         | 70h – 7Fh)                    | 27Eb  | / /                           | 255h   | 70h – 7Fh)                    |

| 07Fh |                               | 0FFh         |                               | 17Fh         |                               | 1FFh         |                               | 27Fh         |                               | ∠⊢⊢n         |                               | 37Fh  |                               | 3FFh   |                               |

**Legend:** = Unimplemented data memory locations, read as '0'.

## 4.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 4.7 Register Definitions: Device ID

## **REGISTER 4-4: DEVID: DEVICE ID REGISTER**

|   | R      | R       | R               | R      | R                                                                      | R                          |  |  |  |

|---|--------|---------|-----------------|--------|------------------------------------------------------------------------|----------------------------|--|--|--|

|   |        |         | DEV<            | :13:8> |                                                                        |                            |  |  |  |

|   | bit 13 | 3 bit 8 |                 |        |                                                                        |                            |  |  |  |

|   |        |         |                 |        |                                                                        |                            |  |  |  |

| R | R      | R       | R               | R      | R                                                                      | R                          |  |  |  |

|   |        | DEV     | <7:0>           |        |                                                                        |                            |  |  |  |

|   |        |         |                 |        |                                                                        | bit 0                      |  |  |  |

|   | R      |         | bit 13<br>R R R | DEV<   | DEV<13:8>           bit 13           R         R           R         R | DEV<13:8>           bit 13 |  |  |  |

## Legend:

R = Readable bit

'1' = Bit is set

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values               |  |  |  |  |  |  |

|-------------|----------------------------------|--|--|--|--|--|--|

| PIC16F1614  | 11 0000 0111 1000 <b>(3078h)</b> |  |  |  |  |  |  |

| PIC16LF1614 | 11 0000 0111 1010 <b>(307Ah)</b> |  |  |  |  |  |  |

| PIC16F1618  | 11 0000 0111 1001 <b>(3079h)</b> |  |  |  |  |  |  |

| PIC16LF1618 | 11 0000 0111 1011 <b>(307Bh)</b> |  |  |  |  |  |  |

'0' = Bit is cleared

### REGISTER 4-5: REVID: REVISION ID REGISTER

|       |   | R      | R   | R     | R      | R | R     |

|-------|---|--------|-----|-------|--------|---|-------|

|       |   |        |     | REV<  | :13:8> |   |       |

|       |   | bit 13 |     |       |        |   | bit 8 |

| r     |   |        |     |       |        |   |       |

| R     | R | R      | R   | R     | R      | R | R     |

|       |   |        | REV | <7:0> |        |   |       |

| bit 7 |   |        |     |       |        |   | bit 0 |

| -     |   |        |     |       |        |   |       |

#### Legend:

R = Readable bit '1' = Bit is set

'0' = Bit is cleared

bit 13-0 **REV<13:0>:** Revision ID bits

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

## EXAMPLE 10-3: WRITING TO FLASH PROGRAM MEMORY (32 WRITE LATCHES)

|                      | LE 10-3:      | WRITING TO FLA     | ASH PROGRAM MEMORY (32 WRITE LATCHES)                      |

|----------------------|---------------|--------------------|------------------------------------------------------------|

| ; This               | write rout    | ine assumes the f  | following:                                                 |

|                      |               |                    | starting at the address in DATA_ADDR                       |

|                      | -             |                    | en is made up of two adjacent bytes in DATA_ADDR,          |

|                      |               | ttle endian forma. |                                                            |

| ; 3. A               | valid star    | ting address (the  | e Least Significant bits = 00000) is loaded in ADDRH:ADDRL |

| ; 4. AI              | DDRH and AD   | DRL are located i  | n shared data memory 0x70 - 0x7F (common RAM)              |

| ;                    |               |                    |                                                            |

|                      | BCF           | INTCON,GIE         | ; Disable ints so required sequences will execute properly |

|                      | BANKSEL       | PMADRH             | ; Bank 3                                                   |

|                      | MOVF          | ADDRH,W            | ; Load initial address                                     |

|                      | MOVWF         | PMADRH             | ;                                                          |

|                      | MOVF          | ADDRL,W            | ;                                                          |

|                      | MOVWF         | PMADRL             | ;                                                          |

|                      | MOVLW         | LOW DATA_ADDR      | ; Load initial data address                                |

|                      | MOVWF         | FSROL              | i                                                          |

|                      | MOVLW         | HIGH DATA_ADDR     | ; Load initial data address                                |

|                      | MOVWF         |                    | ;                                                          |

|                      | BCF           |                    | ; Not configuration space                                  |

|                      | BSF           |                    | ; Enable writes                                            |

|                      | BSF           | PMCON1,LWLO        | ; Only Load Write Latches                                  |

| LOOP                 |               |                    |                                                            |

|                      | MOVIW         | FSR0++             | ; Load first data byte into lower                          |

|                      | MOVWF         | PMDATL             | ;                                                          |

|                      | MOVIW         | FSR0++             | ; Load second data byte into upper                         |

|                      | MOVWF         | PMDATH             | ;                                                          |

|                      |               |                    |                                                            |

|                      | MOVF          | PMADRL,W           | ; Check if lower bits of address are '00000'               |

|                      | XORLW         | 0x1F               | ; Check if we're on the last of 32 addresses .             |

|                      | ANDLW         |                    | ;<br>. This if less of 20 monda                            |

|                      | BTFSC<br>GOTO | STATUS,Z           | ; Exit if last of 32 words,<br>;                           |

|                      | GOIO          | START_WRITE        | 1                                                          |

|                      | MOVLW         | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF         |                    | ; Write 55h                                                |

| - O                  | MOVLW         |                    | ;                                                          |

| anc of               | MOVWF         |                    | ; Write AAh                                                |

| Required<br>Sequence | BSF           |                    | ; Set WR bit to begin write                                |

| Sec                  | NOP           |                    | ; NOP instructions are forced as processor                 |

|                      |               |                    | ; loads program memory write latches                       |

|                      | NOP           |                    | ;                                                          |

|                      |               |                    |                                                            |

|                      | INCF          | PMADRL, F          | ; Still loading latches Increment address                  |

|                      | GOTO          |                    | ; Write next latches                                       |

|                      |               |                    |                                                            |

| START_W              | WRITE         |                    |                                                            |

|                      | BCF           | PMCON1,LWLO        | ; No more loading latches - Actually start Flash program   |

|                      |               |                    | ; memory write                                             |

|                      |               |                    |                                                            |

|                      | MOVLW         | 55h                | ; Start of required write sequence:                        |

|                      | MOVWF         | PMCON2             | ; Write 55h                                                |

| e e                  | MOVLW         |                    | i                                                          |

| uire                 | MOVWF         | PMCON2             | ; Write AAh                                                |

| Required<br>Sequence | BSF           | PMCON1,WR          | ; Set WR bit to begin write                                |

| шs                   | NOP           |                    | ; NOP instructions are forced as processor writes          |

|                      |               |                    | ; all the program memory write latches simultaneously      |

|                      | NOP           |                    | ; to program memory.                                       |

| L                    |               |                    | ; After NOPs, the processor                                |

|                      |               |                    | ; stalls until the self-write process in complete          |

|                      | DOE           | DMOON1 LIESS       | ; after write processor continues with 3rd instruction     |

|                      | BCF           | PMCON1, WREN       | ; Disable writes                                           |

|                      | BSF           | INTCON,GIE         | ; Enable interrupts                                        |

|                      |               |                    |                                                            |

| R/W-1/1              | R/W-1/1              | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|----------------------|----------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| SLRC7 <sup>(1)</sup> | SLRC6 <sup>(1)</sup> | SLRC5             | SLRC4   | SLRC3                                                 | SLRC2   | SLRC1   | SLRC0   |  |  |  |

| bit 7                |                      |                   |         |                                                       |         | •       | bit 0   |  |  |  |

|                      |                      |                   |         |                                                       |         |         |         |  |  |  |

| Legend:              |                      |                   |         |                                                       |         |         |         |  |  |  |

| R = Readable         | bit                  | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unch      | anged                | x = Bit is unkr   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set     |                      | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |  |

|                      |                      |                   |         |                                                       |         |         |         |  |  |  |

|                      |                      |                   |         |                                                       |         |         |         |  |  |  |

## REGISTER 12-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits<sup>(1)</sup> For RC<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

Note 1: SLRC<7:6> on PIC16(L)F1618 only.

## REGISTER 12-24: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| R/W-0/0                | R/W-0/0                | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------------------|------------------------|---------|---------|---------|---------|---------|---------|

| INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7                  |                        |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLC<7:0>: PORTC Input Level Select bits<sup>(1)</sup>

For RC<7:0> pins, respectively

- 1 = ST input used for PORT reads and interrupt-on-change

- 0 = TTL input used for PORT reads and interrupt-on-change

Note 1: INLVLC<7:6> on PIC16(L)F1618 only.

## 14.0 INTERRUPT-ON-CHANGE

The PORTA, PORTB<sup>(1)</sup> and PORTC pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 14-1 is a block diagram of the IOC module.

#### Note 1: PORTB available on PIC16(L)F1618 only.

## 14.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

## 14.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

## 14.3 Interrupt Flags

The IOCAFx, IOCBFx and IOCCFx bits located in the IOCAF, IOCBF and IOCCF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx, IOCBFx and IOCCFx bits.

## 14.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx, IOCBFx and IOCCFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 14-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 14.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

| Peripheral | Conditions                                                    | Description                                                        |

|------------|---------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                       | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                               | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                                 | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                                 | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC16F1614/8 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

TABLE 15-1:

PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

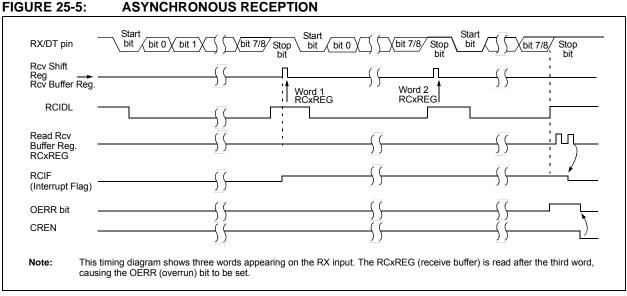

#### 25.1.2.8 Asynchronous Reception Set-up

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- If 9-bit reception is desired, set the RX9 bit. 5.

- Enable reception by setting the CREN bit. 6.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags 8. and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- Enable the serial port by setting the SPEN bit. 3. The SYNC bit must be clear for asynchronous operation.

- 4 If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN 6. bit.

- Enable reception by setting the CREN bit. 7.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags. 9. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

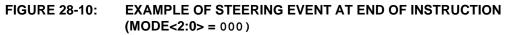

## 28.9 CWG Steering Mode

In Steering mode (MODE = 00x), the CWG allows any combination of the CWGxx pins to be the modulated signal. The same signal can be simultaneously available on multiple pins, or a fixed-value output can be presented.

When the respective STRx bit of CWGxOCON0 is '0', the corresponding pin is held at the level defined. When the respective STRx bit of CWGxOCON0 is '1', the pin is driven by the input data signal. The user can assign the input data signal to one, two, three, or all four output pins.

The POLx bits of the CWGxCON1 register control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 28.10 "Auto-Shutdown"**. An auto-shutdown event will only affect pins that have STRx = 1.

## 28.9.1 STEERING SYNCHRONIZATION

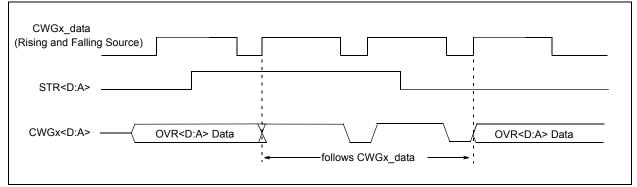

Changing the MODE bits allows for two modes of steering, synchronous and asynchronous.

When MODE = 000, the steering event is asynchronous and will happen at the end of the instruction that writes to STRx (that is, immediately). In this case, the output signal at the output pin may be an incomplete waveform. This can be useful for immediately removing a signal from the pin.

When MODE = 001, the steering update is synchronous and occurs at the beginning of the next rising edge of the input data signal. In this case, steering the output on/off will always produce a complete waveform.

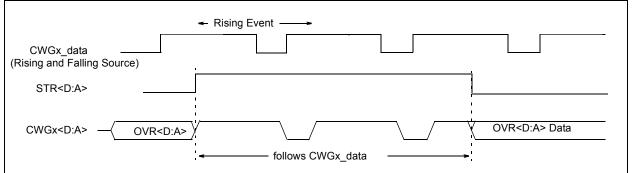

Figure 28-10 and Figure 28-11 illustrate the timing of asynchronous and synchronous steering, respectively.

FIGURE 28-11: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (MODE<2:0> = 001)

| U-0   | U-0 | R-x | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | IN  | —   | POLD    | POLC    | POLB    | POLA    |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:                                                                                   |              |                            |                                    |

|-------------------------------------------------------------------------------------------|--------------|----------------------------|------------------------------------|

| R = Readable bit W = Writable bit                                                         |              | W = Writable bit           | U = Unimplemented bit, read as '0' |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Re |              |                            |                                    |

| '1' = Bit is set                                                                          |              | '0' = Bit is cleared       | q = Value depends on condition     |

|                                                                                           |              |                            |                                    |

| bit 7-6                                                                                   | Unimplemer   | nted: Read as '0'          |                                    |

| bit 5 IN: CWG Input Value                                                                 |              |                            |                                    |

| bit 4 Unimplemented: Read as '0'                                                          |              |                            |                                    |

| bit 3 POLD: CWGxD Output Polarity bit                                                     |              |                            |                                    |

| 1 = Signal output is inverted polarity                                                    |              |                            |                                    |

| <ul><li>0 = Signal output is normal polarity</li></ul>                                    |              |                            |                                    |

| bit 2 POLC: CWGxC Output Polarity bit                                                     |              |                            |                                    |

|                                                                                           | •            | utput is inverted polarity |                                    |

| 0 = Signal output is normal polarity                                                      |              |                            |                                    |

| bit 1                                                                                     | POLB: CWG    | SxB Output Polarity bit    |                                    |

| 1 = Signal output is inverted polarity                                                    |              |                            |                                    |

|                                                                                           | 0 = Signal o | utput is normal polarity   |                                    |

| bit 0                                                                                     | POLA: CWG    | ExA Output Polarity bit    |                                    |

|                                                                                           | •            | utput is inverted polarity |                                    |

|                                                                                           | 0 = Signal o | utput is normal polarity   |                                    |

|                                                                                           |              |                            |                                    |

| U-0                                                                            | U-0 | R/W-x/u        | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u     | R/W-x/u |

|--------------------------------------------------------------------------------|-----|----------------|---------|--------------|------------------|-------------|---------|

| —                                                                              | -   |                |         | DBR          | <5:0>            |             |         |

| bit 7                                                                          |     |                |         |              |                  |             | bit 0   |

|                                                                                |     |                |         |              |                  |             |         |

| Legend:                                                                        |     |                |         |              |                  |             |         |

| R = Readable                                                                   | bit | W = Writable b | bit     | U = Unimplen | nented bit, read | as '0'      |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at a |     |                |         |              | R/Value at all o | ther Resets |         |

q = Value depends on condition

| bit 7-6 Unimplemented: Read as '0' | bit 7-6 | Unimplemented: Read as '0' |

|------------------------------------|---------|----------------------------|

|------------------------------------|---------|----------------------------|

'1' = Bit is set

bit 5-0 DBR<5:0>: Rising Event Dead-Band Value for Counter bits

'0' = Bit is cleared

## REGISTER 28-4: CWGxDBF: CWGx FALLING DEAD-BAND COUNTER REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF     | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 DBF<5:0>: Falling Event Dead-Band Value for Counter bits

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|---------|--------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                    | SMTxTN  | MR<7:0>        |                  |                |              |

| bit 7            |         |                    |         |                |                  |                | bit 0        |

|                  |         |                    |         |                |                  |                |              |

| Legend:          |         |                    |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unknown |         | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                |                  |                |              |

## REGISTER 30-9: SMTxTMRL: SMT TIMER REGISTER – LOW BYTE

bit 7-0 SMTxTMR<7:0>: Significant bits of the SMT Counter – Low Byte

### REGISTER 30-10: SMTxTMRH: SMT TIMER REGISTER - HIGH BYTE

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------------|---------|---------|---------|---------|---------|---------|---------|

| SMTxTMR<15:8> |         |         |         |         |         |         |         |

| bit 7 bit 0   |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxTMR<15:8>: Significant bits of the SMT Counter – High Byte

### REGISTER 30-11: SMTxTMRU: SMT TIMER REGISTER - UPPER BYTE

| R/W-0/0        | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|----------------|---------|-----------------|---------|--------------|------------------|----------|---------|--|

| SMTxTMR<23:16> |         |                 |         |              |                  |          |         |  |

| bit 7          |         |                 |         |              |                  |          | bit 0   |  |

|                |         |                 |         |              |                  |          |         |  |

| Legend:        |         |                 |         |              |                  |          |         |  |

| R = Readable b | pit     | W = Writable bi | t       | U = Unimpler | nented bit, read | d as '0' |         |  |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxTMR<23:16>: Significant bits of the SMT Counter – Upper Byte

| TABLE 30-3: |                         |               |           |           |          |                  |           |        |                     |

|-------------|-------------------------|---------------|-----------|-----------|----------|------------------|-----------|--------|---------------------|

| Name        | Bit 7                   | Bit 6         | Bit 5     | Bit 4     | Bit 3    | Bit 2            | Bit 1     | Bit 0  | Register on<br>Page |

| PIE4        | SCANIE                  | CRCIE         | SMT2PWAIE | SMT2PRAIE | SMT2IE   | SMT1PWAIE        | SMT1PRAIE | SMT1IE | 101                 |

| PIR4        | SCANIF                  | CRCIF         | SMT2PWAIF | SMT2PRAIF | SMT2IF   | SMT1PWAIF        | SMT1PRAIF | SMT1IF | 106                 |

| SMT1CLK     | _                       | _             | —         | —         | _        |                  | CSEL<2:0> |        | 438                 |

| SMT1CON0    | EN                      | _             | STP       | WPOL      | SPOL     | CPOL             | SMT1P     | 435    |                     |

| SMT1CON1    | SMT1GO REPEAT MODE<3:0> |               |           |           |          |                  | 436       |        |                     |

| SMT1CPRH    | SMT1CPR<15:8>           |               |           |           |          |                  |           | 444    |                     |

| SMT1CPRL    | SMT1CPR<7:0>            |               |           |           |          |                  |           |        | 444                 |

| SMT1CPRU    | SMT1CPR<23:16>          |               |           |           |          |                  |           |        | 444                 |

| SMT1CPWH    |                         | SMT1CPW<15:8> |           |           |          |                  |           |        |                     |

| SMT1CPWL    |                         | SMT1CPW<7:0>  |           |           |          |                  |           |        |                     |

| SMT1CPWU    | SMT1CPW<23:16>          |               |           |           |          |                  |           |        | 445                 |

| SMT1PRH     |                         |               |           | SMT1PF    | R<15:8>  |                  |           |        | 446                 |

| SMT1PRL     | SMT1PR<7:0>             |               |           |           |          |                  |           |        | 446                 |

| SMT1PRU     | SMT1PR<23:16>           |               |           |           |          |                  |           |        | 446                 |

| SMT1SIG     | — — — SSEL<4:0>         |               |           |           |          |                  |           | 441    |                     |

| SMT1STAT    | CPRUP                   | CPWUP         | RST       | —         |          | TS               | WS        | AS     | 437                 |

| SMT1TMRH    | SMT1TMR<15:8>           |               |           |           |          |                  |           |        | 443                 |

| SMT1TMRL    | SMT1TMR<7:0>            |               |           |           |          |                  |           |        | 443                 |

| SMT1TMRU    | SMT1TMR<23:16>          |               |           |           |          |                  |           | 443    |                     |

| SMT1WIN     | — — — WSEL<4:0>         |               |           |           |          |                  | 439       |        |                     |

| SMT2CLK     | — — — — — CSEL<2:0>     |               |           |           |          |                  | 438       |        |                     |

| SMT2CON0    | EN                      | _             | STP       | WPOL      | SPOL     | CPOL SMT2PS<1:0> |           |        | 435                 |

| SMT2CON1    | SMT2GO                  | REPEAT        | _         | _         |          | MODE             | 436       |        |                     |

| SMT2CPRH    | SMT2CPR<15:8>           |               |           |           |          |                  | 444       |        |                     |

| SMT2CPRL    | SMT2CPR<7:0>            |               |           |           |          |                  |           | 444    |                     |

| SMT2CPRU    |                         |               |           | SMT2CPI   | R<23:16> |                  |           |        | 444                 |

| SMT2CPWH    |                         |               |           | SMT2CP    | W<15:8>  |                  |           |        | 445                 |

| SMT2CPWL    |                         | SMT2CPW<7:0>  |           |           |          |                  |           |        |                     |

| SMT2CPWU    | SMT2CPW<23:16>          |               |           |           |          |                  |           |        | 445                 |

| SMT2PRH     |                         |               |           | SMT2PF    | R<15:8>  |                  |           |        | 446                 |

| SMT2PRL     |                         |               |           | SMT2P     | R<7:0>   |                  |           |        | 446                 |

| SMT2PRU     |                         |               |           | SMT2PF    | R<23:16> |                  |           |        | 446                 |

| SMT2SIG     | —                       | _             | _         | _         | —        |                  | SSEL<2:0> |        | 441                 |

| SMT2STAT    | CPRUP                   | CPWUP         | RST       | _         | _        | TS               | WS        | AS     | 437                 |

| SMT2TMRH    |                         |               | •         | SMT2TM    | IR<15:8> |                  |           |        | 443                 |

| SMT2TMRL    | SMT2TMR<7:0>            |               |           |           |          |                  |           | 443    |                     |

| SMT2TMRU    | SMT2TMR<23:16>          |               |           |           |          |                  |           | 443    |                     |

| SMT2WIN     | WSEL<4:0>               |               |           |           |          |                  | 438       |        |                     |

|             |                         |               |           |           |          |                  |           |        |                     |

TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH SMTx

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for SMTx module.

## 31.7 Interrupts

The angular timer and its capture/compare features can generate multiple interrupt conditions. To accommodate all of these interrupt sources, the module is provided with its own interrupt logic structure, similar to that of the micro controller. Angular timer interrupts are enabled by the ATxIE0 register (Register 31-13) and their respective flags are located in the ATxIR0 register (Register 31-14). The capture/compare interrupts are enabled by the ATxIE1 register (Register 31-15) with flags in the ATxIR1 register (Register 31-16). All sources are funneled into a single Angular Timer Interrupt Flag bit, ATxIF of the PIR5 register (Register 7-11). This means that upon a triggered interrupt, the ATxIR0 and ATxIR1 register bits will indicate the source of the triggered interrupt. It also means that in order for specific interrupts to generate a microcontroller interrupt, both the ATxIE bit of the PIE register and the desired enable bit in either ATxIE0 or ATxIE1 must be set.

| Note: | Due to the nature of the angular timer     |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | interrupts, the ATxIF flag bit of the PIR5 |  |  |  |  |  |

|       | register is read-only.                     |  |  |  |  |  |

## 31.7.1 ANGULAR TIMER PERIOD INTERRUPT

This interrupt is triggered when the AT module detects a period event. In Single-Pulse mode, a period event occurs on every input signal edge. In Multi-Pulse mode, a period event occurs on the input signal edge following a missed pulse. The period interrupt generation matches with the pulses on the period clock output of the timer. It is enabled by the ATPERIE bit of the ATxIE0 register and the status is indicated by the PERIF bit of the ATxIR0 register.

# 31.7.2 ANGULAR TIMER PHASE CLOCK INTERRUPT

This interrupt is triggered on each pulse of the phase clock output of the timer. It is enabled by the ATPHIE bit of the ATxIE0 register and the status is indicated by the PHSIF bit of the ATxIR0 register.

# 31.7.3 ANGULAR TIMER MISSING PULSE INTERRUPT

This interrupt is triggered upon the output of a missing pulse detection signal. Refer to **Section 31.2.3 "Missing Pulse Detection"** for more information. This interrupt is enabled by the ATMISSIE bit of the ATXIE0 register and its status is indicated by the ATMISSIF bit of the ATXIR0 register.

## 31.7.4 ANGULAR TIMER CAPTURE/COMPARE INTERRUPTS

Capture and compare interrupts are triggered by the capture/compare functions of the module. If configured for Capture mode, the interrupt will trigger after the capture signal has successfully latched the value of the phase counter into the capture registers. If configured for Compare mode, the interrupt will trigger when a match is detected between the value placed in the compare register and the value of the phase counter. These interrupts are controlled by the CC1IE, CC2IE, and CC3IE bits of the ATxIE1 register, respectively, and are similarly indicated by the CC1IF, CC2IF, and CC3IF bits of the ATxIR1 register.

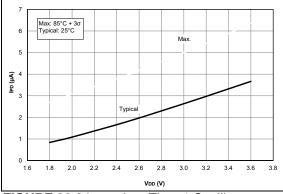

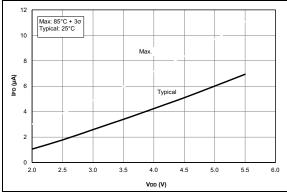

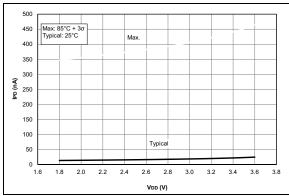

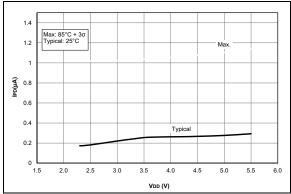

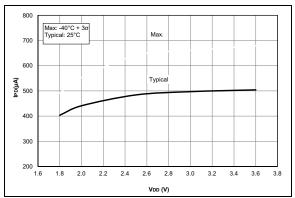

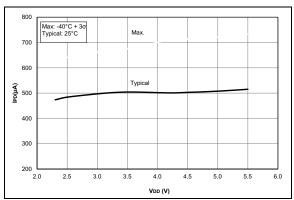

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

FIGURE 36-32: IPD, Timer1 Oscillator, Fosc = 32 kHz, PIC16F1614/8 Only.

FIGURE 36-33: IPD, ADC Non-Converting, PIC16LF1614/8 Only.

FIGURE 36-34: IPD, ADC Non-Converting, PIC16F1614/8 Only.

**FIGURE 36-35:** IPD, Comparator, NP Mode (CxSP = 1), PIC16LF1614/8 Only.

**FIGURE 36-36:** IPD, Comparator, NP Mode (CxSP = 1), PIC16F1614/8 Only.