Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1614t-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Value on Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR, BOR

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-14:

| Banks              | <u>s 27</u> |                |                                       |     |         |          |           |           |           | _         |           |

|--------------------|-------------|----------------|---------------------------------------|-----|---------|----------|-----------|-----------|-----------|-----------|-----------|

| D80h<br>to<br>D8Bh | _           | Unimplemented  | Unimplemented                         |     |         |          |           |           |           |           | _         |

| D8Ch               | SMT1TMRL    |                |                                       |     | SMT1TN  | /IR<7:0> |           |           |           | 0000 0000 | 0000 0000 |

| D8Dh               | SMT1TMRH    |                |                                       |     | SMT1TM  | IR<15:8> |           |           |           | 0000 0000 | 0000 0000 |

| D8Eh               | SMT1TMRU    |                |                                       |     | SMT1TMI | R<23:16> |           |           |           | 0000 0000 | 0000 0000 |

| D8Fh               | SMT1CPRL    |                |                                       |     | SMT1CF  | PR<7:0>  |           |           |           | XXXX XXXX | XXXX XXXX |

| D90h               | SMT1CPRH    |                |                                       |     | SMT1CP  | R<15:8>  |           |           |           | xxxx xxxx | XXXX XXXX |

| D91h               | SMT1CPRU    |                |                                       |     | SMT1CP  | R<23:16> |           |           |           | XXXX XXXX | XXXX XXXX |

| D92h               | SMT1CPWL    |                |                                       |     | SMT1CF  | PW<7:0>  |           |           |           | XXXX XXXX | XXXX XXXX |

| D93h               | SMT1CPWH    |                |                                       |     | SMT1CP  | W<15:8>  |           |           |           | XXXX XXXX | XXXX XXXX |

| D94h               | SMT1CPWU    |                | SMT1CPW<23:16>                        |     |         |          |           |           |           | xxxx xxxx | xxxx xxxx |

| D95h               | SMT1PRL     |                | SMT1PR<7:0>                           |     |         |          |           |           |           | xxxx xxxx | XXXX XXXX |

| D96h               | SMT1PRH     |                | SMT1PR<15:8>                          |     |         |          |           |           |           | XXXX XXXX | xxxx xxxx |

| D97h               | SMT1PRU     |                |                                       |     | SMT1PR  | <23:16>  |           |           |           | XXXX XXXX | xxxx xxxx |

| D98h               | SMT1CON0    | EN             | _                                     | STP | WPOL    | SPOL     | CPOL      | SMT1P     | S<1:0>    | 0-00 0000 | 0-00 0000 |

| D99h               | SMT1CON1    | SMT1GO         | REPEAT                                | —   | —       |          | MODE      | <3:0>     |           | 00 0000   | 00 0000   |

| D9Ah               | SMT1STAT    | CPRUP          | CPWUP                                 | RST | —       |          | TS        | WS        | AS        | 000000    | 000000    |

| D9Bh               | SMT1CLK     | —              | _                                     | _   | —       | _        |           | CSEL<2:0> |           | 000       | 000       |

| D9Ch               | SMT1SIG     | —              | _                                     | —   |         |          | SSEL<4:0> |           |           | 0 0000    | 0 0000    |

| D9Dh               | SMT1WIN     | _              |                                       | _   |         |          | WSEL<4:0> |           |           | 0 0000    | 0 0000    |

| D9Eh               | SMT2TMRL    |                |                                       |     | SMT2TM  | /IR<7:0> |           |           |           | 0000 0000 | 0000 0000 |

| D9Fh               | SMT2TMRH    |                | SMT2TMR<15:8>                         |     |         |          |           |           |           | 0000 0000 | 0000 0000 |

| DA0h               | SMT2TMRU    | SMT2TMR<23:16> |                                       |     |         |          |           |           |           | 0000 0000 | 0000 0000 |

| DA1h               | SMT2CPRL    | SMT2CPR<7:0>   |                                       |     |         |          |           |           |           | xxxx xxxx | xxxx xxxx |

| DA2h               | SMT2CPRH    | SMT2CPR<15:8>  |                                       |     |         |          |           |           | XXXX XXXX | xxxx xxxx |           |

| DA3h               | SMT2CPRU    |                |                                       |     | SMT2CPI | R<23:16> |           |           |           | xxxx xxxx | XXXX XXXX |

| DA4h               | SMT2CPWL    |                | SMT2CPW<7:0> xxxx xxxx xxxx xxxx xxxx |     |         |          |           |           |           |           | XXXX XXXX |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

Value on all

other Resets

# PIC16(L)F1614/8

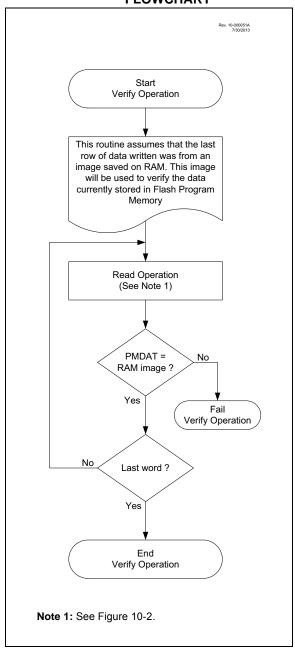

#### 10.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

#### 12.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when in Analog mode.

| R/W-0/0                                  | R/W-0/0                                        | R/W-0/0                             | R/W-0/0          | R/W-0/0        | U-0              | U-0              | U-0          |  |  |  |  |

|------------------------------------------|------------------------------------------------|-------------------------------------|------------------|----------------|------------------|------------------|--------------|--|--|--|--|

|                                          | Т                                              | [RIGSEL<4:0>(1                      | 1)               |                | —                | —                | —            |  |  |  |  |

| bit 7                                    |                                                |                                     |                  |                |                  |                  | bit (        |  |  |  |  |

|                                          |                                                |                                     |                  |                |                  |                  |              |  |  |  |  |

| Legend:                                  | alo hit                                        | W = Writable                        | bit              | II – Unimplor  | nented bit, read | d ac 'O'         |              |  |  |  |  |

| R = Readable bit<br>u = Bit is unchanged |                                                |                                     |                  | ther Decete    |                  |                  |              |  |  |  |  |

|                                          |                                                | x = Bit is unki                     |                  |                | at POR and BC    | R/Value at all o | Juner Resels |  |  |  |  |

| '1' = Bit is s                           | et                                             | '0' = Bit is cle                    | ared             |                |                  |                  |              |  |  |  |  |

|                                          |                                                |                                     | · <b>·</b> ·     | 0.1            | <b>`</b>         |                  |              |  |  |  |  |

| bit 7-3                                  |                                                | I:0>: Auto-Conv                     | ersion Trigger   | Selection bits | ,                |                  |              |  |  |  |  |

|                                          | 11111 = Re                                     | eserved                             |                  |                |                  |                  |              |  |  |  |  |

|                                          | •                                              |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | •                                              |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 10101 <b>= Re</b>                              | 10101 = Reserved                    |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | 10100 = AT1_cmp3                    |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | 10011 = AT1_cmp2                    |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | 10010 = AT1_cmp1<br>10001 = CLC4OUT |                  |                |                  |                  |              |  |  |  |  |

|                                          | 10001 = CL<br>10000 = CL                       |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 01111 = CL                                     |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 01110 = CL                                     |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | IR5_overflow                        |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | 1R3_overflow                        |                  |                |                  |                  |              |  |  |  |  |

|                                          | 01011 = SM                                     |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | =SMT1_match                         |                  |                |                  |                  |              |  |  |  |  |

|                                          | $01001 = TMR6_postscaled$                      |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 01000 = TMR4_postscaled<br>00111 = C2_OUT_sync |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | $00111 = C2_001_sync$ $00110 = C1_0UT_sync$    |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          |                                                | 00101 = TMR2_postscaled             |                  |                |                  |                  |              |  |  |  |  |

|                                          | 00100 <b>= T1</b>                              | $D100 = T1_overflow^{(2)}$          |                  |                |                  |                  |              |  |  |  |  |

|                                          | 00011 <b>= TO</b>                              |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 00010 = CC                                     |                                     |                  |                |                  |                  |              |  |  |  |  |

|                                          | 00001 = CC                                     |                                     | n trigger ecles  | atad           |                  |                  |              |  |  |  |  |

|                                          |                                                | auto-conversio                      |                  | lea            |                  |                  |              |  |  |  |  |

| bit 2-0                                  | Unimpleme                                      | nted: Read as '                     | 0.               |                |                  |                  |              |  |  |  |  |

| Note 1: 7                                | This is a rising e                             | dge sensitive inp                   | out for all sour | ces.           |                  |                  |              |  |  |  |  |

| 2.                                       | Signal also sets i                             | its correspondin                    | a interrunt flag | r              |                  |                  |              |  |  |  |  |

#### REGISTER 17-3: ADCON2: ADC CONTROL REGISTER 2

2: Signal also sets its corresponding interrupt flag.

#### 20.2 ZCD Logic Output

The ZCD module includes a Status bit, which can be read to determine whether the current source or sink is active. The ZCDxOUT bit of the ZCDxCON register is set when the current sink is active, and cleared when the current source is active. The ZCDxOUT bit is affected by the polarity bit.

### 20.3 ZCD Logic Polarity

The ZCDxPOL bit of the ZCDxCON register inverts the ZCDxOUT bit relative to the current source and sink output. When the ZCDxPOL bit is set, a ZCDxOUT high indicates that the current source is active, and a low output indicates that the current sink is active.

The ZCDxPOL bit affects the ZCD interrupts. See **Section20.4 "ZCD Interrupts"**.

#### 20.4 ZCD Interrupts

An interrupt will be generated upon a change in the ZCD logic output when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in the ZCD for this purpose.

The ZCDIF bit of the PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The ZCDxINTP enables rising edge interrupts and the ZCDxINTN bit enables falling edge interrupts. Both are located in the ZCDxCON register.

To fully enable the interrupt, the following bits must be set:

- ZCDIE bit of the PIE3 register

- ZCDxINTP bit of the ZCDxCON register (for a rising edge detection)

- ZCDxINTN bit of the ZCDxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

Changing the ZCDxPOL bit will cause an interrupt, regardless of the level of the ZCDxEN bit.

The ZCDIF bit of the PIR3 register must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

#### 20.5 Correcting for VCPINV offset

The actual voltage at which the ZCD switches is the reference voltage at the non-inverting input of the ZCD op amp. For external voltage source waveforms other than square waves, this voltage offset from zero causes the zero-cross event to occur either too early or too late. When the waveform is varying relative to Vss, then the zero cross is detected too early as the waveform falls and too late as the waveform rises. When the waveform is varying relative to VDD, then the zero cross is detected too late as the waveform rises and too early as the waveform falls. The actual offset time can be determined for sinusoidal waveforms with the corresponding equations shown in Equation 20-2.

#### EQUATION 20-2: ZCD EVENT OFFSET

When External Voltage Source is relative to Vss:

$$TOFFSET = \frac{\operatorname{asin}\left(\frac{Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$$

When External Voltage Source is relative to VDD:

$TOFFSET = \frac{\operatorname{asin}\left(\frac{VDD - Vcpinv}{VPEAK}\right)}{2\pi \bullet Freq}$

This offset time can be compensated for by adding a pull-up or pull-down biasing resistor to the ZCD pin. A pull-up resistor is used when the external voltage source is varying relative to Vss. A pull-down resistor is used when the voltage is varying relative to VDD. The resistor adds a bias to the ZCD pin so that the target external voltage source must go to zero to pull the pin voltage to the VCPINV switching voltage. The pull-up or pull-down value can be determined with the equations shown in Equation 20-3 or Equation 20-4.

#### EQUATION 20-3: ZCD PULL-UP/DOWN

When External Signal is relative to Vss:

$$R_{PULLUP} = \frac{R_{SERIES}(V_{PULLUP} - V_{Cpinv})}{V_{Cpinv}}$$

When External Signal is relative to VDD:

$$R_{PULLDOWN} = \frac{R_{SERIES}(Vcpinv)}{(VDD - Vcpinv)}$$

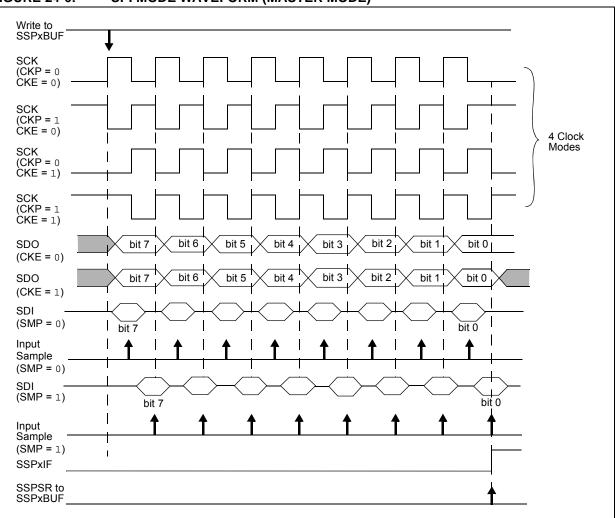

#### 24.2.4 SPI SLAVE MODE

In Slave mode, the data is transmitted and received as external clock pulses appear on SCK. When the last bit is latched, the SSPxIF interrupt flag bit is set.

Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit of the SSPxCON1 register.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. The shift register is clocked from the SCK pin input and when a byte is received, the device will generate an interrupt. If enabled, the device will wake-up from Sleep.

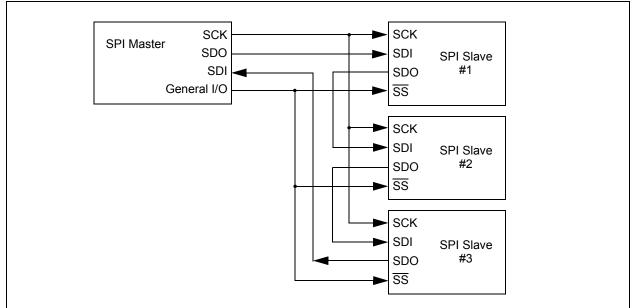

#### 24.2.4.1 Daisy-Chain Configuration

The SPI bus can sometimes be connected in a daisychain configuration. The first slave output is connected to the second slave input, the second slave output is connected to the third slave input, and so on. The final slave output is connected to the master input. Each slave sends out, during a second group of clock pulses, an exact copy of what was received during the first group of clock pulses. The whole chain acts as one large communication shift register. The daisychain feature only requires a single Slave Select line from the master device.

Figure 24-7 shows the block diagram of a typical daisy-chain connection when operating in SPI mode.

In a daisy-chain configuration, only the most recent byte on the bus is required by the slave. Setting the BOEN bit of the SSPxCON3 register will enable writes to the SSPxBUF register, even if the previous byte has not been read. This allows the software to ignore data that may not apply to it.

#### 24.2.5 SLAVE SELECT SYNCHRONIZATION

The Slave Select can also be used to synchronize communication. The Slave Select line is held high until the master device is ready to communicate. When the Slave Select line is pulled low, the slave knows that a new transmission is starting.

If the slave fails to receive the communication properly, it will be reset at the end of the transmission, when the Slave Select line returns to a high state. The slave is then ready to receive a new transmission when the Slave Select line is pulled low again. If the Slave Select line is not used, there is a risk that the slave will eventually become out of sync with the master. If the slave misses a bit, it will always be one bit off in future transmissions. Use of the Slave Select line allows the slave and master to align themselves at the beginning of each transmission.

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPxCON1<3:0> = 0100).

FIGURE 24-7: SPI DAISY-CHAIN CONNECTION

When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven.

When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin  |  |  |  |  |  |

|---------|---------------------------------------------------------|--|--|--|--|--|

|         | control enabled (SSPxCON1<3:0> =                        |  |  |  |  |  |

|         | 0100), the SPI module will reset if the $\overline{SS}$ |  |  |  |  |  |

|         | pin is set to VDD.                                      |  |  |  |  |  |

|         |                                                         |  |  |  |  |  |

- 2: When the SPI is used in Slave mode with CKE set; the user must enable SS pin control.

- While operated in SPI Slave mode the SMP bit of the SSPxSTAT register must remain clear.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

PIC16(L)F1614/8

## 24.8 Register Definitions: MSSP Control

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R-0/0                                                                                                                                                  | R-0/0                                                        | R-0/0                   | R-0/0                | R-0/0               | R-0/0            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|----------------------|---------------------|------------------|--|--|--|--|

| SMP              | CKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D/A                                                                                                                                                    | Р                                                            | S                       | R/W                  | UA                  | BF               |  |  |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·                                                                                                                                                      | ·                                                            | •                       | •                    |                     | bit C            |  |  |  |  |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                        |                                                              |                         |                      |                     |                  |  |  |  |  |

| R = Readable b   | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W = Writable bi                                                                                                                                        | t                                                            | U = Unimpleme           | nted bit, read as '0 | )'                  |                  |  |  |  |  |

| u = Bit is uncha | nged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | x = Bit is unkno                                                                                                                                       | wn                                                           | -n/n = Value at         | POR and BOR/Val      | ue at all other Res | ets              |  |  |  |  |

| '1' = Bit is set | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '0' = Bit is clear                                                                                                                                     | 0' = Bit is cleared                                          |                         |                      |                     |                  |  |  |  |  |

| bit 7            | <u>SPI Master mo</u><br>1 = Input data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | a Input Sample bit<br><u>ode:</u><br>sampled at end of<br>sampled at middle                                                                            | •                                                            | 1e                      |                      |                     |                  |  |  |  |  |

|                  | $\frac{\text{SPI Slave mod}}{\text{SMP must be of}}$ $\frac{\text{In I}^2 \text{C Master of}}{1} = \text{Slew rate}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | cleared when SPI i                                                                                                                                     | s used in Slave n<br>r Standard Speed                        | node<br>I mode (100 kHz | and 1 MHz)           |                     |                  |  |  |  |  |

| bit 6            | In SPI Master of<br>1 = Transmit of<br>0 = Transmit of<br>In I <sup>2</sup> C™ mode<br>1 = Enable inp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ck Edge Select bit (<br>or Slave mode:<br>ccurs on transition<br>ccurs on transition<br><u>only:</u><br>ut logic so that thread<br>IBus specific input | from active to Idl<br>from Idle to activ<br>esholds are comp | e clock state           | specification        |                     |                  |  |  |  |  |

| bit 5            | 1 = Indicates th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ress bit (I <sup>2</sup> C mode<br>hat the last byte re-<br>hat the last byte re-                                                                      | ceived or transmi                                            |                         |                      |                     |                  |  |  |  |  |

| bit 4            | <ul> <li>P: Stop bit</li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the 1 = Indicates that a Stop bit has been detect</li> <li>0 = Stop bit was not detected last</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |                                                              | o module is disabl      | led, SSPEN is clea   | ired.)              |                  |  |  |  |  |

| bit 3            | <ul> <li>Start bit</li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the 1 = Indicates that a Start bit has been detect</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |                                                              |                         |                      | ired.)              |                  |  |  |  |  |

| bit 2            | <ul> <li>Start bit was not detected last</li> <li>RW: Read/Write bit information (I<sup>2</sup>C mode only)</li> <li>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to next Start bit, Stop bit, or not ACK bit.</li> <li><u>In I<sup>2</sup>C Slave mode:</u> <ol> <li>Read</li> <li>Write</li> <li><u>In I<sup>2</sup>C Master mode:</u></li> <li>Transmit is in progress</li> <li>Transmit is not in progress</li> <li>OR-ing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is in Idle mode.</li> </ol> </li> </ul> |                                                                                                                                                        |                                                              |                         |                      |                     | ess match to the |  |  |  |  |

| bit 1            | <b>UA:</b> Update Address bit (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the S<br>0 = Address does not need to be updated                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |                                                              |                         | 1ADD register        |                     |                  |  |  |  |  |

| bit 0            | BF: Buffer Full Status bit         Receive (SPI and I <sup>2</sup> C modes):         1 = Receive complete, SSP1BUF is full         0 = Receive not complete, SSP1BUF is empty         Transmit (I <sup>2</sup> C mode only):         1 = Data transmit in progress (does not include the ACK and Stop bits), SSP1BUF is full         0 = Data transmit complete (does not include the ACK and Stop bits), SSP1BUF is empty                                                                                                                                                                                             |                                                                                                                                                        |                                                              |                         |                      |                     |                  |  |  |  |  |

#### 25.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 5.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 25.4.1 "Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| 1100KL 25-12.                           | STACHAOUS RECEITION (MASTER MODE, SREN)                                |          |

|-----------------------------------------|------------------------------------------------------------------------|----------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0) | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                        |          |

| TX/CK pin                               |                                                                        | <u> </u> |

| SREN bit                                |                                                                        | '0'      |

| RCIF bit<br>(Interrupt)                 |                                                                        | Ľ        |

| Read<br>RCxREG                          | gram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |          |

| 1                                       |                                                                        |          |

#### FIGURE 25-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# TABLE 25-8: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION RECEPTION

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4       | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|-------------|--------------|------------|--------|--------|---------------------|

| ANSELA                | —                     | —                     |        | ANSA4       |              | ANSA2      | ANSA1  | ANSA0  | 152                 |

| ANSELB <sup>(1)</sup> | _                     | —                     | ANSB5  | ANSB4       | _            | —          | _      | —      | 159                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  |        | —           | ANSC3        | ANSC2      | ANSC1  | ANSC0  | 166                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | _      | SCKP        | BRG16        | —          | WUE    | ABDEN  | 323                 |

| CKPPS                 | —                     | —                     | -      |             |              | CKPPS<4:0> |        |        | 174, 172            |

| INTCON                | GIE                   | PEIE                  | TMR0IE | INTE        | IOCIE        | TMR0IF     | INTF   | IOCIF  | 97                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE   | TXIE        | SSP1IE       | CCP1IE     | TMR2IE | TMR1IE | 98                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF   | TXIF        | SSP1IF       | CCP1IF     | TMR2IF | TMR1IF | 103                 |

| RC1REG                |                       |                       | EUS    | SART Receiv | e Data Regis | ster       |        |        | 316*                |

| RC1STA                | SPEN                  | RX9                   | SREN   | CREN        | ADDEN        | FERR       | OERR   | RX9D   | 322                 |

| RXPPS                 | —                     | —                     | _      |             | RXPPS<4:0>   |            |        |        |                     |

| RxyPPS                | —                     | _                     | _      |             | F            | RxyPPS<4:0 | >      |        | 172                 |

| SP1BRGL               |                       |                       |        | BRG<        | BRG<7:0>     |            |        |        |                     |

| SP1BRGH               |                       |                       |        | BRG<15:8>   |              |            |        |        | 324*                |

| TRISA                 | —                     | —                     | TRISA5 | TRISA4      | (2)          | TRISA2     | TRISA1 | TRISA0 | 151                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4      | —            | —          | —      | —      | 158                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4      | TRISC3       | TRISC2     | TRISC1 | TRISC0 | 165                 |

| TX1STA                | CSRC                  | TX9                   | TXEN   | SYNC        | SENDB        | BRGH       | TRMT   | TX9D   | 321                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

Note 1: PIC16(L)F1618 only.

**2:** Unimplemented, read as '1'.

#### 30.6.7 TIME OF FLIGHT MEASURE MODE

This mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMTx\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMTxCPR register and resetting the timer upon observing a rising edge on the SMTx\_signal input. In the event of two SMTWINx rising edges without an SMTx\_signal rising edge, it will update the SMTxCPW register with the current value of the timer and reset the timer value. See Figure 30-14 and Figure 30-15.

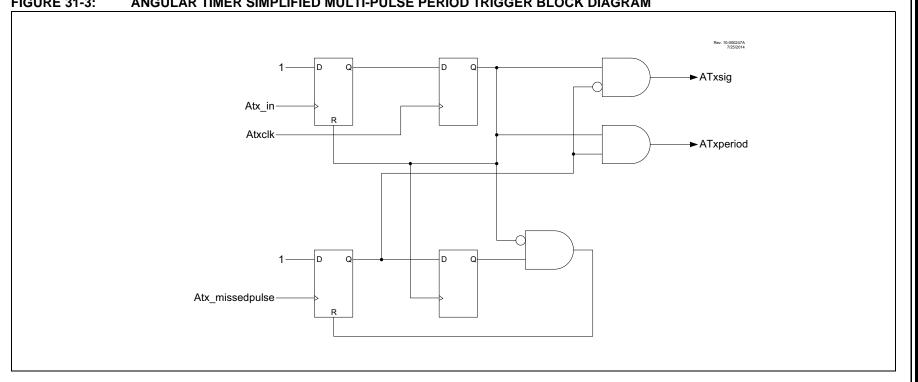

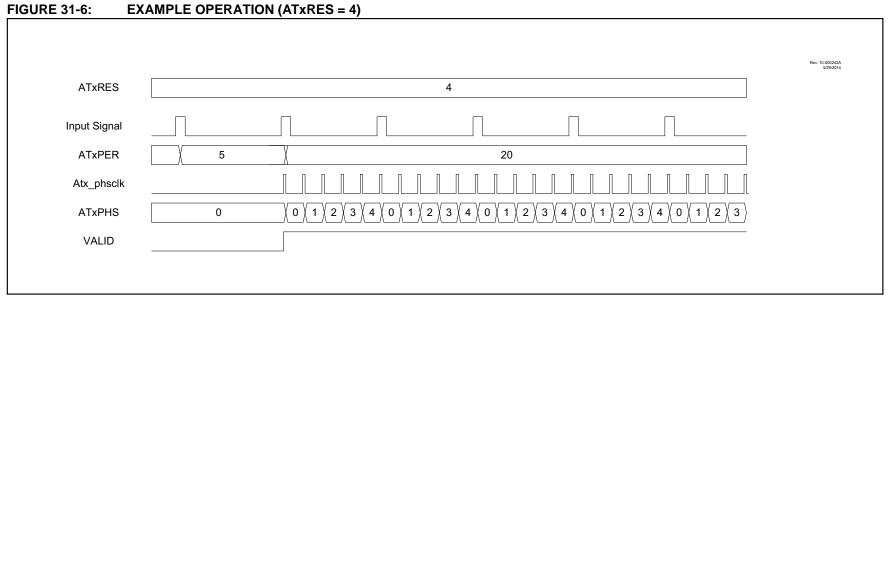

#### FIGURE 31-3: ANGULAR TIMER SIMPLIFIED MULTI-PULSE PERIOD TRIGGER BLOCK DIAGRAM

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                            |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a 2-<br>cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BRW              | Relative Branch with W                                                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                              |

| Operands:        | None                                                                                                                                                                                                              |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be PC + 1 + (W).<br>This instruction is a 2-cycle instruc-<br>tion. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                              |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| CALL             | Call Subroutine                                                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                      |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                      |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | 1 → (f <b>)</b>                                                     |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

# TABLE 35-3: POWER-DOWN CURRENTS (IPD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF16 | 614/8                                       | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |      |       |        |       |     |             |

|-----------|---------------------------------------------|-------------------------------------------------------------------------|------|-------|--------|-------|-----|-------------|

| PIC16F161 | 4/8                                         | Low-Power Sleep Mode, VREGPM = 1                                        |      |       |        |       |     |             |

| Param.    | Device Characteristics   Min   Typt   Units | Conditions                                                              |      |       |        |       |     |             |

| No.       |                                             | Min.                                                                    | Турт | +85°C | +125°C | Units | Vdd | Note        |

| D027      |                                             |                                                                         | 7    | 22    | 25     | μA    | 1.8 | Comparator, |

|           |                                             | _                                                                       | 8    | 23    | 27     | μA    | 3.0 | CxSP = 0    |

| D027      |                                             | —                                                                       | 17   | 35    | 37     | μA    | 2.3 | Comparator, |

|           |                                             | _                                                                       | 18   | 37    | 38     | μA    | 3.0 | CxSP = 0    |

|           |                                             | _                                                                       | 19   | 38    | 40     | μA    | 5.0 |             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Legend:** TBD = To Be Determined

Note 1: The peripheral ∆ current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

Note: Unless otherwise noted, VIN = 5V, Fosc = 500 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

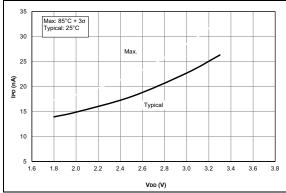

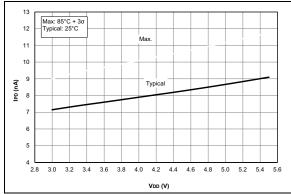

FIGURE 36-25: IPD, Fixed Voltage Reference (FVR), PIC16LF1614/8 Only.

FIGURE 36-26: IPD, Fixed Voltage Reference (FVR), PIC16F1614/8 Only.

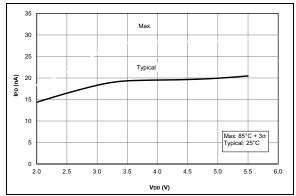

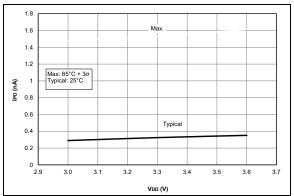

FIGURE 36-27: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16LF1614/8 Only.

FIGURE 36-28: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16F1614/8 Only.

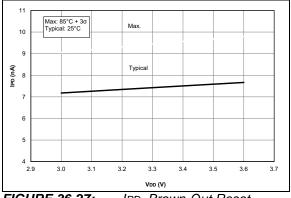

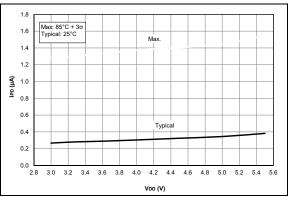

**FIGURE 36-29:** IPD, LP Brown-Out Reset (LPBOR = 0), PIC16LF1614/8 Only.

**FIGURE 36-30:** IPD, LP Brown-Out Reset (LPBOR = 0), PIC16F1614/8 Only.

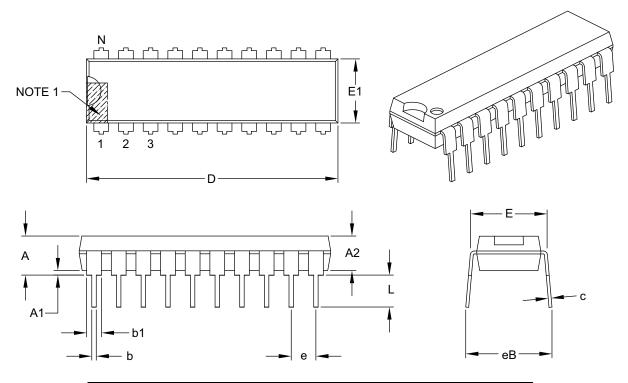

### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES   |       |       |

|----------------------------|------------------|----------|-------|-------|

| Dimensio                   | Dimension Limits |          | NOM   | MAX   |

| Number of Pins             | Ν                | 20       |       |       |

| Pitch                      | е                | .100 BSC |       |       |

| Top to Seating Plane       | А                | -        | -     | .210  |

| Molded Package Thickness   | A2               | .115     | .130  | .195  |

| Base to Seating Plane      | A1               | .015     | -     | -     |

| Shoulder to Shoulder Width | E                | .300     | .310  | .325  |

| Molded Package Width       | E1               | .240     | .250  | .280  |

| Overall Length             | D                | .980     | 1.030 | 1.060 |

| Tip to Seating Plane       | L                | .115     | .130  | .150  |

| Lead Thickness             | С                | .008     | .010  | .015  |

| Upper Lead Width           | b1               | .045     | .060  | .070  |

| Lower Lead Width           | b                | .014     | .018  | .022  |

| Overall Row Spacing §      | eB               | -        | -     | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

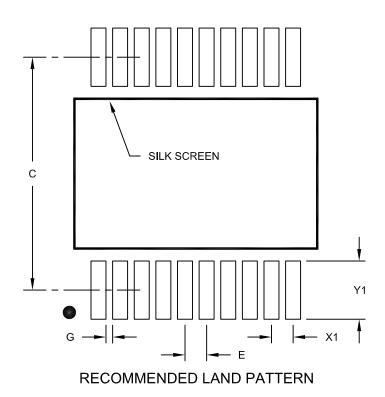

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|------|-------------|--|--|--|

| Dimensior                | Dimension Limits |          |      | MAX         |  |  |  |

| Contact Pitch            | E                | 0.65 BSC |      |             |  |  |  |

| Contact Pad Spacing      | С                |          | 7.20 |             |  |  |  |

| Contact Pad Width (X20)  | X1               |          |      | 0.45        |  |  |  |

| Contact Pad Length (X20) | Y1               |          |      | 1.75        |  |  |  |

| Distance Between Pads    | G                | 0.20     |      |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A