# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

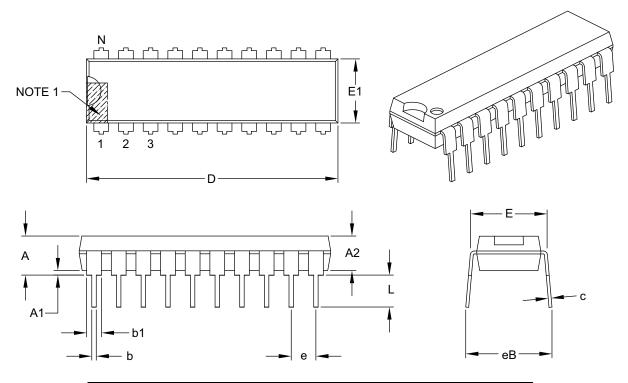

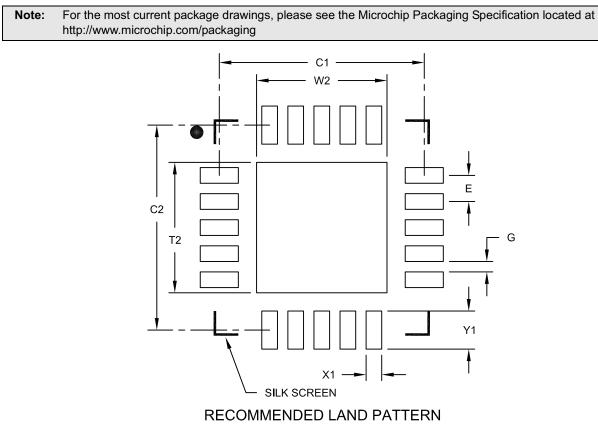

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1618-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-2: PIC16(L)F1614 MEMORY MAP, BANK 0-7

|      | BANK 0                        |              | BANK 1                        |              | BANK 2                        |              | BANK 3                        |              | BANK 4                        |              | BANK 5                        |       | BANK 6                        |        | BANK 7                        |

|------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|-------|-------------------------------|--------|-------------------------------|

| 000h | Core Registers<br>(Table 3-1) | 080h         | Core Registers<br>(Table 3-1) | 100h         | Core Registers<br>(Table 3-1) | 180h         | Core Registers<br>(Table 3-1) | 200h         | Core Registers<br>(Table 3-1) | 280h         | Core Registers<br>(Table 3-1) | 300h  | Core Registers<br>(Table 3-1) | 380h   | Core Registers<br>(Table 3-1) |

| 00Bh |                               | 08Bh         |                               | 10Bh         |                               | 18Bh         |                               | 20Bh         |                               | 28Bh         |                               | 30Bh  |                               | 38Bh   |                               |

| 00Ch | PORTA                         | 08Ch         | TRISA                         | 10Ch         | LATA                          | 18Ch         | ANSELA                        | 20Ch         | WPUA                          | 28Ch         | ODCONA                        | 30Ch  | SLRCONA                       | 38Ch   | INLVLA                        |

| 00Dh |                               | 08Dh         |                               | 10Dh         |                               | 18Dh         |                               | 20Dh         |                               | 28Dh         |                               | 30Dh  |                               | 38Dh   |                               |

| 00Eh | PORTC                         | 08Eh         | TRISC                         | 10Eh         | LATC                          | 18Eh         | ANSELC                        | 20Eh         | WPUC                          | 28Eh         | ODCONC                        | 30Eh  | SLRCONC                       | 38Eh   | INLVLC                        |

| 00Fh |                               | 08Fh         |                               | 10Fh         | _                             | 18Fh         | _                             | 20Fh         | _                             | 28Fh         | _                             | 30Fh  | —                             | 38Fh   | —                             |

| 010h | PIR1                          | 090h         | PIE1                          | 110h         |                               | 190h         |                               | 210h         | —                             | 290h         |                               | 310h  | _                             | 390h   | _                             |

| 011h | PIR2                          | 091h         | PIE2                          | 111h         | CM1CON0                       | 191h         | PMADRL                        | 211h         | SSP1BUF                       | 291h         | CCP1RL                        | 311h  | —                             | 391h   | IOCAP                         |

| 012h | PIR3                          | 092h         | PIE3                          | 112h         | CM1CON1                       | 192h         | PMADRH                        | 212h         | SSP1ADD                       | 292h         | CCP1RH                        | 312h  | —                             | 392h   | IOCAN                         |

| 013h | PIR4                          | 093h         | PIE4                          | 113h         | CM2CON0                       | 193h         | PMDATL                        | 213h         | SSP1MSK                       | 293h         | CCP1CON                       | 313h  | —                             | 393h   | IOCAF                         |

| 014h | PIR5                          | 094h         | PIE5                          | 114h         | CM2CON1                       | 194h         | PMDATH                        | 214h         | SSP1STAT                      | 294h         | CCP1CAP                       | 314h  | —                             | 394h   | _                             |

| 015h | TMR0                          | 095h         | OPTION_REG                    | 115h         | CMOUT                         | 195h         | PMCON1                        | 215h         | SSP1CON                       | 295h         | _                             | 315h  | —                             | 395h   |                               |

| 016h | TMR1L                         | 096h         | PCON                          | 116h         | BORCON                        | 196h         | PMCON2                        | 216h         | SSP1CON2                      | 296h         | —                             | 316h  | _                             | 396h   | —                             |

| 017h | TMR1H                         | 097h         | —                             | 117h         | FVRCON                        | 197h         | VREGCON                       | 217h         | SSP1CON3                      | 297h         | _                             | 317h  | —                             | 397h   | IOCCP                         |

| 018h | T1CON                         | 098h         | OSCTUNE                       | 118h         | DAC1CON0                      | 198h         | —                             | 218h         | —                             | 298h         | CCP2RL                        | 318h  | —                             | 398h   | IOCCN                         |

| 019h | T1GCON                        | 099h         | OSCCON                        | 119h         | DAC1CON1                      | 199h         | RC1REG                        | 219h         | —                             | 299h         | CCP2RH                        | 319h  | —                             | 399h   | IOCCF                         |

| 01Ah | TMR2                          | 09Ah         | OSCSTAT                       | 11Ah         | —                             | 19Ah         | TX1REG                        | 21Ah         | —                             | 29Ah         | CCP2CON                       | 31Ah  | —                             | 39Ah   | —                             |

| 01Bh | PR2                           | 09Bh         | ADRESL                        | 11Bh         | —                             | 19Bh         | SP1BRGL                       | 21Bh         | —                             | 29Bh         | CCP2CAP                       | 31Bh  | _                             | 39Bh   |                               |

| 01Ch | T2CON                         | 09Ch         | ADRESH                        | 11Ch         | ZCD1CON                       | 19Ch         | SP1BRGH                       | 21Ch         | —                             | 29Ch         | —                             | 31Ch  | _                             | 39Ch   |                               |

| 01Dh | T2HLT                         | 09Dh         | ADCON0                        | 11Dh         | _                             | 19Dh         | RC1STA                        | 21Dh         | —                             | 29Dh         | _                             | 31Dh  | _                             | 39Dh   | _                             |

| 01Eh | T2CLKCON                      | 09Eh         | ADCON1                        | 11Eh         | _                             | 19Eh         | TX1STA                        | 21Eh         |                               | 29Eh         | CCPTMRS                       | 31Eh  | _                             | 39Eh   |                               |

| 01Fh | T2RST                         | 09Fh         | ADCON2                        | 11Fh         |                               | 19Fh         | BAUD1CON                      | 21Fh         | _                             | 29Fh         | _                             | 31Fh  | _                             | 39Fh   |                               |

| 020h |                               | 0A0h         |                               | 120h         |                               | 1A0h         |                               | 220h         |                               | 2A0h         |                               | 320h  | General Purpose<br>Register   | 3A0h   |                               |

|      |                               |              | General                       | 32Fh  | 16 Bytes                      |        |                               |

|      |                               |              | Purpose                       | 330h  |                               |        | Unimplemented                 |

|      | General                       |              | Register<br>80 Bytes          | 00011 | Unimplemented                 |        | Read as '0'                   |

|      | Purpose                       |              | oo bytes                      |       | Read as '0'                   |        |                               |

|      | Register<br>96 Bytes          | 0EFh         |                               |              |                               |              |                               | 005          |                               | 0            |                               | 36Fh  |                               | 3EFh   |                               |

|      | 00 Dy(00                      | 0EFn<br>0F0h |                               | 16Fh<br>170h |                               | 1EFh<br>1F0h |                               | 26Fh<br>270h |                               | 2EFh<br>2F0h |                               |       |                               | 3F0h   |                               |

|      |                               | 01.011       | Common RAM                    | 17011        | Common RAM                    | 11.011       | Common RAM                    | 21011        | Common RAM                    | 21.011       | Common RAM                    | 370h  | A                             | 51 011 | Common RAM                    |

|      |                               |              | (Accesses                     |       | Accesses<br>70h – 7Fh         |        | (Accesses                     |

| 0755 |                               | OFER         | 70h – 7Fh)                    | 175h         | 70h – 7Fh)                    | 1556         | 70h – 7Fh)                    | 27Eh         | 70h – 7Fh)                    | 2FFh         | 70h – 7Fh)                    | 27Eb  | / /                           | 255h   | 70h – 7Fh)                    |

| 07Fh |                               | 0FFh         |                               | 17Fh         |                               | 1FFh         |                               | 27Fh         |                               | ∠⊢⊢n         |                               | 37Fh  |                               | 3FFh   |                               |

**Legend:** = Unimplemented data memory locations, read as '0'.

# 7.6 Register Definitions: Interrupt Control

| R/W-0/0            | R/W-0/0                                                       | R/W-0/0                                                     | R/W-0/0              | R/W-0/0         | R/W-0/0           | R/W-0/0          | R-0/0                |

|--------------------|---------------------------------------------------------------|-------------------------------------------------------------|----------------------|-----------------|-------------------|------------------|----------------------|

| GIE <sup>(1)</sup> | PEIE <sup>(2)</sup>                                           | TMR0IE                                                      | INTE                 | IOCIE           | TMR0IF            | INTF             | IOCIF <sup>(3)</sup> |

| oit 7              | ·                                                             |                                                             |                      |                 |                   |                  | bit (                |

|                    |                                                               |                                                             |                      |                 |                   |                  |                      |

| Legend:            |                                                               |                                                             |                      |                 |                   |                  |                      |

| R = Readal         | ole bit                                                       | W = Writable                                                | bit                  | U = Unimpler    | mented bit, read  | l as '0'         |                      |

| u = Bit is ur      | 0                                                             | x = Bit is unkı                                             |                      | -n/n = Value a  | at POR and BO     | R/Value at all o | ther Resets          |

| 1' = Bit is s      | et                                                            | '0' = Bit is cle                                            | ared                 |                 |                   |                  |                      |

| oit 7              | GIE: Global                                                   | Interrupt Enable                                            | e bit <sup>(1)</sup> |                 |                   |                  |                      |

|                    | 0 = Disables                                                  | all active interru<br>all interrupts                        |                      |                 |                   |                  |                      |

| oit 6              | 1 = Enables                                                   | neral Interrupt E<br>all active periph<br>all peripheral ir | neral interrupts     | 6               |                   |                  |                      |

| oit 5              | 1 = Enables                                                   | ner0 Overflow Ir<br>the Timer0 inter<br>the Timer0 inter    | rrupt                | e bit           |                   |                  |                      |

| oit 4              | 1 = Enables                                                   | xternal Interrupt<br>the INT externa<br>the INT externa     | l interrupt          |                 |                   |                  |                      |

| oit 3              | 1 = Enables                                                   | upt-on-Change<br>the interrupt-on<br>the interrupt-or       | -change              |                 |                   |                  |                      |

| oit 2              | 1 = TMR0 re                                                   | ner0 Overflow Ir<br>gister has overf<br>gister did not ov   | lowed                | it              |                   |                  |                      |

| oit 1              | 1 = The INT                                                   | kternal Interrupt<br>external interru<br>external interru   | pt occurred          | ır              |                   |                  |                      |

| oit O              | 1 = When at                                                   | upt-on-Change<br>least one of the<br>the interrupt-on       | e interrupt-on-o     | change pins ch  |                   |                  |                      |

| Note 1:            | Interrupt flag bits<br>enable bit or the<br>appropriate inter | Global Interrupt                                            | Enable bit, G        | IE of the INTCO | ON register. Use  |                  |                      |

| 2:                 | Bit PEIE of the I                                             | NTCON register                                              | must be set t        | o enable any p  | eripheral interru | upt.             |                      |

| 3:                 | The IOCIF Flag                                                | -                                                           |                      |                 |                   |                  |                      |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

# 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 32 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 11 bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:4>) with the lower four bits of PMADRL, (PMADRL<7:0) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

| Note: | The special unlock sequence is required to load a write latch with data or initiate a |

|-------|---------------------------------------------------------------------------------------|

|       | Flash programming operation. If the                                                   |

|       | unlock sequence is interrupted, writing to                                            |

|       | the latches or program memory will not be                                             |

|       | initiated.                                                                            |

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the Blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

| R/W-0/0           |                                        | R-0                       | R-0                                                | R/W-0/0                | U-0                        | R/W-0/0       | R/W-0/0          |

|-------------------|----------------------------------------|---------------------------|----------------------------------------------------|------------------------|----------------------------|---------------|------------------|

| EN <sup>(1)</sup> | SCANGO <sup>(2, 3)</sup>               | BUSY <sup>(4)</sup>       | INVALID                                            | INTM                   |                            | MODE          | <1:0> <b>(5)</b> |

| bit 7             |                                        |                           |                                                    |                        |                            |               | bit 0            |

| Legend:           |                                        |                           |                                                    |                        |                            |               |                  |

| R = Readal        | hle hit                                | W = Writable              | hit                                                | U = Unimpler           | mented bit, read           | 1 as '0'      |                  |

| u = Bit is ur     |                                        | x = Bit is unk            |                                                    | •                      | at POR and BO              |               | other Resets     |

| '1' = Bit is s    | 0                                      | '0' = Bit is cle          |                                                    |                        | eared by hardw             |               |                  |

|                   |                                        |                           |                                                    |                        |                            |               |                  |

| bit 7             | EN: Scanner                            | Enable bit <sup>(1)</sup> |                                                    |                        |                            |               |                  |

|                   | 1 = Scanner is                         |                           |                                                    |                        |                            |               |                  |

| 1.1.0             |                                        |                           | ernal states are                                   | e reset                |                            |               |                  |

| bit 6             | SCANGO: Sc                             |                           |                                                    |                        |                            |               |                  |

|                   |                                        | ent peripheral.           | i ready signal,                                    | NVIVI WIII De ac       | ccessed accord             | ing to MDx an | d data passed    |

|                   | 0 = Scanner o                          |                           | not occur                                          |                        |                            |               |                  |

| bit 5             | BUSY: Scann                            | er Busy Indica            | ator bit <sup>(4)</sup>                            |                        |                            |               |                  |

|                   | 1 = Scanner o                          | ycle is in proc           | ess                                                |                        |                            |               |                  |

|                   | 0 = Scanner o                          | cycle is comple           | ete (or never st                                   | arted)                 |                            |               |                  |

| bit 4             | INVALID: Sca                           | -                         |                                                    |                        | <i>(</i> <b>-</b> )        |               |                  |

|                   |                                        |                           | remented or co<br>o a valid addre                  | ontains an inva<br>ess | lid address <sup>(6)</sup> |               |                  |

| bit 3             |                                        |                           | ipt Manageme                                       | nt Mode Select         | t bit                      |               |                  |

|                   | If MODE = 10:                          |                           |                                                    |                        |                            |               |                  |

|                   | This bit is igno                       |                           |                                                    |                        |                            |               |                  |

|                   |                                        | •                         | <u>d until all data is</u>                         |                        |                            |               |                  |

|                   |                                        | is overridden             | (to zero) during                                   | g interrupt oper       | ration; scanner            | resumes after | returning from   |

|                   | interrupt<br>0 = SCANGO                | is not affected           | d bv interrupts.                                   | the interrupt re       | esponse will be            | affected      |                  |

|                   | If MODE = 00                           |                           | · · <b>,</b> · · · · · · · · · · · · · · · · · · · |                        |                            |               |                  |

|                   | 1 = SCANGO<br>from inter               |                           | (to zero) during                                   | interrupt opera        | ation; scan oper           | ations resume | after returning  |

|                   |                                        |                           | t NVM access                                       |                        |                            |               |                  |

| bit 2             | Unimplement                            | ted: Read as              | 0'                                                 |                        |                            |               |                  |

| bit 1-0           | MODE<1:0>:                             | Memory Acce               | ess Mode bits <sup>(5</sup>                        | )                      |                            |               |                  |

|                   | 11 = Triggere                          | d mode                    |                                                    |                        |                            |               |                  |

|                   | 10 = Peek mo                           |                           |                                                    |                        |                            |               |                  |

|                   | 01 = Burst mo<br>00 = Concurre         |                           |                                                    |                        |                            |               |                  |

| Note 1:           | Setting EN = 0 (SC                     | CANCON0 red               | ister) does not                                    | affect any othe        | er register conte          | ent.          |                  |

|                   | This bit is cleared                    | -                         |                                                    | -                      | -                          |               |                  |

|                   | If INTM = 1, this bi                   |                           | -                                                  | -                      |                            | response.     |                  |

|                   | BUSY = 1 when th                       |                           | •                                                  |                        | •                          | •             |                  |

| 5: 3              | See Table 11-1 for                     | more detailed             | information.                                       |                        |                            |               |                  |

| I                 | An invalid address<br>memory is 0x4000 |                           |                                                    |                        |                            |               |                  |

# REGISTER 11-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

address is invalid.

| U-0                                     | R/W-x/u           | R/W-x/u                                                          | R/W-x/u                                               | R/W-x/u                                                                                                                         | R/W-x/u                                                                                                                                                                                 | R/W-x/u                                                                                                                       |  |

|-----------------------------------------|-------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| —                                       | LATA5             | LATA4                                                            | LATA3                                                 | LATA2                                                                                                                           | LATA1                                                                                                                                                                                   | LATA0                                                                                                                         |  |

|                                         |                   |                                                                  |                                                       |                                                                                                                                 |                                                                                                                                                                                         | bit 0                                                                                                                         |  |

|                                         |                   |                                                                  |                                                       |                                                                                                                                 |                                                                                                                                                                                         |                                                                                                                               |  |

|                                         |                   |                                                                  |                                                       |                                                                                                                                 |                                                                                                                                                                                         |                                                                                                                               |  |

| oit                                     | W = Writable      | bit                                                              | U = Unimplemented bit, read as '0'                    |                                                                                                                                 |                                                                                                                                                                                         |                                                                                                                               |  |

| u = Bit is unchanged x = Bit is unknown |                   |                                                                  | -n/n = Value at POR and BOR/Value at all other Resets |                                                                                                                                 |                                                                                                                                                                                         |                                                                                                                               |  |

|                                         | '0' = Bit is clea | ared                                                             |                                                       |                                                                                                                                 |                                                                                                                                                                                         |                                                                                                                               |  |

|                                         | Dit               | LATA5       Dit     W = Writable       anged     x = Bit is unkr | LATA5     LATA4       Dit     W = Writable bit        | LATA5     LATA4     LATA3       Dit     W = Writable bit     U = Unimpler       anged     x = Bit is unknown     -n/n = Value a | LATA5       LATA4       LATA3       LATA2         Dit       W = Writable bit       U = Unimplemented bit, read         anged       x = Bit is unknown       -n/n = Value at POR and BOI | —LATA5LATA4LATA3LATA2LATA1DitW = Writable bitU = Unimplemented bit, read as '0'<br>-n/n = Value at POR and BOR/Value at all c |  |

#### REGISTER 12-3: LATA: PORTA DATA LATCH REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LATA<5:0>: RA<5:0> Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|---------|-----|---------|---------|---------|

| —     | —   | _   | ANSA4   | _   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ANSA4: Analog Select between Analog or Digital Function on Pins RA4, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                    |

| bit 2-0 | <b>ANSA&lt;2:0&gt;</b> : Analog Select between Analog or Digital Function on Pins RA<2:0>, respectively<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> . Digital input buffer disabled.<br>0 = Digital I/O. Pin is assigned to port or digital special function.         |

| Note 1: | When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.                                                                                                                                     |

| R/W-0/0               | R/W-0/0                                        | R/W-0/0                  | R/W-0/0          | R/W-0/0        | U-0              | U-0              | U-0          |  |  |  |  |

|-----------------------|------------------------------------------------|--------------------------|------------------|----------------|------------------|------------------|--------------|--|--|--|--|

|                       | Т                                              | [RIGSEL<4:0>(1           | 1)               |                | —                | —                | —            |  |  |  |  |

| bit 7                 |                                                |                          |                  |                |                  |                  | bit (        |  |  |  |  |

|                       |                                                |                          |                  |                |                  |                  |              |  |  |  |  |

| Legend:<br>R = Readab | alo hit                                        | W = Writable             | bit              | II – Unimplor  | nonted hit read  | d ac 'O'         |              |  |  |  |  |

|                       |                                                |                          |                  | -              | nented bit, read |                  | ther Decete  |  |  |  |  |

| u = Bit is un         | •                                              | x = Bit is unki          |                  |                | at POR and BC    | R/Value at all o | Juner Resels |  |  |  |  |

| '1' = Bit is s        | et                                             | '0' = Bit is cle         | ared             |                |                  |                  |              |  |  |  |  |

|                       |                                                |                          | · <b>·</b> ·     | 0.1            | <b>`</b>         |                  |              |  |  |  |  |

| bit 7-3               |                                                | I:0>: Auto-Conv          | ersion Trigger   | Selection bits | ,                |                  |              |  |  |  |  |

|                       | 11111 = Re                                     | eserved                  |                  |                |                  |                  |              |  |  |  |  |

|                       | •                                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | •                                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 10101 <b>= Re</b>                              | served                   |                  |                |                  |                  |              |  |  |  |  |

|                       | 10100 <b>= AT</b>                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 10011 <b>= AT</b>                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 10010 <b>= AT</b>                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 10001 = CL<br>10000 = CL                       |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 01111 = CL                                     |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 01110 = CL                                     |                          |                  |                |                  |                  |              |  |  |  |  |

|                       |                                                | IR5_overflow             |                  |                |                  |                  |              |  |  |  |  |

|                       |                                                | 1R3_overflow             |                  |                |                  |                  |              |  |  |  |  |

|                       | 01011 = SM                                     |                          |                  |                |                  |                  |              |  |  |  |  |

|                       |                                                | 01010 =SMT1_match        |                  |                |                  |                  |              |  |  |  |  |

|                       | $01001 = TMR6_postscaled$                      |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 01000 = TMR4_postscaled<br>00111 = C2_OUT_sync |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | $00110 = C1_OUT_sync$                          |                          |                  |                |                  |                  |              |  |  |  |  |

|                       |                                                | IR2_postscaled           |                  |                |                  |                  |              |  |  |  |  |

|                       | 00100 <b>= T1</b>                              | _overflow <sup>(2)</sup> |                  |                |                  |                  |              |  |  |  |  |

|                       | 00011 <b>= TO</b>                              |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 00010 = CC                                     |                          |                  |                |                  |                  |              |  |  |  |  |

|                       | 00001 = CC                                     |                          | n trigger ecles  | atad           |                  |                  |              |  |  |  |  |

|                       |                                                | auto-conversio           |                  | lea            |                  |                  |              |  |  |  |  |

| bit 2-0               | Unimpleme                                      | nted: Read as '          | 0.               |                |                  |                  |              |  |  |  |  |

| Note 1: 7             | This is a rising e                             | dge sensitive inp        | out for all sour | ces.           |                  |                  |              |  |  |  |  |

| 2.                    | Signal also sets i                             | its correspondin         | a interrunt flag | r              |                  |                  |              |  |  |  |  |

## REGISTER 17-3: ADCON2: ADC CONTROL REGISTER 2

2: Signal also sets its corresponding interrupt flag.

## 17.4 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 17-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 17-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 17-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 17-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature = 50°C and external impedance of 10k

$$\Omega$$

5.0V VDD

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

= 2µs + TC + [(Temperature - 25°C)(0.05µs/°C)]

The value for TC can be approximated with the following equations:

$$VAPPLIED\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = VCHOLD \qquad ;[1] VCHOLD charged to within 1/2 lsb$$

$$VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = VCHOLD \qquad ;[2] VCHOLD charge response to VAPPLIED$$

$$VAPPLIED\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

Note: Where n = number of bits of the ADC.

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$$$

$$= -12.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

= 1.12µs

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.37\mu s

Note 1: The reference voltage (VRPOS) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

#### 23.5.7 EDGE-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

In Edge-Triggered Hardware Limit One-Shot modes the timer starts on the first external signal edge after the ON bit is set and resets on all subsequent edges. Only the first edge after the ON bit is set is needed to start the timer. The counter will resume counting automatically two clocks after all subsequent external Reset edges. Edge triggers are as follows:

- Rising edge start and Reset (MODE<4:0> = 01100)

- Falling edge start and Reset (MODE<4:0> = 01101)

The timer resets and clears the ON bit when the timer value matches the PRx period value. External signal edges will have no effect until after software sets the ON bit. Figure 23-10 illustrates the rising edge hardware limit one-shot operation.

When this mode is used in conjunction with the CCP then the first starting edge trigger, and all subsequent Reset edges, will activate the PWM drive. The PWM drive will deactivate when the timer matches the CCPRx pulse-width value and stay deactivated until the timer halts at the PRx period match unless an external signal edge resets the timer before the match occurs.

#### 23.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the PRx value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

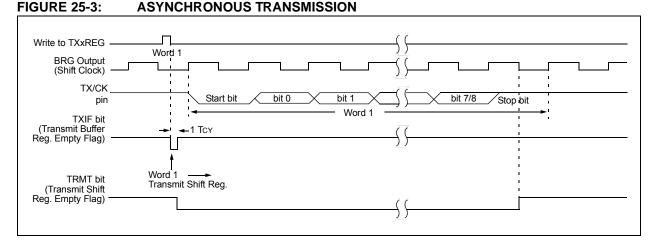

#### 25.1.1.5 TSR Status

The TRMT bit of the TXxSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXxREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 25.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXxSTA register is set, the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXxSTA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXxREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXxREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 25.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 25.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPxBRGH, SPxBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TXxREG register. This will start the transmission.

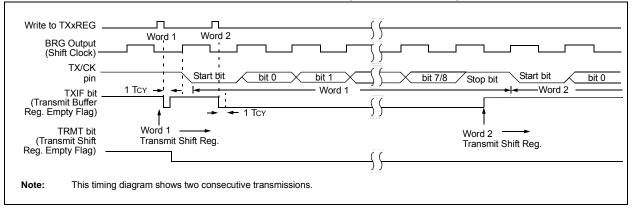

#### FIGURE 25-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

#### TABLE 25-3: BAUD RATE FORMULAS

| (    | Configuration Bi | ts   |                     | Baud Rate Formula |

|------|------------------|------|---------------------|-------------------|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Kate Formula |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0                | 1    | 8-bit/Asynchronous  |                   |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1                | 1    | 16-bit/Asynchronous |                   |

| 1    | 0                | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1                | х    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPxBRGH, SPxBRGL register pair.

#### TABLE 25-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-----------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUD1CON | ABDOVF    | RCIDL |       | SCKP  | BRG16 |       | WUE   | ABDEN | 323                 |

| RC1STA   | SPEN      | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 322                 |

| SP1BRGL  | BRG<7:0>  |       |       |       |       |       |       | 324   |                     |

| SP1BRGH  | BRG<15:8> |       |       |       |       |       | 324   |       |                     |

| TX1STA   | CSRC      | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 321                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

# 25.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 25.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCxREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 25.5.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCxSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCxREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

# TABLE 25-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4                      | Bit 3      | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|----------------------------|------------|------------|--------|--------|---------------------|

| ANSELA                |                       | _                     |        | ANSA4                      | _          | ANSA2      | ANSA1  | ANSA0  | 152                 |

| ANSELB <sup>(1)</sup> | —                     | _                     | ANSB5  | ANSB4                      | _          | _          | _      | —      | 159                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | _      |                            | ANSC3      | ANSC2      | ANSC1  | ANSC0  | 166                 |

| BAUD1CON              | ABDOVF                | RCIDL                 | _      | SCKP                       | BRG16      | —          | WUE    | ABDEN  | 323                 |

| CKPPS                 | —                     | _                     | —      |                            | CKPPS<4:0> |            |        |        | 174, 172            |

| INTCON                | GIE                   | PEIE                  | TMR0IE | INTE                       | IOCIE      | TMR0IF     | INTF   | IOCIF  | 97                  |

| PIE1                  | TMR1GIE               | ADIE                  | RCIE   | TXIE                       | SSP1IE     | CCP1IE     | TMR2IE | TMR1IE | 98                  |

| PIR1                  | TMR1GIF               | ADIF                  | RCIF   | TXIF                       | SSP1IF     | CCP1IF     | TMR2IF | TMR1IF | 103                 |

| RC1REG                |                       |                       | EUS    | SART Receive Data Register |            |            |        | 316*   |                     |

| RC1STA                | SPEN                  | RX9                   | SREN   | CREN                       | ADDEN      | FERR       | OERR   | RX9D   | 322                 |

| RXPPS                 | —                     | _                     | —      |                            |            | RXPPS<4:0> |        |        | 174, 172            |

| TRISA                 | _                     | _                     | TRISA5 | TRISA4                     | (2)        | TRISA2     | TRISA1 | TRISA0 | 151                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4                     | _          |            | _      | _      | 158                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4                     | TRISC3     | TRISC2     | TRISC1 | TRISC0 | 165                 |

| TX1STA                | CSRC                  | TX9                   | TXEN   | SYNC                       | SENDB      | BRGH       | TRMT   | TX9D   | 321                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

\* Page provides register information.

Note 1: PIC16(L)F1618 only.

2: Unimplemented, read as '1'.

#### 26.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section22.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 26.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (MODE<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 26.2.4 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 26.2.5 CAPTURE OUTPUT

When in Compare mode, the CCP will provide an output upon the 16-bit value of the CCPRxH:CCPRxL register pair matching the TMR1H:TMR1L register pair. The compare output depends on which Compare mode the CCP is configured as. If the MODE bits of CCPxCON register are equal to '1011' or '1010', the CCP module will output high, while TMR1 is equal to CCPRxH:CCPRxL register pair. This means that the pulse width is determined by the TMR1 prescaler. If the MODE bits of CCPxCON are equal to '0001' or '0010', the output will toggle upon a match, going from '0' to '1' or vice-versa. If the MODE bits of CCPxCON are equal to '1001', the output is cleared on a match, and if the MODE bits are equal to '1000', the output is set on a match. This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an external Reset signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module. In addition, the CCPx pin output can be mapped to output pins through the use of PPS (see Section13.2 "PPS Outputs").

PIC16(L)F1614/8

|                   |                   | Rev. 10-000188A<br>4/222016 |

|-------------------|-------------------|-----------------------------|

| SMTxWIN           |                   |                             |

| SMTxWIN_sync      |                   |                             |

| SMTx_signal       |                   |                             |

| SMTx_signalsync   |                   |                             |

|                   |                   |                             |

| SMTxEN            |                   |                             |

| SMTxGO            |                   |                             |

| SMTxGO_sync       |                   | i                           |

| SMTxTMR 0 1 2 3 4 | 5 (1)(2)(3)(4)(5) |                             |

| SMTxCPW           |                   | 13                          |

| SMTxCPR           | 4                 |                             |

| SMTxPWAIF         |                   |                             |

| SMTxPRAIF         |                   |                             |

# REGISTER 30-2: SMTxCON1: SMT CONTROL REGISTER 1

| R/W/HC-0/0       | R/W-0/0                                                                                                                                   | U-0                                                                                                                                              | U-0            | R/W-0/0        | R/W-0/0         | R/W-0/0         | R/W-0/0      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|-----------------|-----------------|--------------|

| SMTxGO           | REPEAT                                                                                                                                    | _                                                                                                                                                | —              |                | MODE            | E<3:0>          |              |

| bit 7            |                                                                                                                                           |                                                                                                                                                  |                |                |                 |                 | bit (        |

| Legend:          |                                                                                                                                           |                                                                                                                                                  |                |                |                 |                 |              |

| HC = Bit is cle  | ared by hardw                                                                                                                             | vare                                                                                                                                             |                | HS = Bit is se | et by hardware  |                 |              |

| R = Readable     | •                                                                                                                                         | W = Writable                                                                                                                                     | hit            |                | nented bit, rea | d as '0'        |              |

| u = Bit is unch  |                                                                                                                                           | x = Bit is unkr                                                                                                                                  |                |                |                 | DR/Value at all | other Resets |

| '1' = Bit is set | ungeu                                                                                                                                     | '0' = Bit is clea                                                                                                                                |                |                | pends on condi  |                 |              |

| i Bit io oot     |                                                                                                                                           |                                                                                                                                                  |                | y value dep    |                 |                 |              |

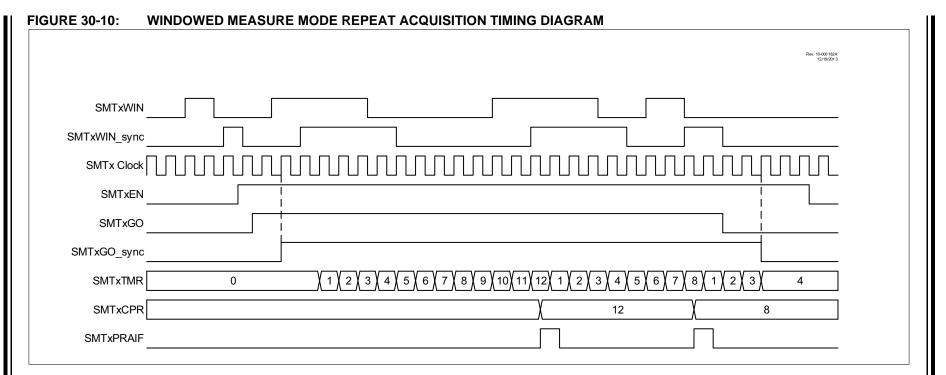

| bit 7            | 1 = Increme                                                                                                                               | MT GO Data Ac<br>nting, acquiring<br>nting, acquiring                                                                                            | data is enable |                |                 |                 |              |

| bit 6            | <b>REPEAT:</b> SMT Repeat Acquisition Enable bit<br>1 = Repeat Data Acquisition mode is enabled<br>0 = Single Acquisition mode is enabled |                                                                                                                                                  |                |                |                 |                 |              |

| bit 5-4          | Unimpleme                                                                                                                                 | nted: Read as '                                                                                                                                  | כ'             |                |                 |                 |              |

| bit 3-0          | MODE<3:0><br>1111 = Rese                                                                                                                  | <ul> <li>SMT Operation</li> <li>erved</li> </ul>                                                                                                 | Node Select    | t bits         |                 |                 |              |

|                  | 1001 = Gate<br>1000 = Cour<br>0111 = Capt<br>0110 = Time<br>0101 = Gate<br>0100 = Wind<br>0011 = High                                     | dowed counter<br>ed counter<br>nter<br>ture<br>e of flight<br>ed windowed me<br>dowed measure<br>a and low time m<br>od and Duty-Cyc<br>ed Timer | easurement     | ı              |                 |                 |              |

| SUBLW            | Subtract W from literal                                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                           |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                |  |  |  |  |

| Operation:       | $k - (W) \to (W)$                                                                                                                  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                           |  |  |  |  |

| Description:     | The W register is subtracted (2's com-<br>plement method) from the 8-bit literal 'k'. The result is placed in the W regis-<br>ter. |  |  |  |  |

|                  | C = 0 W > k                                                                                                                        |  |  |  |  |

|                  | $C = 1$ $W \le k$                                                                                                                  |  |  |  |  |

DC = 0

DC = 1

| SUBWF      | Subtract W from f                     |

|------------|---------------------------------------|

| Syntax:    | [label] SUBWF f,d                     |

| Operands:  | $0 \le f \le 127$<br>$d \in [0,1]$    |

| Operation: | (f) - (W) $\rightarrow$ (destination) |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description:     | Subtract (2's complement method) W<br>register from register 'f'. If 'd' is '0', the<br>result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f. |

| <b>C =</b> 0 | W > f           |

|--------------|-----------------|

| <b>C =</b> 1 | $W \leq f$      |

| DC = 0       | W<3:0> > f<3:0> |

| DC = 1       | W<3:0> ≤ f<3:0> |

W<3:0> > k<3:0>

$W<3:0> \le k<3:0>$

| SUBWFB           | Subtract W from f with Borrow                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | SUBWFB f {,d}                                                                                                                                                                                       |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                  |

| Operation:       | $(f) - (W) - (\overline{B}) \rightarrow dest$                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                            |

| Description:     | Subtract W and the BORROW flag<br>(CARRY) from register 'f' (2's comple-<br>ment method). If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                |