Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1618-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                | Function | Input<br>Type                          | Output<br>Type | Description                             |

|---------------------------------------------------------------------|----------|----------------------------------------|----------------|-----------------------------------------|

| RC1/AN5/C1IN1-/C2IN1-/                                              | RC1      | TTL/ST                                 | CMOS/OD        | General purpose I/O.                    |

| T4IN <sup>(1)</sup> /SMTSIG2 <sup>(1)</sup> /SDI <sup>(1)</sup>     | AN5      | AN                                     | _              | ADC Channel input.                      |

|                                                                     | C1IN1-   | AN                                     | _              | Comparator negative input.              |

|                                                                     | C2IN1-   | C2IN1- AN — Comparator negative input. |                | Comparator negative input.              |

|                                                                     | T4IN     | T4IN TTL/ST — Timer4 input.            |                | Timer4 input.                           |

|                                                                     | SMTSIG2  | TTL/ST                                 | _              | SMT2 signal input.                      |

|                                                                     | CLCIN2   | ST                                     | _              | Configurable Logic Cell source input.   |

|                                                                     | SDI      | CMOS                                   | _              | SPI data input.                         |

| RC2/AN6/C1IN2-/C2IN2-                                               | RC2      | TTL/ST                                 | CMOS/OD        | General purpose I/O.                    |

|                                                                     | AN6      | AN                                     | —              | ADC Channel input.                      |

|                                                                     | C1IN2-   | AN                                     | —              | Comparator negative input.              |

|                                                                     | C2IN2-   | AN                                     | —              | Comparator negative input.              |

| RC3/AN7/C1IN3-/C2IN3-/T5G <sup>(1)</sup> /                          | RC3      | TTL/ST                                 | —              | General purpose input with IOC and WPU. |

| CCP2 <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> /ATCC <sup>(1)</sup> /SS | AN7      | AN                                     | —              | ADC Channel input.                      |

|                                                                     | C1IN3-   | AN                                     | —              | Comparator negative input.              |

|                                                                     | C2IN3-   | AN                                     | —              | Comparator negative input.              |

|                                                                     | T5G      | ST                                     | —              | Timer5 Gate input.                      |

|                                                                     | CCP2     | TTL/ST                                 | CMOS/OD        | Capture/Compare/PWM2.                   |

|                                                                     | CLCIN0   | ST                                     | —              | Configurable Logic Cell source input.   |

|                                                                     | ATCC     | ST                                     | —              | Angular Timer Capture/Compare input.    |

|                                                                     | SS       | ST                                     | —              | Slave Select input.                     |

| RC4/T3G <sup>(1)</sup> /CLCIN1 <sup>(1)</sup> /CK <sup>(1)</sup> /  | RC4      | TTL/ST                                 | CMOS/OD        | General purpose I/O.                    |

| HIC4                                                                | T3G      | TTL/ST                                 | —              | Timer3 Gate input.                      |

|                                                                     | CLCIN1   | ST                                     | —              | Configurable Logic Cell source input.   |

|                                                                     | СК       | ST                                     | CMOS           | USART synchronous clock.                |

|                                                                     | HIC4     | TTL                                    | CMOS           | High Current I/O.                       |

| RC5/T3CKI <sup>(1)</sup> /CCP1 <sup>(1)</sup> /RX <sup>(1)</sup> /  | RC5      | TTL/ST                                 | CMOS/OD        | General purpose I/O.                    |

| ATIN <sup>(1)</sup> /HIC5                                           | T3CKI    | TTL/ST                                 | _              | Timer3 clock input.                     |

|                                                                     | CCP1     | TTL/ST                                 | CMOS/OD        | Capture/Compare/PWM1.                   |

|                                                                     | RX       | ST                                     | —              | USART asynchronous input.               |

|                                                                     | ATIN     | TTL/ST                                 | —              | Angular Timer clock input.              |

|                                                                     | HIC5     | TTL                                    | —              | High Current I/O.                       |

| Vdd                                                                 | Vdd      | Power                                  | —              | Positive supply.                        |

| Vss                                                                 | Vss      | Power                                  | _              | Ground reference.                       |

TABLE 1-2. PIC16(L)F1614 PINOUT DESCRIPTION (CONTINUED)

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C Schmitt Trigger input with I<sup>2</sup>C = HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection 2: registers. See Register 13-1.

### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

# 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled, will cause a software Reset. See section **Section 3.5** "**Stack**" for more details.

# 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

# 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 34.0** "Instruction Set Summary" for more details.

| Addr               | Name                 | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2       | Bit 1      | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|--------------------|----------------------|---------------|-------|-------|-------|--------|-------------|------------|-----------|----------------------|---------------------------|

| Bank               | Bank 12              |               |       |       |       |        |             |            |           |                      |                           |

| 60Ch               | PID1Z2L              |               |       |       | Z2<   | 7:0>   |             |            |           | 0000 0000            | 0000 0000                 |

| 60Dh               | PID1Z2H              |               |       |       | Z2<1  | 5:8>   |             |            |           | 0000 0000            | 0000 0000                 |

| 60Eh               | PID1Z2U              | —             | —     | —     | —     | —      | —           | —          | Z216      | 0                    | 0                         |

| 60Fh               | PID1ACCLL            |               |       |       | ACC   | <7:0>  |             |            |           | 0000 0000            | 0000 0000                 |

| 610h               | PID1ACCLH            |               |       |       | ACC<  | :15:8> |             |            |           | 0000 0000            | 0000 0000                 |

| 611h               | PID1ACCHL ACC<23:16> |               |       |       |       |        |             | 0000 0000  | 0000 0000 |                      |                           |

| 612h               | PID1ACCHH            | ACC<31:24>    |       |       |       |        | 0000 0000   | 0000 0000  |           |                      |                           |

| 613h               | PID1ACCU             | —             | —     | —     | —     | —      |             | ACC<34:32> |           | 000                  | 000                       |

| 614h               | PID1CON              | EN            | BUSY  | —     | —     | —      | — MODE<2:0> |            |           | 00 0000              | 00 0000                   |

| 615h               | _                    | Unimplemented | I     |       |       |        |             |            |           | —                    | —                         |

| 616h               | —                    | Unimplemented | I     |       |       |        |             |            |           | —                    | _                         |

| 617h               | PWM3DCL              | DC<           | :1:0> | —     | —     | —      | —           | —          | —         | xx                   | xx                        |

| 618h               | PWM3DCH              |               |       |       | DC<   | 9:2>   |             |            |           | xxxx xxxx            | xxxx xxxx                 |

| 619h               | PWM3CON              | EN            | —     | OUT   | POL   | —      | —           | —          | —         | 0-x0                 | 0-x0                      |

| 61Ah               | PWM4DCL              | DC<           | :1:0> | —     | —     | —      | —           | —          | —         | xx                   | xx                        |

| 61Bh               | PWM4DCH              | CH DC<9:2>    |       |       |       |        |             | xxxx xxxx  | xxxx xxxx |                      |                           |

| 61Ch               | PWM4CON              | EN            | —     | OUT   | POL   | —      | _           | _          | _         | 0-x0                 | 0-x0                      |

| 61Dh<br>to<br>61Fh | _                    | Unimplemented | 1     |       |       |        |             |            |           | _                    | _                         |

#### TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

#### Value on Value on all Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR. BOR other Resets Banks 15 78Ch Unimplemented to 790h 791h CRCDATL DAT<7:0> XXXX XXXX XXXX XXXX 792h CRCDATH DAT<15:8> XXXX XXXX XXXX XXXX ACC<7:0> 793h CRCACCL 0000 0000 0000 0000 794h CRCACCH ACC<15:8> 0000 0000 0000 0000 795h CRCSHIFTL SHIFT<7:0> 0000 0000 0000 0000 796h CRCSHIFTH SHIFT<15:8> 0000 0000 0000 0000 797h CRCXORL XOR<7:1> \_\_\_\_ XXXX XXXxxxx xxx-798h CRCXORH XOR<15:8> XXXX XXXX XXXX XXXX CRCCON0 CRCGO BUSY ACCM 799h ΕN \_ \_ SHIFTM FULL 0000 --00 0000 -00 DLEN<3:0> PLEN<3:0> 79Ah CRCCON1 0000 0000 0000 0000 79Bh Unimplemented to \_\_\_\_ \_\_\_\_ 79Fh

#### TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

#### 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

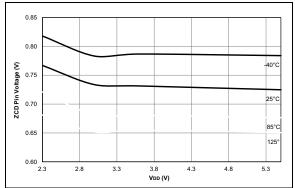

#### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|--|--|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready                                                 |  |  |  |  |  |

| 10         | Х      | Sleep       | Disabled | (BORRDY = 1)                                                        |  |  |  |  |  |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

|            | 0      | х           | Disabled | Begins immediately                                                  |  |  |  |  |  |

| 00         | Х      | Х           | Disabled | (BORRDY = x)                                                        |  |  |  |  |  |

TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 6.4 Low-Power Brown-Out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) operates like the BOR to detect low voltage conditions on the VDD pin. When too low of a voltage is detected, the device is held in Reset. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The BOR bit in PCON is used for both BOR and the LPBOR. Refer to Register 6-2.

The LPBOR voltage threshold (VLPBOR) has a wider tolerance than the BOR (VBOR), but requires much less current (LPBOR current) to operate. The LPBOR is intended for use when the BOR is configured as disabled (BOREN = 00) or disabled in Sleep mode (BOREN = 10).

Refer to Figure 6-1 to see how the LPBOR interacts with other modules.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

# 6.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

#### TABLE 6-2: MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

# 6.5.1 MCLR ENABLED

When  $\overline{\text{MCLR}}$  is enabled and the pin is held low, the device is held in Reset. The  $\overline{\text{MCLR}}$  pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

# Note: A Reset does not drive the MCLR pin low.

# 6.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section12.1** "**PORTA Registers**" for more information.

# 6.6 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section9.0 "Windowed Watchdog Timer (WDT)**" for more information.

# 6.7 **RESET Instruction**

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

# 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section3.5.2 "Overflow/Underflow Reset"** for more information.

# 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

# 6.10 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of Configuration Words.

# 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See **Section5.0** "Oscillator Module" for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 FOSC cycles (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

#### REGISTER 9-3: WDTPSL: WDT PRESCALE SELECT LOW BYTE REGISTER (READ ONLY)

| R-0/0              | R-0/0                                 | R-0/0            | R-0/0 | R-0/0             | R-0/0              | R-0/0             | R-0/0  |

|--------------------|---------------------------------------|------------------|-------|-------------------|--------------------|-------------------|--------|

|                    |                                       |                  | PSCN  | T<7:0> <b>(1)</b> |                    |                   |        |

| bit 7              |                                       |                  |       |                   |                    |                   | bit 0  |

|                    |                                       |                  |       |                   |                    |                   |        |

| Legend:            |                                       |                  |       |                   |                    |                   |        |

| R = Readable bit   |                                       | W = Writable bit |       | U = Unimpleme     | ented bit, read as | ʻ0'               |        |

| u = Bit is unchang | = Bit is unchanged x = Bit is unknown |                  |       |                   | POR and BOR/V      | alue at all other | Resets |

bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

'0' = Bit is cleared

'1' = Bit is set

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-4: WDTPSH: WDT PRESCALE SELECT HIGH BYTE REGISTER (READ ONLY)

| R-0/0             | R-0/0 | R-0/0                | R-0/0 | R-0/0                 | R-0/0              | R-0/0                | R-0/0  |

|-------------------|-------|----------------------|-------|-----------------------|--------------------|----------------------|--------|

|                   |       |                      | PSCNT | <15:8> <sup>(1)</sup> |                    |                      |        |

| bit 7             |       |                      |       |                       |                    |                      | bit 0  |

|                   |       |                      |       |                       |                    |                      |        |

| Legend:           |       |                      |       |                       |                    |                      |        |

| R = Readable bi   | t     | W = Writable bit     |       | U = Unimpleme         | ented bit, read as | ; 'O'                |        |

| u = Bit is unchan | nged  | x = Bit is unknown   |       | -n/n = Value at       | POR and BOR/V      | /alue at all other R | lesets |

| '1' = Bit is set  |       | '0' = Bit is cleared |       |                       |                    |                      |        |

bit 7-0 **PSCNT<15:8>**: Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

#### REGISTER 9-5: WDTTMR: WDT TIMER REGISTER (READ ONLY)

| R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0             |

|-------------|-------|-------|-------|-------|-------|--------|-------------------|

| WDTTMR<3:0> |       |       |       |       | STATE | PSCNT< | 17:16> <b>(1)</b> |

| bit 7       |       |       |       |       |       |        | bit 0             |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 WDTTMR<4:0>: Watchdog Timer Value

- bit 2 STATE: WDT Armed Status bit 1 = WDT is armed 0 = WDT is not armed

- bit 1-0 **PSCNT<17:16>**: Prescale Select Upper Byte bits<sup>(1)</sup>

- **Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should be read during normal operation.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/ erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the CP bit of Configuration Words.

#### 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 16K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

# 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: |

|-------|

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

| TABLE 10-1: | FLASH MEMORY                  |

|-------------|-------------------------------|

|             | <b>ORGANIZATION BY DEVICE</b> |

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1614 | 32                   | 32                          |

| PIC16(L)F1618 | 52                   | 52                          |

#### 12.1.7 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELA register. Digital output functions may continue to control the pin when in Analog mode.

# 12.2 Register Definitions: PORTA

| U-0                                     | U-0 | R/W-x/x           | R/W-x/x                                               | R-x/x                              | R/W-x/x | R/W-x/x | R/W-x/x |  |  |

|-----------------------------------------|-----|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

|                                         | _   | RA5               | RA4                                                   | RA3                                | RA2     | RA1     | RA0     |  |  |

| bit 7                                   |     | -<br>-            |                                                       | •                                  | •       |         | bit 0   |  |  |

|                                         |     |                   |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |     |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable bit W = Writable bit       |     |                   |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |     |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

|                                         |     | '0' = Bit is clea |                                                       |                                    |         |         |         |  |  |

#### REGISTER 12-1: PORTA: PORTA REGISTER

| bit 7-6 | Unimplemented: Read as '0'                   |

|---------|----------------------------------------------|

| bit 5-0 | RA<5:0>: PORTA I/O Value bits <sup>(1)</sup> |

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 <b>= Port pin is <u>&lt;</u> V</b> IL      |

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### REGISTER 12-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>TRISA&lt;5:4&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

| bit 3   | Unimplemented: Read as '1'                                                                                                                         |

| bit 2-0 | <b>TRISA&lt;2:0&gt;:</b> PORTA Tri-State Control bit<br>1 = PORTA pin configured as an input (tri-stated)<br>0 = PORTA pin configured as an output |

Note 1: Unimplemented, read as '1'.

#### 12.3.7 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after Reset. Other functions are selected with the peripheral pin select logic. See **Section13.0** "**Peripheral Pin Select (PPS) Module**" for more information. Analog input functions, such as ADC inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

# 15.3 Register Definitions: FVR Control

| R/W-0/0              | R-q/q                                        | R/W-0/0                                                  | R/W-0/0                                                  | R/W-0/0                                                                        | R/W-0/0                                                                   | R/W-0/0          | R/W-0/0              |

|----------------------|----------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|----------------------|

| FVREN <sup>(1)</sup> | FVRRDY <sup>(2)</sup>                        | TSEN <sup>(3)</sup>                                      | TSRNG <sup>(3)</sup>                                     | CDAFV                                                                          | R<1:0> <sup>(1)</sup>                                                     | ADFVR            | <1:0> <sup>(1)</sup> |

| bit 7                |                                              |                                                          |                                                          |                                                                                |                                                                           |                  | bit                  |

|                      |                                              |                                                          |                                                          |                                                                                |                                                                           |                  |                      |

| Legend:              |                                              |                                                          |                                                          |                                                                                |                                                                           |                  |                      |

| R = Readable         |                                              | W = Writable                                             |                                                          |                                                                                | nented bit, read                                                          |                  |                      |

| u = Bit is unch      | nanged                                       | x = Bit is unk                                           |                                                          |                                                                                | at POR and BO                                                             |                  | ther Resets          |

| '1' = Bit is set     |                                              | '0' = Bit is cle                                         | ared                                                     | q = Value dep                                                                  | pends on condit                                                           | ion              |                      |

| bit 7                | 1 = Fixed Vo                                 | d Voltage Refe<br>Itage Referenc<br>Itage Referenc       | e is enabled                                             | bit <sup>(1)</sup>                                                             |                                                                           |                  |                      |

| bit 6                | 1 = Fixed Vo                                 | ed Voltage Re<br>Itage Referenc<br>Itage Referenc        | e output is rea                                          |                                                                                | enabled                                                                   |                  |                      |

| bit 5                | 1 = Tempera                                  | erature Indicato<br>ture Indicator i<br>ture Indicator i | s enabled                                                | )                                                                              |                                                                           |                  |                      |

| bit 4                | 1 = VOUT = V                                 | perature Indica<br>/DD - 4VT (Higł<br>/DD - 2VT (Low     | n Range)                                                 | lection bit <sup>(3)</sup>                                                     |                                                                           |                  |                      |

| bit 3-2              | 11 = Compara<br>10 = Compara<br>01 = Compara | ator FVR Buffe<br>ator FVR Buffe                         | er Gain is 4x, v<br>er Gain is 2x, v<br>er Gain is 1x, v | /ith output Vc□                                                                | bits <sup>(1)</sup><br>AFVR = 4x VFVR<br>AFVR = 2x VFVR<br>AFVR = 1x VFVR | <sub>2</sub> (4) |                      |

| bit 1-0              | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV    | 'R Buffer Gain                                           | is 4x, with out<br>is 2x, with out                       | ction bit <sup>(1)</sup><br>out VADFVR = 4<br>out VADFVR = 2<br>out VADFVR = 1 | x V <sub>FVR</sub> (4)                                                    |                  |                      |

|                      | minimize curren<br>the Buffer Gain           |                                                          |                                                          | R is disabled, th                                                              | ne FVR buffers                                                            | should be turne  | ed off by clea       |

|                      |                                              | 11 for the DIC                                           |                                                          | viene                                                                          |                                                                           |                  |                      |

# **REGISTER 15-1:** FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

- 2: FVRRDY is always '1' for the PIC16F1614/8 devices.

- 3: See Section16.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|---------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | ′R<1:0> | ADFVF | R<1:0> | 186                 |

**Legend:** Shaded cells are unused by the Fixed Voltage Reference module.

© 2014-2016 Microchip Technology Inc.

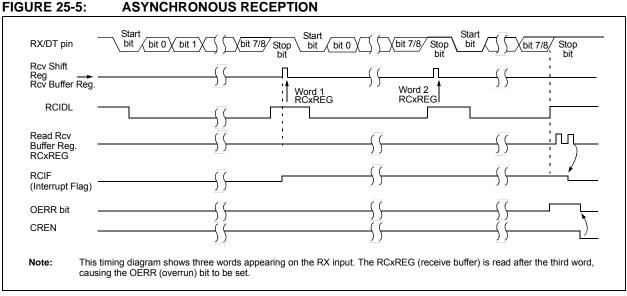

#### 25.1.2.8 Asynchronous Reception Set-up

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- 3. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- If 9-bit reception is desired, set the RX9 bit. 5.

- Enable reception by setting the CREN bit. 6.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags 8. and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPxBRGH, SPxBRGL register pair 1 and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- Clear the ANSEL bit for the RX pin (if applicable). 2.

- Enable the serial port by setting the SPEN bit. 3. The SYNC bit must be clear for asynchronous operation.

- 4 If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN 6. bit.

- Enable reception by setting the CREN bit. 7.

- 8. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCxSTA register to get the error flags. 9. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCxREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

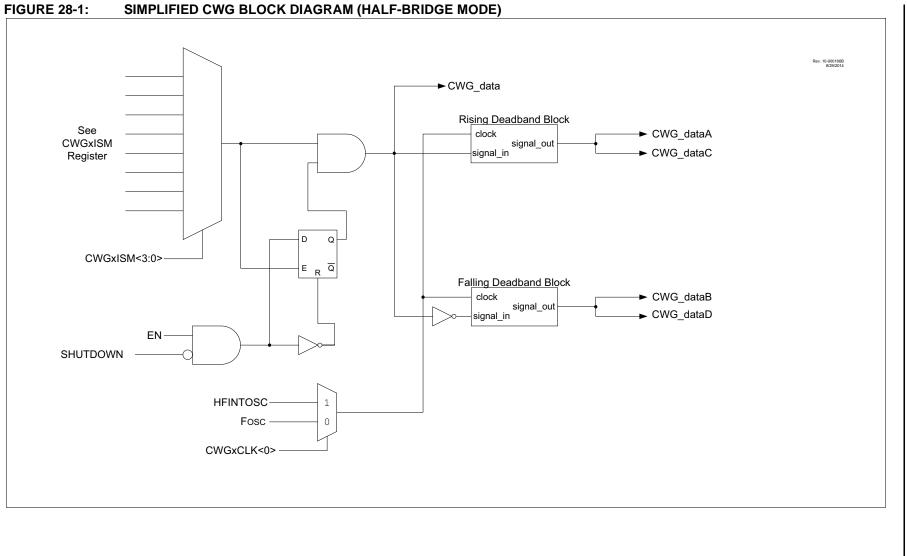

# SIMPLIFIED CWG BLOCK DIAGRAM (HALF-BRIDGE MODE)

PIC16(L)F1614/8

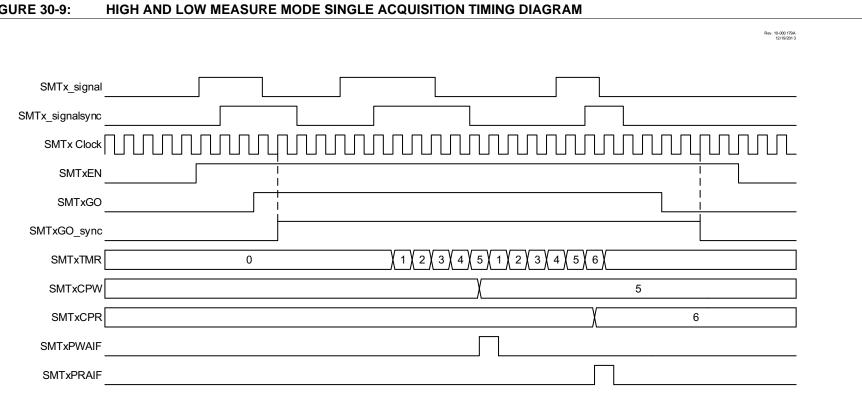

# 30.1 SMT Operation

The core of the module is the 24-bit counter, SMTxTMR combined with a complex data acquisition front-end. Depending on the mode of operation selected, the SMT can perform a variety of measurements summarized in Table 30-1.

#### 30.1.1 CLOCK SOURCES

Clock sources available to the SMT include:

- Fosc

- Fosc/4

- HFINTOSC 16 MHz

- LFINTOSC

- MFINTOSC 31.25 kHz

The SMT clock source is selected by configuring the CSEL<2:0> bits in the SMTxCLK register. The clock source can also be prescaled using the PS<1:0> bits of the SMTxCON0 register. The prescaled clock source is used to clock both the counter and any synchronization logic used by the module.

#### 30.1.2 PERIOD MATCH INTERRUPT

Similar to other timers, the SMT triggers an interrupt when SMTxTMR rolls over to '0'. This happens when SMTxTMR = SMTxPR, regardless of mode. Hence, in any mode that relies on an external signal or a window to reset the timer, proper operation requires that SMTxPR be set to a period larger than that of the expected signal or window.

# **30.2 Basic Timer Function Registers**

The SMTxTMR time base and the SMTxCPW/SMTxPR/SMTxCPR buffer registers serve several functions and can be manually updated using software.

#### 30.2.1 TIME BASE

The SMTxTMR is the 24-bit counter that is the center of the SMT. It is used as the basic counter/timer for measurement in each of the modes of the SMT. It can be reset to a value of 24'h00\_0000 by setting the RST bit of the SMTxSTAT register. It can be written to and read from software, but it is not guarded for atomic access, therefore reads and writes to the SMTxTMR should only be made when the GO = 0, or the software should have other measures to ensure integrity of SMTxTMR reads/writes.

#### 30.2.2 PULSE WIDTH LATCH REGISTERS

The SMTxCPW registers are the 24-bit SMT pulse width latch. They are used to latch in the value of the SMTxTMR when triggered by various signals, which are determined by the mode the SMT is currently in. The SMTxCPW registers can also be updated with the current value of the SMTxTMR value by setting the CPWUP bit of the SMTxSTAT register.

#### 30.2.3 PERIOD LATCH REGISTERS

The SMTxCPR registers are the 24-bit SMT period latch. They are used to latch in other values of the SMTxTMR when triggered by various other signals, which are determined by the mode the SMT is currently in.

The SMTxCPR registers can also be updated with the current value of the SMTxTMR value by setting the CPRUP bit in the SMTxSTAT register.

# 30.3 Halt Operation

The counter can be prevented from rolling-over using the STP bit in the SMTxCON0 register. When halting is enabled, the period match interrupt persists until the SMTxTMR is reset (either by a manual reset, **Section30.2.1 "Time Base**") or by clearing the SMTxGO bit of the SMTxCON1 register and writing the SMTxTMR values in software.

# **30.4 Polarity Control**

The three input signals for the SMT have polarity control to determine whether or not they are active high/positive edge or active low/negative edge signals.

The following bits apply to Polarity Control:

- WSEL bit (Window Polarity)

- SSEL bit (Signal Polarity)

- CSEL bit (Clock Polarity)

These bits are located in the SMTxCON0 register.

#### 30.5 Status Information

The SMT provides input status information for the user without requiring the need to deal with the polarity of the incoming signals.

#### 30.5.1 WINDOW STATUS

Window status is determined by the WS bit of the SMTxSTAT register. This bit is only used in Windowed Measure, Gated Counter and Gated Window Measure modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

#### 30.5.2 SIGNAL STATUS

Signal status is determined by the AS bit of the SMTxSTAT register. This bit is used in all modes except Window Measure, Time of Flight and Capture modes, and is only valid when TS = 1, and will be delayed in time by synchronizer delays in non-Counter modes.

#### 30.5.3 GO STATUS

Timer run status is determined by the TS bit of the SMTxSTAT register, and will be delayed in time by synchronizer delays in non-Counter modes.

# FIGURE 30-9:

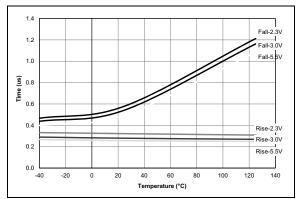

### 35.3 DC Characteristics

# TABLE 35-1: SUPPLY VOLTAGE

| PIC16F1614/8  |         |                                            | Standard Operating Conditions (unless otherwise stated) |        |            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|---------------|---------|--------------------------------------------|---------------------------------------------------------|--------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIC16F1       | 614/8   |                                            |                                                         |        |            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Param.<br>No. | Sym.    | Characteristic                             | Min.                                                    | Тур†   | Max.       | Units  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| D001          | Vdd     | Supply Voltage                             |                                                         |        | •          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|               |         |                                            | VDDMIN                                                  |        | VDDMAX     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|               |         |                                            | 1.8                                                     | —      | 3.6        | V      | Fosc ≤ 16 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|               |         |                                            | 2.5                                                     | _      | 3.6        | V      | Fosc ≤ 32 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |