## Microchip Technology - PIC16LF1614-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1614-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

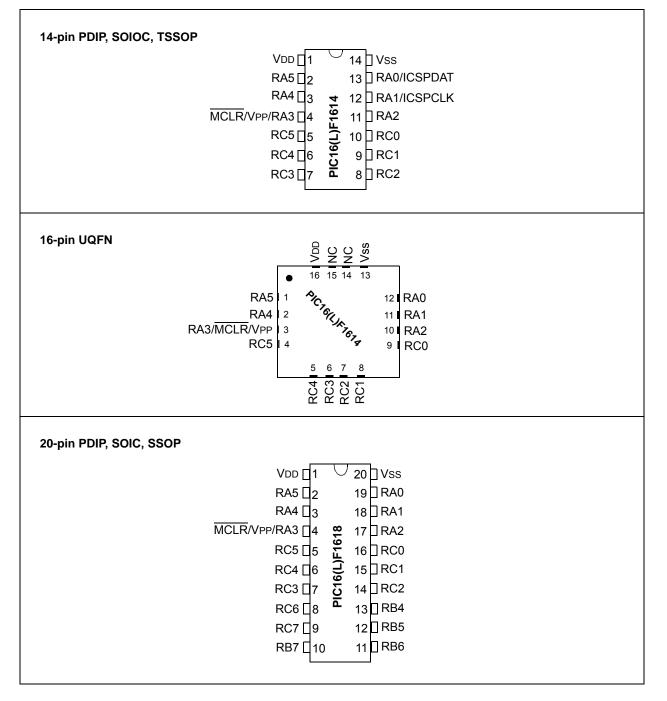

#### TABLE 2:PACKAGES

| Packages      | PDIP | SOIC | DFN | UDFN | TSSOP | QFN | UQFN | SSOP |

|---------------|------|------|-----|------|-------|-----|------|------|

| PIC16(L)F1614 | ٠    | •    |     |      | •     | •   |      |      |

| PIC16(L)F1618 | •    | •    |     |      |       | •   | •    | ٠    |

**Note:** Pin details are subject to change.

## **PIN DIAGRAMS**

© 2014-2016 Microchip Technology Inc.

## 1.0 DEVICE OVERVIEW

The PIC16(L)F1614/8 are described within this data sheet. The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pin out descriptions are shown in Tables 1-2 and 1-3.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                                    |            | PIC16(L)F1614 | PIC16(L)F1618 |

|-------------------------------------------------------------------------------|------------|---------------|---------------|

| Analog-to-Digital Converter (A                                                | ADC)       | ٠             | ٠             |

| Complementary Wave Generation                                                 | ator (CWG) | •             | •             |

| Cyclic Redundancy Check (C                                                    | RC)        | ٠             | ٠             |

| Digital-to-Analog Converter (I                                                | DAC)       | ٠             | ٠             |

| Enhanced Universal<br>Synchronous/Asynchronous<br>Receiver/Transmitter (EUSAR | •          | •             |               |

| Fixed Voltage Reference (FV                                                   | R)         | •             | ٠             |

| Temperature Indicator                                                         |            | •             | ٠             |

| Windowed Watchdog Timer (                                                     | •          | ٠             |               |

| Zero Cross Detection (ZCD)                                                    |            | •             | ٠             |

| Capture/Compare/PWM (CCI                                                      | P) Modules |               |               |

|                                                                               | CCP1       | •             | ٠             |

|                                                                               | CCP2       | •             | ٠             |

| Comparators                                                                   |            |               |               |

|                                                                               | C1         | •             | ٠             |

|                                                                               | C2         | •             | •             |

| Configurable Logic Cell (CLC                                                  | ;)         |               |               |

|                                                                               | CLC1       | •             | ٠             |

|                                                                               | CLC2       | •             | ٠             |

| Master Synchronous Serial P                                                   | Ports      |               |               |

|                                                                               | MSSP1      | •             | ٠             |

| Pulse Width Modulator (PWM                                                    | 1)         |               |               |

|                                                                               | PWM3       | ٠             | ٠             |

|                                                                               | PWM4       | ٠             | ٠             |

| Signal Measurement Timer (S                                                   | SMT)       |               |               |

|                                                                               | SMT1       | ٠             | ٠             |

|                                                                               | SMT2       | •             | •             |

| Timers                                                                        |            |               |               |

|                                                                               | Timer0     | •             | •             |

|                                                                               | Timer1     | •             | •             |

|                                                                               | Timer2     | •             | ٠             |

|                                                                               | Timer3     | •             | ٠             |

|                                                                               | Timer4     | •             | ٠             |

|                                                                               | Timer5     | •             | •             |

|                                                                               | Timer6     | •             | ٠             |

| TABLE 1-3: PIC16(L)F1618 PINOUT DESCRIPTION (CONTINUED) |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Name                                                                 | Function | Input<br>Type | Output<br>Type | Description                             |

|----------------------------------------------------------------------|----------|---------------|----------------|-----------------------------------------|

| RB6/SCK <sup>(1, 3)</sup>                                            | RB6      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

|                                                                      | SCK      | ST            | CMOS           | SPI clock.                              |

| RB7/CK <sup>(1)</sup>                                                | RB7      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

|                                                                      | СК       | ST            | CMOS           | USART synchronous clock.                |

| RC0/AN4/C2IN+/T5CKI <sup>(1)</sup>                                   | RC0      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

|                                                                      | AN4      | AN            | —              | ADC Channel input.                      |

|                                                                      | C2IN+    | AN            | _              | Comparator positive input.              |

|                                                                      | T5CKI    | TTL/ST        | —              | Timer5 clock input.                     |

| RC1/AN5/C1IN1-/C2IN1-/                                               | RC1      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| T4IN <sup>(1)</sup> /CLCIN <sup>(2)</sup> /SMTSIG2 <sup>(1)</sup>    | AN5      | AN            | _              | ADC Channel input.                      |

|                                                                      | C1IN1-   | AN            | _              | Comparator negative input.              |

|                                                                      | C2IN1-   | AN            | —              | Comparator negative input.              |

|                                                                      | T4IN     | TTL/ST        | _              | Timer4 input.                           |

|                                                                      | CLCIN2   | ST            | _              | Configurable Logic Cell source input.   |

|                                                                      | SMTSIG2  | TTL/ST        | —              | SMT2 signal input.                      |

| RC2/AN6/C1IN2-/C2IN2-                                                | RC2      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

|                                                                      | AN6      | AN            | _              | ADC Channel input.                      |

|                                                                      | C1IN2-   | AN            | —              | Comparator negative input.              |

|                                                                      | C2IN2-   | AN            | —              | Comparator negative input.              |

| RC3/AN7/C1IN3-/C2IN3-/T5G <sup>(1)</sup> /                           | RC3      | TTL/ST        | —              | General purpose input with IOC and WPU. |

| CCP2 <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> /ATCC <sup>(1)</sup>      | AN7      | AN            | —              | ADC Channel input.                      |

|                                                                      | C1IN3-   | AN            | —              | Comparator negative input.              |

|                                                                      | C2IN3-   | AN            | —              | Comparator negative input.              |

|                                                                      | T5G      | ST            | —              | Timer5 Gate input.                      |

|                                                                      | CCP2     | ST            | CMOS           | Capture/Compare/PWM2.                   |

|                                                                      | CLCIN0   | ST            | —              | Configurable Logic Cell source input.   |

|                                                                      | ATCC     | ST            | -              | Angular Timer Capture/Compare input.    |

| RC4/T3G <sup>(1)</sup> /CLCIN1 <sup>(1)</sup> /HIC4                  | RC4      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

|                                                                      | T3G      | ST            | —              | Timer3 Gate input.                      |

|                                                                      | CLCIN1   | ST            | _              | Configurable Logic Cell source input.   |

|                                                                      | HIC4     | TTL           | CMOS           | High Current I/O.                       |

| RC5/T3CKI <sup>(1)</sup> /CCP2 <sup>(1)</sup> /ATIN <sup>(1)</sup> / | RC5      | TTL/ST        | CMOS/OD        | General purpose I/O.                    |

| HIC5                                                                 | T3CKI    | TTL/ST        | —              | Timer3 clock input.                     |

|                                                                      | CCP2     | TTL/ST        | CMOS/OD        | Capture/Compare/PWM2.                   |

|                                                                      | ATIN     | TTL/ST        | —              | Angular Timer clock input.              |

|                                                                      | HIC5     | TTL           | CMOS           | High Current I/O.                       |

Legend:AN= Analog input or outputCMOS= CMOS compatible input or outputOD=Open-DrainTTL= TTL compatible inputST=Schmitt Trigger input with CMOS levels $l^2C$ =Schmitt Trigger input with  $l^2C$

XTAL = Crystal

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-1.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

HV = High Voltage

levels

## TABLE 3-2: PIC16(L)F1614 MEMORY MAP, BANK 0-7

|      | BANK 0                        |              | BANK 1                        |              | BANK 2                        |              | BANK 3                        |              | BANK 4                        |              | BANK 5                        |       | BANK 6                        |        | BANK 7                        |

|------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|--------------|-------------------------------|-------|-------------------------------|--------|-------------------------------|

| 000h | Core Registers<br>(Table 3-1) | 080h         | Core Registers<br>(Table 3-1) | 100h         | Core Registers<br>(Table 3-1) | 180h         | Core Registers<br>(Table 3-1) | 200h         | Core Registers<br>(Table 3-1) | 280h         | Core Registers<br>(Table 3-1) | 300h  | Core Registers<br>(Table 3-1) | 380h   | Core Registers<br>(Table 3-1) |

| 00Bh |                               | 08Bh         |                               | 10Bh         |                               | 18Bh         |                               | 20Bh         |                               | 28Bh         |                               | 30Bh  |                               | 38Bh   |                               |

| 00Ch | PORTA                         | 08Ch         | TRISA                         | 10Ch         | LATA                          | 18Ch         | ANSELA                        | 20Ch         | WPUA                          | 28Ch         | ODCONA                        | 30Ch  | SLRCONA                       | 38Ch   | INLVLA                        |

| 00Dh |                               | 08Dh         |                               | 10Dh         |                               | 18Dh         |                               | 20Dh         |                               | 28Dh         |                               | 30Dh  |                               | 38Dh   |                               |

| 00Eh | PORTC                         | 08Eh         | TRISC                         | 10Eh         | LATC                          | 18Eh         | ANSELC                        | 20Eh         | WPUC                          | 28Eh         | ODCONC                        | 30Eh  | SLRCONC                       | 38Eh   | INLVLC                        |

| 00Fh |                               | 08Fh         |                               | 10Fh         | _                             | 18Fh         | _                             | 20Fh         | —                             | 28Fh         | _                             | 30Fh  | —                             | 38Fh   | —                             |

| 010h | PIR1                          | 090h         | PIE1                          | 110h         |                               | 190h         |                               | 210h         | —                             | 290h         |                               | 310h  | _                             | 390h   | _                             |

| 011h | PIR2                          | 091h         | PIE2                          | 111h         | CM1CON0                       | 191h         | PMADRL                        | 211h         | SSP1BUF                       | 291h         | CCP1RL                        | 311h  | —                             | 391h   | IOCAP                         |

| 012h | PIR3                          | 092h         | PIE3                          | 112h         | CM1CON1                       | 192h         | PMADRH                        | 212h         | SSP1ADD                       | 292h         | CCP1RH                        | 312h  | —                             | 392h   | IOCAN                         |

| 013h | PIR4                          | 093h         | PIE4                          | 113h         | CM2CON0                       | 193h         | PMDATL                        | 213h         | SSP1MSK                       | 293h         | CCP1CON                       | 313h  | —                             | 393h   | IOCAF                         |

| 014h | PIR5                          | 094h         | PIE5                          | 114h         | CM2CON1                       | 194h         | PMDATH                        | 214h         | SSP1STAT                      | 294h         | CCP1CAP                       | 314h  | —                             | 394h   | _                             |

| 015h | TMR0                          | 095h         | OPTION_REG                    | 115h         | CMOUT                         | 195h         | PMCON1                        | 215h         | SSP1CON                       | 295h         | _                             | 315h  | —                             | 395h   |                               |

| 016h | TMR1L                         | 096h         | PCON                          | 116h         | BORCON                        | 196h         | PMCON2                        | 216h         | SSP1CON2                      | 296h         | —                             | 316h  | _                             | 396h   | —                             |

| 017h | TMR1H                         | 097h         | —                             | 117h         | FVRCON                        | 197h         | VREGCON                       | 217h         | SSP1CON3                      | 297h         | _                             | 317h  | —                             | 397h   | IOCCP                         |

| 018h | T1CON                         | 098h         | OSCTUNE                       | 118h         | DAC1CON0                      | 198h         | —                             | 218h         | —                             | 298h         | CCP2RL                        | 318h  | —                             | 398h   | IOCCN                         |

| 019h | T1GCON                        | 099h         | OSCCON                        | 119h         | DAC1CON1                      | 199h         | RC1REG                        | 219h         | —                             | 299h         | CCP2RH                        | 319h  | —                             | 399h   | IOCCF                         |

| 01Ah | TMR2                          | 09Ah         | OSCSTAT                       | 11Ah         | —                             | 19Ah         | TX1REG                        | 21Ah         | —                             | 29Ah         | CCP2CON                       | 31Ah  | —                             | 39Ah   | —                             |

| 01Bh | PR2                           | 09Bh         | ADRESL                        | 11Bh         | —                             | 19Bh         | SP1BRGL                       | 21Bh         | —                             | 29Bh         | CCP2CAP                       | 31Bh  | _                             | 39Bh   | _                             |

| 01Ch | T2CON                         | 09Ch         | ADRESH                        | 11Ch         | ZCD1CON                       | 19Ch         | SP1BRGH                       | 21Ch         | —                             | 29Ch         | —                             | 31Ch  | _                             | 39Ch   | _                             |

| 01Dh | T2HLT                         | 09Dh         | ADCON0                        | 11Dh         | _                             | 19Dh         | RC1STA                        | 21Dh         | —                             | 29Dh         | _                             | 31Dh  | _                             | 39Dh   | _                             |

| 01Eh | T2CLKCON                      | 09Eh         | ADCON1                        | 11Eh         | _                             | 19Eh         | TX1STA                        | 21Eh         |                               | 29Eh         | CCPTMRS                       | 31Eh  | _                             | 39Eh   |                               |

| 01Fh | T2RST                         | 09Fh         | ADCON2                        | 11Fh         |                               | 19Fh         | BAUD1CON                      | 21Fh         | _                             | 29Fh         | _                             | 31Fh  | _                             | 39Fh   |                               |

| 020h |                               | 0A0h         |                               | 120h         |                               | 1A0h         |                               | 220h         |                               | 2A0h         |                               | 320h  | General Purpose<br>Register   | 3A0h   |                               |

|      |                               |              | General                       | 32Fh  | 16 Bytes                      |        |                               |

|      |                               |              | Purpose                       | 330h  |                               |        | Unimplemented                 |

|      | General                       |              | Register<br>80 Bytes          | 00011 | Unimplemented                 |        | Read as '0'                   |

|      | Purpose                       |              | oo bytes                      |       | Read as '0'                   |        |                               |

|      | Register<br>96 Bytes          | 0EFh         |                               |              |                               |              |                               | 005          |                               | 0            |                               | 36Fh  |                               | 3EFh   |                               |

|      | 00 Dy(00                      | 0EFn<br>0F0h |                               | 16Fh<br>170h |                               | 1EFh<br>1F0h |                               | 26Fh<br>270h |                               | 2EFh<br>2F0h |                               |       |                               | 3F0h   |                               |

|      |                               | 01.011       | Common RAM                    | 17011        | Common RAM                    | 11.011       | Common RAM                    | 27011        | Common RAM                    | 21.011       | Common RAM                    | 370h  | A                             | 51 011 | Common RAM                    |

|      |                               |              | (Accesses                     |       | Accesses<br>70h – 7Fh         |        | (Accesses                     |

| 0755 |                               | OFER         | 70h – 7Fh)                    | 175h         | 70h – 7Fh)                    | 1556         | 70h – 7Fh)                    | 27Eh         | 70h – 7Fh)                    | 2FFh         | 70h – 7Fh)                    | 27Eb  | / /                           | 255h   | 70h – 7Fh)                    |

| 07Fh |                               | 0FFh         |                               | 17Fh         |                               | 1FFh         |                               | 27Fh         |                               | ∠⊢⊢n         |                               | 37Fh  |                               | 3FFh   |                               |

**Legend:** = Unimplemented data memory locations, read as '0'.

| Addr | Name      | Bit 7         | Bit 6         | Bit 5 | Bit 4       | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|------|-----------|---------------|---------------|-------|-------------|-------|-------|-----------|-----------|----------------------|---------------------------|

| Bank | 11        |               |               |       | · · · · · · |       |       |           |           | •                    |                           |

| 58Ch | PID1SELT  |               |               |       | SET<        | 7:0>  |       |           |           | xxxx xxxx            | XXXX XXXX                 |

| 58Dh | PID1SETH  |               |               |       | SET<1       | 5:8>  |       |           |           | XXXX XXXX            | xxxx xxxx                 |

| 58Eh | PID1INL   |               |               |       | IN<7        | :0>   |       |           |           | 0000 0000            | 0000 0000                 |

| 58Fh | PID1INH   |               |               |       | IN<15       | 5:8>  |       |           |           | 0000 0000            | 0000 0000                 |

| 590h | PID1K1L   |               | K1<7:0>       |       |             |       |       |           |           |                      | XXXX XXXX                 |

| 591h | PID1K1H   |               | K1<15:8>      |       |             |       |       |           |           | xxxx xxxx            | XXXX XXXX                 |

| 592h | PID1K2L   |               | K2<7:0>       |       |             |       |       |           |           | XXXX XXXX            | XXXX XXXX                 |

| 593h | PID1K2H   |               | K2<15:8>      |       |             |       |       |           |           | XXXX XXXX            | XXXX XXXX                 |

| 594h | PID1K3L   |               | K3<7:0>       |       |             |       |       |           |           | XXXX XXXX            | xxxx xxxx                 |

| 595h | PID1K3H   |               | K3<15:8>      |       |             |       |       |           |           | XXXX XXXX            | xxxx xxxx                 |

| 596h | PID10UTLL |               |               |       | OUT<        | 7:0>  |       |           |           | 0000 0000            | 0000 0000                 |

| 597h | PID10UTLH |               |               |       | OUT<1       | 15:8> |       |           |           | 0000 0000            | 0000 0000                 |

| 598h | PID10UTHL |               |               |       | OUT<2       | 3:16> |       |           |           | 0000 0000            | 0000 0000                 |

| 599h | PID10UTHH |               | _             | _     | OUT<3       | 1:24> |       |           |           | 0000 0000            | 0000 0000                 |

| 59Ah | PID10UTU  | —             | OUT<35:32>    |       |             |       |       |           |           | 0000                 | 0000                      |

| 59Bh | PID1Z1L   | Z1<7:0>       |               |       |             |       |       |           | 0000 0000 | 0000 0000            |                           |

| 59Ch | PID1Z1H   | Z1<15:8>      |               |       |             |       |       | 0000 0000 | 0000 0000 |                      |                           |

| 59Dh | PID1Z1U   | _             | Z116          |       |             |       |       |           |           | 0                    | 0                         |

| 59Eh | —         | Unimplemented | Unimplemented |       |             |       |       |           |           | —                    | —                         |

| 59Fh | —         | Unimplemented | nimplemented  |       |             |       |       |           |           | —                    | —                         |

### TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

| U-0             | U-0               | R/W-0/0           | R/W-0/0       | R/W-0/0                            | R/W-0/0          | R/W-0/0        | R/W-0/0      |  |  |  |  |

|-----------------|-------------------|-------------------|---------------|------------------------------------|------------------|----------------|--------------|--|--|--|--|

| —               | —                 |                   |               | TUN                                | <5:0>            |                |              |  |  |  |  |

| bit 7           |                   |                   |               |                                    |                  |                | bit 0        |  |  |  |  |

|                 |                   |                   |               |                                    |                  |                |              |  |  |  |  |

| Legend:         |                   |                   |               |                                    |                  |                |              |  |  |  |  |

| R = Readabl     | le bit            | W = Writable      | bit           | U = Unimplemented bit, read as '0' |                  |                |              |  |  |  |  |

| u = Bit is und  | changed           | x = Bit is unkr   | nown          | -n/n = Value a                     | at POR and BO    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se | et                | '0' = Bit is clea | ared          |                                    |                  |                |              |  |  |  |  |

|                 |                   |                   |               |                                    |                  |                |              |  |  |  |  |

| bit 7-6         | Unimpleme         | nted: Read as '   | 0'            |                                    |                  |                |              |  |  |  |  |

| bit 5-0         | TUN<5:0>:         | Frequency Tunir   | ng bits       |                                    |                  |                |              |  |  |  |  |

|                 | 100000 = N        | 1inimum frequen   | су            |                                    |                  |                |              |  |  |  |  |

|                 | •                 |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | •                 |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | 111111 =          |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | 000000 = C        | scillator module  | is running at | the factory-calib                  | orated frequence | cy.            |              |  |  |  |  |

|                 | 000001 =          |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | •                 |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | •                 |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | 011110 =          |                   |               |                                    |                  |                |              |  |  |  |  |

|                 | 011111 <b>= N</b> | laximum frequer   | псу           |                                    |                  |                |              |  |  |  |  |

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7  | Bit 6 | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|-------|------------|--------|--------|--------|--------|--------|---------------------|

| OSCCON  | SPLLEN |       | IRCF       | <3:0>  |        |        | SCS    | 81     |                     |

| OSCSTAT | _      | PLLR  | OSTS       | HFIOFR | HFIOFL | MFIOFR | LFIOFR | HFIOFS | 82                  |

| OSCTUNE |        | _     | — TUN<5:0> |        |        |        |        |        | 83                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG1 | 13:8 | _       |         | _        | _        | CLKOUTEN | BORE     | N<1:0>  |         | 67                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | _        |          |          | FOSC    | <1:0>   | 07                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

| U-0          | R/W-0/0                                | R/W-0/0                                       | U-0          | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|--------------|----------------------------------------|-----------------------------------------------|--------------|----------------|------------------|------------------|--------------|--|--|--|--|

| _            | C2IF                                   | C1IF                                          | _            | BCL1IF         | TMR6IF           | TMR4IF           | CCP2IF       |  |  |  |  |

| bit 7        |                                        |                                               |              |                |                  |                  | bit 0        |  |  |  |  |

|              |                                        |                                               |              |                |                  |                  |              |  |  |  |  |

| Legend:      |                                        |                                               |              |                |                  |                  |              |  |  |  |  |

| R = Read     |                                        | W = Writable t                                |              | •              | nented bit, read |                  |              |  |  |  |  |

|              | unchanged                              | x = Bit is unkn                               |              | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is | set                                    | '0' = Bit is clea                             | ired         |                |                  |                  |              |  |  |  |  |

| bit 7        | Unimpleme                              | nted: Read as '0                              | ,            |                |                  |                  |              |  |  |  |  |

| bit 6        | 1 1 5                                  |                                               |              |                |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                          |                                               |              |                |                  |                  |              |  |  |  |  |

|              | •                                      | is not pending                                |              |                |                  |                  |              |  |  |  |  |

| bit 5        | -                                      | arator C1 Interru                             | pt Flag bit  |                |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                          | is pending<br>is not pending                  |              |                |                  |                  |              |  |  |  |  |

| bit 4        |                                        |                                               |              |                |                  |                  |              |  |  |  |  |

| bit 3        | -                                      | BCL1IF: MSSP Bus Collision Interrupt Flag bit |              |                |                  |                  |              |  |  |  |  |

| Sit C        | 1 = Interrupt                          |                                               | , mon apri   |                |                  |                  |              |  |  |  |  |

|              |                                        | is not pending                                |              |                |                  |                  |              |  |  |  |  |

| bit 2        | TMR6IF: Tin                            | ner6 to PR6 Inter                             | rupt Flag bi | t              |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                          |                                               |              |                |                  |                  |              |  |  |  |  |

| 1.11.4       | -                                      | is not pending                                |              |                |                  |                  |              |  |  |  |  |

| bit 1        | 1 = Interrupt                          | ner4 to PR4 Inter                             | rupt Flag bi | t              |                  |                  |              |  |  |  |  |

|              |                                        | is not pending                                |              |                |                  |                  |              |  |  |  |  |

| bit 0        |                                        | P2 Interrupt Flag                             | ı bit        |                |                  |                  |              |  |  |  |  |

|              | 1 = Interrupt                          |                                               |              |                |                  |                  |              |  |  |  |  |

|              | 0 = Interrupt                          | is not pending                                |              |                |                  |                  |              |  |  |  |  |

|              |                                        |                                               |              |                |                  |                  |              |  |  |  |  |

| Note:        | Interrupt flag bits                    |                                               |              |                |                  |                  |              |  |  |  |  |

|              | condition occurs,<br>its corresponding |                                               |              |                |                  |                  |              |  |  |  |  |

|              | Enable bit, GIE                        |                                               |              |                |                  |                  |              |  |  |  |  |

|              | User software                          | should ensu                                   | re the       |                |                  |                  |              |  |  |  |  |

|              | appropriate interru                    |                                               | ear prior    |                |                  |                  |              |  |  |  |  |

|              | to enabling an inte                    | errupt.                                       |              |                |                  |                  |              |  |  |  |  |

## REGISTER 7-8: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

The CPU is held until the scan stops. Note that because the CPU is not executing instructions, the SCANGO bit cannot be cleared in software, so the CPU will remain stalled until one of the hardware end-conditions occurs. Burst mode has the highest throughput for the scanner, but has the cost of stalling other execution while it occurs.

## 11.10.2 CONCURRENT MODE

When MODE = 00, the scanner is in Concurrent mode. Concurrent mode, like Burst mode, stalls the CPU while performing accesses of memory. However, while Burst mode stalls until all accesses are complete, Concurrent mode allows the CPU to execute in between access cycles.

#### 11.10.3 TRIGGERED MODE

When MODE = 11, the scanner is in Triggered mode. Triggered mode behaves identically to Concurrent mode, except instead of beginning the scan immediately upon the SCANGO bit being set, it waits for a rising edge from a separate trigger clock, the source of which is determined by the SCANTRIG register.

#### 11.10.4 PEEK MODE

When MODE = 10, the scanner is in Peek mode. Peek mode waits for an instruction cycle in which the CPU does not need to access the NVM (such as a branch instruction) and uses that cycle to do its own NVM access. This results in the lowest throughput for the NVM access (and can take a much longer time to complete a scan than the other modes), but does so without any impact on execution times, unlike the other modes.

| MO   | )DE<1:0>   |                                         | Description                |                                                  |  |  |  |  |  |  |  |

|------|------------|-----------------------------------------|----------------------------|--------------------------------------------------|--|--|--|--|--|--|--|

| IVIC |            | First Scan Access                       | CPU                        | Operation                                        |  |  |  |  |  |  |  |

| 11   | Triggered  | As soon as possible following a trigger | Stalled during NVM access  | CPU resumes execution following each access      |  |  |  |  |  |  |  |

| 10   | Peek       | At the first dead cycle                 | Timing is unaffected       | CPU continues execution following<br>each access |  |  |  |  |  |  |  |

| 01   | Burst      | As soon as possible                     | Stalled during NV/M appage | CPU suspended until scan<br>completes            |  |  |  |  |  |  |  |

| 00   | Concurrent | As soon as possible                     | Stalled during NVM access  | CPU resumes execution following<br>each access   |  |  |  |  |  |  |  |

#### TABLE 11-1: SUMMARY OF SCANNER MODES

#### 11.10.5 INTERRUPT INTERACTION

The INTM bit of the SCANCON0 register controls the scanner's response to interrupts depending on which mode the NVM scanner is in, as described in Table 11-2.

#### TABLE 11-2: SCAN INTERRUPT MODES

| INTM | MODE                                                                                                                                                                  | MODE<1:0>                                                                                                                            |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      | MODE == Burst                                                                                                                                                         | MODE != Burst                                                                                                                        |  |  |  |

| 1    | Interrupt overrides SCANGO to pause the burst<br>and the interrupt handler executes at full speed;<br>Scanner Burst resumes when interrupt<br>completes.              | Scanner suspended during interrupt response;<br>interrupt executes at full speed and scan<br>resumes when the interrupt is complete. |  |  |  |

| 0    | Interrupts do not override SCANGO, and the scan (burst) operation will continue; interrupt response will be delayed until scan completes (latency will be increased). | Scanner accesses NVM during interrupt response. If MODE != Peak the interrupt handler execution speed will be affected.              |  |  |  |

In general, if INTM = 0, the scanner will take precedence over the interrupt, resulting in decreased interrupt processing speed and/or increased interrupt response latency. If INTM = 1, the interrupt will take precedence and have a better speed, delaying the memory scan.

| R/W-0/0           |                                        | R-0                       | R-0                                                | R/W-0/0                | U-0                        | R/W-0/0       | R/W-0/0          |

|-------------------|----------------------------------------|---------------------------|----------------------------------------------------|------------------------|----------------------------|---------------|------------------|

| EN <sup>(1)</sup> | SCANGO <sup>(2, 3)</sup>               | BUSY <sup>(4)</sup>       | INVALID                                            | INTM                   |                            | MODE          | <1:0> <b>(5)</b> |

| bit 7             |                                        |                           |                                                    |                        |                            |               | bit 0            |

| Legend:           |                                        |                           |                                                    |                        |                            |               |                  |

| R = Readal        | hle hit                                | W = Writable              | hit                                                | U = Unimpler           | mented bit, read           | 1 as '0'      |                  |

| u = Bit is ur     |                                        | x = Bit is unk            |                                                    | •                      | at POR and BO              |               | other Resets     |

| '1' = Bit is s    | 0                                      | '0' = Bit is cle          |                                                    |                        | eared by hardw             |               |                  |

|                   |                                        |                           |                                                    |                        |                            |               |                  |

| bit 7             | EN: Scanner                            | Enable bit <sup>(1)</sup> |                                                    |                        |                            |               |                  |

|                   | 1 = Scanner is                         |                           |                                                    |                        |                            |               |                  |

| 1.1.0             |                                        |                           | ernal states are                                   | e reset                |                            |               |                  |

| bit 6             | SCANGO: Sc                             |                           |                                                    |                        |                            |               |                  |

|                   |                                        | ent peripheral.           | i ready signal,                                    | NVIVI WIII De ac       | ccessed accord             | ing to MDx an | d data passed    |

|                   | 0 = Scanner o                          |                           | not occur                                          |                        |                            |               |                  |

| bit 5             | BUSY: Scann                            | er Busy Indica            | ator bit <sup>(4)</sup>                            |                        |                            |               |                  |

|                   | 1 = Scanner o                          | ycle is in proc           | ess                                                |                        |                            |               |                  |

|                   | 0 = Scanner o                          | cycle is comple           | ete (or never st                                   | arted)                 |                            |               |                  |

| bit 4             | INVALID: Sca                           | -                         |                                                    |                        | <i>(</i> <b>-</b> )        |               |                  |

|                   |                                        |                           | remented or co<br>o a valid addre                  | ontains an inva<br>ess | lid address <sup>(6)</sup> |               |                  |

| bit 3             |                                        |                           | ipt Manageme                                       | nt Mode Select         | t bit                      |               |                  |

|                   | If MODE = 10:                          |                           |                                                    |                        |                            |               |                  |

|                   | This bit is igno                       |                           |                                                    |                        |                            |               |                  |

|                   |                                        | •                         | <u>d until all data is</u>                         |                        |                            |               |                  |

|                   |                                        | is overridden             | (to zero) during                                   | g interrupt oper       | ration; scanner            | resumes after | returning from   |

|                   | interrupt<br>0 = SCANGO                | is not affected           | d bv interrupts.                                   | the interrupt re       | esponse will be            | affected      |                  |

|                   | If MODE = 00                           |                           | · · <b>,</b> · · · · · · · · · · · · · · · · · · · |                        |                            |               |                  |

|                   | 1 = SCANGO<br>from inter               |                           | (to zero) during                                   | interrupt opera        | ation; scan oper           | ations resume | after returning  |

|                   |                                        |                           | t NVM access                                       |                        |                            |               |                  |

| bit 2             | Unimplement                            | ted: Read as              | 0'                                                 |                        |                            |               |                  |

| bit 1-0           | MODE<1:0>:                             | Memory Acce               | ess Mode bits <sup>(5</sup>                        | )                      |                            |               |                  |

|                   | 11 = Triggere                          | d mode                    |                                                    |                        |                            |               |                  |

|                   | 10 = Peek mo                           |                           |                                                    |                        |                            |               |                  |

|                   | 01 = Burst mo<br>00 = Concurre         |                           |                                                    |                        |                            |               |                  |

| Note 1:           | Setting EN = 0 (SC                     | CANCON0 red               | ister) does not                                    | affect any othe        | er register conte          | ent.          |                  |

|                   | This bit is cleared                    | -                         |                                                    | -                      | -                          |               |                  |

|                   | If INTM = 1, this bi                   |                           | -                                                  | -                      |                            | response.     |                  |

|                   | BUSY = 1 when th                       |                           | •                                                  |                        | •                          | •             |                  |

| 5: 3              | See Table 11-1 for                     | more detailed             | information.                                       |                        |                            |               |                  |

| I                 | An invalid address<br>memory is 0x4000 |                           |                                                    |                        |                            |               |                  |

## REGISTER 11-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

address is invalid.

| R/W-0/0                      | R/W-0/0                               | R/W-0/0           | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|------------------------------|---------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

| HADR<15:8> <sup>(1, 2)</sup> |                                       |                   |                                                       |                                    |         |         |         |  |  |

| bit 7                        |                                       |                   |                                                       |                                    |         |         | bit 0   |  |  |

|                              |                                       |                   |                                                       |                                    |         |         |         |  |  |

| Legend:                      |                                       |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable                 | le bit W = Writable bit               |                   |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is uncha             | = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

| '1' = Bit is set             |                                       | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |  |

#### REGISTER 11-14: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

### REGISTER 11-15: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0        | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0         | R/W-0/0 | R/W-0/0 |

|----------------|---------|------------------|---------|--------------------|-----------------|---------|---------|

|                |         |                  | HADR<   | 7:0> <b>(1, 2)</b> |                 |         |         |

| bit 7          |         |                  |         |                    |                 |         | bit 0   |

|                |         |                  |         |                    |                 |         |         |

| Legend:        |         |                  |         |                    |                 |         |         |

| R = Readable I | hit     | W = Writable bit | ł       | =   Inimplen       | nented hit read | as 'O'  |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

#### **REGISTER 12-19: LATC: PORTC DATA LATCH REGISTER**

| R/W-x/u              | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|----------------------|---------|---------|---------|---------|---------|---------|

| LATC7 <sup>(1)</sup> | LATC6 <sup>(1)</sup> | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7                |                      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | LATC<7:0>: RC<7:0> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|         | 1 = PORTC pin configured as an input (tri-stated)         |

|         | 0 = PORTC pin configured as an output                     |

**Note 1:** LATC<7:6> on PIC16(L)F1618 only.

2: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

#### REGISTER 12-20: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1              | R/W-1/1              | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|----------------------|-----|-----|---------|---------|---------|---------|

| ANSC7 <sup>(1)</sup> | ANSC6 <sup>(1)</sup> | —   | —   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7                |                      |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ANSC<7:6>**: Analog Select between Analog or Digital Function on Pins RC<7:6>, respectively<sup>(1)</sup> 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- bit 5-4 Unimplemented: Read as '0'

bit 3-0 **ANSC<3:0>**: Analog Select between Analog or Digital Function on Pins RC<3:0>, respectively 1 = Analog input. Pin is assigned as analog input<sup>(2)</sup>. Digital input buffer disabled. 0 = Digital I/O. Pin is assigned to port or digital special function.

Note 1: ANSC<7:6> on PIC16(L)F1618 only.

2: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name     | Bit 7                                        | Bit 6                  | Bit 5               | Bit 4  | Bit 3       | Bit 2     | Bit 1     | Bit 0  | Register<br>on Page |

|----------|----------------------------------------------|------------------------|---------------------|--------|-------------|-----------|-----------|--------|---------------------|

| CCP1CON  | EN                                           |                        | - OUT FMT MODE<3:0> |        |             |           |           | 352    |                     |

| CCP2CON  | EN                                           | _                      | OUT                 | FMT    |             | MODE      | E<3:0>    |        | 352                 |

| INTCON   | GIE                                          | PEIE                   | TMR0IE              | INTE   | IOCIE       | TMR0IF    | INTF      | IOCIF  | 97                  |

| PIE1     | TMR1GIE                                      | ADIE                   | _                   | _      | -           | CCP1IE    | TMR2IE    | TMR1IE | 98                  |

| PIR1     | TMR1GIF                                      | ADIF                   | RCIF                | TXIF   | SSP1IF      | CCP1IF    | TMR2IF    | TMR1IF | 103                 |

| PR2      | Timer2 Module Period Register                |                        |                     |        |             |           |           |        | 235*                |

| TMR2     | Holding Register for the 8-bit TMR2 Register |                        |                     |        |             |           |           |        | 235*                |

| T2CON    | ON                                           | N CKPS<2:0> OUTPS<3:0> |                     |        |             |           |           | 254    |                     |

| T2CLKCON | —                                            | _                      | _                   | _      |             | CS<       | :3:0>     |        | 253                 |

| T2RST    | _                                            |                        |                     |        | — RSEL<3:0> |           |           |        |                     |

| T2HLT    | PSYNC                                        | CKPOL CKSYNC MODE<4:0> |                     |        |             |           |           | 255    |                     |

| PR4      | Timer4 Modu                                  | ule Period Re          | gister              |        |             |           |           |        | 235*                |

| TMR4     | Holding Reg                                  | ister for the 8        | -bit TMR4 Re        | gister |             |           |           |        | 235*                |

| T4CON    | ON                                           |                        | CKPS<2:0>           |        |             | OUTP      | S<3:0>    |        | 254                 |

| T4CLKCON | —                                            | _                      | _                   | _      |             | CS<       | <3:0>     |        | 253                 |

| T4RST    | _                                            |                        | _                   | _      |             | RSEL      | _<3:0>    |        | 256                 |

| T4HLT    | PSYNC                                        | CKPOL                  | CKSYNC              |        |             | MODE<4:0> |           |        | 255                 |

| PR6      | Timer6 Modu                                  | ule Period Re          | gister              |        |             |           |           |        | 235*                |

| TMR6     | Holding Reg                                  | ister for the 8        | -bit TMR6 Re        | gister |             |           |           |        | 235*                |

| T6CON    | ON                                           |                        | CKPS<2:0>           |        |             | OUTP      | S<3:0>    |        | 254                 |

| T6CLKCON | _                                            | _                      | _                   | _      |             |           | T6CS<2:0> |        | 253                 |

| T6RST    | —                                            | _                      | _                   | _      |             | RSEL      | _<3:0>    |        | 256                 |

| T6HLT    | PSYNC                                        | CKPOL                  | CKSYNC              |        |             | MODE<4:0> |           |        | 255                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

PIC16(L)F1614/8

© 2014-2016 Microchip Technology Inc.

| Name                                        | Bit 7                   | Bit 6        | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------------------------------------------|-------------------------|--------------|---------------------|--------|--------|--------|--------|--------|---------------------|

| CCPxCAP                                     | —                       | _            | -                   | —      | —      | —      | CTS    | <1:0>  | 355                 |

| CCPxCON                                     | EN                      | _            | - OUT FMT MODE<3:0> |        |        |        |        |        | 352                 |

| CCPRxL Capture/Compare/PWM Register x (LSB) |                         |              |                     |        |        |        |        | 354    |                     |

| CCPRxH                                      | Capture/Com             | pare/PWM Re  | egister x (MSE      | 3)     |        |        |        |        | 355                 |

| CCPTMRS                                     | P4TSEL<1:0> P3TSEL<1:0> |              |                     | L<1:0> | C2TSE  | L<1:0> | C1TSE  | L<1:0> | 353                 |

| INTCON                                      | GIE                     | PEIE         | TMR0IE              | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 97                  |

| PIE1                                        | TMR1GIE                 | ADIE         | RCIE                | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 98                  |

| PIE2                                        | _                       | C2IE         | C1IE                | —      | BCLIE  | TMR6IE | TMR4IE | CCP2IE | 99                  |

| PR2                                         | Timer2 Peric            | od Register  |                     |        |        |        |        |        | 235*                |

| T2CON                                       | ON                      |              | CKPS<2:0>           |        |        | OUTP   | S<3:0> |        | 254                 |

| TMR2                                        | Timer2 Modu             | ule Register |                     |        |        |        |        |        | 235*                |

| PR4                                         | Timer4 Peric            | d Register   |                     |        |        |        |        |        | 235*                |

| T4CON                                       | ON                      |              | CKPS<2:0>           |        |        | OUTP   | S<3:0> |        | 254                 |

| TMR4                                        | Timer4 Modu             | ule Register |                     |        |        |        |        |        | 235*                |

| PR6                                         | Timer6 Peric            | d Register   |                     |        |        |        |        |        | 235*                |

| T6CON                                       | ON                      |              | CKPS<2:0>           |        |        | 254    |        |        |                     |

| TMR6                                        | Timer6 Modu             | ule Register |                     |        | •      |        |        |        | 235*                |

| TRISA                                       | —                       | _            | TRISA5              | TRISA4 | (1)    | TRISA2 | TRISA1 | TRISA0 | 151                 |

| TABLE 26-3: \$ | SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM |

|----------------|---------------------------------------------------|

|----------------|---------------------------------------------------|

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

## REGISTER 29-3: CLCxSEL0: MULTIPLEXER DATA 0 SELECT REGISTERS

| U-0            | U-0 | R/W-x/u         | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u | R/W-x/u |

|----------------|-----|-----------------|---------|--------------|------------------|---------|---------|

| —              | _   |                 |         | LCxD1        | IS<5:0>          |         |         |

| bit 7          |     | •               |         |              |                  |         | bit 0   |

|                |     |                 |         |              |                  |         |         |

| Legend:        |     |                 |         |              |                  |         |         |

| R = Readable b | bit | W = Writable bi | it      | U = Unimplen | nented bit, read | as '0'  |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |   |

|---------------------------------------------------------------------------------------------|---|

|                                                                                             | S |

| '1' = Bit is set '0' = Bit is cleared                                                       |   |

| bit 7-6 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 5-0 | LCxD1S<5:0>: Input Data 1 Selection Control bits        |

|         | See Table 29-1 for signal names associated with inputs. |

#### REGISTER 29-4: CLCxSEL1: MULTIPLEXER DATA 1 SELECT REGISTERS

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|

| —     | —   |         | LCxD2S<5:0> |         |         |         |         |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD2S<5:0>: Input Data 2 Selection Control bits

See Table 29-1 for signal names associated with inputs.

#### REGISTER 29-5: CLCxSEL2: MULTIPLEXER DATA 2 SELECT REGISTERS

| U-0   | U-0 | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|-------------|---------|---------|---------|---------|---------|--|

| —     | —   | LCxD3S<5:0> |         |         |         |         |         |  |

| bit 7 |     |             |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| 0' |

|----|

| (  |