Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1614-i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr               | Name                | Bit 7                | Bit 6                                                    | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all<br>other Resets |

|--------------------|---------------------|----------------------|----------------------------------------------------------|-------|----------|----------|-------|--------|-----------|----------------------|------------------------------|

| Bank 4             | Sank 4              |                      |                                                          |       |          |          |       |        |           |                      |                              |

| 20Ch               | WPUA                | —                    |                                                          | WPUA5 | WPUA4    | WPUA3    | WPUA2 | WPUA1  | WPUA0     | 11 1111              | 11 1111                      |

| 20Dh               | WPUB <sup>(4)</sup> | WPUB7                | WPUB6                                                    | WPUB5 | WPUB4    | —        | —     | —      | —         | 1111                 | 1111                         |

| 20Eh               | WPUC                | WPUC7 <sup>(4)</sup> | WPUC6 <sup>(4)</sup>                                     | WPUC5 | WPUC4    | WPUC3    | WPUC2 | WPUC1  | WPUC0     | 1111 1111            | 111 1111                     |

| 20Fh               | —                   | Unimplemented        | Inimplemented                                            |       |          |          |       |        |           |                      | —                            |

| 210h               | —                   | Unimplemented        | Jnimplemented                                            |       |          |          |       |        |           | —                    | —                            |

| 211h               | SSP1BUF             |                      | Synchronous Serial Port Receive Buffer/Transmit Register |       |          |          |       |        |           | xxxx xxxx            | xxxx xxxx                    |

| 212h               | SSP1ADD             |                      |                                                          |       | ADD      | <7:0>    |       |        |           | 0000 0000            | 0000 0000                    |

| 213h               | SSP1MSK             |                      |                                                          |       | MSK      | <7:0>    |       |        |           | 1111 1111            | 1111 1111                    |

| 214h               | SSP1STAT            | SMP                  | CKE                                                      | D/A   | Р        | S        | R/W   | UA     | BF        | 0000 0000            | 0000 0000                    |

| 215h               | SSP1CON1            | WCOL                 | SSPOV                                                    | SSPEN | СКР      |          | SSPM  | 1<3:0> |           | 0000 0000            | 0000 0000                    |

| 216h               | SSP1CON2            | GCEN                 | ACKSTAT                                                  | ACKDT | ACKEN    | RCEN     | PEN   | RSEN   | SEN       | 0000 0000            | 0000 0000                    |

| 217h               | SSP1CON3            | ACKTIM               | ACKTIM PCIE SCIE BOEN SDAHT SBCDE AHEN DHEN              |       |          |          |       |        | 0000 0000 | 0000 0000            |                              |

| 218h<br>to<br>21Fh | _                   | Unimplemented        |                                                          |       | <u>.</u> | <u>.</u> |       |        | ·         | _                    | _                            |

# TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

| <b>TABLE 3-14</b> : | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) |  |

|---------------------|-----------------------------------|-------------|--|

|                     |                                   |             |  |

| Addr         Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         Value on POR, BOR           Bank 17         Bank 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Value on all other Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 88Ch         AT1CLK         —         —         —         —         —         —         CS0        0           88Dh         AT1SIG         —         —         —         —         —         —         CS0        0           88Dh         AT1SIG         —         —         —         —         —         SSEL<2:0>        000           88Eh         AT1CSEL1         —         —         —         —         CP1S<2:0>        000           88Fh         AT1CC1L         —         —         —         —         CC1<7:0>         0000 0000           890h         AT1CC1H         —         —         —         —         —         —         0000 0000           891h         AT1CC0N1         CC1EN         —         —         —         —         —         —         —         —         —         —         —         …         0000 0000         0000           891h         AT1CC0N1         CC1EN         —         —         —         —         —         CC1<9:8>         —         …         …         …         …         …         …         …         …         …         …                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| 88Dh         AT1SIG         —         —         —         —         SSEL<2:0>        000        000        000        000        000        000        000        000        000         0000 0000        000         0000 0000        000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         0000 0000         00000         00000         00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| 88Eh         AT1CSEL1         —         —         —         —         —         CP1S<2:0>        000           88Fh         AT1CC1L         CC1<7:0>         0000 0000         0000 0000           890h         AT1CC1H         —         —         —         —         —         —         0000 0000           890h         AT1CC1H         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                         |

| 88Fh         AT1CC1L         CC1<7:0>         0000 0000           890h         AT1CC1H         -         -         -         -         CC1<9:8>         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 000                       |

| 890h         AT1CC1H         -         -         -         -         -         CC1<9:8>        000           891h         AT1CC0N1         CC1EN         -         -         CC1POL         CAP1P         -         -         CC1MODE         00         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 000                       |

| 891h         AT1CCON1         CC1EN         —         —         CC1POL         CAP1P         —         —         CC1MODE         00         00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0000 0000                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 00                     |

| 892h AT1CSEL2 — — — — — — CP2S<2:0>000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 000                       |

| 893h AT1CC2L CC2<7:0> 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                 |

| 894h AT1CC2H — — — — — — — CC2<9:8>000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 000                       |

| 895h AT1CCON2 CC2EN — — CC2POL CAP2P — — CC2MODE 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00 00                     |

| 896h AT1CSEL3 — — — — — — CP3S<2:0>000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 000                       |

| 897h AT1CC1L CC3<7:0> 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000 0000                 |

| 898h         AT1CC1H         —         —         —         —         —         CC3<9:8>        000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 000                       |

| 899h AT1CCON1 CC3EN — — CC3POL CAP3P — — CC3MODE 00 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00 00                     |

| 89Ah     Image: Second se |                           |

| Bank 18-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| Bank 1        | 8-26 |               |  |  |

|---------------|------|---------------|--|--|

| x0Ch/<br>x8Ch | _    | Unimplemented |  |  |

| _             |      |               |  |  |

| x1Fh/<br>x9Fh |      |               |  |  |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

\_\_\_\_

### Value on Addr Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR, BOR

### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-14:

| Banks              | <u>s 27</u> |               |                |     |         |          |           |           |           | _         |           |

|--------------------|-------------|---------------|----------------|-----|---------|----------|-----------|-----------|-----------|-----------|-----------|

| D80h<br>to<br>D8Bh | _           | Unimplemented | l              |     |         |          |           |           |           | _         | _         |

| D8Ch               | SMT1TMRL    |               |                |     | SMT1TN  | /IR<7:0> |           |           |           | 0000 0000 | 0000 0000 |

| D8Dh               | SMT1TMRH    |               |                |     | SMT1TM  | IR<15:8> |           |           |           | 0000 0000 | 0000 0000 |

| D8Eh               | SMT1TMRU    |               |                |     | SMT1TMI | R<23:16> |           |           |           | 0000 0000 | 0000 0000 |

| D8Fh               | SMT1CPRL    |               | SMT1CPR<7:0>   |     |         |          |           |           |           |           |           |

| D90h               | SMT1CPRH    |               |                |     | SMT1CP  | R<15:8>  |           |           |           | xxxx xxxx | XXXX XXXX |

| D91h               | SMT1CPRU    |               |                |     | SMT1CP  | R<23:16> |           |           |           | XXXX XXXX | XXXX XXXX |

| D92h               | SMT1CPWL    |               |                |     | SMT1CF  | PW<7:0>  |           |           |           | XXXX XXXX | XXXX XXXX |

| D93h               | SMT1CPWH    |               |                |     | SMT1CP  | W<15:8>  |           |           |           | XXXX XXXX | XXXX XXXX |

| D94h               | SMT1CPWU    |               |                |     | SMT1CPV | W<23:16> |           |           |           | xxxx xxxx | xxxx xxxx |

| D95h               | SMT1PRL     |               | SMT1PR<7:0>    |     |         |          |           |           |           |           | XXXX XXXX |

| D96h               | SMT1PRH     | SMT1PR<15:8>  |                |     |         |          |           |           | XXXX XXXX | xxxx xxxx |           |

| D97h               | SMT1PRU     |               | SMT1PR<23:16>  |     |         |          |           |           |           | XXXX XXXX | xxxx xxxx |

| D98h               | SMT1CON0    | EN            | _              | STP | WPOL    | SPOL     | CPOL      | SMT1P     | S<1:0>    | 0-00 0000 | 0-00 0000 |

| D99h               | SMT1CON1    | SMT1GO        | REPEAT         | —   | —       |          | MODE      | <3:0>     |           | 00 0000   | 00 0000   |

| D9Ah               | SMT1STAT    | CPRUP         | CPWUP          | RST | —       | _        | TS        | WS        | AS        | 000000    | 000000    |

| D9Bh               | SMT1CLK     | —             | _              | _   | —       | _        |           | CSEL<2:0> |           | 000       | 000       |

| D9Ch               | SMT1SIG     | —             | _              | —   |         |          | SSEL<4:0> |           |           | 0 0000    | 0 0000    |

| D9Dh               | SMT1WIN     | _             |                | _   |         |          | WSEL<4:0> |           |           | 0 0000    | 0 0000    |

| D9Eh               | SMT2TMRL    |               |                |     | SMT2TM  | /IR<7:0> |           |           |           | 0000 0000 | 0000 0000 |

| D9Fh               | SMT2TMRH    |               |                |     | SMT2TM  | IR<15:8> |           |           |           | 0000 0000 | 0000 0000 |

| DA0h               | SMT2TMRU    |               | SMT2TMR<23:16> |     |         |          |           |           |           | 0000 0000 | 0000 0000 |

| DA1h               | SMT2CPRL    |               |                |     | SMT2CF  | PR<7:0>  |           |           |           | xxxx xxxx | xxxx xxxx |

| DA2h               | SMT2CPRH    |               |                |     | SMT2CP  | 'R<15:8> |           |           |           | XXXX XXXX | xxxx xxxx |

| DA3h               | SMT2CPRU    |               |                |     | SMT2CPI | R<23:16> |           |           |           | xxxx xxxx | XXXX XXXX |

| DA4h               | SMT2CPWL    |               |                |     | SMT2CF  | PW<7:0>  |           |           |           | XXXX XXXX | XXXX XXXX |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

Value on all

other Resets

# TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name                     | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3           | Bit 2         | Bit 1      | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|--------------------|--------------------------|---------------|-------|-------|-------|-----------------|---------------|------------|-------|----------------------|---------------------------|

| Banks              | 28                       |               |       |       |       |                 |               |            |       |                      |                           |

| E0Ch<br>to<br>E0Eh | _                        | Unimplemented |       |       |       |                 |               |            |       | —                    | —                         |

| E0Fh               | PPSLOCK                  | —             | _     |       | —     | — — — PPSLOCKEI |               |            |       |                      | 0                         |

| E10h               | INTPPS                   | —             | _     |       |       |                 | INTPPS<4:0>   |            |       | 0 0010               | 0 0010                    |

| E11h               | TOCKIPPS                 | —             | _     |       |       |                 | T0CKIPPS<4:0> |            |       | 0 0010               | 0 0010                    |

| E12h               | T1CKIPPS                 | —             | —     | _     |       |                 | T1CKIPPS<4:0> |            |       | 0 0101               | 0 0101                    |

| E13h               | T1GPPS                   | —             | —     | _     |       |                 | T1GPPS<4:0>   |            |       | 0 0100               | 0 0100                    |

| E14h               | CCP1PPS                  | —             | —     | —     |       |                 | CCP1PPS<4:0>  |            |       | 1 0101               | 1 0101                    |

| E15h               | CCP2PPS                  | —             | —     | _     |       | CCP2PPS<4:0>    |               |            |       |                      | 1 0011                    |

| E16h               | ATINPPS                  | —             | —     | _     |       | ATINPPS<4:0>    |               |            |       |                      | 1 0101                    |

| E17h               | CWGINPPS                 | —             | —     | —     |       | CWGINPPS<4:0>   |               |            |       |                      | 0 0010                    |

| E18h               | T2PPS                    | —             | —     | _     |       | T2PPS<4:0>      |               |            |       |                      | 0 0101                    |

| E19h               | T3CKIPPS                 | —             | —     | _     |       | T3CKIPPS<4:0>   |               |            |       |                      | 1 0101                    |

| E1Ah               | T3GPPS                   | —             | —     | _     |       |                 | T3GPPS<4:0>   |            |       | 1 0100               | 1 0100                    |

| E1Bh               | T4PPS                    | —             | —     | _     |       |                 | T4PPS<4:0>    |            |       | 1 0001               | 1 0001                    |

| E1Ch               | T5CKIPPS                 | —             | —     | _     |       |                 | T5CKIPPS<4:0> |            |       | 1 0000               | 1 0000                    |

| E1Dh               | T5GPPS                   | —             | —     | _     |       |                 | T5GPPS<4:0>   |            |       | 1 0011               | 1 0011                    |

| E1Eh               | T6PPS                    | —             | —     | _     |       |                 | T6PPS<4:0>    |            |       | 0 0011               | 0 0011                    |

| E1Fh               | ATCC1PPS                 | —             | —     | _     |       |                 | ATCC1PPS<4:0> | ,          |       | 1 0011               | 1 0011                    |

| E20h               | SSPCLKPPS <sup>(3)</sup> | —             | —     | _     |       |                 | SSPCLKPPS<4:0 | >          |       | 1 0000               | 1 0000                    |

| E20h               | SSPCLKPPS <sup>(4)</sup> | —             | _     |       |       | SSPCLKPPS<4:0>  |               |            |       |                      | 0 1110                    |

| E21h               | SSPDATPPS <sup>(3)</sup> | —             | —     | _     |       | SSPDATPPS<4:0>  |               |            |       |                      | 1 0001                    |

| E21h               | SSPDATPPS <sup>(4)</sup> | —             | —     |       |       |                 | SSPDATPPS<4:0 | >          |       | 1 0001               | 0 1100                    |

| E22h               | SSPSSPPS <sup>(3)</sup>  | —             | _     |       |       |                 | SSPSSPPS<4:0> | , <u> </u> |       | 1 0011               | 1 0011                    |

| E22h               | SSPSSPPS <sup>(4)</sup>  | —             | _     | _     |       |                 | SSPSSPPS<4:0> | •          |       | 1 0110               | 1 0110                    |

| E23h               | ATCC2PPS                 | _             | _     | _     |       |                 | ATCC2PPS<4:0> | •          |       | 1 0100               | 1 0100                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

# 4.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

# 4.7 Register Definitions: Device ID

# **REGISTER 4-4: DEVID: DEVICE ID REGISTER**

|   | R      | R       | R               | R      | R                                                                      | R                          |  |  |  |  |

|---|--------|---------|-----------------|--------|------------------------------------------------------------------------|----------------------------|--|--|--|--|

|   |        |         | DEV<            | :13:8> |                                                                        |                            |  |  |  |  |

|   | bit 13 | 3 bit 8 |                 |        |                                                                        |                            |  |  |  |  |

|   |        |         |                 |        |                                                                        |                            |  |  |  |  |

| R | R      | R       | R               | R      | R                                                                      | R                          |  |  |  |  |

|   |        | DEV     | <7:0>           |        |                                                                        |                            |  |  |  |  |

|   |        |         |                 |        |                                                                        | bit 0                      |  |  |  |  |

|   | R      |         | bit 13<br>R R R | DEV<   | DEV<13:8>           bit 13           R         R           R         R | DEV<13:8>           bit 13 |  |  |  |  |

# Legend:

R = Readable bit

'1' = Bit is set

bit 13-0 **DEV<13:0>:** Device ID bits

| Device      | DEVID<13:0> Values               |  |  |  |  |  |  |  |

|-------------|----------------------------------|--|--|--|--|--|--|--|

| PIC16F1614  | 11 0000 0111 1000 <b>(3078h)</b> |  |  |  |  |  |  |  |

| PIC16LF1614 | 11 0000 0111 1010 <b>(307Ah)</b> |  |  |  |  |  |  |  |

| PIC16F1618  | 11 0000 0111 1001 <b>(3079h)</b> |  |  |  |  |  |  |  |

| PIC16LF1618 | 11 0000 0111 1011 <b>(307Bh)</b> |  |  |  |  |  |  |  |

'0' = Bit is cleared

### REGISTER 4-5: REVID: REVISION ID REGISTER

|       |   | R      | R     | R     | R      | R | R     |  |  |  |  |

|-------|---|--------|-------|-------|--------|---|-------|--|--|--|--|

|       |   |        |       | REV<  | :13:8> |   |       |  |  |  |  |

|       |   | bit 13 | bit 8 |       |        |   |       |  |  |  |  |

| r     |   |        |       |       |        |   |       |  |  |  |  |

| R     | R | R      | R     | R     | R      | R | R     |  |  |  |  |

|       |   |        | REV   | <7:0> |        |   |       |  |  |  |  |

| bit 7 |   |        |       |       |        |   | bit 0 |  |  |  |  |

| -     |   |        |       |       |        |   |       |  |  |  |  |

### Legend:

R = Readable bit '1' = Bit is set

'0' = Bit is cleared

bit 13-0 **REV<13:0>:** Revision ID bits

# 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

# 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

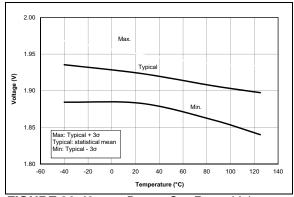

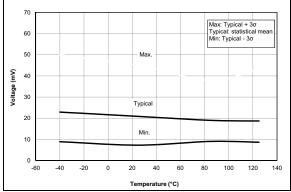

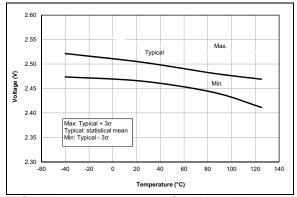

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|--|--|

| 11         | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

| 1.0        | 37     | Awake       | Active   | Waits for BOR ready                                                 |  |  |  |  |  |

| 10         | Х      | Sleep       | Disabled | (BORRDY = 1)                                                        |  |  |  |  |  |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |  |  |

|            | 0      | х           | Disabled | Begins immediately                                                  |  |  |  |  |  |

| 00         | Х      | Х           | Disabled | (BORRDY = x)                                                        |  |  |  |  |  |

TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

# 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

| R/W-0/0                                                                          | R/W-0/0                           | R/W-0/0           | R/W-0/0 | R/W-0/0             | R/W-0/0                            | R/W-0/0 | R/W-0/0 |  |  |

|----------------------------------------------------------------------------------|-----------------------------------|-------------------|---------|---------------------|------------------------------------|---------|---------|--|--|

|                                                                                  |                                   |                   | HADR<   | 15:8> <b>(1, 2)</b> |                                    |         |         |  |  |

| bit 7                                                                            | bit 7 bit 0                       |                   |         |                     |                                    |         |         |  |  |

|                                                                                  |                                   |                   |         |                     |                                    |         |         |  |  |

| Legend:                                                                          |                                   |                   |         |                     |                                    |         |         |  |  |

| R = Readable                                                                     | R = Readable bit W = Writable bit |                   |         |                     | U = Unimplemented bit, read as '0' |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all |                                   |                   |         | R/Value at all o    | ther Resets                        |         |         |  |  |

| '1' = Bit is set                                                                 |                                   | '0' = Bit is clea | ared    |                     |                                    |         |         |  |  |

### REGISTER 11-14: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

# REGISTER 11-15: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-0/0        | R/W-0/0 | R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0         | R/W-0/0 | R/W-0/0 |

|----------------|---------|------------------|---------|--------------------|-----------------|---------|---------|

|                |         |                  | HADR<   | 7:0> <b>(1, 2)</b> |                 |         |         |

| bit 7          |         |                  |         |                    |                 |         | bit 0   |

|                |         |                  |         |                    |                 |         |         |

| Legend:        |         |                  |         |                    |                 |         |         |

| R = Readable I | hit     | W = Writable bit | ł       | =   Inimplen       | nented hit read | as 'O'  |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRH/L form a 16-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SCANGO = 0 (SCANCON0 register).

- 2: While SCANGO = 1 (SCANCON0 register), writing to this register is ignored.

|             | Outrast Olamak          |       | PIC16(L)F161 | B     | PIC16(L)F1614 |       |

|-------------|-------------------------|-------|--------------|-------|---------------|-------|

| RxyPPS<4:0> | Output Signal           | PORTA | PORTB        | PORTC | PORTA         | PORTO |

| llxxx       | Reserved                | •     | •            | ٠     | •             | •     |

| 10111       | Reserved                | •     | •            | •     | •             | •     |

| 10110       | Reserved                | •     | •            | •     | •             | •     |

| 10101       | Reserved                | •     | •            | •     | •             | •     |

| 10100       | Reserved                | •     | •            | •     | •             | •     |

| 10011       | DT                      | •     | •            | •     | •             | •     |

| 10010       | TX/CK                   | •     | •            | •     | •             | •     |

| 10001       | SDO/SDA <sup>(1)</sup>  | •     | •            | •     | •             | •     |

| 10000       | SCK/SCL <sup>(1)</sup>  | •     | •            | •     | •             | •     |

| 01111       | PWM4_out                | •     | •            | •     | •             | •     |

| 01110       | PWM3_out                | •     | •            | •     | •             | •     |

| 01101       | CCP2_out                | •     | •            | •     | •             | •     |

| 01100       | CCP1_out                | •     | •            | •     | •             | •     |

| 01011       | CWG1OUTD <sup>(1)</sup> | •     | •            | •     | •             | •     |

| 01010       | CWG1OUTC <sup>(1)</sup> | •     | •            | •     | •             | •     |

| 01001       | CWG1OUTB <sup>(1)</sup> | •     | •            | •     | •             | •     |

| 01000       | CWG1OUTA <sup>(1)</sup> | •     | •            | •     | •             | •     |

| 00111       | LC4_out                 | •     | •            | ٠     | •             | •     |

| 00110       | LC3_out                 | •     | •            | •     | •             | •     |

| 00101       | LC2_out                 | •     | •            | •     | •             | •     |

| 00100       | LC1_out                 | •     | •            | ٠     | •             | •     |

| 00011       | ZCD1_out                | •     | •            | •     | •             | •     |

| 00010       | sync_C2OUT              | •     | •            | •     | •             | •     |

| 00001       | sync_C1OUT              | •     | •            | ٠     | •             | •     |

| 00000       | LATxy                   | •     | •            | •     | •             | •     |

| TABLE 13-2: AV | AILABLE PORTS FOR OUTPUT BY PERIPHERAL <sup>(2)</sup> |

|----------------|-------------------------------------------------------|

|----------------|-------------------------------------------------------|

**Note 1:** TRIS control is overridden by the peripheral as required.

2: Unsupported peripherals will output a '0'.

# **19.0 COMPARATOR MODULE**

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- PWM shutdown

- Programmable and Fixed Voltage Reference

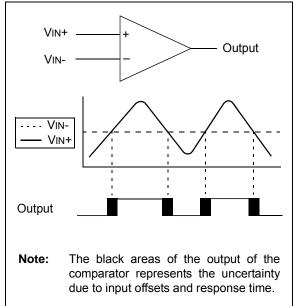

# **19.1** Comparator Overview

A single comparator is shown in Figure 19-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 19-1.

### TABLE 19-1: COMPARATOR AVAILABILITY PER DEVICE

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1618 | •  | •  |

| PIC16(L)F1614 | •  | •  |

### FIGURE 19-1: SINGLE COMPARATOR

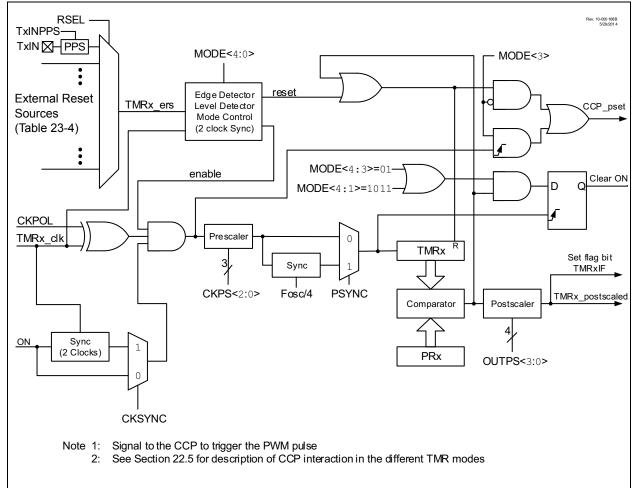

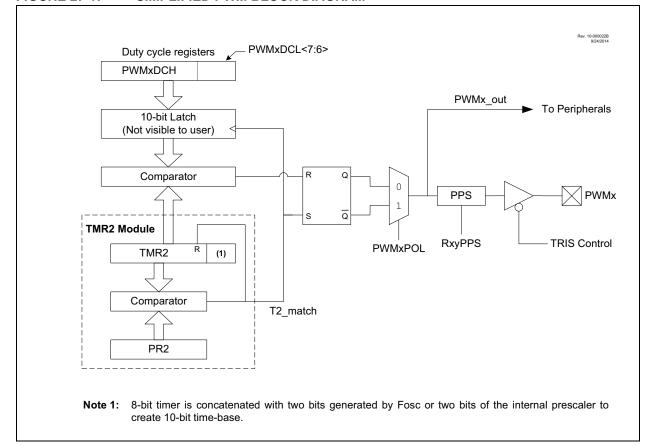

# 23.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- · 8-bit period register

- · Selectable external hardware timer Resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- · Alternate clock sources

- Interrupt-on-period

### FIGURE 23-1: TIMER2 BLOCK DIAGRAM

- Three modes of operation:

- Free Running Period

- One-shot

- Monostable

See Figure 23-1 for a block diagram of Timer2. See Figure 23-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

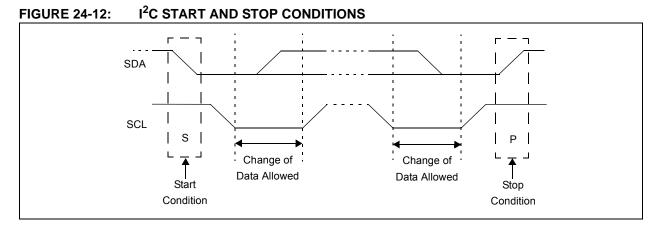

### 24.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 24-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

# 24.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

# 24.4.7 RESTART CONDITION

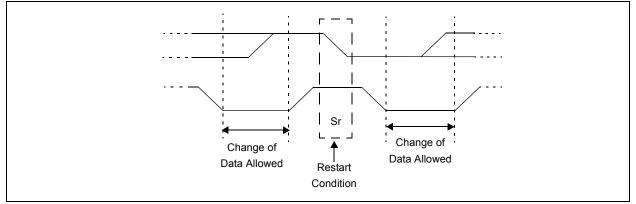

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 24-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

### 24.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

## FIGURE 24-13: I<sup>2</sup>C RESTART CONDITION

| TADLE 20-1. EXAMIFLE FWW FREQUENCIES AND RESOLUTIONS (FUSC = 20 MITZ) | TABLE 26-1: | <b>EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (I</b> | Fosc = 20 MHz) |

|-----------------------------------------------------------------------|-------------|---------------------------------------------------|----------------|

|-----------------------------------------------------------------------|-------------|---------------------------------------------------|----------------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|