Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1614-i-st |

| PC |

|----|

|    |

| TΔRI F 3-14. | SPECIAL | FUNCTION REGISTER SUMMARY (CONTINUE) | D) |

|--------------|---------|--------------------------------------|----|

|              |         |                                      |    |

| Addr               | Name      | Bit 7               | Bit 6 | Bit 5 | Bit 4    | Bit 3  | Bit 2 | Bit 1  | Bit 0 | Value on POR, BOR | Value on all other Resets |  |  |

|--------------------|-----------|---------------------|-------|-------|----------|--------|-------|--------|-------|-------------------|---------------------------|--|--|

| Banks              | Banks 15  |                     |       |       |          |        |       |        |       |                   |                           |  |  |

| 78Ch<br>to<br>790h | _         | Unimplemented       |       |       |          |        |       |        |       | _                 | _                         |  |  |

| 791h               | CRCDATL   |                     |       |       | DAT<     | 7:0>   |       |        |       | xxxx xxxx         | xxxx xxxx                 |  |  |

| 792h               | CRCDATH   |                     |       |       | DAT<     | 15:8>  |       |        |       | xxxx xxxx         | xxxx xxxx                 |  |  |

| 793h               | CRCACCL   |                     |       |       | ACC-     | <7:0>  |       |        |       | 0000 0000         | 0000 0000                 |  |  |

| 794h               | CRCACCH   |                     |       |       | ACC<     | 15:8>  |       |        |       | 0000 0000         | 0000 0000                 |  |  |

| 795h               | CRCSHIFTL |                     |       |       | SHIFT    | <7:0>  |       |        |       | 0000 0000         | 0000 0000                 |  |  |

| 796h               | CRCSHIFTH |                     |       |       | SHIFT    | <15:8> |       |        |       | 0000 0000         | 0000 0000                 |  |  |

| 797h               | CRCXORL   |                     |       |       | XOR<7:1> |        |       |        | 1     | xxxx xxx-         | xxxx xxx-                 |  |  |

| 798h               | CRCXORH   |                     |       |       | XOR<     | 15:8>  |       |        |       | xxxx xxxX         | xxxx xxxX                 |  |  |

| 799h               | CRCCON0   | EN                  | CRCGO | BUSY  | ACCM     | _      | _     | SHIFTM | FULL  | 000000            | 0000 -00                  |  |  |

| 79Ah               | CRCCON1   | DLEN<3:0> PLEN<3:0> |       |       |          |        |       |        |       | 0000 0000         | 0000 0000                 |  |  |

| 79Bh<br>to<br>79Fh | _         | Unimplemented       |       |       |          |        |       |        |       | _                 | _                         |  |  |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

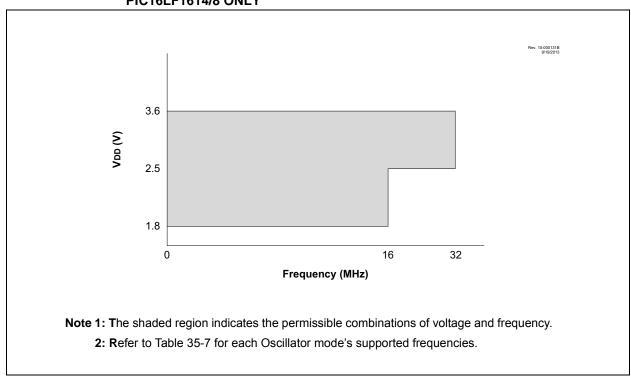

Note 1: PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

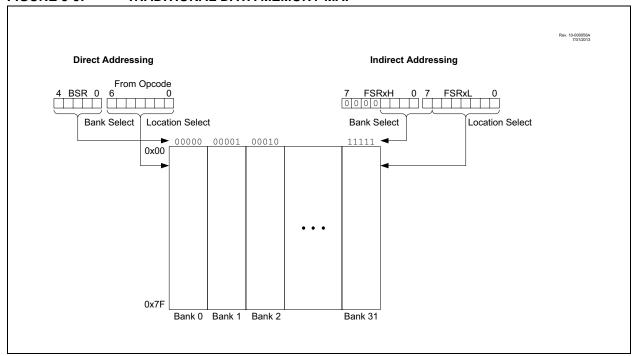

# 3.6.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

FIGURE 3-9: TRADITIONAL DATA MEMORY MAP

# REGISTER 7-5: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0   | R/W-0/0 | R/W-0/0   | R/W-0/0   | R/W-0/0 |

|---------|---------|-----------|-----------|---------|-----------|-----------|---------|

| SCANIE  | CRCIE   | SMT2PWAIE | SMT2PRAIE | SMT2IE  | SMT1PWAIE | SMT1PRAIE | SMT1IE  |

| bit 7   |         |           |           |         |           |           | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | SCANIE: Scanner Interrupt Enable bit                                 |

|-------|----------------------------------------------------------------------|

|       | 1 = Enables the scanner interrupt                                    |

|       | 0 = Disables the scanner interrupt                                   |

| bit 6 | CRCIE: CRC Interrupt Enable bit                                      |

|       | 1 = Enables the CRC interrupt                                        |

|       | 0 = Disables the CRC interrupt                                       |

| bit 5 | <b>SMT2PWAIE</b> : SMT2 Pulse Width Acquisition Interrupt Enable bit |

|       | 1 = Enables the SMT2 acquisition interrupt                           |

|       | 0 = Disables the SMT2 acquisition interrupt                          |

| bit 4 | SMT2PRAIE: SMT2 Period Acquisition Interrupt Enable bit              |

|       | 1 = Enables the SMT2 acquisition interrupt                           |

|       | 0 = Disables the SMT2 acquisition interrupt                          |

| bit 3 | SMT2IE: SMT2 Match Interrupt Enable bit                              |

|       | 1 = Enables the SMT2 period match interrupt                          |

|       | 0 = Disables the SMT2 period match interrupt                         |

| bit 2 | <b>SMT1PWAIE</b> : SMT1 Pulse Width Acquisition Interrupt Enable bit |

|       | 1 = Enables the SMT1 acquisition interrupt                           |

|       | 0 = Disables the SMT1 acquisition interrupt                          |

| bit 1 | SMT1PRAIE: SMT1 Period Acquisition Interrupt Enable bit              |

|       | 1 = Enables the SMT1 acquisition interrupt                           |

|       | 0 = Disables the SMT1 acquisition interrupt                          |

| bit 0 | SMT1IE: SMT1 Match Interrupt Enable bit                              |

|       | 1 = Enables the SMT1 period match interrupt                          |

|       | 0 = Disables the SMT1 period match interrupt                         |

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

# 19.8 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section35.0** "Electrical **Specifications**" for more details.

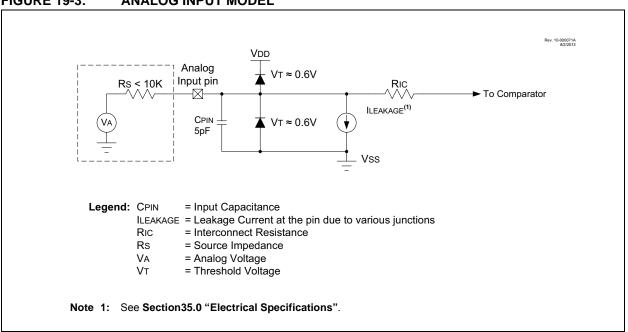

# 19.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 19-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to  $V_{\rm DD}$  and  $V_{\rm SS}$ . The analog input, therefore, must be between  $V_{\rm SS}$  and  $V_{\rm DD}$ . If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 19-3: ANALOG INPUT MODEL

# 20.0 ZERO-CROSS DETECTION (ZCD) MODULE

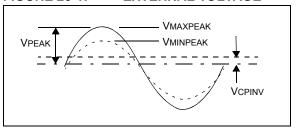

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero crossing threshold is the zero crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 20-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- · A/C period measurement

- · Accurate long term time measurement

- · Dimmer phase delayed drive

- · Low EMI cycle switching

## 20.1 External Resistor Selection

The ZCD module requires a current limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu A$ . Refer to Equation 20-1 and Figure 20-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

# **EQUATION 20-1: EXTERNAL RESISTOR**

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

#### FIGURE 20-1: EXTERNAL VOLTAGE

# 21.2 Register Definitions: Option Register

# **REGISTER 21-1: OPTION REG: OPTION REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         | PS<2:0> |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 **WPUEN:** Weak Pull-Up Enable bit

1 = All weak pull-ups are disabled (except  $\overline{MCLR}$ , if it is enabled) 0 = Weak pull-ups are enabled by individual WPUx latch values

bit 6 **INTEDG:** Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TMR0CS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 TMR0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is not assigned to the Timer0 module0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

Bit Value Timer0 Rate 000 1:2 1:4 001 010 1:8 011 1:16 100 1:32 101 1:64 110 1:128 1:256 111

#### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name       | Bit 7                                       | Bit 6              | Bit 5  | Bit 4  | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Register on Page |

|------------|---------------------------------------------|--------------------|--------|--------|-------|---------|--------|--------|------------------|

| ADCON2     |                                             | TRIGSEL<4:0> — — — |        |        |       |         |        |        | 197              |

| INTCON     | GIE                                         | PEIE               | TMR0IE | INTE   | IOCIE | TMR0IF  | INTF   | IOCIF  | 97               |

| OPTION_REG | WPUEN                                       | INTEDG             | TMR0CS | TMR0SE | PSA   | PS<2:0> |        |        | 222              |

| TMR0       | Holding Register for the 8-bit Timer0 Count |                    |        |        |       |         |        |        | 220*             |

| TRISA      | _                                           | _                  | TRISA5 | TRISA4 | (1)   | TRISA2  | TRISA1 | TRISA0 | 151              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

Page provides register information.

Note 1: Unimplemented, read as '1'.

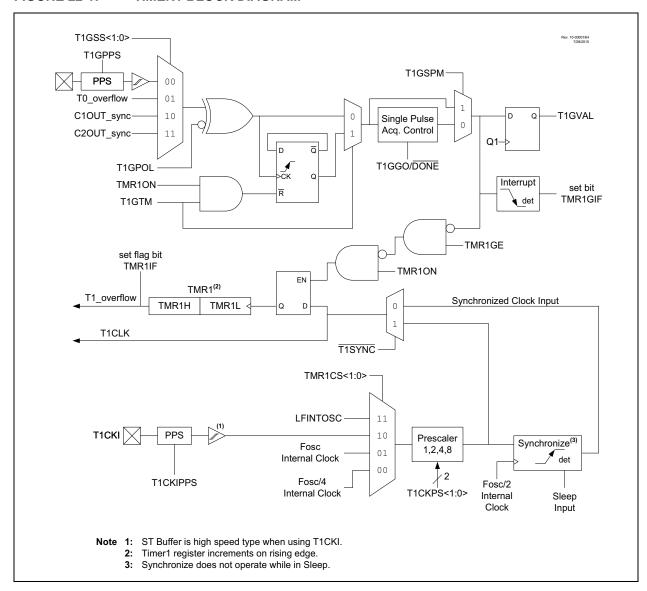

# 22.0 TIMER1/3/5 MODULE WITH GATE CONTROL

The Timer1/3/5 modules are a 16-bit timers/counters with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- · Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- · Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 22-1 is a block diagram of the Timer1 module.

Note: Three identical Timer1 modules are implemented on this device. The timers are named Timer1, Timer3, and Timer5. All references to Timer1 apply as well to Timer3 and Timer5, as well as references to their associated registers.

## FIGURE 22-1: TIMER1 BLOCK DIAGRAM

## REGISTER 22-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u     | R-x/x  | R/W-0/u | R/W-0/u |

|---------|---------|---------|---------|----------------|--------|---------|---------|

| TMR1GE  | T1GPOL  | T1GTM   | T1GSPM  | T1GGO/<br>DONE | T1GVAL | T1GS    | S<1:0>  |

| bit 7   |         |         |         |                |        |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHC = Bit is cleared by hardware

bit 7 TMR1GE: Timer1 Gate Enable bit

If TMR1ON = 0: This bit is ignored If TMR1ON = 1:

1 = Timer1 counting is controlled by the Timer1 gate function

0 = Timer1 counts regardless of Timer1 gate function

bit 6 T1GPOL: Timer1 Gate Polarity bit

1 = Timer1 gate is active-high (Timer1 counts when gate is high)

0 = Timer1 gate is active-low (Timer1 counts when gate is low)

bit 5 **T1GTM:** Timer1 Gate Toggle Mode bit

1 = Timer1 Gate Toggle mode is enabled

0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared

Timer1 gate flip-flop toggles on every rising edge.

bit 4 T1GSPM: Timer1 Gate Single-Pulse Mode bit

1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate

0 = Timer1 gate Single-Pulse mode is disabled

bit 3 T1GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit

1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge

0 = Timer1 gate single-pulse acquisition has completed or has not been started

bit 2 T1GVAL: Timer1 Gate Value Status bit

Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.

Unaffected by Timer1 Gate Enable (TMR1GE).

bit 0 T1GSS<1:0>: Timer1 Gate Source Select bits

11 = Comparator 2 optionally synchronized output (C2 OUT sync)

10 =Comparator 1 optionally synchronized output (C1\_OUT\_sync)

01 =Timer0 overflow output (T0\_overflow)

00 =Timer1 gate pin (T1G)

# 23.4 Timer2 Interrupt

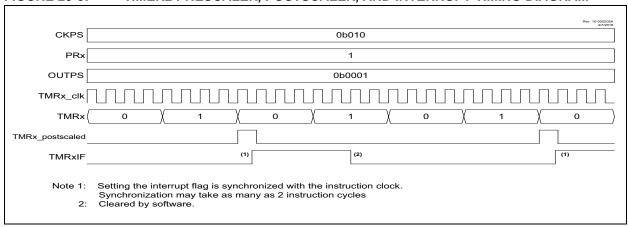

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE1 register. Interrupt timing is illustrated in Figure 23-3.

FIGURE 23-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

#### 26.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section22.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note

Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, Tlmer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 26.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (MODE<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

#### 26.2.4 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 26.2.5 CAPTURE OUTPUT

When in Compare mode, the CCP will provide an output upon the 16-bit value of the CCPRxH:CCPRxL register pair matching the TMR1H:TMR1L register pair. The compare output depends on which Compare mode the CCP is configured as. If the MODE bits of CCPxCON register are equal to '1011' or '1010', the CCP module will output high, while TMR1 is equal to CCPRxH:CCPRxL register pair. This means that the pulse width is determined by the TMR1 prescaler. If the MODE bits of CCPxCON are equal to '0001' or '0010', the output will toggle upon a match, going from '0' to '1' or vice-versa. If the MODE bits of CCPxCON are equal to '1001', the output is cleared on a match, and if the MODE bits are equal to '1000', the output is set on a match. This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an external Reset signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module. In addition, the CCPx pin output can be mapped to output pins through the use of PPS (see Section13.2 "PPS Outputs").

# REGISTER 30-4: SMTxCLK: SMT CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|-----------|---------|

| _     | _   | _   | _   | _   |         | CSEL<2:0> |         |

| bit 7 |     |     |     |     |         |           | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared q = Value depends on condition

bit 7-3 **Unimplemented**: Read as '0'

bit 2-0 CSEL<2:0>: SMT Clock Selection bits

111 = Reserved 110 = AT1\_perclk 101 = MFINTOSC 100 = MFINTOSC/16

011 = LFINTOSC

010 = HFINTOSC 16 MHz

001 = Fosc/4 000 = Fosc

#### 31.2.5 VALID BIT

Several values used by the AT module must be calculated from external signals. As such, these values may be inaccurate for a period of time after the angular timer starts up. Because of this, the module will not output signals or trigger interrupts for a period of time after the module is enabled, or under certain other conditions that might jeopardize accurate output values. This output inhibition is indicated by the read-only VALID bit of the ATxCON1 being clear.

The following cases will clear the VALID bit in hardware:

- · Any write to ATxRES register pair

- Phase counter overflow (ATxPHS register pair) clocked beyond 0x3FF)

- · In-Circuit Debugger halt

- EN = 0

- ATxPER register pair = 0

- · Device Reset

As long as the VALID bit is cleared, the following occurs:

- Period clock is not output and associated interrupts do not trigger.

- Missed pulse is not output and associated interrupts do not trigger.

- Phase clock is not output and associated interrupts do not trigger.

- · Phase counter does not increment.

- Capture logic does not function and associated interrupts do not trigger.

- Compare logic does not function and associated interrupts do not trigger.

- Every ATxsig edge latches the period counter into the ATxPER register pair, regardless of mode.

In single-pulse modes, the VALID bit becomes set upon the 3rd active input edge of the signal that latches the ATxPER register pair. In multi-pulse modes, a missing pulse trigger is also required, ensuring that at least one full revolution of the input has occurred.

An example of the VALID bit in Single-Pulse mode is shown in Figure 31-6.

#### 31.2.6 DETERMINING ACCURACY

The ATxRES register pair determines the resolution of the period measurement and, by extension, the maximum value that the phase counter reaches at the end of each input signal period. The interim value, ATxPER, used to derive the phase counter is, by nature of the circuitry, an integer. The ratio of the integer value obtained by the circuit and the calculated floating point value is the inherent error of the measurement. When ATxRES is small then integer rounding results in large errors. Factors that contribute to large errors include:

- · Large values for ATxRES

- Relatively low ATxclk frequency

- · Relatively high ATxsig input frequency

The actual error can be determined with Equation 31-7.

#### **EQUATION 31-7:**

$$period = \frac{F(ATxclk)}{F(ATxsig) \bullet (ATxRES + 1)}$$

$$error\% = 100 \bullet \left(\frac{period - int(period + 1)}{period}\right)$$

## 31.3 Input and Clock Selection

The input clock for the AT module can come from either the Fosc system clock or the 16 MHz HFINTOSC, and is chosen by the CS0 bit of the ATxCLK register. In addition, the clock is run through a prescaler that can be /1, /2, /4, or /8, which is configured by the PS<1:0> bits of the ATxCON0 register. This prescaled clock is then used for all clock operations of the Angular Timer, and as such, should be used for all of the equations demonstrated above determining the Angular Timer's behavior.

The input signal for the AT module can come from a variety of sources. The source is selected by the SSEL bits of the ATxSIG register (Register 31-4).

## 31.4 Module Outputs

# 31.4.1 ANGLE/PHASE CLOCK OUTPUT

The angle/phase clock signal (ATx\_phsclk) can be used by the CLC as an input signal to combinational logic. The polarity of this signal is configured by the PHP bit of the ATxCON1 register.

## 31.4.2 PERIOD CLOCK OUTPUT

The period clock signal (ATx\_perclk) can be used as an input clock for the Timer2/4/6 and Signal Measurement module, as well as an input signal to the CLC for combinational logic. The polarity of this signal is configured by the PRP bit of the ATxCON1 register (Register 31-2).

## 31.4.3 MISSED PULSE OUTPUT

The missed pulse signal (ATx\_missedpulse) can be used by the CLC as an input signal to combinational logic. The polarity of this signal is configured by the MPP bit of the ATxCON1 register.

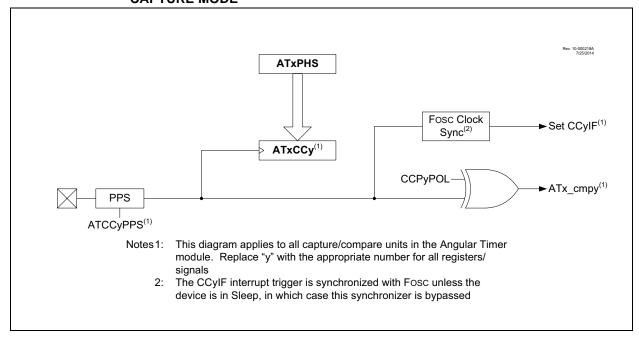

FIGURE 31-8: ANGULAR TIMER CAPTURE/COMPARE UNIT BLOCK DIAGRAM: CAPTURE MODE

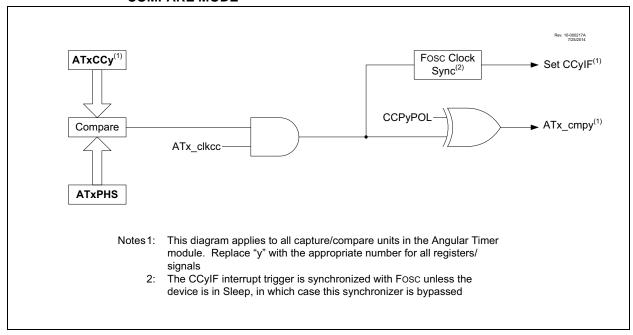

# FIGURE 31-9: ANGULAR TIMER CAPTURE/COMPARE UNIT BLOCK DIAGRAM: COMPARE MODE

# REGISTER 31-7: ATXMISSH: ANGULAR TIMER MISSING PULSE DELAY HIGH REGISTER

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u              | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|---------|---------|---------|----------------------|---------|---------|---------|

|         |         |         | MISS<   | 15:8> <sup>(1)</sup> |         |         |         |

| bit 7   |         |         |         |                      |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-0 MISS<15:8><sup>(1)</sup>: Most Significant bits (2's complement) of ATxMISS. ATxMISS defines the period counter value at which the missing pulse output becomes valid, based on the difference between the current counter value and the latched-in value of ATxPER.

**Note 1:** ATXMISSH is held until ATXMISSL is written. Proper writes of ATXMISS should write to ATXMISSH first, then ATXMISSL to ensure the value is properly written.

## REGISTER 31-8: ATXMISSL: ANGULAR TIMER MISSING PULSE DELAY LOW REGISTER

| R/W-x/u   | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| MISS<7:0> |         |         |         |         |         |         |         |

| bit 7 bit |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-0 MISS<7:0>: Least Significant bits (2's complement) of ATxMISS. ATxMISS defines the period counter value at which the missing pulse output becomes valid, based on the difference between the current counter value and the latched-in value of ATxPER.

# 34.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 34-3 lists the instructions recognized by the MPASM assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

TABLE 34-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                         |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                      |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                           |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                               |  |  |  |  |  |

| х     | Don't care location (= 0 or 1). The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |

| d     | Destination select; $d = 0$ : store result in W, $d = 1$ : store result in file register f. Default is $d = 1$ .                                                    |  |  |  |  |  |

| n     | FSR or INDF number. (0-1)                                                                                                                                           |  |  |  |  |  |

| mm    | Pre-post increment-decrement mode selection                                                                                                                         |  |  |  |  |  |

## **TABLE 34-2: ABBREVIATION DESCRIPTIONS**

| Field | Description     |  |  |

|-------|-----------------|--|--|

| PC    | Program Counter |  |  |

| TO    | Time-Out bit    |  |  |

| С     | Carry bit       |  |  |

| DC    | Digit Carry bit |  |  |

| Z     | Zero bit        |  |  |

| PD    | Power-Down bit  |  |  |

One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 34.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

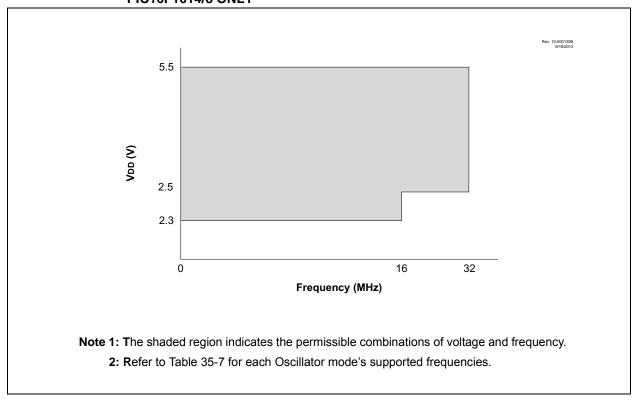

FIGURE 35-1: VOLTAGE FREQUENCY GRAPH, -40°C  $\leq$  TA  $\leq$  +125°C, PIC16F1614/8 ONLY

FIGURE 35-2: VOLTAGE FREQUENCY GRAPH, -40°C  $\leq$  Ta  $\leq$  +125°C, PIC16LF1614/8 ONLY

# TABLE 35-4: I/O PORTS

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                       | Min.              | Тур† | Max.     | Units | Conditions                                                                       |  |  |  |

|---------------|------|--------------------------------------|-------------------|------|----------|-------|----------------------------------------------------------------------------------|--|--|--|

|               | VIL  | Input Low Voltage                    | ow Voltage        |      |          |       |                                                                                  |  |  |  |

|               |      | I/O PORT:                            |                   |      |          |       |                                                                                  |  |  |  |

| D030          |      | with TTL buffer                      | _                 | _    | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                                          |  |  |  |

| D030A         |      |                                      | _                 | _    | 0.15 VDD | V     | $1.8V \le VDD \le 4.5V$                                                          |  |  |  |

| D031          |      | with Schmitt Trigger buffer          | _                 | _    | 0.2 VDD  | V     | $2.0V \le VDD \le 5.5V$                                                          |  |  |  |

| D032          |      | MCLR                                 | _                 | _    | 0.2 VDD  | V     |                                                                                  |  |  |  |

|               | VIH  | Input High Voltage I/O PORT:         |                   |      |          |       |                                                                                  |  |  |  |

| D040          |      | with TTL buffer                      | 2.0               | _    | _        | V     | 4.5V ≤ VDD ≤ 5.5V                                                                |  |  |  |

| D040A         |      |                                      | 0.25 VDD +<br>0.8 | _    | _        | V     | $1.8V \le VDD \le 4.5V$                                                          |  |  |  |

| D041          |      | with Schmitt Trigger buffer          | 0.8 VDD           | _    | _        | V     | 2.0V ≤ VDD ≤ 5.5V                                                                |  |  |  |

| D042          |      | MCLR                                 | 0.8 VDD           |      | _        | V     |                                                                                  |  |  |  |

|               | lıL  | Input Leakage Current <sup>(1)</sup> |                   |      |          |       |                                                                                  |  |  |  |

| D060          |      | I/O Ports                            | _                 | ± 5  | ± 125    | nA    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance, 85°C                                 |  |  |  |

|               |      |                                      | _                 | ± 5  | ± 1000   | nA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, 125°C                                |  |  |  |

| D061          |      | MCLR <sup>(3)</sup>                  | _                 | ± 50 | ± 200    | nA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance, 85°C                                 |  |  |  |

|               | IPUR | Weak Pull-up Current                 |                   |      |          | •     |                                                                                  |  |  |  |

| D070*         |      |                                      | 25                | 100  | 200      | μА    | VDD = 3.3V, VPIN = VSS                                                           |  |  |  |

|               |      |                                      | 25                | 140  | 300      | μΑ    | VDD = 5.0V, VPIN = VSS                                                           |  |  |  |

|               | Vol  | Output Low Voltage <sup>(3)</sup>    |                   |      |          | •     |                                                                                  |  |  |  |

| D080          |      | I/O Ports                            | _                 | _    | 0.6      | ٧     | IOL = 8.0 mA, VDD = 5.0V<br>IOL = 6.0 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |  |  |

| D080A         |      | High Drive I/O <sup>(1)</sup>        | _                 | 1.4V | _        | V     | IOL = 100 mA, VDD = 5.0V                                                         |  |  |  |

|               | Vон  | Output High Voltage <sup>(3)</sup>   |                   |      |          |       | •                                                                                |  |  |  |

| D090          |      | I/O Ports                            | VDD - 0.7         | _    | _        | ٧     | IOH = 3.5 mA, VDD = 5.0V<br>IOH = 3.0 mA, VDD = 3.3V<br>IOH = 1.0 mA, VDD = 1.8V |  |  |  |

| D090A         |      | High Drive I/O <sup>(1)</sup>        | _                 | 3.5V | _        | V     | IOL = 100 mA, VDD = 5.0V                                                         |  |  |  |

| D101A*        | CIO  | All I/O pins                         | _                 | _    | 50       | pF    |                                                                                  |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Negative current is defined as current sourced by the pin.

3: Excluding OSC2 in CLKOUT mode.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

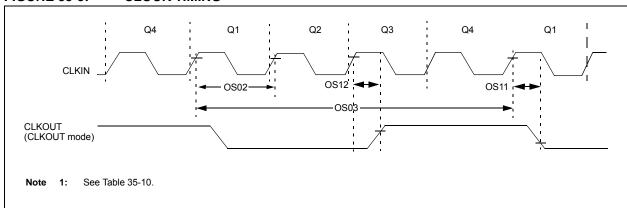

# FIGURE 35-5: CLOCK TIMING

TABLE 35-7: CLOCK OSCILLATOR TIMING REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

| Param.<br>No. | Sym. | Characteristic                        | Min.  | Typ† | Max. | Units | Conditions           |

|---------------|------|---------------------------------------|-------|------|------|-------|----------------------|

| OS01          | Fosc | External CLKIN Frequency(1)           | DC    | _    | 0.5  | MHz   | External Clock (ECL) |

|               |      |                                       | DC    | _    | 4    | MHz   | External Clock (ECM) |

|               |      |                                       | DC    | _    | 32   | MHz   | External Clock (ECH) |

| OS02          | Tosc | External CLKIN Period <sup>(1)</sup>  | 31.25 | _    | 8    | ns    | External Clock (EC)  |

| OS03          | TCY  | Instruction Cycle Time <sup>(1)</sup> | 200   | Tcy  | DC   | ns    | Tcy = 4/Fosc         |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

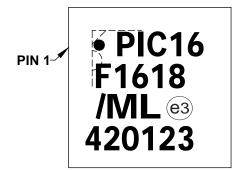

# 38.1 Package Marking Information (Continued)

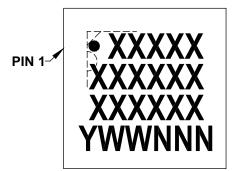

16-Lead QFN (4x4x0.5 mm)

Example

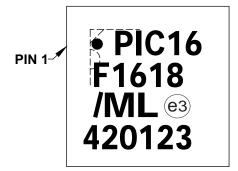

20-Lead QFN/UQFN (4x4x0.5 mm)

Example

# APPENDIX A: DATA SHEET REVISION HISTORY

# Revision A (12/2014)

Original release.

# **Revision B (5/2016)**

Minor typos corrected.

Added High endurance column to Table 1: PIC12/16(L)F161x Family Types.

Updated High-Endurance Flash data memory information on the cover page.

Updated Registers 19-2, 29-1 and 31-22. Section 19.6, 19.7. Updated Table 3: Pin Allocations Table and Table 5-1. Updated Figure 19-2.

Updated Package Drawings C04-127.