Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 8x10b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1614t-i-st |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to 17 I/O Pins and One Input-only Pin:

- Individually programmable pull-ups

- Slew rate control

- Interrupt-on-change with edge-select

- Two High Current Drive pins

- Peripheral Pin Select (PPS):

- Enables pin mapping of digital I/O

# **Intelligent Analog Peripherals**

- 10-Bit Analog-to-Digital Converter (ADC):

- Up to 12 external channels

- Conversion available during Sleep

- Two Comparators (COMP):

- Low-Power/High-Speed mode

- Up to three external inverting inputs

- Fixed Voltage Reference at non-inverting input(s)

- Comparator outputs externally accessible

- 8-Bit Digital-to-Analog Converter (DAC):

- 8-bit resolution, rail-to-rail

- Positive Reference Selection

- Voltage Reference:

- Fixed Voltage Reference (FVR): 1.024V, 2.048V and 4.096V output levels

- Zero-Cross Detect (ZCD):

- Detect when AC signal on pin crosses ground

- Two High-Current Drive Pins:

- 100mA @ 5V

# **Clocking Structure**

- 16 MHz Internal Oscillator:

- ±1% at calibration

- Selectable frequency range from 32 MHz to 31 kHz

- 31 kHz Low-Power Internal Oscillator

- 4x Phase-Locked Loop (PLL):

- For up to 32 MHz internal operation

- External Oscillator Block with:

- Three external clock modes up to 32 MHz

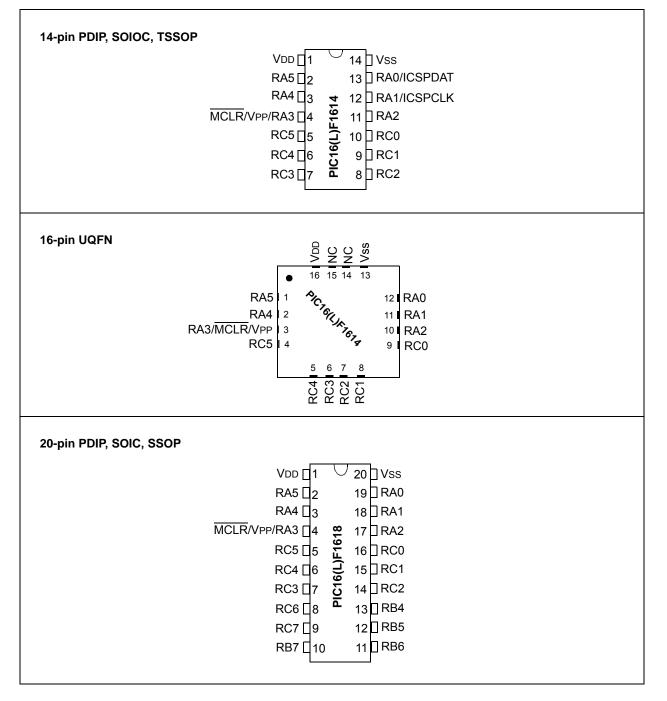

#### TABLE 2:PACKAGES

| Packages      | PDIP | SOIC | DFN | UDFN | TSSOP | QFN | UQFN | SSOP |

|---------------|------|------|-----|------|-------|-----|------|------|

| PIC16(L)F1614 | ٠    | •    |     |      | •     | •   |      |      |

| PIC16(L)F1618 | •    | •    |     |      |       | •   | •    | ٠    |

**Note:** Pin details are subject to change.

# **PIN DIAGRAMS**

© 2014-2016 Microchip Technology Inc.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

| U-0          | U-0                                                   | R/W-0/0                      | R/W-0/0       | U-0            | U-0              | R/W-0/0          | R/W-0/0      |  |  |

|--------------|-------------------------------------------------------|------------------------------|---------------|----------------|------------------|------------------|--------------|--|--|

| _            | _                                                     | CWGIF                        | ZCDIF         | _              | _                | CLC2IF           | CLC1IF       |  |  |

| bit 7        |                                                       |                              | _             |                |                  |                  | bit 0        |  |  |

|              |                                                       |                              |               |                |                  |                  |              |  |  |

| Legend:      |                                                       |                              |               |                |                  |                  |              |  |  |

| R = Read     | able bit                                              | W = Writable                 | bit           | U = Unimpler   | nented bit, read | as '0'           |              |  |  |

| u = Bit is   | unchanged                                             | x = Bit is unkr              | nown          | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is | set                                                   | '0' = Bit is cle             | ared          |                |                  |                  |              |  |  |

|              |                                                       |                              |               |                |                  |                  |              |  |  |

| bit 7-6      | Unimplemen                                            | ted: Read as '               | 0'            |                |                  |                  |              |  |  |

| bit 5        | CWGIF: CWG                                            | Interrupt Flag               | bit           |                |                  |                  |              |  |  |

|              | 1 = Interrupt is                                      |                              |               |                |                  |                  |              |  |  |

|              | 0 = Interrupt is                                      | s not pending                |               |                |                  |                  |              |  |  |

| bit 4        |                                                       | nterrupt Flag b              | oit           |                |                  |                  |              |  |  |

|              | 1 = Interrupt i                                       |                              |               |                |                  |                  |              |  |  |

|              | 0 = Interrupt i                                       | , ,                          |               |                |                  |                  |              |  |  |

| bit 3-2      | •                                                     | ted: Read as '               |               |                |                  |                  |              |  |  |

| bit 1        |                                                       | igurable Logic               | Block 2 Inter | rupt Flag bit  |                  |                  |              |  |  |

|              | 1 = Interrupt i                                       |                              |               |                |                  |                  |              |  |  |

|              | •                                                     | 0 = Interrupt is not pending |               |                |                  |                  |              |  |  |

| bit 0        | CLC1IF: Configurable Logic Block 1 Interrupt Flag bit |                              |               |                |                  |                  |              |  |  |

|              | 1 = Interrupt is<br>0 = Interrupt is                  |                              |               |                |                  |                  |              |  |  |

|              |                                                       | s not penuing                |               |                |                  |                  |              |  |  |

| Nucl         |                                                       |                              | 1. ( (        |                |                  |                  |              |  |  |

| Note:        | Interrupt flag bits an condition occurs, re           |                              |               |                |                  |                  |              |  |  |

|              | its corresponding e                                   |                              |               |                |                  |                  |              |  |  |

|              | Enable bit, GIE of                                    |                              |               |                |                  |                  |              |  |  |

# REGISTER 7-9: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3

User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT        |

|----------------------------------------------------------|------------|

| WDTE<1:0> = 00                                           |            |

| WDTE<1:0> = 01 and SEN = 0                               |            |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared    |

| CLRWDT Command                                           | Cleared    |

| Oscillator Fail Detected                                 |            |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |            |

| Change INTOSC divider (IRCF bits)                        | Unaffected |

| FIGURE 9-2: | WINDOW PERIOD AND DELAY |

|-------------|-------------------------|

| 1160NL 3-2. |                         |

# 12.6 Register Definitions: PORTC

### REGISTER 12-17: PORTC: PORTC REGISTER

| R/W-x/u            | R/W-x/u            | R/W-x/u          | R/W-x/u  | R/W-x/u                                          | R/W-x/u          | R/W-x/u  | R/W-x/u     |

|--------------------|--------------------|------------------|----------|--------------------------------------------------|------------------|----------|-------------|

| RC7 <sup>(1)</sup> | RC6 <sup>(1)</sup> | RC5              | RC4      | RC3                                              | RC2              | RC1      | RC0         |

| bit 7              |                    | <u>.</u>         | <u>.</u> | •                                                |                  |          | bit 0       |

| Legend:            |                    |                  |          |                                                  |                  |          |             |

| 0                  |                    |                  |          |                                                  |                  |          |             |

| R = Readable       | bit                | W = Writable     | bit      | U = Unimpler                                     | nented bit, read | l as '0' |             |

| u = Bit is unch    | anged              | x = Bit is unkr  | nown     | -n/n = Value at POR and BOR/Value at all other I |                  |          | ther Resets |

| '1' = Bit is set   |                    | '0' = Bit is cle | ared     |                                                  |                  |          |             |

| bit 7-0 | RC<7:0>: PORTC I/O Value bits <sup>(1, 2)</sup> |

|---------|-------------------------------------------------|

|         | 1 = Port pin is <u>&gt;</u> Vін                 |

|         | 0 <b>= Port pin is <u>&lt;</u> Vı∟</b>          |

**Note 1:** RC<7:6> on PIC16(L)F1618 only.

2: Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

# REGISTER 12-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1               | R/W-1/1               | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-----------------------|-----------------------|---------|---------|---------|---------|---------|---------|

| TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7                 |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | TRISC<7:0>: PORTC Tri-State Control bits <sup>(1)</sup> |

|---------|---------------------------------------------------------|

|         | 1 = PORTC pin configured as an input (tri-stated)       |

|         | 0 = PORTC pin configured as an output                   |

Note 1: TRISC<7:6> on PIC16(L)F1618 only.

### TABLE 13-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED)

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3       | Bit 2    | Bit 1 | Bit 0 | Register<br>on page |  |

|-----------------------|-------|-------|-------|-------------|-------------|----------|-------|-------|---------------------|--|

| RC1PPS                | —     | -     | _     |             |             | RC1PPS<4 | :0>   |       | 172                 |  |

| RC2PPS                | —     | _     | _     |             | RC2PPS<4:0> |          |       |       |                     |  |

| RC3PPS                | —     | -     | _     | RC3PPS<4:0> |             |          |       |       | 172                 |  |

| RC4PPS                | —     | -     | _     |             | 172         |          |       |       |                     |  |

| RC5PPS                | —     | _     | _     |             | 172         |          |       |       |                     |  |

| RC6PPS <sup>(1)</sup> | —     | _     | _     |             | 172         |          |       |       |                     |  |

| RC7PPS <sup>(1)</sup> | —     | _     |       |             | 172         |          |       |       |                     |  |

Note 1: PIC16(L)F1618 only.

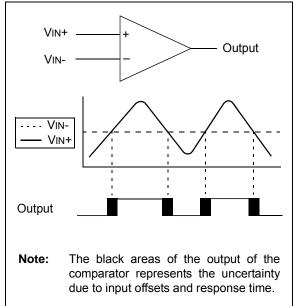

# **19.0 COMPARATOR MODULE**

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- · Programmable Speed/Power optimization

- PWM shutdown

- Programmable and Fixed Voltage Reference

### **19.1** Comparator Overview

A single comparator is shown in Figure 19-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 19-1.

#### TABLE 19-1: COMPARATOR AVAILABILITY PER DEVICE

| Device        | C1 | C2 |

|---------------|----|----|

| PIC16(L)F1618 | •  | ٠  |

| PIC16(L)F1614 | •  | ٠  |

#### FIGURE 19-1: SINGLE COMPARATOR

| 1/1 R/W-1/1                                                                        | R/W-1/1                                                                      | R/W-1/1                                                                                          | R/W-1/1                                                                                                                     | R/W-1/1                                                                                                                                                                                           | R/W-1/1                                    |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|                                                                                    | MSK                                                                          | <7:0>                                                                                            |                                                                                                                             |                                                                                                                                                                                                   |                                            |

|                                                                                    |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   | bit 0                                      |

|                                                                                    |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   |                                            |

|                                                                                    |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   |                                            |

| R = Readable bit W = Writable bit                                                  |                                                                              | U = Unimplen                                                                                     | nented bit, read                                                                                                            | l as '0'                                                                                                                                                                                          |                                            |

| = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all oth |                                                                              | ther Resets                                                                                      |                                                                                                                             |                                                                                                                                                                                                   |                                            |

| '0' = Bit is clea                                                                  | ared                                                                         |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   |                                            |

|                                                                                    |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   |                                            |

| :1>: Mask bits                                                                     |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   |                                            |

|                                                                                    |                                                                              |                                                                                                  |                                                                                                                             |                                                                                                                                                                                                   | atch                                       |

| >                                                                                  | x = Bit is unkr<br>'0' = Bit is clea<br>1>: Mask bits<br>received address bi | x = Bit is unknown<br>'0' = Bit is cleared<br>1>: Mask bits<br>received address bit n is compare | x = Bit is unknown -n/n = Value a<br>'0' = Bit is cleared<br>1>: Mask bits<br>received address bit n is compared to SSP1ADI | <ul> <li>x = Bit is unknown -n/n = Value at POR and BO</li> <li>'0' = Bit is cleared</li> <li>1&gt;: Mask bits</li> <li>received address bit n is compared to SSP1ADD<n> to detect</n></li> </ul> | x = Bit is unknown<br>'0' = Bit is cleared |

### REGISTER 24-5: SSP1MSK: SSP MASK REGISTER

|       | <ul> <li>1 = The received address bit n is compared to SSP1ADD<n> to detect I<sup>2</sup>C address match</n></li> <li>0 = The received address bit n is not used to detect I<sup>2</sup>C address match</li> </ul> |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                                                                                                                                                   |

|       | I <sup>2</sup> C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111):                                                                                                                                            |

|       | 1 = The received address bit 0 is compared to SSP1ADD<0> to detect I <sup>2</sup> C address match                                                                                                                  |

|       | 0 = The received address bit 0 is not used to detect I <sup>2</sup> C address match                                                                                                                                |

|       | I <sup>2</sup> C Slave mode, 7-bit address, the bit is ignored                                                                                                                                                     |

# REGISTER 24-6: SSP1ADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0        | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|----------------|---------|-----------------|---------|--------------|------------------|----------|---------|

|                |         |                 | ADD<    | <7:0>        |                  |          |         |

| bit 7          |         |                 |         |              |                  |          | bit 0   |

|                |         |                 |         |              |                  |          |         |

| Legend:        |         |                 |         |              |                  |          |         |

| R = Readable I | oit     | W = Writable bi | it      | U = Unimpler | nented bit, read | d as '0' |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### 10-Bit Slave mode – Most Significant Address Byte:

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode – Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

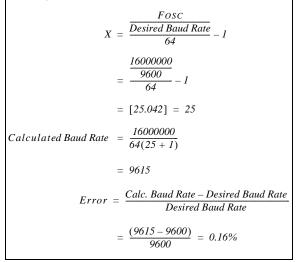

### 25.4 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDxCON register selects 16-bit mode.

The SPxBRGH, SPxBRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXxSTA register and the BRG16 bit of the BAUDxCON register. In Synchronous mode, the BRGH bit is ignored.

Table 25-3 contains the formulas for determining the baud rate. Example 25-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various Asynchronous modes have been computed for your convenience and are shown in Table 25-5. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPxBRGH, SPxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

# EXAMPLE 25-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SPxBRGH:SPxBRGL:

#### 25.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXxSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXxSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCxSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCxSTA register enables the EUSART.

#### 25.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 25.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode.

If two words are written to the TXxREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TXxREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXxREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 25.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXxREG register.

The maximum PWM resolution is ten bits when PR2/4/6 is 255. The resolution is a function of the PR2/4/6 register value as shown by Equation 26-4.

# EQUATION 26-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

**Note:** If the pulse width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

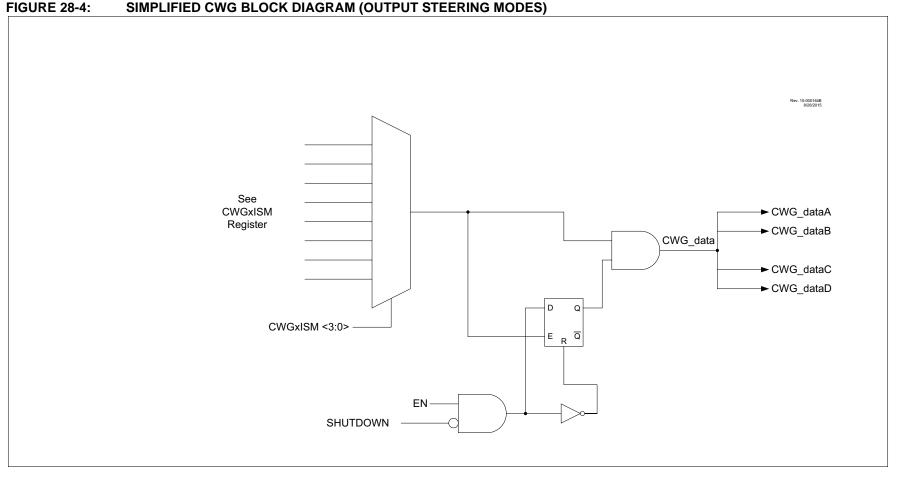

# 28.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous ECCP functions.

The CWG has the following features:

- · Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- · Output polarity control

- Output steering

- Synchronized to rising event

- Immediate effect

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

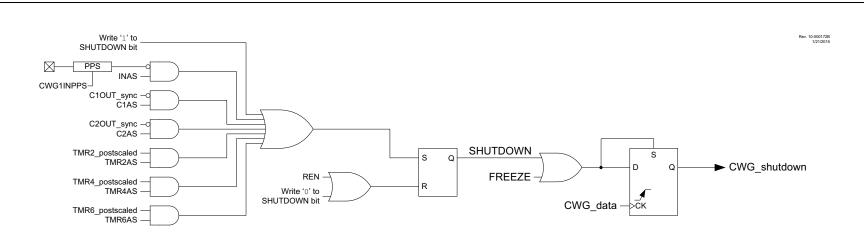

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

# 28.1 Fundamental Operation

The CWG module can operate in six different modes, as specified by MODE of the CWGxCON0 register:

- Half-Bridge mode (Figure 28-9)

- Push-Pull mode (Figure 28-2)

- Full-Bridge mode, Forward (Figure 28-3)

- Full-Bridge mode, Reverse (Figure 28-3)

- Steering mode (Figure 28-10)

- Synchronous Steering mode (Figure 28-11)

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. Thus, all output modes support auto-shutdown, which is covered in **28.10** "Auto-Shutdown".

### 28.1.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 28-9. A non-overlap (dead-band) time is inserted between the two outputs to prevent shoot through current in various power supply applications. Dead-band control is described in **Section 28.5 "Dead-Band Control"**.

The unused outputs CWGxC and CWGxD drive similar signals, with polarity independently controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

#### **FIGURE 28-4:** SIMPLIFIED CWG BLOCK DIAGRAM (OUTPUT STEERING MODES)

# FIGURE 28-12: CWG SHUTDOWN BLOCK DIAGRAM

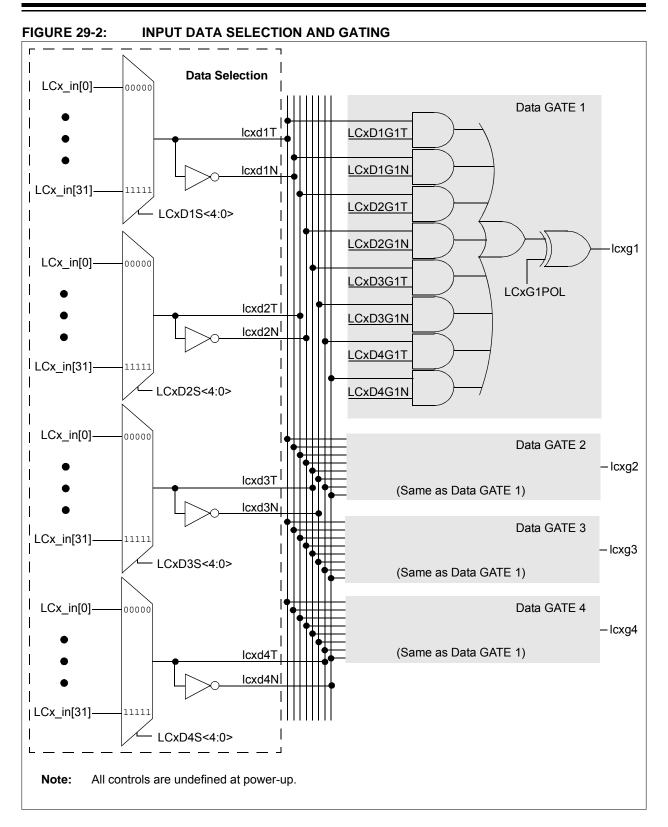

# 29.7 Register Definitions: CLC Control

| R/W-0/0                                                      | U-0                                                                                                                                   | R-0/0                                                                            | R/W-0/0       | R/W-0/0                              | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------------------------------|------------------|------------------|-------------|

| LCxEN                                                        |                                                                                                                                       | LCxOUT                                                                           | LCxINTP       | LCxINTN                              | L                | .CxMODE<2:0>     | •           |

| bit 7                                                        |                                                                                                                                       |                                                                                  |               |                                      |                  |                  | bit 0       |

|                                                              |                                                                                                                                       |                                                                                  |               |                                      |                  |                  |             |

| Legend:                                                      |                                                                                                                                       |                                                                                  |               |                                      |                  |                  |             |

| R = Readable                                                 | e bit                                                                                                                                 | W = Writable                                                                     | bit           | U = Unimplen                         | nented bit, read | 1 as '0'         |             |

| u = Bit is uncl                                              | nanged                                                                                                                                | x = Bit is unkr                                                                  | nown          | -n/n = Value a                       | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set                                             |                                                                                                                                       | '0' = Bit is clea                                                                | ared          |                                      |                  |                  |             |

|                                                              |                                                                                                                                       |                                                                                  |               |                                      |                  |                  |             |

| bit 7                                                        |                                                                                                                                       | igurable Logic                                                                   |               |                                      |                  |                  |             |

|                                                              |                                                                                                                                       |                                                                                  |               | l mixing input s<br>d has logic zerc |                  |                  |             |

| bit 6                                                        | •                                                                                                                                     | •                                                                                |               | a nas logic zero                     | output           |                  |             |

| bit 5                                                        | Unimplemented: Read as '0'                                                                                                            |                                                                                  |               |                                      |                  |                  |             |

| DIT O                                                        | <b>LCxOUT:</b> Configurable Logic Cell Data Output bit<br>Read-only: logic cell output data, after LCxPOL; sampled from lcx out wire. |                                                                                  |               |                                      |                  |                  |             |

| bit 4                                                        | •                                                                                                                                     | <b>LCxINTP:</b> Configurable Logic Cell Positive Edge Going Interrupt Enable bit |               |                                      |                  |                  |             |

|                                                              | 1 = CLCxIF will be set when a rising edge occurs on lcx out                                                                           |                                                                                  |               |                                      |                  |                  |             |

|                                                              | 0 = CLCxIF will not be set                                                                                                            |                                                                                  |               |                                      |                  |                  |             |

| bit 3                                                        | LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit                                                             |                                                                                  |               |                                      |                  |                  |             |

| 1 = CLCxIF will be set when a falling edge occurs on lcx_out |                                                                                                                                       |                                                                                  |               |                                      |                  |                  |             |

|                                                              | 0 = CLCxIFv                                                                                                                           |                                                                                  |               | <b>E</b>                             | 1. 1.1.          |                  |             |

| bit 2-0                                                      |                                                                                                                                       | •                                                                                | •             | Functional Mo                        | de dits          |                  |             |

|                                                              |                                                                                                                                       | 1-input transpa<br>J-K flip-flop wi                                              |               |                                      |                  |                  |             |

|                                                              |                                                                                                                                       | 2-input D flip-f                                                                 |               |                                      |                  |                  |             |

|                                                              |                                                                                                                                       | 1-input D flip-f                                                                 | op with S and | l R                                  |                  |                  |             |

|                                                              | 011 = Cell is                                                                                                                         |                                                                                  |               |                                      |                  |                  |             |

|                                                              | 010 = Cell is<br>001 = Cell is                                                                                                        | •                                                                                |               |                                      |                  |                  |             |

|                                                              | 001 = Cell is<br>000 = Cell is                                                                                                        |                                                                                  |               |                                      |                  |                  |             |

### REGISTER 29-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

# 34.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [0, 1]                                                          |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | FSRn is limited to the range 0000h -                                                          |

FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | $(W) + k \to (W)$                                                                                                   |

| Status Affected: | C, DC, Z                                                                                                            |

| Description:     | The contents of the W register are<br>added to the 8-bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                               |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |

| Status Affected: | Z                                                                                                                                                               |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                             |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label]ASRF f{,d}                                                                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |  |  |  |  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                            |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                               |  |  |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in |  |  |  |  |

register 'f'.

| • | register f | ┢ | С |  |

|---|------------|---|---|--|

ADD W and CARRY bit to f

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                        |  |

| Operation:       | (W) + (f) + (C) $\rightarrow$ dest                                                                                                                                       |  |

| Status Affected: | C, DC, Z                                                                                                                                                                 |  |

| Description:     | Add W, the Carry flag and data mem<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |  |

| PIC16LF1614/8 |                           | Standard Operating Conditions (unless otherwise stated) |      |      |       |                |                                          |  |

|---------------|---------------------------|---------------------------------------------------------|------|------|-------|----------------|------------------------------------------|--|

| PIC16F1       | 614/8                     |                                                         |      |      |       |                |                                          |  |

| Param.<br>No. | Device<br>Characteristics | Min.                                                    | Тур† | Max. | Units | Conditions     |                                          |  |

|               |                           |                                                         |      |      |       | Vdd            | Note                                     |  |

| D019          |                           |                                                         | 1.6  | 5.0  | mA    | 3.0            | Fosc = 32 MHz, HFINTOSC                  |  |

|               |                           | _                                                       | 1.9  | 6.0  | mA    | 3.6            |                                          |  |

| D019          |                           | _                                                       | 1.6  | 5.0  | mA    | 3.0            | Fosc = 32 MHz, HFINTOSC                  |  |

|               |                           | —                                                       | 1.9  | 6.0  | mA    | 5.0            |                                          |  |

| D020A         |                           | —                                                       | 1.6  | 5.0  | mA    | 3.0            | Fosc = 32 MHz,                           |  |

|               |                           | —                                                       | 1.9  | 6.0  | mA    | 3.6            | External Clock (ECH),<br>High-Power mode |  |

| D020A         |                           | —                                                       | 1.6  | 5.0  | mA    | 3.0            | Fosc = 32 MHz,                           |  |

|               |                           | —                                                       | 1.9  | 6.0  | mA    | 5.0            | External Clock (ECH),<br>High-Power mode |  |

| D020B         |                           | _                                                       | 6    | 16   | μA    | 1.8            | Fosc = 32 kHz,                           |  |

|               |                           | —                                                       | 8    | 22   | μA    | 3.0            | External Clock (ECL),<br>Low-Power mode  |  |

| D020B         |                           | —                                                       | 13   | 43   | μA    | 2.3            | Fosc = 32 kHz,                           |  |

|               |                           | —                                                       | 15   | 55   | μA    | 3.0            | External Clock (ECL),<br>Low-Power mode  |  |

|               | _                         | 16                                                      | 57   | μA   | 5.0   | Low-Power mode |                                          |  |

| D020C         |                           |                                                         | 19   | 40   | μA    | 1.8            | Fosc = 500 kHz,                          |  |

|               |                           | _                                                       | 32   | 60   | μA    | 3.0            | External Clock (ECL),<br>Low-Power mode  |  |

| D020C         |                           |                                                         | 31   | 60   | μA    | 2.3            | Fosc = 500 kHz,                          |  |

|               |                           |                                                         | 38   | 90   | μA    | 3.0            | External Clock (ECL),<br>Low-Power mode  |  |

|               |                           | _                                                       | 44   | 100  | μA    | 5.0            |                                          |  |

| TABLE 35-2: | SUPPLY CURRENT | (IDD) <sup>(1,2)</sup> | (CONTINUED) |

|-------------|----------------|------------------------|-------------|

|-------------|----------------|------------------------|-------------|

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

**2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.