Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

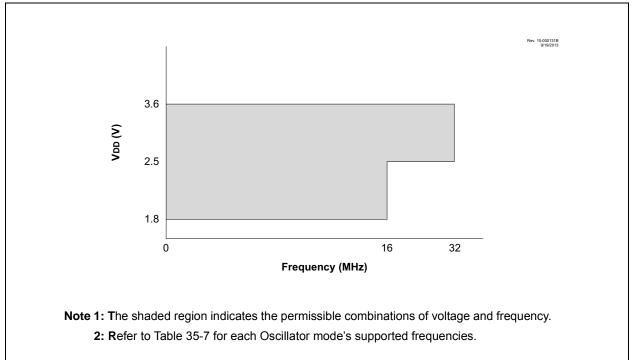

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1618-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |

|-------------|-----------------------------------------------|

| IADLL 3-14. |                                               |

| TADLE  | : 3-14: SPE            |                                           | ION REGIST           | ER SUIVIIVIA     |                   |                  |        |        |           |                   |                           |

|--------|------------------------|-------------------------------------------|----------------------|------------------|-------------------|------------------|--------|--------|-----------|-------------------|---------------------------|

| Addr   | Name                   | Bit 7                                     | Bit 6                | Bit 5            | Bit 4             | Bit 3            | Bit 2  | Bit 1  | Bit 0     | Value on POR, BOR | Value on all other Resets |

| Bank 3 |                        |                                           |                      |                  |                   |                  |        |        |           |                   |                           |

| 18Ch   | ANSELA                 | —                                         | —                    | —                | ANSA4             | —                | ANSA2  | ANSA1  | ANSA0     | 1 -111            | 1 -111                    |

| 18Dh   | ANSELB <sup>(4)</sup>  | —                                         | —                    | ANSB5            | ANSB4             | —                | —      | —      | —         | 11                | 11                        |

| 18Eh   | ANSELC                 | ANSC7 <sup>(4)</sup>                      | ANSC6 <sup>(4)</sup> | —                | —                 | ANSC3            | ANSC2  | ANSC1  | ANSC0     | 11 1111           | 11 1111                   |

| 18Fh   | —                      | Unimplemented                             | nimplemented         |                  |                   |                  |        |        |           |                   | —                         |

| 190h   | —                      | Unimplemented                             | Inimplemented        |                  |                   |                  |        |        |           |                   | —                         |

| 191h   | PMADRL                 | Flash Program                             | Memory Address       | Register Low B   | Byte              |                  |        |        |           | 0000 0000         | 0000 0000                 |

| 192h   | PMADRH                 | (2)                                       | Flash Program        | Memory Address   | s Register High I | 3yte             |        |        |           | 1000 0000         | 1000 0000                 |

| 193h   | PMDATL                 | Flash Program                             | Memory Read D        | ata Register Lov | v Byte            |                  |        |        |           | xxxx xxxx         | uuuu uuuu                 |

| 194h   | PMDATH                 | —                                         | —                    | Flash Program    | Memory Read D     | ata Register Hig | h Byte |        |           | xx xxxx           | uu uuuu                   |

| 195h   | PMCON1                 | (2)                                       | CFGS                 | LWLO             | FREE              | WRERR            | WREN   | WR     | RD        | 1000 x000         | 1000 q000                 |

| 196h   | PMCON2                 | Flash Program                             | Memory Control       | Register 2       |                   |                  |        |        |           | 0000 0000         | 0000 0000                 |

| 197h   | VREGCON <sup>(1)</sup> | —                                         | —                    | —                | —                 | —                | —      | VREGPM | Reserved  | 01                | 01                        |

| 198h   | —                      | Unimplemented                             | 1                    |                  |                   |                  |        |        |           | —                 | —                         |

| 199h   | RC1REG                 | EUSART Recei                              | ve Data Register     |                  |                   |                  |        |        |           | 0000 0000         | 0000 0000                 |

| 19Ah   | TX1REG                 | EUSART Trans                              | mit Data Registe     | r                |                   |                  |        |        |           | 0000 0000         | 0000 0000                 |

| 19Bh   | SP1BRGL                | RGL Baud Rate Generator Data Register Low |                      |                  |                   |                  |        |        | 0000 0000 | 0000 0000         |                           |

| 19Ch   | SP1BRGH                | Baud Rate Generator Data Register High    |                      |                  |                   |                  |        |        | 0000 0000 | 0000 0000         |                           |

| 19Dh   | RC1STA                 | SPEN                                      | RX9                  | SREN             | CREN              | ADDEN            | FERR   | OERR   | RX9D      | 0000 000x         | 0000 000x                 |

| 19Eh   | TX1STA                 | CSRC                                      | TX9                  | TXEN             | SYNC              | SENDB            | BRGH   | TRMT   | TX9D      | 0000 0010         | 0000 0010                 |

| 19Fh   | BAUD1CON               | ABDOVF                                    | RCIDL                | —                | SCKP              | BRG16            | —      | WUE    | ABDEN     | 01-0 0-00         | 01-0 0-00                 |

PIC16(L)F1614/8

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

**Note 1:** PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1612/16(L)F161X Memory Programming Specification*" (DS40001720).

| R/W-0/       | 0 R/W-0/0                            | R/W-0/0                          | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0           | R/W-0/0    |  |  |  |

|--------------|--------------------------------------|----------------------------------|-----------------|----------------|------------------|-------------------|------------|--|--|--|

| SCANI        | F CRCIF                              | SMT2PWAIF                        | SMT2PRAIF       | SMT2IF         | SMT1PWAIF        | SMT1PRAIF         | SMT1IF     |  |  |  |

| bit 7        |                                      |                                  |                 | •              |                  |                   | bit        |  |  |  |

|              |                                      |                                  |                 |                |                  |                   |            |  |  |  |

| Legend:      |                                      |                                  |                 |                |                  |                   |            |  |  |  |

| R = Reada    | able bit                             | W = Writable I                   | bit             | U = Unimple    | mented bit, read | l as '0'          |            |  |  |  |

| u = Bit is u | •                                    | x = Bit is unkn                  | own             | -n/n = Value   | at POR and BO    | R/Value at all ot | her Resets |  |  |  |

| '1' = Bit is | set                                  | '0' = Bit is clea                | ared            |                |                  |                   |            |  |  |  |

| bit 7        | SCANIF: So                           | canner Interrupt                 | Flag bit        |                |                  |                   |            |  |  |  |

|              |                                      | t is pending<br>t is not pending |                 |                |                  |                   |            |  |  |  |

| bit 6        | CRCIF: CR                            | C Interrupt Flag                 | bit             |                |                  |                   |            |  |  |  |

|              | 1 = Interrup                         | t is pending                     |                 |                |                  |                   |            |  |  |  |

| hit 5        | •                                    | t is not pending                 | Midth Acquisiti | on Intorrunt E | log bit          |                   |            |  |  |  |

| bit 5        |                                      | IF: SMT2 Pulse<br>If is pending  | width Acquisiti | оп іпцентирі г | nag bit          |                   |            |  |  |  |

|              |                                      | t is not pending                 |                 |                |                  |                   |            |  |  |  |

| bit 4        |                                      | F: SMT2 Period                   | Acquisition Int | errupt Flag bi | t                |                   |            |  |  |  |

|              |                                      | t is pending                     |                 |                |                  |                   |            |  |  |  |

|              | 0 = Interrup                         | t is not pending                 |                 |                |                  |                   |            |  |  |  |

| bit 3        |                                      | MT2 Match Inter                  | upt Flag bit    |                |                  |                   |            |  |  |  |

|              |                                      | t is pending<br>t is not pending |                 |                |                  |                   |            |  |  |  |

| bit 2        | -                                    | IF: SMT1 Pulse                   | Width Acquisiti | on Interrunt F | ilaa hit         |                   |            |  |  |  |

|              |                                      | t is pending                     |                 | on interrupt i | lag bit          |                   |            |  |  |  |

|              |                                      | t is not pending                 |                 |                |                  |                   |            |  |  |  |

| bit 1        | SMT1PRAI                             | F: SMT1 Period                   | Acquisition Int | errupt Flag bi | t                |                   |            |  |  |  |

|              |                                      | 1 = Interrupt is pending         |                 |                |                  |                   |            |  |  |  |

|              | -                                    | t is not pending                 |                 |                |                  |                   |            |  |  |  |

| bit 0        |                                      | MT1 Match Inter                  | upt Flag bit    |                |                  |                   |            |  |  |  |

|              |                                      | t is pending<br>t is not pending |                 |                |                  |                   |            |  |  |  |

|              | 0 – interrup                         | t is not pending                 |                 |                |                  |                   |            |  |  |  |

| Note:        | Interrupt flag bits                  |                                  |                 |                |                  |                   |            |  |  |  |

|              | condition occurs,                    |                                  |                 |                |                  |                   |            |  |  |  |

|              | its corresponding<br>Enable bit, GIE |                                  |                 |                |                  |                   |            |  |  |  |

|              | User software                        |                                  |                 |                |                  |                   |            |  |  |  |

|              | appropriate interi                   | rupt flag bits are o             |                 |                |                  |                   |            |  |  |  |

|              | to enabling an in                    | terrupt.                         |                 |                |                  |                   |            |  |  |  |

# REGISTER 7-10: PIR4: PERIPHERAL INTERRUPT REQUEST REGISTER 4

#### 11.10.6 WDT INTERACTION

Operation of the WDT is not affected by scanner activity. Hence, it is possible that long scans, particularly in Burst mode, may exceed the WDT time-out period and result in an undesired device Reset. This should be considered when performing memory scans with an application that also utilizes WDT.

### 11.10.7 IN-CIRCUIT DEBUG (ICD) INTERACTION

The scanner freezes when an ICD halt occurs, and remains frozen until user-mode operation resumes. The debugger may inspect the SCANCON0 and SCANLADR registers to determine the state of the scan.

The ICD interaction with each operating mode is summarized in Table 11-3.

|                     | Scanner Operating Mode                                                                                                                                        |                                                                                                                                                                                       |                                                                                                                                                                                        |                                                                                                                                                                                                                                                          |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ICD Halt            | Peek                                                                                                                                                          | Concurrent<br>Triggered                                                                                                                                                               | Burst                                                                                                                                                                                  |                                                                                                                                                                                                                                                          |  |  |  |

| External Halt       | If Scanner would peek an instruction<br>that is not executed (because of ICD<br>entry), the peek will occur after ICD<br>exit, when the instruction executes. | If external halt is asserted during a<br>scan cycle, the instruction (delayed<br>by scan) may or may not execute<br>before ICD entry, depending on<br>external halt timing.           |                                                                                                                                                                                        | If external halt is asserted during the<br>BSF (SCANCON.GO), ICD entry<br>occurs, and the burst is delayed until<br>ICD exit.<br>Otherwise, the current NVM-access<br>cycle will complete, and then the<br>scanner will be interrupted for ICD<br>entry. |  |  |  |

|                     |                                                                                                                                                               | If external halt is asserted during the cycle immediately prior to the scan cycle, both scan and instruction execution happen after the ICD exits.                                    | If external halt is asserted during the<br>burst, the burst is suspended and will<br>resume with ICD exit.                                                                             |                                                                                                                                                                                                                                                          |  |  |  |

| PC<br>Breakpoint    |                                                                                                                                                               | Scan cycle occurs before ICD entry<br>and instruction execution happens<br>after the ICD exits.                                                                                       | If PCPB (or single step) is on                                                                                                                                                         |                                                                                                                                                                                                                                                          |  |  |  |

| Data<br>Breakpoint  |                                                                                                                                                               | The instruction with the dataBP<br>executes and ICD entry occurs<br>immediately after. If scan is<br>requested during that cycle, the scan<br>cycle is postponed until the ICD exits. | BSF (SCANCON.GO), the ICD is<br>entered before execution; execution<br>of the burst will occur at ICD exit, and<br>the burst will run to completion.                                   |                                                                                                                                                                                                                                                          |  |  |  |

| Single Step         |                                                                                                                                                               | If a scan cycle is ready after the debug instruction is executed, the scan will read PFM and then the ICD is re-entered.                                                              | Note that the burst can be interrupted by an external halt.                                                                                                                            |                                                                                                                                                                                                                                                          |  |  |  |

| SWBP and<br>ICDINST |                                                                                                                                                               | If scan would stall a SWBP, the scan cycle occurs and the ICD is entered.                                                                                                             | If SWBP replaces<br>BSF(SCANCON.GO), the ICD will be<br>entered; instruction execution will<br>occur at ICD exit (from ICDINSTR<br>register), and the burst will run to<br>completion. |                                                                                                                                                                                                                                                          |  |  |  |

## TABLE 11-3: ICD AND SCANNER INTERACTIONS

# REGISTER 12-25: HIDRVC: PORTC HIGH DRIVE STRENGTH REGISTER

| U-0              | U-0                                         | R/W-0/0           | R/W-0/0        | U-0                                                   | U-0              | U-0    | U-0   |  |  |

|------------------|---------------------------------------------|-------------------|----------------|-------------------------------------------------------|------------------|--------|-------|--|--|

| —                | —                                           | HIDC5             | HIDC4          | —                                                     | —                | —      | —     |  |  |

| bit 7            |                                             |                   |                |                                                       |                  |        | bit 0 |  |  |

|                  |                                             |                   |                |                                                       |                  |        |       |  |  |

| Legend:          |                                             |                   |                |                                                       |                  |        |       |  |  |

| R = Readable     | bit                                         | W = Writable      | bit            | U = Unimpler                                          | nented bit, read | as '0' |       |  |  |

| u = Bit is unch  | anged                                       | x = Bit is unkr   | nown           | -n/n = Value at POR and BOR/Value at all other Resets |                  |        |       |  |  |

| '1' = Bit is set |                                             | '0' = Bit is clea | ared           |                                                       |                  |        |       |  |  |

|                  |                                             |                   |                |                                                       |                  |        |       |  |  |

| bit 7-6          | Unimplemen                                  | ted: Read as '    | 0'             |                                                       |                  |        |       |  |  |

| bit 5            | HIDC5: High                                 | Current Drive E   | Enable on Port | t C5                                                  |                  |        |       |  |  |

|                  | 1 = High Drive enabled                      |                   |                |                                                       |                  |        |       |  |  |

|                  | 0 = High Drive disabled                     |                   |                |                                                       |                  |        |       |  |  |

| bit 4            | HIDC4: High Current Drive Enable on Port C4 |                   |                |                                                       |                  |        |       |  |  |

|                  | 1 = High Drive enabled                      |                   |                |                                                       |                  |        |       |  |  |

|                  | 0 = High Drive disabled                     |                   |                |                                                       |                  |        |       |  |  |

bit 3-0 Unimplemented: Read as '0'

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name    | Bit 7                  | Bit 6                  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|------------------------|------------------------|---------|---------|---------|---------|---------|---------|---------------------|

| ANSELC  | ANSC7 <sup>(1)</sup>   | ANSC6 <sup>(1)</sup>   | —       | —       | ANSC3   | ANSC2   | ANSC1   | ANSC0   | 166                 |

| HIDRVC  |                        | _                      | HIDC5   | HIDC4   | _       | _       | —       | _       | 169                 |

| INLVLC  | INLVLC7 <sup>(1)</sup> | INLVLC6 <sup>(1)</sup> | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 | 168                 |

| LATC    | LATC7 <sup>(1)</sup>   | LATC6 <sup>(1)</sup>   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   | 166                 |

| ODCONC  | ODC7 <sup>(1)</sup>    | ODC6 <sup>(1)</sup>    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    | 167                 |

| PORTC   | RC7 <sup>(1)</sup>     | RC6 <sup>(1)</sup>     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     | 165                 |

| SLRCONC | SLRC7 <sup>(1)</sup>   | SLRC6 <sup>(1)</sup>   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   | 168                 |

| TRISC   | TRISC7 <sup>(1)</sup>  | TRISC6 <sup>(1)</sup>  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  | 165                 |

| WPUC    | WPUC7 <sup>(1)</sup>   | WPUC6 <sup>(1)</sup>   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   | 167                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC. **Note 1:** PIC16(L)F1618 only

| D DDO - 4-0 | Outrast Olamal          |       | PIC16(L)F161 | PIC16(I | L)F1614 |       |

|-------------|-------------------------|-------|--------------|---------|---------|-------|

| RxyPPS<4:0> | Output Signal           | PORTA | PORTB        | PORTC   | PORTA   | PORTC |

| 11xxx       | Reserved                | •     | •            | ٠       | •       | •     |

| 10111       | Reserved                | •     | •            | •       | •       | •     |

| 10110       | Reserved                | •     | •            | •       | •       | •     |

| 10101       | Reserved                | •     | •            | •       | •       | •     |

| 10100       | Reserved                | •     | •            | •       | •       | •     |

| 10011       | DT                      | •     | •            | •       | •       | •     |

| 10010       | TX/CK                   | •     | •            | •       | •       | •     |

| 10001       | SDO/SDA <sup>(1)</sup>  | •     | •            | •       | •       | •     |

| 10000       | SCK/SCL <sup>(1)</sup>  | •     | •            | •       | •       | •     |

| 01111       | PWM4_out                | •     | •            | •       | •       | •     |

| 01110       | PWM3_out                | •     | •            | •       | •       | •     |

| 01101       | CCP2_out                | •     | •            | •       | •       | •     |

| 01100       | CCP1_out                | •     | •            | •       | •       | •     |

| 01011       | CWG1OUTD <sup>(1)</sup> | •     | •            | •       | •       | •     |

| 01010       | CWG1OUTC <sup>(1)</sup> | •     | •            | •       | •       | •     |

| 01001       | CWG1OUTB <sup>(1)</sup> | •     | •            | •       | •       | •     |

| 01000       | CWG1OUTA <sup>(1)</sup> | •     | •            | •       | •       | •     |

| 00111       | LC4_out                 | •     | •            | ٠       | •       | •     |

| 00110       | LC3_out                 | •     | •            | •       | •       | •     |

| 00101       | LC2_out                 | •     | •            | •       | •       | •     |

| 00100       | LC1_out                 | •     | •            | •       | •       | •     |

| 00011       | ZCD1_out                | •     | •            | ٠       | •       | •     |

| 00010       | sync_C2OUT              | •     | •            | ٠       | •       | •     |

| 00001       | sync_C1OUT              | •     | •            | •       | •       | •     |

| 00000       | LATxy                   | •     | •            | •       | •       | •     |

| TABLE 13-2: AV | AILABLE PORTS FOR OUTPUT BY PERIPHERAL <sup>(2)</sup> |

|----------------|-------------------------------------------------------|

|----------------|-------------------------------------------------------|

**Note 1:** TRIS control is overridden by the peripheral as required.

2: Unsupported peripherals will output a '0'.

# 17.3 Register Definitions: ADC Control

| U-0            | R/W-0/0                                 | R/W-0/0             | R/W-0/0                           | R/W-0/0                              | R/W-0/0         | R/W-0/0           | R/W-0/0      |  |  |

|----------------|-----------------------------------------|---------------------|-----------------------------------|--------------------------------------|-----------------|-------------------|--------------|--|--|

|                |                                         |                     | CHS<4:0>                          |                                      |                 | GO/DONE           | ADON         |  |  |

| oit 7          |                                         |                     |                                   |                                      |                 |                   | bit          |  |  |

|                |                                         |                     |                                   |                                      |                 |                   |              |  |  |

| Legend:        |                                         |                     |                                   |                                      |                 |                   |              |  |  |

| R = Readal     | ole bit                                 | W = Writable        | bit                               | U = Unimpler                         | nented bit, rea | ad as '0'         |              |  |  |

| u = Bit is ur  | nchanged                                | x = Bit is unk      | nown                              | -n/n = Value a                       | at POR and B    | OR/Value at all o | other Resets |  |  |

| '1' = Bit is s | et                                      | '0' = Bit is cle    | ared                              |                                      |                 |                   |              |  |  |

| hit 7          | Unimalama                               | ntad. Dood oo       | · • '                             |                                      |                 |                   |              |  |  |

| bit 7          | -                                       | nted: Read as       |                                   |                                      |                 |                   |              |  |  |

| oit 6-2        |                                         | Analog Channe       |                                   | Duffor 1 Output                      | (3)             |                   |              |  |  |

|                | 11111 = FV $11110 = DA$                 | C (Digital-to-Ar    | je Relefence) i<br>jalog Converte | Buffer 1 Output<br><sub>r)</sub> (2) |                 |                   |              |  |  |

|                | 11101 = Ter                             | nperature Indic     | ator <sup>(1)</sup>               | • /                                  |                 |                   |              |  |  |

|                |                                         | ,<br>served. No cha |                                   | d.                                   |                 |                   |              |  |  |

|                | •                                       |                     |                                   |                                      |                 |                   |              |  |  |

|                | •                                       |                     |                                   |                                      |                 |                   |              |  |  |

|                | 01100 = Re                              | served. No cha      | innel connecte                    | d.                                   |                 |                   |              |  |  |

|                | 01011 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 01010 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 01001 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 01000 = AN                              | served. No cha      |                                   | d                                    |                 |                   |              |  |  |

|                |                                         | served. No cha      |                                   |                                      |                 |                   |              |  |  |

|                |                                         | served. No cha      |                                   |                                      |                 |                   |              |  |  |

|                | 00100 = Re                              | served. No cha      | innel connecte                    | d.                                   |                 |                   |              |  |  |

|                |                                         | served. No cha      | innel connecte                    | d.                                   |                 |                   |              |  |  |

|                | 00111 = AN<br>00110 = AN                |                     |                                   |                                      |                 |                   |              |  |  |

|                | 00110 - AN<br>00101 - AN                |                     |                                   |                                      |                 |                   |              |  |  |

|                | 00100 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 00011 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 00010 = AN                              |                     |                                   |                                      |                 |                   |              |  |  |

|                | 00001 = AN<br>00000 = AN                |                     |                                   |                                      |                 |                   |              |  |  |

| oit 1          |                                         | ADC Conversio       | n Status hit                      |                                      |                 |                   |              |  |  |

|                |                                         |                     |                                   | tting this bit sta                   | rts an ADC co   | nversion cycle.   |              |  |  |

|                |                                         |                     |                                   |                                      |                 | sion has comple   | eted.        |  |  |

|                |                                         | version comple      |                                   |                                      |                 |                   |              |  |  |

| oit 0          | ADON: ADC                               | Enable bit          |                                   |                                      |                 |                   |              |  |  |

|                | 1 = ADC is e                            |                     |                                   |                                      |                 |                   |              |  |  |

|                |                                         | lisabled and co     | -                                 | -                                    |                 |                   |              |  |  |

|                | See Section16.0                         | -                   |                                   |                                      |                 |                   |              |  |  |

|                | See Section18.0                         | -                   | -                                 |                                      |                 | more informatio   | n.           |  |  |

|                | See Section15.0                         | -                   | -                                 | FVR)" for more                       | information.    |                   |              |  |  |

| <b>∆</b> • /   | N<11:8> available on PIC16(1)E1618 only |                     |                                   |                                      |                 |                   |              |  |  |

# REGISTER 17-1: ADCON0: ADC CONTROL REGISTER 0

4: AN<11:8> available on PIC16(L)F1618 only.

# 22.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 22.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section22.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 22.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate pin (T1G)                                                 |

| 01    | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

| 10    | Comparator 1 Output (C1_OUT_sync) <sup>(1)</sup>                      |

| 11    | Comparator 2 Output (C2_OUT_sync) <sup>(1)</sup>                      |

Note 1: Optionally synchronized comparator output.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 22.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 22.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 22-3 for timing details.

| <b>TABLE 22-3:</b> | TIMER1 GATE ENABLE |

|--------------------|--------------------|

|                    | SELECTIONS         |

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| 1          | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

### 22.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 22-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| Mode            | MODE                                             | E<4:0>                                | Output                                      | Operation                                                 |                            | Timer Control                   |                                   |   |  |

|-----------------|--------------------------------------------------|---------------------------------------|---------------------------------------------|-----------------------------------------------------------|----------------------------|---------------------------------|-----------------------------------|---|--|

| Mode            | <4:3>                                            | <2:0>                                 | Operation                                   | Operation                                                 | Start                      | Reset                           | Stop                              |   |  |

|                 |                                                  | 000                                   |                                             | Software gate (Figure 23-4)                               | ON = 1                     | _                               | <b>ON =</b> 0                     |   |  |

| Free            | 001                                              | Period<br>Pulse                       | Hardware gate, active-high<br>(Figure 23-5) | ON = 1 and<br>TMRx_ers = 1                                | _                          | ON = 0 or<br>TMRx_ers = 0       |                                   |   |  |

|                 | 010                                              | T uloc                                | Hardware gate, active-low                   | ON = 1 and<br>TMRx_ers = 0                                |                            | ON = 0 or<br>TMRx_ers = 1       |                                   |   |  |

| Free<br>Running | 0.0                                              | 011                                   |                                             | Rising or falling edge Reset                              |                            | TMRx_ers                        |                                   |   |  |

| Period          | 00 100                                           | 100                                   | Period                                      | Rising edge Reset (Figure 23-6)                           |                            | TMRx_ers ↑                      | <b>ON =</b> 0                     |   |  |

|                 |                                                  | 101                                   | Pulse                                       | Falling edge Reset                                        |                            | TMRx_ers ↓                      |                                   |   |  |

|                 |                                                  | 110                                   | with<br>Hardware<br>Reset                   | Low level Reset                                           | ON = 1                     | TMRx_ers = 0                    | ON = 0 or<br>TMRx_ers = 0         |   |  |

|                 |                                                  | 111                                   | Resel                                       | High level Reset (Figure 23-7)                            |                            | TMRx_ers = 1                    | ON = 0 or<br>TMRx_ers = 1         |   |  |

|                 |                                                  | 000                                   | One-shot                                    | Software start (Figure 23-8)                              | ON = 1                     |                                 |                                   |   |  |

|                 |                                                  |                                       |                                             | 001                                                       | Edge                       | Rising edge start (Figure 23-9) | ON = 1 and<br>TMRx_ers ↑          | _ |  |

| One-shot 01     |                                                  | 010                                   | triggered<br>start                          | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | -                               | l                                 |   |  |

|                 |                                                  | 011                                   | (Note 1)                                    | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                               | ON = 0<br>or                      |   |  |

|                 | 01                                               | 100                                   | Edge<br>triggered<br>start                  | Rising edge start and<br>Rising edge Reset (Figure 23-10) | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers ↑                      | Next clock<br>after<br>TMRx = PRx |   |  |

|                 |                                                  | 101                                   |                                             | Falling edge start and<br>Falling edge Reset              | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers ↓                      | (Note 2)                          |   |  |

|                 |                                                  | 110                                   | and<br>hardware<br>Reset                    | Rising edge start and<br>Low level Reset (Figure 23-11)   | ON = 1 and<br>TMRx_ers ↑   | TMRx_ers = 0                    |                                   |   |  |

|                 |                                                  | 111                                   | (Note 1)                                    | Falling edge start and<br>High level Reset                | ON = 1 and<br>TMRx_ers ↓   | TMRx_ers = 1                    |                                   |   |  |

|                 |                                                  | 000                                   |                                             | Rese                                                      | rved                       |                                 |                                   |   |  |

|                 |                                                  | 001                                   | Edge                                        | Rising edge start<br>(Figure 23-12)                       | ON = 1 and<br>TMRx_ers ↑   | _                               | ON = 0<br>or                      |   |  |

| Mono-stable     |                                                  | 010                                   | triggered<br>start                          | Falling edge start                                        | ON = 1 and<br>TMRx_ers ↓   | _                               | Next clock<br>after               |   |  |

|                 |                                                  | 011                                   | (Note 1)                                    | Any edge start                                            | ON = 1 and<br>TMRx_ers     | _                               | TMRx = PRx<br>( <b>Note 3</b> )   |   |  |

| Reserved        | 10                                               | 100                                   |                                             | Rese                                                      | rved                       |                                 |                                   |   |  |

| Reserved        | erved 101                                        |                                       |                                             | Rese                                                      | rved                       |                                 |                                   |   |  |

|                 |                                                  | 110                                   | Level<br>triggered                          | High level start and<br>Low level Reset (Figure 23-13)    | ON = 1 and<br>TMRx_ers = 1 | TMRx_ers = 0                    | ON = 0 or                         |   |  |

| One-shot        | start<br>and<br><sup>111</sup> hardware<br>Reset | Low level start &<br>High level Reset | ON = 1 and<br>TMRx_ers = 0                  | TMRx_ers = 1                                              | Held in Reset<br>(Note 2)  |                                 |                                   |   |  |

| Reserved        | 11                                               | xxx                                   |                                             | Rese                                                      | rved                       |                                 |                                   |   |  |

TABLE 23-1: TIMER2 OPERATING MODES

**Note** 1: If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TMRx = PRx then the next clock clears ON and stops TMRx at 00h.

3: When TMRx = PRx then the next clock stops TMRx at 00h but does not clear ON.

| Name     | Bit 7                                        | Bit 6                       | Bit 5        | Bit 4  | Bit 3      | Bit 2     | Bit 1     | Bit 0  | Register<br>on Page |

|----------|----------------------------------------------|-----------------------------|--------------|--------|------------|-----------|-----------|--------|---------------------|

| CCP1CON  | EN                                           |                             | OUT          | FMT    | MODE<3:0>  |           |           |        | 352                 |

| CCP2CON  | EN                                           | _                           | OUT          | FMT    |            | MODE      | E<3:0>    |        | 352                 |

| INTCON   | GIE                                          | PEIE                        | TMR0IE       | INTE   | IOCIE      | TMR0IF    | INTF      | IOCIF  | 97                  |

| PIE1     | TMR1GIE                                      | ADIE                        | _            | _      | -          | CCP1IE    | TMR2IE    | TMR1IE | 98                  |

| PIR1     | TMR1GIF                                      | ADIF                        | RCIF         | TXIF   | SSP1IF     | CCP1IF    | TMR2IF    | TMR1IF | 103                 |

| PR2      | Timer2 Modu                                  | mer2 Module Period Register |              |        |            |           |           |        | 235*                |

| TMR2     | Holding Register for the 8-bit TMR2 Register |                             |              |        |            |           |           |        | 235*                |

| T2CON    | ON                                           |                             | CKPS<2:0>    |        | OUTPS<3:0> |           |           |        |                     |

| T2CLKCON | —                                            | _                           | _            | _      |            | CS<3:0>   |           |        |                     |

| T2RST    | _                                            |                             |              |        |            | 256       |           |        |                     |

| T2HLT    | PSYNC                                        | CKPOL                       | CKSYNC       |        | MODE<4:0>  |           |           |        |                     |

| PR4      | Timer4 Module Period Register                |                             |              |        |            |           |           | 235*   |                     |

| TMR4     | Holding Reg                                  | ister for the 8             | -bit TMR4 Re | gister |            |           |           |        | 235*                |

| T4CON    | ON                                           |                             | CKPS<2:0>    |        |            | OUTP      | S<3:0>    |        | 254                 |

| T4CLKCON | —                                            | _                           | _            | _      |            | CS<       | <3:0>     |        | 253                 |

| T4RST    | _                                            |                             | _            | _      |            | RSEL      | _<3:0>    |        | 256                 |

| T4HLT    | PSYNC                                        | CKPOL                       | CKSYNC       |        |            | MODE<4:0> |           |        | 255                 |

| PR6      | Timer6 Modu                                  | ule Period Re               | gister       |        |            |           |           |        | 235*                |

| TMR6     | Holding Reg                                  | ister for the 8             | -bit TMR6 Re | gister |            |           |           |        | 235*                |

| T6CON    | ON                                           |                             | CKPS<2:0>    |        |            | OUTP      | S<3:0>    |        | 254                 |

| T6CLKCON | _                                            | _                           | _            | _      |            |           | T6CS<2:0> |        | 253                 |

| T6RST    | —                                            | _                           | _            | _      |            | RSEL      | _<3:0>    |        | 256                 |

| T6HLT    | PSYNC                                        | CKPOL                       | CKSYNC       |        |            | MODE<4:0> |           |        | 255                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

PIC16(L)F1614/8

© 2014-2016 Microchip Technology Inc.

# 25.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VOL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 25-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 25.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 25-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXxREG register.

#### 25.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXxSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXxSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCxSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

Note: The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

### 25.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXxREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXxREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXxREG until the Stop bit of the previous character has been transmitted. The pending character in the TXxREG is then transferred to the TSR in one Tcy immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXxREG.

#### 25.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 25.5.1.2 "Clock Polarity**".

#### 25.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXxREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXxREG. The TXIF flag bit is not cleared immediately upon writing TXxREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXxREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXxREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXxREG.

PIC16(L)F1614/8

## 30.8 Register Definitions: SMT Control

Long bit name prefixes for the Signal Measurement Timer peripherals are shown in Table 30-2. Refer to Section 1.1 "Register and Bit Naming Conventions" for more information.

TABLE 30-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| SMT1       | SMT1            |

| SMT2       | SMT2            |

### REGISTER 30-1: SMTxCON0: SMT CONTROL REGISTER 0

| R/W-0/0           | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 |

|-------------------|-----|---------|---------|---------|---------|-------------|---------|

| EN <sup>(1)</sup> | —   | STP     | WPOL    | SPOL    | CPOL    | SMTxPS<1:0> |         |

| bit 7             |     |         |         |         |         |             | bit 0   |

| Legend:                                  |                          |                                                                |                                                       |  |  |  |

|------------------------------------------|--------------------------|----------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| R = Readable bit                         |                          | W = Writable bit                                               | U = Unimplemented bit, read as '0'                    |  |  |  |

| u = Bit is unchanged<br>'1' = Bit is set |                          | x = Bit is unknown                                             | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |

|                                          |                          | '0' = Bit is cleared                                           |                                                       |  |  |  |

|                                          |                          |                                                                |                                                       |  |  |  |

| bit 7                                    | EN: SMT E                | Enable bit <sup>(1)</sup>                                      |                                                       |  |  |  |

|                                          | 1 = SMT is               |                                                                |                                                       |  |  |  |

|                                          |                          |                                                                | e reset, clock requests are disabled                  |  |  |  |

| bit 6                                    | Unimplem                 | ented: Read as '0'                                             |                                                       |  |  |  |

| bit 5                                    | STP: SMT                 | Counter Halt Enable bit                                        |                                                       |  |  |  |

|                                          | When SMTxTMR = SMTxPR:   |                                                                |                                                       |  |  |  |

|                                          |                          | · •                                                            | match interrupt occurs when clocked                   |  |  |  |

| 1.11.4                                   |                          | , I                                                            | iod match interrupt occurs when clocked               |  |  |  |

| bit 4                                    |                          | /TxWIN Input Polarity Contr<br>VIN signal is active-low/fallir |                                                       |  |  |  |

|                                          |                          | VIN signal is active-high/risi                                 |                                                       |  |  |  |

| bit 3                                    |                          | ITxSIG Input Polarity Contro                                   |                                                       |  |  |  |

| bit o                                    |                          | signal is active-low/falling e                                 |                                                       |  |  |  |

|                                          | 0 = SMTx                 | signal is active-high/rising e                                 | dge enabled                                           |  |  |  |

| bit 2                                    | CPOL: SM                 | IT Clock Input Polarity Cont                                   | rol bit                                               |  |  |  |

|                                          |                          |                                                                | ng edge of the selected clock signal                  |  |  |  |

|                                          | 0 = SMTxT                | MR increments on the rising                                    | g edge of the selected clock signal                   |  |  |  |

| bit 1-0                                  | •••••••                  | 1:0>: SMT Prescale Select                                      | bits                                                  |  |  |  |

|                                          | 11 = Preso<br>10 = Preso |                                                                |                                                       |  |  |  |

|                                          | 10 = Presc01 = Presc     |                                                                |                                                       |  |  |  |

|                                          | 01 = Presc               |                                                                |                                                       |  |  |  |

|                                          |                          |                                                                |                                                       |  |  |  |

|                                          |                          |                                                                |                                                       |  |  |  |

#### **Note 1:** Setting EN to '0' does not affect the register contents.

## REGISTER 30-15: SMTxCPWL: SMT CAPTURED PULSE WIDTH REGISTER – LOW BYTE

| R-x/x            | R-x/x | R-x/x             | R-x/x | R-x/x                                             | R-x/x            | R-x/x    | R-x/x |

|------------------|-------|-------------------|-------|---------------------------------------------------|------------------|----------|-------|

|                  |       |                   | SMTxC | PW<7:0>                                           |                  |          |       |

| bit 7            |       |                   |       |                                                   |                  |          | bit 0 |

|                  |       |                   |       |                                                   |                  |          |       |

| Legend:          |       |                   |       |                                                   |                  |          |       |

| R = Readable     | bit   | W = Writable b    | it    | U = Unimpler                                      | mented bit, read | d as '0' |       |

| u = Bit is unch  | anged | x = Bit is unkno  | own   | -n/n = Value at POR and BOR/Value at all other Re |                  |          |       |

| '1' = Bit is set |       | '0' = Bit is clea | red   |                                                   |                  |          |       |

bit 7-0 SMTxCPW<7:0>: Significant bits of the SMT PW Latch – Low Byte

### REGISTER 30-16: SMTxCPWH: SMT CAPTURED PULSE WIDTH REGISTER - HIGH BYTE

| R-x/x         | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x |  |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| SMTxCPW<15:8> |       |       |       |       |       |       |       |  |  |

| bit 7         |       |       |       |       |       |       | bit 0 |  |  |

|               |       |       |       |       |       |       |       |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<15:8>: Significant bits of the SMT PW Latch – High Byte

### REGISTER 30-17: SMTxCPWU: SMT CAPTURED PULSE WIDTH REGISTER - UPPER BYTE

| R-x/x          | R-x/x | R-x/x | R-x/x   | R-x/x          | R-x/x          | R-x/x          |  |  |  |

|----------------|-------|-------|---------|----------------|----------------|----------------|--|--|--|

| SMTxCPW<23:16> |       |       |         |                |                |                |  |  |  |

|                |       |       |         |                |                | bit 0          |  |  |  |

|                |       |       |         |                |                |                |  |  |  |

|                |       |       | SMTxCPV | SMTxCPW<23:16> | SMTxCPW<23:16> | SMTxCPW<23:16> |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<23:16>: Significant bits of the SMT PW Latch – Upper Byte

### REGISTER 31-3: ATxCLK: ANGULAR TIMER CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-x/x |

|-------|-----|-----|-----|-----|-----|-----|---------|

| —     | —   | —   | —   | —   | —   | —   | CS0     |

| bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-1 Unimplemented: Read as '0' bit 0 CS0: Angular Timer Clock Selection bit 1 = HFINTOSC 16 MHz 0 = Fosc

#### REGISTER 31-4: ATxSIG: ANGULAR TIMER INPUT SIGNAL SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x/x | R/W-x/x   | R/W-x/x |

|-------|-----|-----|-----|-----|---------|-----------|---------|

| —     | —   | —   | —   | —   |         | SSEL<2:0> |         |

| bit 7 |     |     |     |     |         |           | bit 0   |