#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1618-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

### REGISTER 3-1: STATUS: STATUS REGISTER

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to **Section 34.0 "Instruction Set Summary"**).

Note 1: The <u>C</u> and <u>DC</u> bits operate as Borrow and <u>Digit</u> Borrow out bits, respectively, in subtraction.

| U-0              | U-0                                                                                        | U-0               | R-1/q                                     | R-1/q        | R/W-0/u          | R/W-0/u           | R/W-0/u          |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|-------------------|-------------------------------------------|--------------|------------------|-------------------|------------------|--|--|--|

| _                | _                                                                                          | —                 | TO                                        | PD           | Z                | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |

| bit 7 bit 0      |                                                                                            |                   |                                           |              |                  |                   |                  |  |  |  |

|                  |                                                                                            |                   |                                           |              |                  |                   |                  |  |  |  |

| Legend:          |                                                                                            |                   |                                           |              |                  |                   |                  |  |  |  |

| R = Readable b   | bit                                                                                        | W = Writable      | bit                                       | U = Unimpler | nented bit, read | as '0'            |                  |  |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |                   |                                           |              |                  |                   | other Resets     |  |  |  |

| '1' = Bit is set |                                                                                            | '0' = Bit is clea | is cleared q = Value depends on condition |              |                  |                   |                  |  |  |  |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                        |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction<br>0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                      |

|         | <ul> <li>1 = After power-up or by the CLRWDT instruction</li> <li>0 = By execution of the SLEEP instruction</li> </ul>                                                  |

| bit 2   | Z: Zero bit                                                                                                                                                             |

|         | <ul> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                               |

|         | <ul> <li>1 = A carry-out from the 4th low-order bit of the result occurred</li> <li>0 = No carry-out from the 4th low-order bit of the result</li> </ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                             |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |

| Note 1. | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the                                                                   |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

# TABLE 3-14: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr               | Name     | Bit 7           | Bit 6         | Bit 5                | Bit 4 | Bit 3 | Bit 2     | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on all other Resets |

|--------------------|----------|-----------------|---------------|----------------------|-------|-------|-----------|--------|-----------|----------------------|---------------------------|

| Bank               | 3        |                 |               |                      |       |       |           |        |           | FUR, BUR             | other Resets              |

| 40Ch               | _        | Unimplemented   |               |                      |       |       |           |        |           | _                    | _                         |

| 40Dh               |          | Unimplemented   |               |                      |       |       |           |        |           |                      |                           |

|                    | -        | Unimplemented   |               |                      |       | 1     |           |        |           |                      |                           |

| 40Eh               | HIDRVC   | —               | —             | HIDC5                | HIDC4 |       | —         | —      | —         | 00                   | 00                        |

| 40Fh<br>to<br>412h | _        | Unimplemented   | Unimplemented |                      |       |       |           |        |           | -                    | —                         |

| 413h               | TMR4     | Timer4 Module   | Register      |                      |       |       |           |        |           | 0000 0000            | 0000 0000                 |

| 414h               | PR4      | Timer4 Period F | Register      |                      |       |       |           |        |           | 1111 1111            | 1111 1111                 |

| 415h               | T4CON    | ON              |               | CKPS<2:0>            |       |       | OUTP      | S<3:0> |           | 0000 0000            | 0000 0000                 |

| 416h               | T4HLT    | PSYNC           | CKPOL         | CKSYNC               |       |       | MODE<4:0> |        |           | 0000 0000            | 0000 0000                 |

| 417h               | T4CLKCON | —               | _             | —                    | —     |       | CS<       | 3:0>   |           | 0000                 | 0000                      |

| 418h               | T4RST    | —               | _             | —                    | —     |       | RSEL      | <3:0>  |           | 0000                 | 0000                      |

| 419h               | _        | Unimplemented   |               |                      |       |       |           |        |           | —                    | —                         |

| 41Ah               | TMR6     | Timer6 Module   | Register      |                      |       |       |           |        |           | 0000 0000            | 0000 0000                 |

| 41Bh               | PR6      | Timer6 Period F | Register      |                      |       |       |           |        |           | 1111 1111            | 1111 1111                 |

| 41Ch               | T6CON    | ON              |               | CKPS<2:0> OUTPS<3:0> |       |       |           |        | 0000 0000 | 0000 0000            |                           |

| 41Dh               | T6HLT    | PSYNC           | CKPOL         | CKSYNC               |       |       | MODE<4:0> |        |           | 0000 0000            | 0000 0000                 |

| 41Eh               | T6CLKCON |                 | _             |                      | —     |       | CS<       | 3:0>   |           | 0000                 | 0000                      |

| 41Fh               | T6RST    | —               | _             | —                    | —     |       | RSEL      | <3:0>  |           | 0000                 | 0000                      |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: PIC16F1614/8 only.

2: Unimplemented, read as '1'.

3: PIC16(L)F1614 only.

4: PIC16(L)F1618 only.

| TABLE 6-5: S | JMMARY OF REGISTERS ASSOCIATED WITH RESETS |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|---------|--------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| BORCON  | SBOREN | BORFS  | _     |       | —     | _     |       | BORRDY | 86                  |

| PCON    | STKOVF | STKUNF | WDTWV | RWDT  | RMCLR | RI    | POR   | BOR    | 90                  |

| STATUS  | _      | _      | _     | TO    | PD    | Z     | DC    | С      | 25                  |

| WDTCON0 |        |        |       |       | SEN   | 116   |       |        |                     |

Legend: — = unimplemented bit, reads as '0'. <u>Shaded</u> cells are not used by Resets.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

#### TABLE 6-6: SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4    | Bit 11/3 | Bit 10/2    | Bit 9/1  | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-------------|----------|-------------|----------|---------|---------------------|

|         | 13:8 |         | _       | _        |             | CLKOUTEN | BOREI       | N<1:0>   | _       | 07                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | _           | —        | _           | FOSC     | <1:0>   | 67                  |

|         | 13:8 | _       | _       | LVP      | DEBUG       | LPBOR    | BORV        | STVREN   | PLLEN   | 00                  |

| CONFIG2 | 7:0  | ZCD     | _       | _        | _           | —        | PPS1WAY     | WRT<1:0> |         | 68                  |

|         | 13:8 | _       | _       |          | WDTCCS<2:0> |          | WDTCWS<2:0> |          |         | 69                  |

| CONFIG3 | 7:0  | _       | WDT     | E<1:0>   |             | WD       | WDTCPS<4:0> |          |         |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

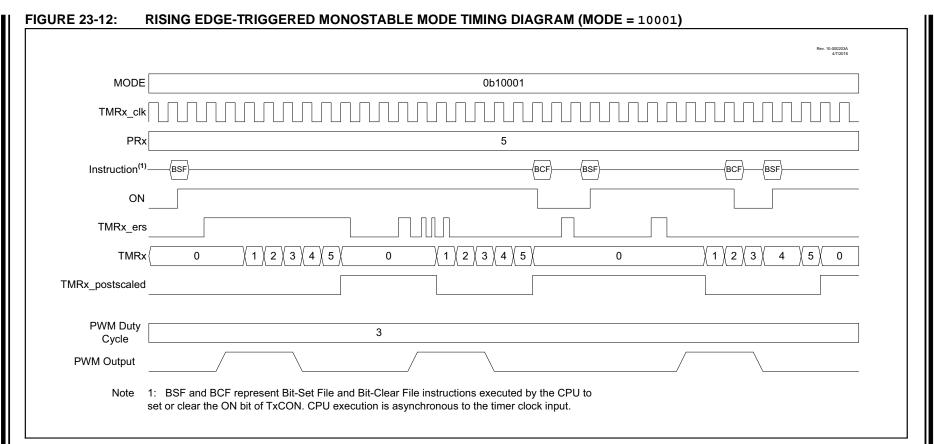

#### 23.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the PRx period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0> = 01011)

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 23-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the PRx period count match.

### FIGURE 23-9: EDGE-TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

| MODE                         | 0b01001                                                      |

|------------------------------|--------------------------------------------------------------|

| TMRx_clk                     |                                                              |

| PRx                          | 5                                                            |

| Instruction <sup>(1)</sup> - | {BSF}BCF                                                     |

| ON                           |                                                              |

| TMRx_ers                     |                                                              |

| TMRx                         | $0 \qquad 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 0 \qquad 1 \\ 2 \qquad 2$ |

| TMRx_out                     |                                                              |

| TMRx_postscaled _            |                                                              |

| PWM Duty<br>Cycle            | 3                                                            |

| PWM Output                   |                                                              |

PIC16(L)F1614/8

DS40001769B-page 279

| R-0/0            | R-1/1                                                                                                   | U-0                              | R/W-0/0                             | R/W-0/0         | U-0              | R/W-0/0           | R/W-0/0       |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|-----------------|------------------|-------------------|---------------|--|--|--|--|

| ABDOVF           | RCIDL                                                                                                   |                                  | SCKP                                | BRG16           |                  | WUE               | ABDEN         |  |  |  |  |

| bit 7            | •                                                                                                       |                                  |                                     |                 |                  |                   | bit C         |  |  |  |  |

|                  |                                                                                                         |                                  |                                     |                 |                  |                   |               |  |  |  |  |

| Legend:          |                                                                                                         |                                  |                                     |                 |                  |                   |               |  |  |  |  |

| R = Readable     | e bit                                                                                                   | W = Writable                     | e bit                               | U = Unimplen    | nented bit, rea  | d as '0'          |               |  |  |  |  |

| u = Bit is uncl  | nanged                                                                                                  | x = Bit is unl                   | known                               | -n/n = Value a  | at POR and BC    | OR/Value at all c | other Resets  |  |  |  |  |

| '1' = Bit is set |                                                                                                         | '0' = Bit is cl                  | eared                               |                 |                  |                   |               |  |  |  |  |

| bit 7            |                                                                                                         | uto Paud Doto                    | ct Overflow bit                     |                 |                  |                   |               |  |  |  |  |

|                  | ASynchronou                                                                                             |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         | ud timer overflo                 | wed                                 |                 |                  |                   |               |  |  |  |  |

|                  | 0 = Auto-bau                                                                                            | ud timer did no                  | t overflow                          |                 |                  |                   |               |  |  |  |  |

|                  | <u>Synchronou</u><br>Don't care                                                                         | <u>s mode</u> :                  |                                     |                 |                  |                   |               |  |  |  |  |

| bit 6            | RCIDL: Rec                                                                                              | eive Idle Flag b                 | bit                                 |                 |                  |                   |               |  |  |  |  |

|                  | Asynchronou                                                                                             |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         | 1 = Receiver is Idle             |                                     |                 |                  |                   |               |  |  |  |  |

|                  | <ul> <li>0 = Start bit has been received and the receiver is receiving<br/>Synchronous mode:</li> </ul> |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  | Don't care                                                                                              |                                  |                                     |                 |                  |                   |               |  |  |  |  |

| bit 5            | Unimpleme                                                                                               | nted: Read as                    | '0'                                 |                 |                  |                   |               |  |  |  |  |

| bit 4            | SCKP: Synchronous Clock Polarity Select bit                                                             |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  | Asynchronous mode:                                                                                      |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         |                                  | to the TX/CK p<br>data to the TX/0  |                 |                  |                   |               |  |  |  |  |

|                  | <u>Synchronou</u>                                                                                       |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         |                                  | g edge of the ong edge of the o     |                 |                  |                   |               |  |  |  |  |

| bit 3            | BRG16: 16-                                                                                              | bit Baud Rate                    | Generator bit                       |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         | aud Rate Gene<br>ud Rate Gener   |                                     |                 |                  |                   |               |  |  |  |  |

| bit 2            | Unimpleme                                                                                               | nted: Read as                    | <b>'</b> 0 <b>'</b>                 |                 |                  |                   |               |  |  |  |  |

| bit 1            | WUE: Wake                                                                                               | -up Enable bit                   |                                     |                 |                  |                   |               |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                      | <u>us mode</u> :                 |                                     |                 |                  |                   |               |  |  |  |  |

|                  |                                                                                                         | •                                | a falling edge.<br>after RCIF is se |                 | vill be received | d, byte RCIF wil  | l be set. WUE |  |  |  |  |

|                  |                                                                                                         | r is operating n                 |                                     |                 |                  |                   |               |  |  |  |  |

|                  | Synchronou:                                                                                             | <u>s mode</u> :                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  | Don't care                                                                                              |                                  |                                     |                 |                  |                   |               |  |  |  |  |

| bit 0            |                                                                                                         | to-Baud Detect                   | Enable bit                          |                 |                  |                   |               |  |  |  |  |

|                  | Asynchronou                                                                                             |                                  | la ia anchiad (-                    |                 | o houd is as     | valata)           |               |  |  |  |  |

|                  |                                                                                                         | iud Detect mod<br>iud Detect mod |                                     | clears when aut | o-daud is com    | ipiete)           |               |  |  |  |  |

|                  | Synchronous                                                                                             |                                  |                                     |                 |                  |                   |               |  |  |  |  |

|                  | Don't care                                                                                              |                                  |                                     |                 |                  |                   |               |  |  |  |  |

# REGISTER 25-3: BAUD1CON: BAUD RATE CONTROL REGISTER

#### 25.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCxSTA register) or the Continuous Receive Enable bit (CREN of the RCxSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCxREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

## 25.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

### 25.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCxREG is read to access the FIFO. When this happens the OERR bit of the RCxSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCxREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

### 25.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCxSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCxSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCxREG.

- 25.5.1.9 Synchronous Master Reception Setup:

- 1. Initialize the SPxBRGH, SPxBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCxSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCxREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCxSTA register or by clearing the SPEN bit which resets the EUSART.

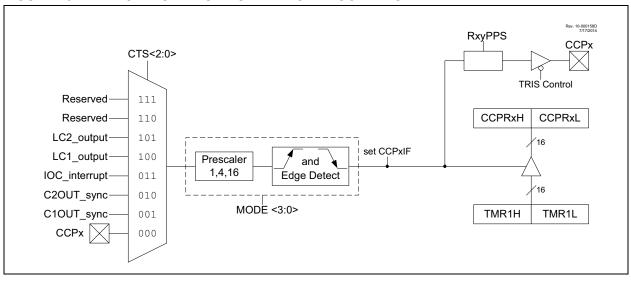

# FIGURE 26-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 26.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section22.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

#### 26.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock (Fosc) should not be used in Capture |  |  |  |  |  |  |  |

|-------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | mode. In order for Capture mode to                                         |  |  |  |  |  |  |  |

|       | recognize the trigger event on the CCPx                                    |  |  |  |  |  |  |  |

|       | pin, Timer1 must be clocked from the                                       |  |  |  |  |  |  |  |

|       | instruction clock (Fosc/4) or from an                                      |  |  |  |  |  |  |  |

|       | external clock source.                                                     |  |  |  |  |  |  |  |

## 26.1.4 CCP PRESCALER

There are four prescaler settings specified by the MODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the EN bit of the CCPxCON register before changing the prescaler.

# 26.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

## 26.1.6 CAPTURE OUTPUT

Whenever a capture occurs, the output of the CCP will go high for a period equal to one system clock period (1/Fosc). This output is available as an input signal to the CWG, as an auto-conversion trigger for the ADC, as an External Reset Signal for the TMR2 modules, as a window input to the SMT, and as an input to the CLC module. In addition, the CCPx pin output can be mapped to output pins through the use of PPS (see **13.2 "PPS Outputs"**).

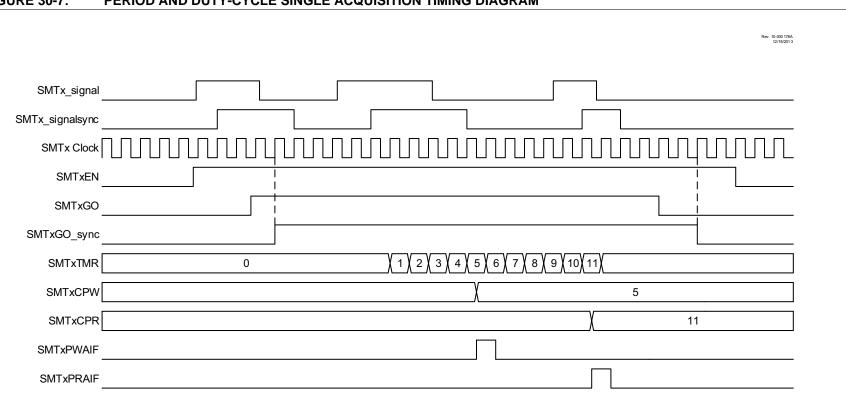

# FIGURE 30-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

PIC16(L)F1614/8

| R-x/x                                                                    | R-x/x | R-x/x             | R-x/x | R-x/x        | R-x/x            | R-x/x        | R-x/x |

|--------------------------------------------------------------------------|-------|-------------------|-------|--------------|------------------|--------------|-------|

|                                                                          |       |                   | SMTxC | CPR<7:0>     |                  |              |       |

| bit 7                                                                    |       |                   |       |              |                  |              | bit 0 |

|                                                                          |       |                   |       |              |                  |              |       |

| Legend:                                                                  |       |                   |       |              |                  |              |       |

| R = Readable I                                                           | bit   | W = Writable b    | oit   | U = Unimpler | nented bit, read | l as '0'     |       |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Valu |       |                   |       |              | R/Value at all   | other Resets |       |

| '1' = Bit is set                                                         |       | '0' = Bit is clea | red   |              |                  |              |       |

### REGISTER 30-12: SMTxCPRL: SMT CAPTURED PERIOD REGISTER – LOW BYTE

bit 7-0 SMTxCPR<7:0>: Significant bits of the SMT Period Latch – Low Byte

### REGISTER 30-13: SMTxCPRH: SMT CAPTURED PERIOD REGISTER - HIGH BYTE

| R-x/x | R-x/x | R-x/x | R-x/x  | R-x/x   | R-x/x | R-x/x | R-x/x |

|-------|-------|-------|--------|---------|-------|-------|-------|

|       |       |       | SMTxCP | R<15:8> |       |       |       |

| bit 7 |       |       |        |         |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPR<15:8>: Significant bits of the SMT Period Latch – High Byte

#### REGISTER 30-14: SMTxCPRU: SMT CAPTURED PERIOD REGISTER - UPPER BYTE

| R-x/x   | R-x/x | R-x/x | R-x/x   | R-x/x    | R-x/x | R-x/x | R-x/x |

|---------|-------|-------|---------|----------|-------|-------|-------|

|         |       |       | SMTxCPF | R<23:16> |       |       |       |

| bit 7   |       |       |         |          |       |       | bit 0 |

|         |       |       |         |          |       |       |       |

| Legend: |       |       |         |          |       |       |       |

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPR<23:16>: Significant bits of the SMT Period Latch – Upper Byte

| U-0             | U-0                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                | U-0                                                                         | U-0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------|------------------|------------------|--------------|

| _               | —                                                                                                                                                                                                                                                                                                                                                      | —                                                                                                                                                                                                                                                                                  | _                                                                           | —            | CC3IE            | CC2IE            | CC1IE        |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |                                                                             |              |                  |                  | bit (        |

|                 |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |                                                                             |              |                  |                  |              |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |                                                                             |              |                  |                  |              |

| R = Readab      | le bit                                                                                                                                                                                                                                                                                                                                                 | W = Writable                                                                                                                                                                                                                                                                       | bit                                                                         | U = Unimplei | mented bit, read | as '0'           |              |

| u = Bit is un   | changed                                                                                                                                                                                                                                                                                                                                                | x = Bit is unkr                                                                                                                                                                                                                                                                    | nown                                                                        | -n/n = Value | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se | et                                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is clea                                                                                                                                                                                                                                                                  | ared                                                                        | q = Value de | pends on condit  | ion              |              |

|                 |                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                    |                                                                             |              |                  |                  |              |

| bit 7-3         | Unimplemen                                                                                                                                                                                                                                                                                                                                             | ted: Read as '                                                                                                                                                                                                                                                                     | כ'                                                                          |              |                  |                  |              |

| bit 2<br>bit 1  | If CC3MODE           1 = Capture           0 = Capture           If CC3MODE           1 = Compare           0 = Compare           CC2IE: Capture           I = Capture           1 = Compare | ure/Compare In<br>= 1 (Capture)<br>interrupt 3 is er<br>interrupt 3 is dis<br>= 0 (Compare)<br>e interrupt 3 is e<br>e interrupt 3 is c<br>ure/Compare In<br>= 1 (Capture)<br>interrupt 2 is er<br>interrupt 2 is dis<br>= 0 (Compare)<br>e interrupt 2 is e<br>e interrupt 2 is e | nabled<br>sabled<br>lisabled<br>terrupt 2 Ena<br>nabled<br>sabled<br>mabled |              |                  |                  |              |

| bit 0           | If CC1MODE<br>1 = Capture<br>0 = Capture<br>If CC1MODE                                                                                                                                                                                                                                                                                                 | ure/Compare In<br>= 1 (Capture)<br>interrupt 1 is er<br>interrupt 1 is dis<br>= 0 (Compare)<br>e interrupt 1 is e                                                                                                                                                                  | abled<br>sabled                                                             | able bit     |                  |                  |              |

# REGISTER 31-15: ATxIE1: ANGULAR TIMER ENABLE 1 REGISTER

0 = Compare interrupt 1 is disabled

| Mnen     | nonic, | Description                                   | Cycles |     | 14-Bit | Opcode | •    | Status   | Notes |

|----------|--------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands |        | Description                                   | Cycles | MSb |        |        | LSb  | Affected | NOLES |

|          |        | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA      | k      | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW      | -      | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL     | k      | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW    | -      | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO     | k      | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE   | k      | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW    | k      | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN   | -      | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|          |        |                                               | TIONS  |     |        |        |      | •        |       |

| CLRWDT   | _      | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP      | -      | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION   | -      | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET    | -      | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP    | -      | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS     | f      | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|          |        | C-COMPILER OPT                                | IMIZED |     |        |        |      | •        |       |

| ADDFSR   | n, k   | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW    | n mm   | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|          |        | modifier, mm                                  |        |     |        |        | kkkk |          |       |

|          | k[n]   | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | 1nmm | Z        | 2     |

| MOVWI    | n mm   | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | kkkk |          | 2, 3  |

|          |        | modifier, mm                                  |        |     |        |        |      |          |       |

|          | k[n]   | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   |      |          | 2     |

### TABLE 34-3: ENHANCED MID-RANGE INSTRUCTION SET (CONTINUED)

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

**3:** See Table in the MOVIW and MOVWI instruction descriptions.

# 35.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:  $V \text{DDMIN} \leq V \text{DD} \leq V \text{DDMAX}$ Operating Voltage: Operating Temperature: TA MIN  $\leq$  TA  $\leq$  TA MAX VDD — Operating Supply Voltage<sup>(1)</sup> PIC16LF1614/8 PIC16F1614/8 TA — Operating Ambient Temperature Range Industrial Temperature TA MIN.....--40°C **Extended Temperature** Ta MIN.....--40°C

Note 1: See Parameter D001, DS Characteristics: Supply Voltage.

| Param.<br>No. | Sym.   | Characteristic                               | Min.   | Тур† | Max.   | Units | Conditions                                                           |

|---------------|--------|----------------------------------------------|--------|------|--------|-------|----------------------------------------------------------------------|

|               |        | Program Memory<br>Programming Specifications |        |      |        |       |                                                                      |

| D110          | VIHH   | Voltage on MCLR/VPP pin                      | 8.0    | _    | 9.0    | V     | (Note 2)                                                             |

| D111          | IDDP   | Supply Current during<br>Programming         | —      | —    | 10     | mA    |                                                                      |

| D112          | VBE    | VDD for Bulk Erase                           | 2.7    |      | VDDMAX | V     |                                                                      |

| D113          | VPEW   | VDD for Write or Row Erase                   | VDDMIN |      | VDDMAX | V     |                                                                      |

| D114          | IPPPGM | Current on MCLR/VPP during<br>Erase/Write    | —      | 1.0  | —      | mA    |                                                                      |

| D115          | IDDPGM | Current on VDD during Erase/<br>Write        | —      | 5.0  | —      | mA    |                                                                      |

| D121          | Ер     | Program Flash Memory<br>Cell Endurance       | 10K    | _    | _      | E/W   | -40°C ≤ TA ≤ +85°C<br>(Note 1)                                       |

| D122          | VPRW   | VDD for Read/Write                           | VDDMIN | _    | VDDMAX | V     |                                                                      |

| D123          | Tiw    | Self-timed Write Cycle Time                  | _      | 2    | 2.5    | ms    |                                                                      |

| D124          | TRETD  | Characteristic Retention                     | —      | 40   | —      | Year  | Provided no other specifications are violated                        |

| D125          | EHEFC  | High-Endurance Flash Cell                    | 100K   |      |        | E/W   | $0^{\circ}C \le TA \le +60^{\circ}C$ , lower byte last 128 addresses |

# TABLE 35-5: MEMORY PROGRAMMING SPECIFICATIONS

Standard Operating Conditions (unless otherwise stated)

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Self-write and Block Erase.

**2:** Required only if single-supply programming is disabled.

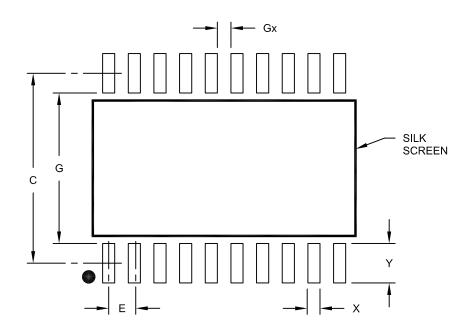

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units            |          |      |      |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          |      | MAX  |  |

| Contact Pitch            | E                | 1.27 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 9.40 |      |  |

| Contact Pad Width (X20)  | X                |          |      | 0.60 |  |

| Contact Pad Length (X20) | Y                |          |      | 1.95 |  |

| Distance Between Pads    | Gx               | 0.67     |      |      |  |

| Distance Between Pads    | G                | 7.45     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A

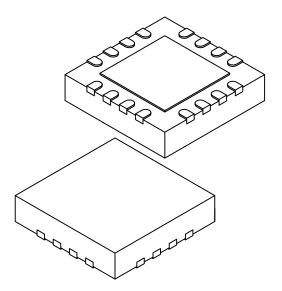

# 16-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4x0.9mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |                |          | S    |  |

|------------------------|-------|----------------|----------|------|--|

| Dimension              | MIN   | NOM            | MAX      |      |  |

| Number of Pins         | Ν     |                | 16       |      |  |

| Pitch                  | е     |                | 0.65 BSC |      |  |

| Overall Height         | Α     | 0.80           | 0.90     | 1.00 |  |

| Standoff               | A1    | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3    | 0.20 REF       |          |      |  |

| Overall Width          | E     | 4.00 BSC       |          |      |  |

| Exposed Pad Width      | E2    | 2.50           | 2.65     | 2.80 |  |

| Overall Length         | D     | 4.00 BSC       |          |      |  |

| Exposed Pad Length     | D2    | 2.50 2.65 2.80 |          |      |  |

| Contact Width          | b     | 0.25           | 0.30     | 0.35 |  |

| Contact Length         | L     | 0.30           | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | К     | 0.20           | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-127D Sheet 2 of 2

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support