# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 640 × 8                                                              |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |

| Data Converters            | A/D 5x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 20-SO                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s103f2m6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introd | luction                                                        | 9  |

|---|--------|----------------------------------------------------------------|----|

| 2 | Descr  | ription                                                        | 10 |

| 3 | Block  | diagram                                                        | 11 |

| 4 | Produ  | act overview                                                   | 12 |

|   | 4.1    | Central processing unit STM8                                   | 12 |

|   | 4.2    | Single wire interface module (SWIM) and debug module (DM)      | 13 |

|   | 4.3    | Interrupt controller                                           | 13 |

|   | 4.4    | Flash program and data EEPROM memory                           | 13 |

|   | 4.5    | Clock controller                                               | 15 |

|   | 4.6    | Power management                                               | 16 |

|   | 4.7    | Watchdog timers                                                | 16 |

|   | 4.8    | Auto wakeup counter                                            | 17 |

|   | 4.9    | Beeper                                                         | 17 |

|   | 4.10   | TIM1 - 16-bit advanced control timer                           | 17 |

|   | 4.11   | TIM2 - 16-bit general purpose timer                            | 17 |

|   | 4.12   | TIM4 - 8-bit basic timer                                       | 18 |

|   | 4.13   | Analog-to-digital converter (ADC1)                             | 18 |

|   | 4.14   | Communication interfaces                                       | 18 |

|   |        | 4.14.1 UART1                                                   | 19 |

|   |        | 4.14.2 SPI                                                     | -  |

|   |        | 4.14.3 l <sup>2</sup> C                                        | 20 |

| 5 | Pinou  | It and pin description                                         | 21 |

|   | 5.1    | STM8S103K3 UFQFPN32/LQFP32/SDIP32 pinout and pin description   | 22 |

|   | 5.2    | STM8S103F2/F3 TSSOP20/SO20/UFQFPN20 pinout and pin description |    |

|   |        | 5.2.1 STM8S103F2/F3 TSSOP20/SO20 pinout                        | 26 |

|   |        | 5.2.2 STM8S103F2/F3 UFQFPN20 pinout                            | 27 |

|   | 5.3    | Alternate function remapping                                   | 30 |

DocID15441 Rev 14

# 1 Introduction

This datasheet contains the description of the device features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 5 Pinout and pin description

| Туре                           | I= Input, O = Output, S = Power supply                                                                                                                                                                |                                                            |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| Level                          | Input                                                                                                                                                                                                 | CM = CMOS                                                  |  |  |  |

|                                | Output                                                                                                                                                                                                | HS = High sink                                             |  |  |  |

| Output speed                   | O1 = Slow (up to 2 MHz)<br>O2 = Fast (up to 10 MHz)<br>O3 = Fast/slow programmability with slow as default state after reset<br>O4 = Fast/slow programmability with fast as default state after reset |                                                            |  |  |  |

| Dent and a sector              | Input float = floating,<br>wpu = weak pull-up                                                                                                                                                         |                                                            |  |  |  |

| Port and control configuration | Output                                                                                                                                                                                                | T = True open drain,<br>OD = Open drain,<br>PP = Push pull |  |  |  |

| Reset state                    | Bold <b>X</b> (pin state after internal reset release).<br>Unless otherwise specified, the pin state is the same during the reset<br>phase and after the internal reset release.                      |                                                            |  |  |  |

#### Table 4. Legend/abbreviations for pin description tables

|            |          |                                                           |      |          | Input |                |                          | Out   | put |    | c                              | ate                                                                         | ion                                               |

|------------|----------|-----------------------------------------------------------|------|----------|-------|----------------|--------------------------|-------|-----|----|--------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

| TSSOP/SO20 | UFQFPN20 | Pin name                                                  | Type | floating | ndw   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | QD  | ΡР | Main function<br>(after reset) | Default alternate<br>function                                               | Alternate function<br>after remap<br>[option bit] |

| 14         | 11       | PC4/<br>CLK_CCO/<br>TIM1_<br>CH4/AIN2/[<br>TIM1_<br>CH2N] | I/O  | x        | x     | x              | HS                       | O3    | x   | x  | Port C4                        | Configurable<br>clock<br>output/Timer 1<br>- channel<br>4/Analog input<br>2 | Timer 1 -<br>inverted<br>channel 2<br>[AFR7]      |

| 15         | 12       | PC5/<br>SPI_SCK<br>[TIM2_CH1]                             | I/O  | x        | x     | x              | HS                       | O3    | x   | х  | Port C5                        | SPI clock                                                                   | Timer 2 -<br>channel 1<br>[AFR0]                  |

| 16         | 13       | PC6/<br>SPI_MOSI<br>[TIM1_CH1]                            | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port C6                        | SPI master<br>out/slave in                                                  | Timer 1 -<br>channel 1<br>[AFR0]                  |

| 17         | 14       | PC7/<br>SPI_MISO<br>[TIM1_CH2]                            | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port C7                        | SPI master in/<br>slave out                                                 | Timer 1 -<br>channel 2<br>[AFR0]                  |

| 18         | 15       | PD1/ SWIM                                                 | I/O  | х        | х     | х              | HS                       | 04    | х   | х  | Port D1                        | SWIM data<br>interface                                                      | -                                                 |

| 19         | 16       | PD2/AIN3/[T<br>IM2_CH3]                                   | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port D2                        | Analog input 3                                                              | Timer 2 -<br>channel 3<br>[AFR1]                  |

| 20         | 17       | PD3/ AIN4/<br>TIM2_CH2/<br>ADC_ETR                        | I/O  | x        | х     | х              | HS                       | O3    | х   | х  | Port D3                        | Analog input 4/<br>Timer 2 -<br>channel 2/ADC<br>external trigger           | -                                                 |

#### Table 6. STM8S103F2 and STM8S103F3 pin descriptions (continued)

1. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings.

2. When the MCU is in halt/active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if halt/active-halt is used in the application.

3. In the open-drain output column, "T" defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented).1

| Address                | Block | Register label | Register name                      | Reset status |

|------------------------|-------|----------------|------------------------------------|--------------|

| 0x00 5208 to 0x00 520F |       | Rese           | rved area (8 byte)                 |              |

| 0x00 5210              |       | I2C_CR1        | I2C control register 1             | 0x00         |

| 0x00 5211              |       | I2C_CR2        | I2C control register 2             | 0x00         |

| 0x00 5212              |       | I2C_FREQR      | I2C frequency register             | 0x00         |

| 0x00 5213              |       | I2C_OARL       | I2C Own address register low       | 0x00         |

| 0x00 5214              |       | I2C_OARH       | I2C Own address register<br>high   | 0x00         |

| 0x00 5215              |       |                | Reserved                           |              |

| 0x00 5216              |       | I2C_DR         | I2C data register                  | 0x00         |

| 0x00 5217              | I2C   | I2C_SR1        | I2C status register 1              | 0x00         |

| 0x00 5218              |       | I2C_SR2        | I2C status register 2              | 0x00         |

| 0x00 5219              |       | I2C_SR3        | I2C status register 3              | 0x0X         |

| 0x00 521A              |       | I2C_ITR        | I2C interrupt control register     | 0x00         |

| 0x00 521B              |       | I2C_CCRL       | I2C Clock control register low     | 0x00         |

| 0x00 521C              |       | I2C_CCRH       | I2C Clock control register high    | 0x00         |

| 0x00 521D              |       | I2C_TRISER     | I2C TRISE register                 | 0x02         |

| 0x00 521E              |       | I2C_PECR       | I2C packet error checking register | 0x00         |

| 0x00 521F to 0x00 522F |       | Reser          | ved area (17 byte)                 |              |

| 0x00 5230              |       | UART1_SR       | UART1 status register              | 0xC0         |

| 0x00 5231              |       | UART1_DR       | UART1 data register                | 0xXX         |

| 0x00 5232              |       | UART1_BRR1     | UART1 baud rate register 1         | 0x00         |

| 0x00 5233              |       | UART1_BRR2     | UART1 baud rate register 2         | 0x00         |

| 0x00 5234              |       | UART1_CR1      | UART1 control register 1           | 0x00         |

| 0x00 5235              | UART1 | UART1_CR2      | UART1 control register 2           | 0x00         |

| 0x00 5236              |       | UART1_CR3      | UART1 control register 3           | 0x00         |

| 0x00 5237              |       | UART1_CR4      | UART1 control register 4           | 0x00         |

| 0x00 5238              |       | UART1_CR5      | UART1 control register 5           | 0x00         |

| 0x00 5239              |       | UART1_GTR      | UART1 guard time register          | 0x00         |

| 0x00 523A              |       | UART1_PSCR     | UART1 prescaler register           | 0x00         |

| 0x00 523B to 0x00 523F |       | Reser          | ved area (21 byte)                 |              |

Table 8. General hardware register map (continued)

# **10** Electrical characteristics

# 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C, and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3 \Sigma$ ).

# 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5.0$  V. They are given only as design guidelines and are not tested.

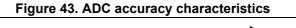

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2 \Sigma$ ).

# 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 10.1.4 Loading capacitor

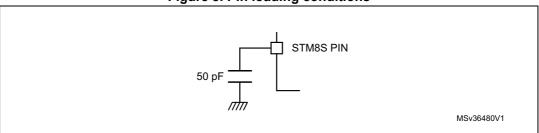

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

#### Figure 8. Pin loading conditions

# 10.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 9*.

| Symbol                        | Parameter                                | Conditions                   | Min | Max | Unit |

|-------------------------------|------------------------------------------|------------------------------|-----|-----|------|

|                               | TSSOP20                                  | TSSOP20                      | -   | 59  |      |

|                               |                                          | SO20W                        | -   | 55  |      |

| P <sub>D</sub> <sup>(3)</sup> | Power dissipation                        | UFQFPN20                     | -   | 55  |      |

| PD                            | at T <sub>A</sub> = 125 °C for suffix 3  | LQFP32                       | -   | 83  | mW   |

|                               |                                          | UFQFPN32                     | -   | 132 |      |

|                               |                                          | SDIP32                       | -   | 83  |      |

| T <sub>A</sub>                | Ambient temperature for suffix 6 version | Maximum power<br>dissipation | -40 | 85  |      |

| T <sub>A</sub>                | Ambient temperature for suffix 3 version | Maximum power<br>dissipation | -40 | 125 | °C   |

| т                             | Junction temperature range               | Suffix 6 version             | -40 | 105 |      |

| ТJ                            |                                          | Suffix 3 version             | -40 | 130 |      |

Table 19. General operating conditions (continued)

1. Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{\mbox{CAP}}$  parameters is given by design of internal regulator.

To calculate P<sub>Dmax</sub>(T<sub>A</sub>), use the formula P<sub>Dmax</sub>=(T<sub>Jmax</sub>- T<sub>A</sub>)/Θ<sub>JA</sub> (see Section 12: Thermal characteristics) with the value for T<sub>Jmax</sub> given in the previous table and the value for Θ<sub>JA</sub> given in Section 12: Thermal characteristics

#### Table 20. Operating conditions at power-up/power-down

| Symbol           | Parameter                                     | Conditions | Min | Тур | Max | Unit  |

|------------------|-----------------------------------------------|------------|-----|-----|-----|-------|

| t <sub>VDD</sub> | V <sub>DD</sub> rise time rate                | -          | 2   | -   | ∞   | us/V  |

|                  | V <sub>DD</sub> fall time rate <sup>(1)</sup> | -          | 2   | -   | 8   | μ5/ V |

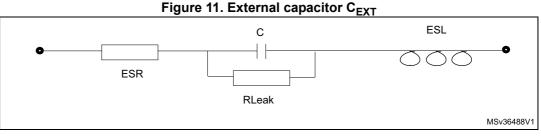

# 10.3.1 VCAP external capacitor

The stabilization for the main regulator is achieved by connecting an external capacitor  $C_{\text{EXT}}$  to the V<sub>CAP</sub> pin.  $C_{\text{EXT}}$  is specified in *Table 19*. Care should be taken to limit the series inductance to less than 15 nH.

1. ESR is the equivalent series resistance and ESL is the equivalent inductance.

### **10.3.2** Supply current characteristics

The current consumption is measured as illustrated in Figure 9: Pin input voltage.

#### Total supply current consumption in run mode

The MCU is placed under the following conditions:

- All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled (clock stopped by peripheral clock gating registers) except if explicitly mentioned.

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol               | Parameter            | Conditi                                                     | ons                             | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------|-------------------------------------------------------------|---------------------------------|------|--------------------|------|

|                      |                      |                                                             | HSE crystal osc. (16 MHz)       | 2.3  | -                  |      |

|                      |                      | t <sub>CPU</sub> = t <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock<br>(16 MHz) | 2    | 2.35               |      |

|                      | Supply<br>current in |                                                             | HSI RC osc. (16 MHz)            | 1.7  | 2                  |      |

| I <sub>DD(RUN)</sub> | Run mode,<br>code    | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSE user ext. clock<br>(16 MHz) | 0.86 | -                  | mA   |

|                      | executed<br>from RAM |                                                             | HSI RC osc. (16 MHz)            | 0.7  | 0.87               |      |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)          | 0.46 | 0.58               |      |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)           | 0.41 | 0.55               |      |

# Total current consumption in active halt mode

|         | Parameter           |                                                      | Conditio                  | ns                           |      |                                |                                |      |

|---------|---------------------|------------------------------------------------------|---------------------------|------------------------------|------|--------------------------------|--------------------------------|------|

| Symbol  |                     | Main<br>voltage<br>regulator<br>(MVR) <sup>(2)</sup> | Flash mode <sup>(3)</sup> | Clock source                 | Тур  | Max at<br>85 °C <sup>(1)</sup> | Max at<br>85 °C <sup>(1)</sup> | Unit |

|         |                     |                                                      | Operating mode            | HSE crystal osc.<br>(16 MHz) | 1030 | -                              | -                              |      |

|         |                     |                                                      | Operating mode            | LSI RC osc. (128 kHz)        | 200  | 260                            | 300                            |      |

| 1       | Supply current in   | On                                                   | Power down<br>mode        | HSE crystal osc.<br>(16 MHz) | 970  | -                              | -                              | μA   |

| IDD(AH) | active halt<br>mode |                                                      | Power down<br>mode        | LSI RC osc. (128 kHz)        | 150  | 200                            | 230                            | μΛ   |

|         |                     |                                                      | Operating mode            | LSI RC osc. (128 kHz)        | 66   | 85                             | 110                            |      |

|         |                     | Off                                                  | Power down<br>mode        | LSI RC osc. (128 kHz)        | 10   | 20                             | 40                             |      |

#### Table 25. Total current consumption in active halt mode at $V_{DD}$ = 5 V

1. Guaranteed by characterization results.

2. Configured by the REGAH bit in the CLK\_ICKR register.

3. Configured by the AHALT bit in the FLASH\_CR1 register.

# Table 26. Total current consumption in active halt mode at $V_{DD}$ = 3.3 V

|         | Parameter         |                                                      | Conditio                  | ns                           |     |                                |                                |      |

|---------|-------------------|------------------------------------------------------|---------------------------|------------------------------|-----|--------------------------------|--------------------------------|------|

| Symbol  |                   | Main<br>voltage<br>regulator<br>(MVR) <sup>(2)</sup> | Flash mode <sup>(3)</sup> | Clock source                 | Тур | Max at<br>85 °C <sup>(1)</sup> | Max at<br>85 °C <sup>(1)</sup> | Unit |

|         |                   |                                                      | Operating mode            | HSE crystal osc.<br>(16 MHz) | 550 | -                              | -                              |      |

|         |                   |                                                      | Operating mode            | LSI RC osc. (128 kHz)        | 200 | 260                            | 290                            |      |

|         | Supply current in | On                                                   | Power down<br>mode        | HSE crystal osc.<br>(16 MHz) | 970 | -                              | -                              | μA   |

| IDD(AH) | active halt mode  |                                                      | Power down<br>mode        | LSI RC osc. (128 kHz)        | 150 | 200                            | 230                            | μΛ   |

|         |                   |                                                      | Operating mode            | LSI RC osc. (128 kHz)        | 66  | 80                             | 105                            |      |

|         |                   | Off                                                  | Power down<br>mode        | LSI RC osc. (128 kHz)        | 10  | 18                             | 35                             |      |

1. Guaranteed by characterization results.

2. Configured by the REGAH bit in the CLK\_ICKR register.

3. Configured by the AHALT bit in the FLASH\_CR1 register.

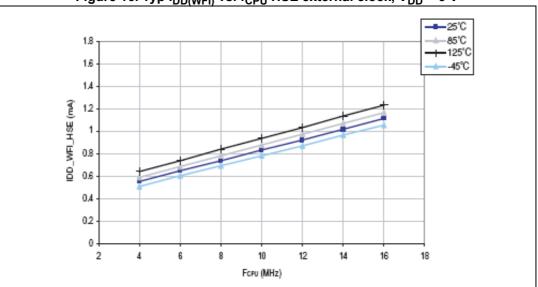

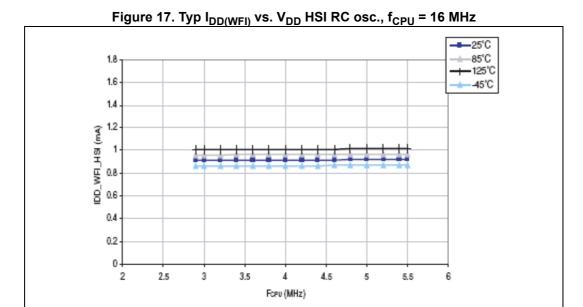

Figure 16. Typ  $I_{DD(WFI)}$  vs.  $f_{CPU}$  HSE external clock,  $V_{DD}$  = 5 V

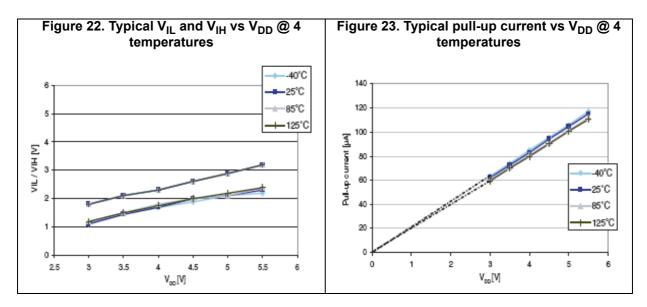

# 10.3.6 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                          | Conditions                                  | Min                   | Тур | Мах                     | Unit |

|---------------------------------|------------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                 | Input low level voltage            |                                             | -0.3 V                | -   | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                 | Input high level voltage           | V <sub>DD</sub> = 5 V                       | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | v    |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>          |                                             | -                     | 700 | -                       | mV   |

| R <sub>pu</sub>                 | Pull-up resistor                   | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time                 | Fast I/Os<br>Load = 50 pF                   | -                     | -   | 35 <sup>(2)</sup>       | 20   |

|                                 | (10% - 90%)                        | Standard and high sink I/Os<br>Load = 50 pF | -                     | -   | 125 <sup>(2)</sup>      | ns   |

|                                 | Rise and fall time                 | Fast I/Os<br>Load = 20 pF                   | -                     | -   | 20 <sup>(2)</sup>       | 20   |

| t <sub>R</sub> , t <sub>F</sub> | (10% - 90%)                        | Standard and high sink I/Os<br>Load = 20 pF | -                     | -   | 50 <sup>(2)</sup>       | ns   |

| I <sub>lkg</sub>                | Digital input leakage<br>current   | $V_{SS} \leq V_{IN} \leq V_{DD}$            | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

| I <sub>Ikg ana</sub>            | Analog input leakage current       | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±250 <sup>(3)</sup>     | nA   |

| I <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O | Injection current ±4 mA                     | -                     | -   | ±1 <sup>(3)</sup>       | μA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

2. Data guaranteed by design.

3. Guaranteed by characterization results

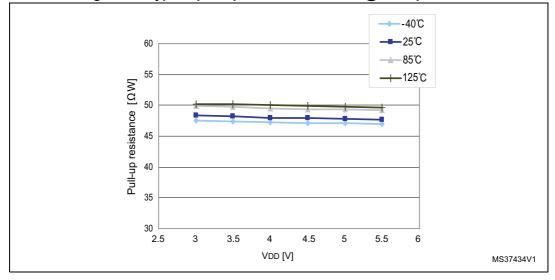

Figure 24. Typical pull-up resistance vs VDD @ 4 temperatures

| Symbol          | Parameter                             | Conditions                                         | Min                | Мах                | Unit |

|-----------------|---------------------------------------|----------------------------------------------------|--------------------|--------------------|------|

| N               | Output low level with 8<br>pins sunk  | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | -                  | 2.0                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | -                  | 1.0 <sup>(1)</sup> | V    |

|                 | Output high level with 8 pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | 2.8                | -                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | 2.1 <sup>(1)</sup> | -                  |      |

1. Guaranteed by characterization results

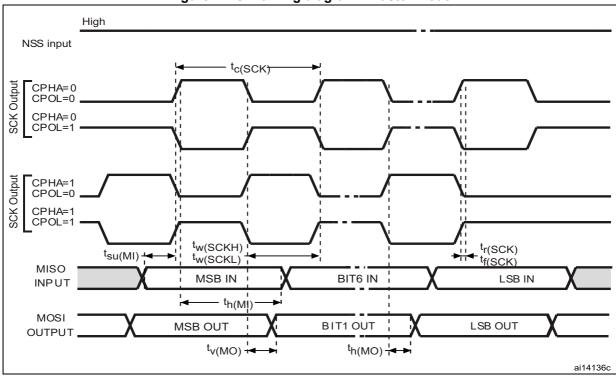

Figure 41. SPI timing diagram - master mode

1. Measurement points are at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|

|                | <b>T</b>                                    | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz | 1.9 | 4                  |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 2 MHz | 1   | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 4 MHz | 1.5 | 2.5                |      |

|                | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 1.3 | 3                  | LSB  |

| E <sub>G</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 2   | 3                  | LOD  |

|                | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.0                |      |

| E <sub>D</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

| EL             | Integral linearity error <sup>(2)</sup>     | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

1. Guaranteed by characterization results.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another 2. analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 10.3.6 does not affect the ADC accuracy.

- 1. Example of an actual transfer curve

- The ideal transfer curve 2.

- End point correlation line 3.

$E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_O$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.

$E_D = Differential linearity error: maximum deviation between any actual steps and the ideal one.$  $<math>E_L = Integral linearity error: maximum deviation between any actual transition and the end point correlation$ line.

# **10.3.11 EMC characteristics**

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709 (EMC design guide for STM microcontrollers).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring. See application note AN1015 (Software techniques for improving microcontroller EMC performance).

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                          | Level/class        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>$f_{MASTER}$ = 16 MHz (HSI clock),<br>Conforms to IEC 61000-4-2 | 2/B <sup>(1)</sup> |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C,<br>$f_{MASTER}$ = 16 MHz (HSI clock),<br>Conforms to IEC 61000-4-4 | 4/A <sup>(1)</sup> |

Table 48. EMS data

1. Data obtained with HSI clock configuration, after applying the hardware recommendations described in AN2860 (EMC guidelines for STM8S microcontrollers).

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC 61967-2 which specifies the board and the loading of each pin.

|                  |                                 | Conditions                                                                           |                        |                                     |                   |      |  |

|------------------|---------------------------------|--------------------------------------------------------------------------------------|------------------------|-------------------------------------|-------------------|------|--|

| Symbol           | Parameter                       | General conditions                                                                   | Monitored              | Max f <sub>CPU</sub> <sup>(1)</sup> |                   | Unit |  |

|                  |                                 |                                                                                      | frequency band         | 16 MHz/<br>8 MHz                    | 16 MHz/<br>16 MHz |      |  |

|                  |                                 | $V_{DD} = 5 V,$<br>$T_A = 25 °C,$<br>LQFP32 package.<br>Conforming to<br>IEC 61967-2 | V <sub>DD</sub> = 5 V, | 0.1 MHz to 30 MHz                   | 5                 | 5    |  |

| S <sub>EMI</sub> | Peak level T <sub>A</sub><br>LC |                                                                                      | 30 MHz to 130 MHz      | 4                                   | 5                 | dBµV |  |

|                  |                                 |                                                                                      | 130 MHz to 1 GHz       | 5                                   | 5                 |      |  |

|                  | EMI level                       |                                                                                      | EMI level              | 2.5                                 | 2.5               | -    |  |

|  | Table | 49. | EMI | data |

|--|-------|-----|-----|------|

|--|-------|-----|-----|------|

1. Guaranteed by characterization results.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD, DLU and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts x (n+1) supply pin). One model can be simulated: Human body model. This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings Conditions                                       |                                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|---------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114                     | А     | 4000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage<br>(Charge device model) | T <sub>A</sub> = 25°C, conforming to<br>SD22-C101<br>LQFP32 package | IV    | 1000                            | V    |

Table 50. ESD absolute maximum ratings

1. Guaranteed by characterization results

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin), and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

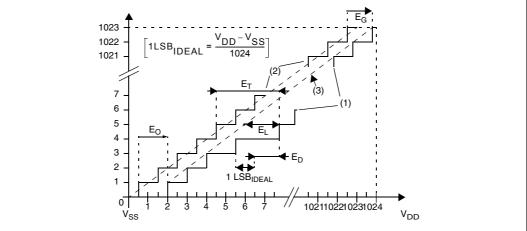

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **Temperature range**

[] -40°C to +85°C or [] -40°C to +125°C

#### Padding value for unused program memory (check only one option)

| []0xFF | Fixed value                                   |

|--------|-----------------------------------------------|

| []0x83 | TRAP instruction code                         |

| []0x75 | Illegal opcode (causes a reset when executed) |

#### OTP0 memory readout protection (check only one option)

[] Disable or [] Enable

#### OTP1 user boot code area (UBC)

0x(\_\_) fill in the hexadecimal value, referring to the datasheet and the binary format below:

| UBC, bit0 | [] 0: Reset<br>[] 1: Set |

|-----------|--------------------------|

| UBC, bit1 | [] 0: Reset<br>[] 1: Set |

| UBC, bit2 | [] 0: Reset<br>[] 1: Set |

| UBC, bit3 | [] 0: Reset<br>[] 1: Set |

| UBC, bit4 | [] 0: Reset<br>[] 1: Set |

| UBC, bit5 | [] 0: Reset<br>[] 1: Set |

| UBC, bit6 | [] 0: Reset<br>[] 1: Set |

| UBC, bit7 | [] 0: Reset<br>[] 1: Set |

#### OTP0 memory readout protection (check only one option)

[] Disable or [] Enable

#### OTP2 alternate function remapping for STM8S103K

Do not use more than one remapping option in the same port. It is forbidden to enable both AFR1 and AFR0.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Oct-1999 | 4        | <ul> <li>Replaced VFQFPN32 package by UFQFPN32 package.</li> <li>Section 4.5: Clock controller: replaced TIM2 and TIM3 with reserved and TIM2 respectively in Table 2: Peripheral clock gating bit assignments in CLK_PCKENR1/2 registers</li> <li>Total current consumption in halt mode: changed the maximum current consumption limit at 125 °C (and VDD= 5 V) from 35 μA to 55 μA.</li> <li>Functional EMS (electromagnetic susceptibility): renamed ESD as FESD (functional); added name of AN1709; replaced EC 1000 with IEC 61000.</li> <li>Designing hardened software to avoid noise problems: replaced IEC 1000 with IEC 61000, added title of AN1015, and added footnote to EMS data table.</li> <li>Electromagnetic interference (EMI): replaced J 1752/3 with IEC 61967-2 and updated data of the EMI data table.</li> <li>Section 12.2: Selecting the product temperature range: changed the value of LQFP32 7x7 mm thermal resistance from 59 °C/W to 60 °C/W.</li> <li>Added Section 13.1: STM8S103 FASTROM microcontroller option list.</li> </ul> |

| 22-Apr-2010 | 5        | <ul> <li>Added VFQFPN32 and SO20 packages.</li> <li>Updated Px_IDR reset value in <i>Table 7: I/O port hardware register</i> map.</li> <li>Section 10.3: Operating conditions: updated VCAP and ESR low limit, added ESL parameter, and Note 1 below <i>Table 19: General</i> operating conditions</li> <li>Updated ACCHSI in <i>Table 34: HSI oscillator characteristics</i>. Modified IDD(H)inand. Removed note 3 related to Accuracy of HSI oscillator.</li> <li>Updated maximum power dissipation in <i>Table 19: General operating</i> conditions.</li> <li>Updated Section 12: Thermal characteristics</li> <li>Replaced package pitch digit by VFQFPN/UFQFPN package digit in <i>Figure 63: STM8S103F2/x3 access line ordering information</i> scheme<sup>(1)</sup>, and removed note 1.</li> </ul>                                                                                                                                                                                                                                                          |

| Table 59. | <b>Document revision</b> | history |

|-----------|--------------------------|---------|

|-----------|--------------------------|---------|

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID15441 Rev 14