Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |  |

|----------------------------|----------------------------------------------------------------------|--|

| Product Status             | Active                                                               |  |

| Core Processor             | STM8                                                                 |  |

| Core Size                  | 8-Bit                                                                |  |

| Speed                      | 16MHz                                                                |  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                      |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |  |

| Number of I/O              | 16                                                                   |  |

| Program Memory Size        | 8KB (8K x 8)                                                         |  |

| Program Memory Type        | FLASH                                                                |  |

| EEPROM Size                | 640 x 8                                                              |  |

| RAM Size                   | 1K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |  |

| Data Converters            | A/D 5x10b                                                            |  |

| Oscillator Type            | Internal                                                             |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |  |

| Mounting Type              | Surface Mount                                                        |  |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                       |  |

| Supplier Device Package    | 20-SO                                                                |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s103f3m3 |  |

|    | 11.2  | UFQFPN32 package information                 |

|----|-------|----------------------------------------------|

|    | 11.3  | UFQFPN20 package information                 |

|    | 11.4  | SDIP32 package information                   |

|    | 11.5  | TSSOP20 package information                  |

|    | 11.6  | SO20 package information                     |

|    | 11.7  | UFQFPN recommended footprint                 |

| 12 | Ther  | mal characteristics 106                      |

|    | 12.1  | Reference document                           |

|    | 12.2  | Selecting the product temperature range      |

| 13 | Orde  | ring information                             |

|    | 13.1  | STM8S103 FASTROM microcontroller option list |

| 14 | STM   | B development tools                          |

|    | 14.1  | Emulation and in-circuit debugging tools113  |

|    |       | 14.1.1 STice key features                    |

|    | 14.2  | Software tools                               |

|    |       | 14.2.1 STM8 toolset                          |

|    |       | 14.2.2 C and assembly toolchains             |

|    | 14.3  | Programming tools                            |

| 15 | Revis | sion history 116                             |

# List of tables

| Table 1.  | STM8S103F2/x3 access line features                                                          | 10 |

|-----------|---------------------------------------------------------------------------------------------|----|

| Table 2.  | Peripheral clock gating bit assignments in CLK_PCKENR1/2 registers                          | 15 |

| Table 3.  | TIM timer features                                                                          | 18 |

| Table 4.  | Legend/abbreviations for pin description tables                                             | 21 |

| Table 5.  | STM8S103K3 pin descriptions                                                                 | 23 |

| Table 6.  | STM8S103F2 and STM8S103F3 pin descriptions                                                  | 28 |

| Table 7.  | I/O port hardware register map                                                              | 32 |

| Table 8.  | General hardware register map                                                               | 33 |

| Table 9.  | CPU/SWIM/debug module/interrupt controller registers                                        | 41 |

| Table 10. | Interrupt mapping                                                                           | 43 |

| Table 11. | Option byte                                                                                 |    |

| Table 12. | Option byte description                                                                     | 46 |

| Table 13. | STM8S103K3 alternate function remapping bits for 32-pin devices                             | 47 |

| Table 14. | STM8S103Fx alternate function remapping bits for 20-pin devices                             | 48 |

| Table 15. | Unique ID registers (96 bits)                                                               | 49 |

| Table 16. | Voltage characteristics                                                                     | 51 |

| Table 17. | Current characteristics                                                                     | 51 |

| Table 18. | Thermal characteristics                                                                     | 52 |

| Table 19. | General operating conditions                                                                | 52 |

| Table 20. | Operating conditions at power-up/power-down                                                 | 53 |

| Table 21. | Total current consumption with code execution in run mode at $V_{DD} = 5 \text{ V}$         | 55 |

| Table 22. | Total current consumption with code execution in run mode at $V_{DD} = 3.3 \text{ V} \dots$ | 56 |

| Table 23. | Total current consumption in wait mode at V <sub>DD</sub> = 5 V                             | 57 |

| Table 24. | Total current consumption in wait mode at V <sub>DD</sub> = 3.3 V                           | 57 |

| Table 25. | Total current consumption in active halt mode at V <sub>DD</sub> = 5 V                      | 58 |

| Table 26. | Total current consumption in active halt mode at V <sub>DD</sub> = 3.3 V                    | 58 |

| Table 27. | Total current consumption in halt mode at V <sub>DD</sub> = 5 V                             | 59 |

| Table 28. | Total current consumption in halt mode at V <sub>DD</sub> = 3.3 V                           | 59 |

| Table 29. | Wakeup times                                                                                |    |

| Table 30. | Total current consumption and timing in forced reset state                                  | 60 |

| Table 31. | Peripheral current consumption                                                              |    |

| Table 32. | HSE user external clock characteristics                                                     | 64 |

| Table 33. | HSE oscillator characteristics                                                              | 65 |

| Table 34. | HSI oscillator characteristics                                                              | 67 |

| Table 35. | LSI oscillator characteristics                                                              | 68 |

| Table 36. | RAM and hardware registers                                                                  | 69 |

| Table 37. | Flash program memory/data EEPROM memory                                                     |    |

| Table 38. | I/O static characteristics                                                                  |    |

| Table 39. | Output driving current (standard ports)                                                     | 71 |

| Table 40. | Output driving current (true open drain ports)                                              | 72 |

| Table 41. | Output driving current (high sink ports)                                                    | 72 |

| Table 42. | NRST pin characteristics                                                                    | 75 |

| Table 43. | SPI characteristics                                                                         |    |

| Table 44. | I <sup>2</sup> C characteristics                                                            | 81 |

| Table 45. | ADC characteristics                                                                         |    |

| Table 46. | ADC accuracy with R <sub>AIN</sub> < 10 kΩ, V <sub>DD</sub> = 5 V                           | 83 |

| Table 47. | ADC accuracy with $R_{AIN}$ < 10 k $\Omega$ , $V_{DD}$ = 3.3 V                              | 84 |

| Table 48. | EMS data                                                                                    |    |

#### 4.6 Power management

For efficient power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- Wait mode: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- Halt mode: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

#### 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- Timeout: At 16 MHz CPU clock the time-out period can be adjusted between 75 µs up

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

[TIM2\_CH2] ADC\_ETR/(HS) PD3 1 32 PD2 (HS) [TIM2\_CH3] 31 | PD1 (HS)/SWIM BEEP/TIM2\_CH1/(HS) PD4 2 UART1\_TX(/HS) PD5 3 30 PD0 (HS)/TIM1\_BKIN [CLK\_CCO] 29 PC7 (HS)/SPI\_MISO UART1\_RX/(HS) PD6 28 PC6 (HS)/SPI\_MOSI [TIM1\_CH4] TLI/(HS) PD7 [] 5 27 | PC5 (HS)/SPI\_SCK NRST [ OSCIN/PA1 26 PC4( HS)/TIM1\_CH4/CLK\_CCO 25 PC3 (HS)/TIM1\_CH3 OSCOUT/PA2 38 24 PC2( HS)/TIM1\_CH2 vss **∏** 9 23 Pc1 (HS)/TIM1\_CH1/UART1\_CK VCAP 22 PE5/SPI\_NSS VDD 11 [SPI\_NSS] TIM2\_CH3/(HS) PA3 12 21 PB0 (HS)/TIM1\_CH1N/AIN0 20 PB1 (HS)/TIM1\_CH2N/AIN1 PF4 [] 13 PB7 14 19 PB2 (HS)/TIM1\_CH3N/AIN2 15 18 PB3 (HS)/TIM1\_ETR/AIN3 PB6 12C\_SDA/(T) PB5 [ 16 17 PB4 (T)/I2C\_SCL MSv36416V1

Figure 4. STM8S103K3 SDIP32 pinout

- 1. (HS) high sink capability.

- 2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

- 3. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

Table 5. STM8S103K3 pin descriptions

|        | 32            |                               |      |          | Input |                |                          | Out   | put |    | _                              | Ite                           | ioi                                               |

|--------|---------------|-------------------------------|------|----------|-------|----------------|--------------------------|-------|-----|----|--------------------------------|-------------------------------|---------------------------------------------------|

| SDIP32 | LQFP/ UFQFP32 | Pin name                      | Туре | floating | ndw   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | Ф   | ЬР | Main function<br>(after reset) | Default alternate<br>function | Alternate function<br>after remap<br>[option bit] |

| 6      | 1             | NRST                          | I/O  | -        | X     | -              | -                        | -     | -   | -  | Re                             | eset                          | -                                                 |

| 7      | 2             | PA1/<br>OSCIN <sup>(2)</sup>  | I/O  | X        | Х     | Х              | -                        | 01    | Х   | Х  | Port A1                        | Resonator/<br>crystal in      | -                                                 |

| 8      | 3             | PA2/<br>OSCOUT                | I/O  | X        | Х     | Х              | -                        | 01    | Х   | Х  | Port A2                        | Resonator/<br>crystal out     | -                                                 |

| 9      | 4             | VSS                           | S    | -        | -     | -              | -                        | -     | -   | -  | Digita                         | l ground                      | -                                                 |

| 10     | 5             | VCAP                          | S    | -        | -     | -              | -                        | -     | -   |    | 1.8 V regula                   | ator capacitor                | -                                                 |

| 11     | 6             | VDD                           | S    | -        | -     | -              | -                        | -     | -   | -  | Digital po                     | wer supply                    | -                                                 |

| 12     | 7             | PA3/<br>TIM2_CH3<br>[SPI_NSS] | I/O  | х        | Х     | х              | HS                       | О3    | Х   | х  | Port A3                        | Timer 2<br>channel 3          | SPI master/<br>slave select<br>[AFR1]             |

| 13     | 8             | PF4                           | I/O  | X        | Χ     | -              | -                        | 01    | Χ   | Х  | Port F4                        | -                             |                                                   |

| 14     | 9             | PB7                           | I/O  | X        | Χ     | Χ              | -                        | 01    | Χ   | Х  | Port B7                        | -                             | -                                                 |

Table 6. STM8S103F2 and STM8S103F3 pin descriptions (continued)

|            |          |                                                           |      |          | Input |                |                          | Out   | put |   | _                              | ıte                                                                         | ion                                               |

|------------|----------|-----------------------------------------------------------|------|----------|-------|----------------|--------------------------|-------|-----|---|--------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

| TSSOP/SO20 | UFQFPN20 | Pin name                                                  | Туре | floating |       | Ext. interrupt | High sink <sup>(1)</sup> | Speed | ОО  | М | Main function<br>(after reset) | Default alternate<br>function                                               | Alternate function<br>after remap<br>[option bit] |

| 14         | 11       | PC4/<br>CLK_CCO/<br>TIM1_<br>CH4/AIN2/[<br>TIM1_<br>CH2N] | I/O  | x        | X     | x              | HS                       | О3    | X   | x | Port C4                        | Configurable<br>clock<br>output/Timer 1<br>- channel<br>4/Analog input<br>2 | Timer 1 -<br>inverted<br>channel 2<br>[AFR7]      |

| 15         | 12       | PC5/<br>SPI_SCK<br>[TIM2_ CH1]                            | I/O  | x        | x     | X              | HS                       | О3    | Х   | х | Port C5                        | SPI clock                                                                   | Timer 2 -<br>channel 1<br>[AFR0]                  |

| 16         | 13       | PC6/<br>SPI_MOSI<br>[TIM1_ CH1]                           | I/O  | x        | Х     | Х              | HS                       | О3    | Х   | Х | Port C6                        | SPI master out/slave in                                                     | Timer 1 -<br>channel 1<br>[AFR0]                  |

| 17         | 14       | PC7/<br>SPI_MISO<br>[TIM1_ CH2]                           | I/O  | X        | X     | X              | HS                       | О3    | X   | Х | Port C7                        | SPI master in/<br>slave out                                                 | Timer 1 -<br>channel 2<br>[AFR0]                  |

| 18         | 15       | PD1/ SWIM                                                 | I/O  | X        | Х     | Х              | HS                       | 04    | X   | Х | Port D1                        | SWIM data interface                                                         | -                                                 |

| 19         | 16       | PD2/AIN3/[T<br>IM2_ CH3]                                  | I/O  | X        | X     | Х              | HS                       | О3    | X   | Х | Port D2                        | Analog input 3                                                              | Timer 2 -<br>channel 3<br>[AFR1]                  |

| 20         | 17       | PD3/ AIN4/<br>TIM2_CH2/<br>ADC_ETR                        | I/O  | X        | Х     | Х              | HS                       | O3    | Х   | Х | Port D3                        | Analog input 4/<br>Timer 2 -<br>channel 2/ADC<br>external trigger           | -                                                 |

I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package. In addition, the total driven current must respect the absolute maximum ratings.

<sup>2.</sup> When the MCU is in halt/active-halt mode, PA1 is automatically configured in input weak pull-up and cannot be used for waking up the device. In this mode, the output state of PA1 is not driven. It is recommended to use PA1 only in input mode if halt/active-halt is used in the application.

<sup>3.</sup> In the open-drain output column, "T" defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to VDD are not implemented).1

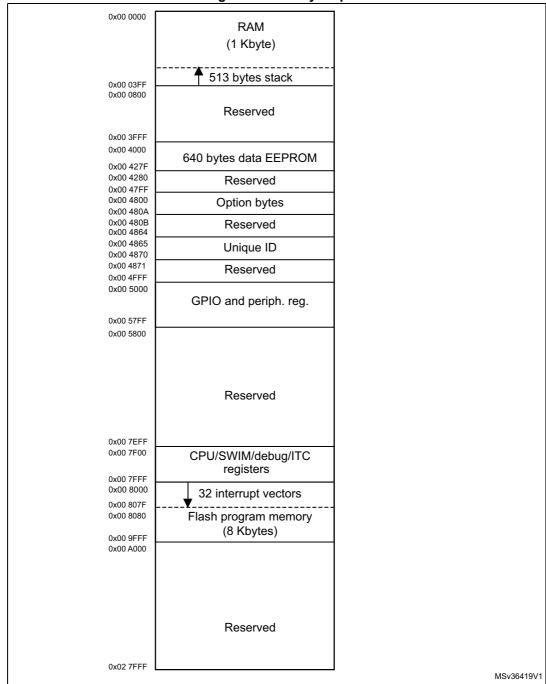

# 6 Memory and register map

### 6.1 Memory map

Figure 7. Memory map

## 6.2.2 General hardware register map

Table 8. General hardware register map

| Address                | Block Register label |             | Register name                                    | Reset status        |

|------------------------|----------------------|-------------|--------------------------------------------------|---------------------|

| 0x00 501E to 0x00 5059 |                      | Reser       | ved area (60 byte)                               |                     |

| 0x00 505A              |                      | FLASH_CR1   | Flash control register 1                         | 0x00                |

| 0x00 505B              |                      | FLASH_CR2   | Flash control register 2                         | 0x00                |

| 0x00 505C              |                      | FLASH_NCR2  | Flash complementary control register 2           | 0xFF                |

| 0x00 505D              | Flash                | FLASH_FPR   | Flash protection register                        | 0x00                |

| 0x00 505E              |                      | FLASH_NFPR  | Flash complementary protection register          | 0xFF                |

| 0x00 505F              |                      | FLASH_IAPSR | Flash in-application programming status register | 0x00                |

| 0x00 5060 to 0x00 5061 |                      | Rese        | rved area (2 byte)                               |                     |

| 0x00 5062              | Flash                | FLASH_PUKR  | Flash program memory unprotection register       | 0x00                |

| 0x00 5063              |                      | Rese        | rved area (1 byte)                               |                     |

| 0x00 5064              | Flash                | FLASH_DUKR  | Data EEPROM unprotection register                | 0x00                |

| 0x00 5065 to 0x00 509F |                      | Reser       | ved area (59 byte)                               |                     |

| 0x00 50A0              | ITC                  | EXTI_CR1    | External interrupt control register 1            | 0x00                |

| 0x00 50A1              | IIC                  | EXTI_CR2    | External interrupt control register 2            | 0x00                |

| 0x00 50A2 to 0x00 50B2 |                      | Reser       | ved area (17 byte)                               |                     |

| 0x00 50B3              | RST                  | RST_SR      | Reset status register                            | 0xXX <sup>(1)</sup> |

| 0x00 50B4 to 0x00 50BF |                      | Reser       | ved area (12 byte)                               |                     |

| 0x00 50C0              | CLK                  | CLK_ICKR    | Internal clock control register                  | 0x01                |

| 0x00 50C1              | CLK                  | CLK_ECKR    | External clock control register                  | 0x00                |

| 0x00 50C2              |                      | Rese        | rved area (1 byte)                               |                     |

## 8 Option byte

Option byte contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Except for the ROP (read-out protection) byte, each option byte has to be stored twice, in a regular form (OPTx) and a complemented one (NOPTx) for redundancy.

Option byte can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in the table below.

Option byte can also be modified 'on the fly' by the application in IAP mode, except the ROP option that can only be modified in ICP mode (via SWIM).

Refer to the STM8S Flash programming manual (PM0051) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

Table 11. Option byte

|         | Option                          | Option |             |              |       | Ор           | tion bits   |               |              |               | Factory |                    |

|---------|---------------------------------|--------|-------------|--------------|-------|--------------|-------------|---------------|--------------|---------------|---------|--------------------|

| Addr.   | name                            | name   | byte<br>no. | 7            | 6     | 5            | 4           | 3             | 2            | 1             | 0       | default<br>setting |

| 0x4800  | Read-out<br>protection<br>(ROP) | OPT0   |             | ROP [7:0]    |       |              |             |               |              |               | 0x00    |                    |

| 0x4801  | User boot                       | OPT1   |             | UBC [7:0]    |       |              |             |               |              |               | 0x00    |                    |

| 0x4802  | code (UBC)                      | NOPT1  |             |              |       | N            | UBC [7:0]   |               |              |               | 0xFF    |                    |

| 0x4803  | Alternate                       | OPT2   | AFR7        | AFR6         | AFR5  | AFR4         | AFR3        | AFR2          | AFR1         | AFR0          | 0x00    |                    |

| 0x4804  | function<br>remapping<br>(AFR)  | NOPT2  | NAFR7       | NAFR6        | NAFR5 | NAFR4        | NAFR3       | NAFR2         | NAFR1        | NAFR0         | 0xFF    |                    |

| 0x4805h | Mina                            | OPT3   |             | Reserved     |       | HSI<br>TRIM  | LSI_EN      | IWDG<br>_HW   | WWDG<br>_HW  | WWDG<br>_HALT | 0x00    |                    |

| 0x4806  | Misc. option                    | NOPT3  |             | Reserved     |       | NHSI<br>TRIM | NLSI<br>_EN | NIWDG<br>_HW  | NWWDG<br>_HW | NWWG<br>_HALT | 0xFF    |                    |

| 0x4807  | Clask antion                    | OPT4   |             | Res          | erved |              | EXT CLK     | CKAWU<br>SEL  | PRS C1       | PRS C0        | 0x00    |                    |

| 0x4808  | Clock option NOPT4              |        | Reserved    |              |       |              | NEXT<br>CLK | NCKA<br>WUSEL | NPRSC1       | NPR SC0       | 0xFF    |                    |

| 0x4809  | HSE clock                       | OPT5   |             | HSECNT [7:0] |       |              |             |               |              | 0x00          |         |                    |

| 0x480A  | startup                         | NOPT5  |             |              |       | NHS          | SECNT [7:0] | 0xFF          |              |               |         |                    |

Table 12. Option byte description

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ОРТ0            | ROP[7:0] Memory readout protection (ROP)  0xAA: Enable readout protection (write access via SWIM protocol)  Note: Refer to the family reference manual (RM0016) section on Flash/EEPROM memory readout protection for details.                                                                                                                                                                        |

| OPT1            | UBC[7:0] User boot code area 0x00: no UBC, no write-protection 0x01: Page 0 defined as UBC, memory write-protected Page 0 and 1 contain the interrupt vectors 0x7F: Pages 0 to 126 defined as UBC, memory write-protected Other values: Pages 0 to 127 defined as UBC, memory write-protected Note: Refer to the family reference manual (RM0016) section on Flash write protection for more details. |

| OPT2            | AFR[7:0] Refer to the following section for alternate function remapping descriptions of bits [7:2] and [1:0] respectively.                                                                                                                                                                                                                                                                           |

|                 | HSITRIM: High speed internal clock trimming register size 0: 3-bit trimming supported in CLK_HSITRIMR register 1: 4-bit trimming supported in CLK_HSITRIMR register                                                                                                                                                                                                                                   |

|                 | LSI_EN: Low speed internal clock enable 0: LSI clock is not available as CPU clock source 1: LSI clock is available as CPU clock source                                                                                                                                                                                                                                                               |

| OPT3            | IWDG_HW: Independent watchdog  0: IWDG Independent watchdog activated by software  1: IWDG Independent watchdog activated by hardware                                                                                                                                                                                                                                                                 |

|                 | WWDG_HW: Window watchdog activation 0: WWDG window watchdog activated by software 1: WWDG window watchdog activated by hardware                                                                                                                                                                                                                                                                       |

|                 | WWDG_HALT: Window watchdog reset on halt  0: No reset generated on halt if WWDG active  1: Reset generated on halt if WWDG active                                                                                                                                                                                                                                                                     |

- 2. Measured from interrupt event to interrupt vector fetch

- 3.  $t_{WU(WFI)} = 2 \times 1/f_{master} + 67 \times 1/f_{CPU}$

- 4. Configured by the REGAH bit in the CLK\_ICKR register.

- 5. Configured by the AHALT bit in the FLASH\_CR1 register.

- 6. Plus 1 LSI clock depending on synchronization.

#### Total current consumption and timing in forced reset state

Table 30. Total current consumption and timing in forced reset state

| Symbol               | Parameter                         | Conditions              | Тур | Max <sup>(1)</sup> | Unit |  |  |

|----------------------|-----------------------------------|-------------------------|-----|--------------------|------|--|--|

|                      | Supply current in reset           | V <sub>DD</sub> = 5 V   | 400 | -                  | μA   |  |  |

| I <sub>DD(R)</sub>   | state <sup>(2)</sup>              | V <sub>DD</sub> = 3.3 V | 300 | -                  | μΛ   |  |  |

| t <sub>RESETBL</sub> | Reset pin release to vector fetch | -                       | -   | 150                | μs   |  |  |

- 1. Guaranteed by design.

- 2. Characterized with all I/Os tied to VSS:

#### **Current consumption of on-chip peripherals**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

HSI internal RC/f<sub>CPU</sub>=  $f_{MASTER}$  = 16 MHz,  $V_{DD}$  = 5 V

Table 31. Peripheral current consumption

| Symbol                 | Parameter                                          | Тур  | Unit |

|------------------------|----------------------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>  | TIM1 supply current <sup>(1)</sup>                 | 210  |      |

| I <sub>DD(TIM2)</sub>  | TIM2 supply current <sup>(1)</sup>                 | 130  |      |

| I <sub>DD(TIM4)</sub>  | TIM4 supply current <sup>(1)</sup>                 | 50   |      |

| I <sub>DD(UART1)</sub> | UART1 supply current (2)                           | 120  | ۸    |

| I <sub>DD(SPI)</sub>   | SPI supply current (2)                             | 45   | μΑ   |

| I <sub>DD(I2C)</sub>   | I2C supply current <sup>(2)</sup>                  | 65   |      |

| I <sub>DD(ADC1)</sub>  | ADC1 supply current when converting <sup>(3)</sup> | 1000 |      |

<sup>1.</sup> Data based on a differential  $I_{DD}$  measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

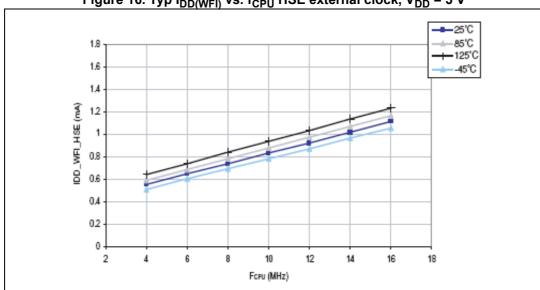

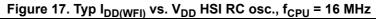

#### **Current consumption curves**

The following figures show typical current consumption measured with code executing in RAM.

<sup>2.</sup> Data based on a differential IDD measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

Data based on a differential IDD measurement between reset configuration and continuous A/D conversions. Not tested in production.

Figure 16. Typ  $I_{DD(WFI)}$  vs.  $f_{CPU}$  HSE external clock,  $V_{DD}$  = 5 V

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

Table 33. HSE oscillator characteristics

| Symbol                              | Parameter                                   | Conditions                             | Min | Тур | Max                                             | Unit |  |

|-------------------------------------|---------------------------------------------|----------------------------------------|-----|-----|-------------------------------------------------|------|--|

| f <sub>HSE</sub>                    | External high speed oscillator frequency    | -                                      | 1   | -   | 16                                              | MHz  |  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                      | -   | 220 | -                                               | kΩ   |  |

| C <sup>(1)</sup>                    | Recommended load capacitance <sup>(2)</sup> | -                                      | -   | -   | 20                                              | pF   |  |

| 1                                   | HSE oscillator power                        | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up)<br>1.6 (stabilized) <sup>(3)</sup> | mΛ   |  |

| IDD(HSE)                            | consumption                                 | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up) 1.2 (stabilized) <sup>(3)</sup>    | mA   |  |

| g <sub>m</sub>                      | Oscillator transconductance                 | -                                      | 5   | -   | -                                               | mA/V |  |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | V <sub>DD</sub> is stabilized          | -   | 1   | -                                               | ms   |  |

<sup>1.</sup> C is approximately equivalent to 2 x crystal Cload.

<sup>2.</sup> The oscillator selection can be optimized in terms of supply current using a high quality resonator with small Rm value. Refer to crystal manufacturer for more details

<sup>3.</sup> Guaranteed by characterization results.

<sup>4.</sup> t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

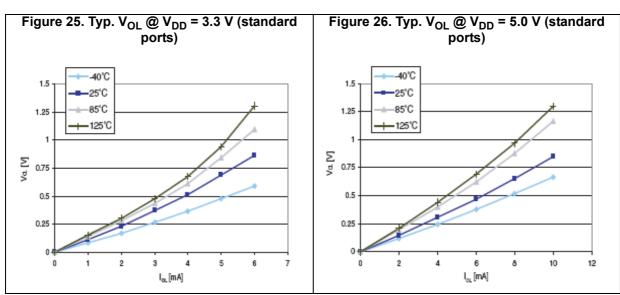

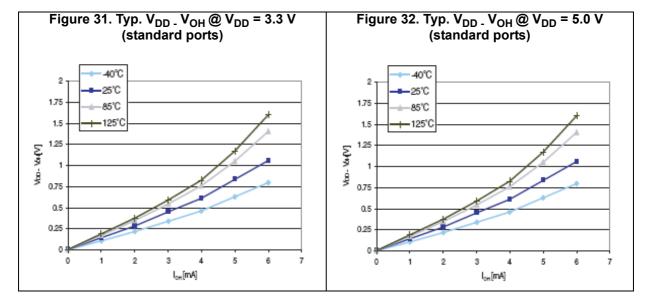

### 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage, using the output mode of the I/O for example or an external pull-up or pull-down resistor.

Table 38. I/O static characteristics

| Symbol                          | Parameter                       | Conditions                                  | Min                   | Тур | Max                     | Unit |  |

|---------------------------------|---------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|--|

| V <sub>IL</sub>                 | Input low level voltage         |                                             | -0.3 V                | -   | 0.3 x V <sub>DD</sub>   | V    |  |

| V <sub>IH</sub>                 | Input high level voltage        | V <sub>DD</sub> = 5 V                       | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3 V | V    |  |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>       |                                             | =                     | 700 | -                       | mV   |  |

| R <sub>pu</sub>                 | Pull-up resistor                | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |  |

| t <sub>R</sub> , t <sub>F</sub> | Rise and fall time              | Fast I/Os<br>Load = 50 pF                   | -                     | -   | 35 <sup>(2)</sup>       | 20   |  |

|                                 | (10% - 90%)                     | Standard and high sink I/Os<br>Load = 50 pF | -                     | -   | 125 <sup>(2)</sup>      | ns   |  |

|                                 | Rise and fall time              | Fast I/Os<br>Load = 20 pF                   | -                     | -   | 20 <sup>(2)</sup>       | 20   |  |

| t <sub>R</sub> , t <sub>F</sub> | (10% - 90%)                     | Standard and high sink I/Os<br>Load = 20 pF | -                     | -   | 50 <sup>(2)</sup>       | ns   |  |

| I <sub>lkg</sub>                | Digital input leakage current   | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±1 <sup>(3)</sup>       | μΑ   |  |

| I <sub>lkg ana</sub>            | Analog input leakage current    | $V_{SS} \le V_{IN} \le V_{DD}$              | -                     | -   | ±250 <sup>(3)</sup>     | nA   |  |

| I <sub>lkg(inj)</sub>           | Leakage current in adjacent I/O | Injection current ±4 mA                     | -                     | -   | ±1 <sup>(3)</sup>       | μΑ   |  |

<sup>1.</sup> Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

<sup>2.</sup> Data guaranteed by design.

<sup>3.</sup> Guaranteed by characterization results

Table 40. Output driving current (true open drain ports)

| Symbol          | Parameter                             | Conditions                                          | Min | Max                | Unit |

|-----------------|---------------------------------------|-----------------------------------------------------|-----|--------------------|------|

| V.              | Output low level with 2 pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V   | -   | 1.0                |      |

| V <sub>OL</sub> | Output low level with 2 pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 3.3 V | -   | 1.5 <sup>(1)</sup> | V    |

| V <sub>OH</sub> | Output high level with 2 pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V   | -   | 2.0 <sup>(1)</sup> |      |

<sup>1.</sup> Guaranteed by characterization results

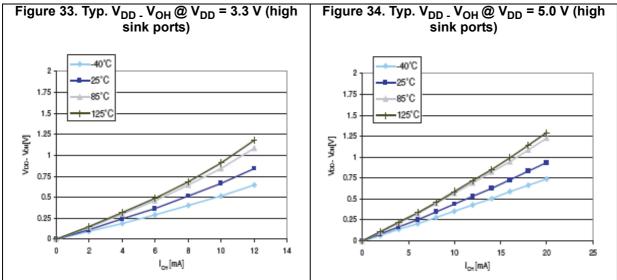

Table 41. Output driving current (high sink ports)

| Symbol          | Parameter                             | Conditions                                          | Min                                               | Max                | Unit |  |

|-----------------|---------------------------------------|-----------------------------------------------------|---------------------------------------------------|--------------------|------|--|

| V <sub>OL</sub> | Output low level with 8 pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V   | -                                                 | 0.8                |      |  |

|                 | Output low level with 4               | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 3.3 V | -                                                 | 1.0 <sup>(1)</sup> |      |  |

|                 | pins sunk                             | I <sub>IO</sub> = 20 mA,<br>V <sub>DD</sub> = 5 V   | -                                                 | 1.5 <sup>(1)</sup> | V    |  |

|                 | Output high level with 8 pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V   | 4.0                                               | -                  | V    |  |

|                 | Output high level with 4              | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 3.3 V | 2.1 <sup>(1)</sup>                                | -                  |      |  |

|                 |                                       | pins sourced                                        | I <sub>IO</sub> = 20 mA,<br>V <sub>DD</sub> = 5 V | 3.3 <sup>(1)</sup> | -    |  |

1. Guaranteed by characterization results.

Table 46. ADC accuracy with R<sub>AIN</sub>< 10 k $\Omega$ , V<sub>DD</sub>= 5 V

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.6 | 3.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.4 | 4.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.1 | 2.5                |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz | 1.5 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 1.8 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 1.5 | 3                  |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 4 MHz | 2.1 | 3                  | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 2.2 | 4                  |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.7 | 1.5                |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     | f <sub>ADC</sub> = 2 MHz | 0.6 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 4 MHz | 0.8 | 2                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz | 0.8 | 2                  |      |

<sup>1.</sup> Guaranteed by characterization results.

<sup>2.</sup> ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

Table 51. Electrical sensitivities

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | T <sub>A</sub> = 25 °C  |                      |

| LU     | Static latch-up class | T <sub>A</sub> = 85 °C  | Α                    |

|        |                       | T <sub>A</sub> = 125 °C |                      |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

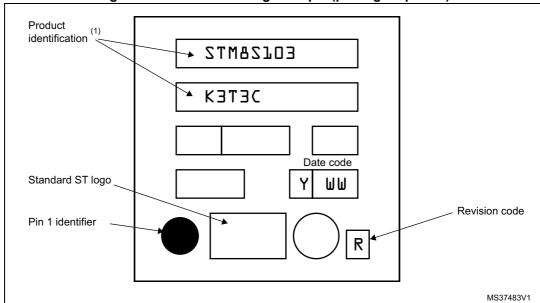

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 47. LQFP32 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 13 Ordering information

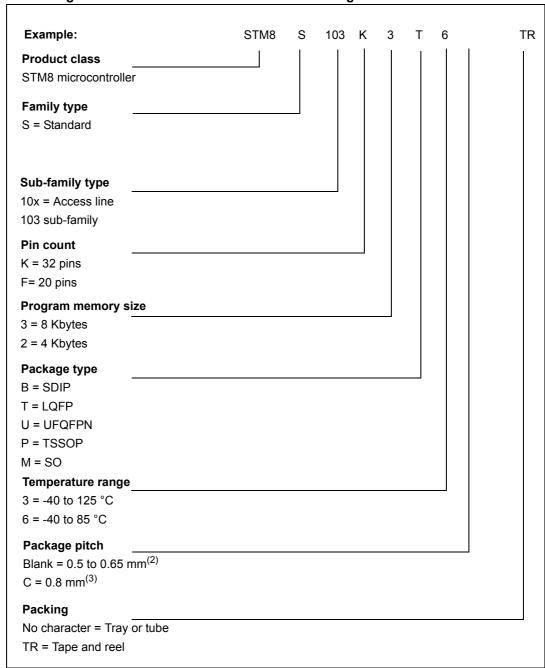

Figure 63. STM8S103F2/x3 access line ordering information scheme<sup>(1)</sup>

- A dedicated ordering information scheme will be released if, in the future, memory programming service (FastROM) is required The letter "P" will be added after STM8S. Three unique letters identifying the customer application code will also be visible in the codification. Example: STM8SP103K3MACTR.

- 2. UFQFPN, TSSOP, and SO packages.

- 3. LQFP package.

For a list of available options (for example memory size, package) and orderable part numbers or for further information on any aspect of this device, please go to <a href="https://www.st.com">www.st.com</a> or contact the ST Sales Office nearest to you.

### 13.1 STM8S103 FASTROM microcontroller option list

| (last update: April 2010)             |  |

|---------------------------------------|--|

| Customer                              |  |

| Address                               |  |

| Contact                               |  |

| Phone number                          |  |

| FASTROM code reference <sup>(1)</sup> |  |

The preferable format for programing code is .hex (.s19 is accepted)

If data EEPROM programing is required, a separate file must be sent with the requested data.

Note:

See the option byte section in the datasheet for authorized option byte combinations and a detailed explanation. Do not use more than one remapping option in the same port. It is forbidden to enable both AFR1 and AFR0.

### Device type/memory size/package (check only one option)

| FASTROM device | 4 Kbyte      | 8 Kbyte       |

|----------------|--------------|---------------|

| LQFP32         | -            | []STM8S103K3  |

| UFQFPN20       | []STM8S103F2 | []STM8S103F3  |

| UFQFPN32       | -            | [] STM8S103K3 |

| TSSOP20        | []STM8S103F2 | [] STM8S103F3 |

| SO20W          | []STM8S103F2 | [] STM8S103F3 |

#### Conditioning (check only one option)

|  | [ ] | Tape | and | reel | or | Π | Tra | ۷ | , |

|--|-----|------|-----|------|----|---|-----|---|---|

|--|-----|------|-----|------|----|---|-----|---|---|

#### Special marking (check only one option)

|  | No | [] | Υ | es |

|--|----|----|---|----|

|--|----|----|---|----|

Authorized characters are letters, digits, '.', '-', '/' and spaces only. Maximum character counts are:

UFQFPN20: 1 line of 4 characters max: "\_\_\_\_"

UFQFPN32: 1 line of 7 characters max: "\_\_\_\_\_"

LQFP32: 2 lines of 7 characters max: "\_\_\_\_\_" and "\_\_\_\_"

TSSOP20/SO20: 1 line of 10 characters max: "\_\_\_\_\_"

Three characters are reserved for code identification.

<sup>1.</sup> The FASTROM code name is assigned by STMicroelectronics.