# \_\_\_\_\_STMicroelectronics - <u>STM8S103F3M6TR Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 640 × 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s103f3m6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49.<br>Table 50. | EMI data 87   ESD absolute maximum ratings 87                             |   |

|------------------------|---------------------------------------------------------------------------|---|

| Table 51.              | Electrical sensitivities                                                  | 8 |

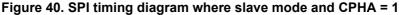

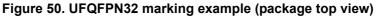

| Table 52.              | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data   | 0 |

| Table 53.              | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat   |   |

|                        | package mechanical data                                                   | 3 |

| Table 54.              | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |   |

|                        | package mechanical data                                                   | 5 |

| Table 55.              | SDIP32 package mechanical data                                            | 8 |

| Table 56.              | TSSOP20 package mechanical data 100                                       | 0 |

| Table 57.              | SO20 mechanical data                                                      | 3 |

| Table 58.              | Thermal characteristics                                                   | 6 |

| Table 59.              | Document revision history                                                 | 6 |

## 4.14.1 UART1

#### Main features

- 1 Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (fCPU/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (fCPU/16)

#### LIN master mode

- Emission: Generates 13-bit synch. break frame

- Reception: Detects 11-bit break frame

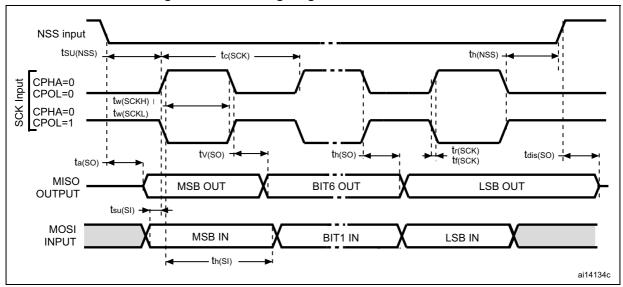

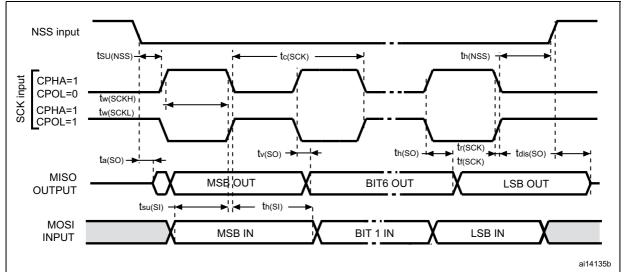

## 4.14.2 SPI

- Maximum speed: 8 Mbit/s (fMASTER/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

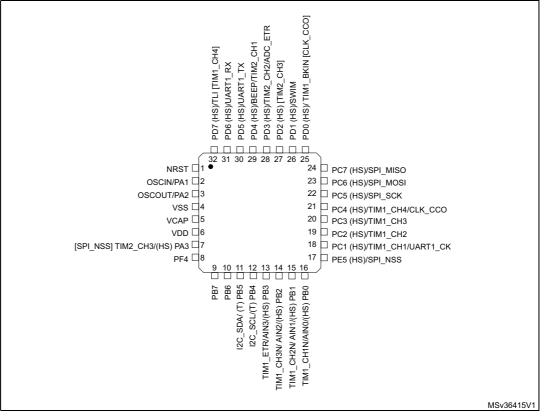

# 5.1 STM8S103K3 UFQFPN32/LQFP32/SDIP32 pinout and pin description

Figure 3. STM8S103K3 UFQFPN32/LQFP32 pinout

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

3. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

## STM8S103F2 STM8S103F3 STM8S103K3

| [TIM2_CH2] ADC_ETR/(HS) PD3 | 1  | 32 PD2 (HS) [TIM2_CH3]          |

|-----------------------------|----|---------------------------------|

| BEEP/TIM2_CH1/(HS) PD4      | 2  | 31 ] PD1 (HS)/SWIM              |

| UART1_TX(/HS) PD5           | 3  |                                 |

| UART1_RX/(HS) PD6           | 4  | 29 D PC7 (HS)/SPI_MISO          |

| [TIM1_CH4] TLI/(HS) PD7     | 5  | 28 PC6 (HS)/SPI_MOSI            |

| NRST                        | 6  | 27 D PC5 (HS)/SPI_SCK           |

| OSCIN/PA1                   | 7  | 26 PC4( HS)/TIM1_CH4/CLK_CCO    |

| OSCOUT/PA2                  | 8  | 25 рсз (нѕ)/тім1_снз            |

| VSS                         | 9  | 24 PC2( HS)/TIM1_CH2            |

| VCAP                        | 10 | 23 D PC1 (HS)/TIM1_CH1/UART1_CK |

| VDD                         | 11 | 22 PE5/SPI_NSS                  |

| [SPI_NSS] TIM2_CH3/(HS) PA3 | 12 | 21 ] рво (нs)/тім1_сн1N/АІN0    |

| PF4                         | 13 | 20 ] рв1 (нs)/тім1_сн2N/АіN1    |

| PB7                         | 14 | 19 ] рв2 (нѕ)/тім1_снзм/аім2    |

| PB6                         | 15 | 18 🗍 РВЗ (HS)/ТІМ1_ЕТК/АІNЗ     |

| I2C_SDA/(T) PB5             | 16 | 17 ] PB4 (T)/I2C_SCL            |

|                             |    | MSv36416V1                      |

Figure 4. STM8S103K3 SDIP32 pinout

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{\text{DD}}$  not implemented).

3. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

|        |               |                               |      |          | Input |                |                          | Out   | put  |    | _                              |                               | <u>_</u>                                          |

|--------|---------------|-------------------------------|------|----------|-------|----------------|--------------------------|-------|------|----|--------------------------------|-------------------------------|---------------------------------------------------|

|        | °32           |                               |      |          | mput  |                |                          | Out   | ւթու |    | 50                             | ate                           |                                                   |

| SDIP32 | LQFP/ UFQFP32 | Pin name                      | Type | floating | ndm   | Ext. interrupt | High sink <sup>(1)</sup> | Speed | ao   | dd | Main function<br>(after reset) | Default alternate<br>function | Alternate function<br>after remap<br>[option bit] |

| 6      | 1             | NRST                          | I/O  | -        | Х     | -              | -                        | -     | -    | -  | Re                             | eset                          | -                                                 |

| 7      | 2             | PA1/<br>OSCIN <sup>(2)</sup>  | I/O  | x        | х     | х              | -                        | 01    | х    | х  | Port A1                        | Resonator/<br>crystal in      | -                                                 |

| 8      | 3             | PA2/<br>OSCOUT                | I/O  | x        | х     | х              | -                        | 01    | х    | х  | Port A2                        | Resonator/<br>crystal out     | -                                                 |

| 9      | 4             | VSS                           | S    | -        | -     | -              | -                        | -     | -    | -  | Digita                         | l ground                      | -                                                 |

| 10     | 5             | VCAP                          | S    | -        | -     | -              | -                        | -     | -    |    | 1.8 V regula                   | ator capacitor                | -                                                 |

| 11     | 6             | VDD                           | S    | -        | -     | -              | -                        | -     | -    | -  | Digital po                     | ower supply                   | -                                                 |

| 12     | 7             | PA3/<br>TIM2_CH3<br>[SPI_NSS] | I/O  | x        | х     | x              | HS                       | O3    | х    | x  | Port A3                        | Timer 2<br>channel 3          | SPI master/<br>slave select<br>[AFR1]             |

| 13     | 8             | PF4                           | I/O  | X        | Х     | -              | -                        | 01    | Х    | Х  | Port F4                        | -                             | -                                                 |

| 14     | 9             | PB7                           | I/O  | X        | Х     | Х              | -                        | 01    | Х    | Х  | Port B7                        | -                             | -                                                 |

| Table 5. | STM8S103K3    | pin  | descriptions |

|----------|---------------|------|--------------|

|          | 0111100100100 | PIII | accomptions  |

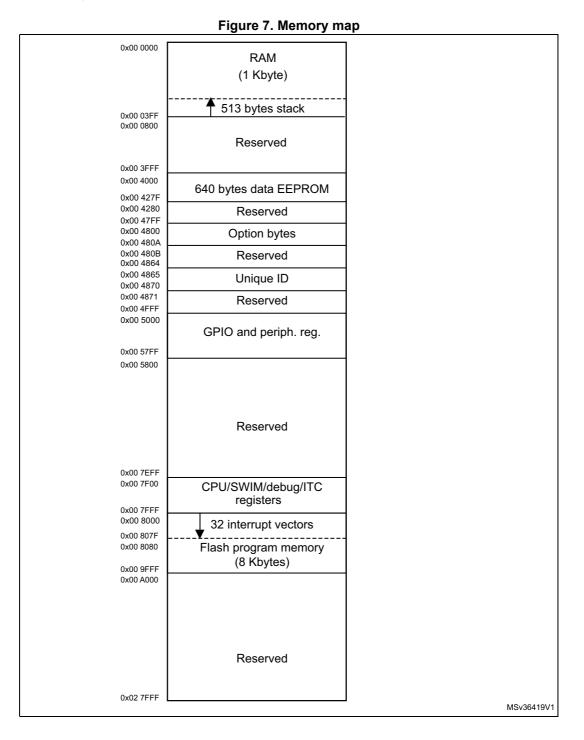

# 6 Memory and register map

## 6.1 Memory map

| AddressBlockRegister labelRegister nameRest status0x00 50C3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |                             | eral hardware regist    |                                |                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|-------------------------|--------------------------------|---------------------|

| 0x00 50C4CLK_SWRClock master switch register0xE10x00 50C5CLK_SWRClock switch control register0xXX0x00 50C6CLK_CKDIVRClock divider register0x180x00 50C7CLK_CCRPeripheral clock gating<br>register0x0FF0x00 50C8CLK_CCRClock security system register0x000x00 50C9CLK_CCCRConfigurable clock control<br>register0x000x00 50C4CLK_CCCRConfigurable clock control<br>register0x000x00 50C6CLK_PCKENR2Peripheral clock gating<br>register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0x000x00 50C1WWD6SWIM clock control register0x7F0x00 50D1WWD6WWD6_CRWWDG control register0x7F0x00 50D2WWD6WWD6_RWRWWDR window register0x7F0x00 50D3 to 00 50DFReserved area (13 byte)0x000x0X0x00 50E1IWD6IWD6_RRIWD6 key register0x2X <sup>(2)</sup> 0x00 50F1IWD6IWD6_RRIWD6 precaler register0x000x00 50F2AWU_CSR1AWU control/status register0x030x00 50F3BEEPAWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F4AWU_SPI_CR2SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50C4SPI_CR2SPI control register0x00 <th>Address</th> <th>Block</th> <th>Register label</th> <th>Register name</th> <th>Reset status</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Address                | Block                       | Register label          | Register name                  | Reset status        |

| 0x00 50C5CLK_SWCRClock switch control register0xXX0x00 50C6CLK_CKDIVRClock divider register0x180x00 50C7CLK_CCSRClock security system register0x000x00 50C8CLK_CSSRClock security system register0x000x00 50C9CLK_CCCRConfigurable clock control<br>register0x000x00 50CACLK_PCKENR2Peripheral clock gating<br>register0x0FF0x00 50CACLK_PCKENR2Peripheral clock gating<br>register0x0F0x00 50CDCLK_SWIMCCRSWIM clock control register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0x7F0x00 50C1WWDGWWDG_CRWWDG control register0x7F0x00 50D1WWDGWWDG_WRWWDG control register0x7F0x00 50E0WWDG_RIWDG prescaler register0x000x00 50E1IWDGIWDG_RRIWDG prescaler register0x000x00 50E1IWDGAWU_CSR1AWU control/status register0x070x00 50F1AWUAWU_APRAWU control/status register0x030x00 50F3BEEPBEEP_CSRBEEP control/status register0x060x00 50F4VAWUSPI_CR1SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x00 50C3              |                             | CLK_CMSR                | Clock master status register   | 0xE1                |

| 0x00 50C6CLK_CKDIVRClock divider register0x180x00 50C7CLK_PCKENR1Peripheral clock gating<br>register 10xFF0x00 50C8CLK_CSSRClock security system register0x000x00 50C9CLK_CCORConfigurable clock control<br>register0x000x00 50CACLK_PCKENR2Peripheral clock gating<br>register 20xFF0x00 50CCCLK_PCKENR2Peripheral clock gating<br>register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0x7F0x00 50C1WWDGWWDG_CRWWDG control register0x7F0x00 50D1WWDGWWDG_WRWWDR window register0x7F0x00 50D2WWDGReserved area (13 byte)0x000x00 50E1IWDGIWDG_RRIWDG register0x020x00 50E2IWDG_RRIWDG register0x000x00 50F1AWUAWU_CSR1AWU control/status register0x030x00 50F3BEEPBEEP_CSRBEEP control/status register0x010x00 50F4AWUSPI_CR1SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 502SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 50F4SPI_CR2SPI control register0x000x00 5204SPI_CR2SPI control register0x000x00 5204SPI_CR2SPI contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 50C4              |                             | CLK_SWR                 | Clock master switch register   | 0xE1                |

| 0x00 50C7CLKCLKCLKOx0x00 50C8CLK_PCKENR1Peripheral clock gating<br>register 10xFF0x00 50C9CLK_CCORConfigurable clock control<br>register0x000x00 50CACLK_PCKENR2Peripheral clock gating<br>register 20xFF0x00 50CACLK_PCKENR2Peripheral clock caling<br>register 10x000x00 50CCCLK_SWIMCCRSWIM clock control register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0x7F0x00 50D1WWDGWWDG_CRWWDG control register0x7F0x00 50D2WWDGWWDG_CRWWDG window register0x7F0x00 50D1WWDGIWDG_RRIWDG prescaler register0x000x00 50D2IWDGIWDG_PRIWDG prescaler register0x000x00 50E1WWDGIWDG_RRIWDG reload register0x000x00 50F1AWUAWU_CSR1AWU control/status register 10x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x3F0x00 50F4VO00 50F1SPI_CR1SPI control register 10x000x00 50F3BEEPSPI_CR1SPI control register0x000x00 50F4SPI_CR2SPI control register 10x000x00 5020SPI_CR2SPI control register0x000x00 5203SPI_CR2SPI control register 10x000x00 5204SPI_CR2SPI control register0x000x00 5205SPI_CR2SPI control register 10x00<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 50C5              |                             | CLK_SWCR                | Clock switch control register  | 0xXX                |

| 0x00 50C7CLK_PCRINTregister 10XPF0x00 50C8CLK_CSSRClock security system register0x000x00 50C9CLK_CCORConfigurable clock control<br>register0x000x00 50CACLK_PCKENR2Peripheral clock gating<br>register 20xFF0x00 50CCCLK_SWIMCCRSWIM clock calibration trimming<br>register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0xXXXXXX00x00 50D1WWDG<br>CUK_SWIMCRWWDG control register0x7F0x00 50D2WWDG<br>WWDG_CRWWDG control register0x7F0x00 50D3 to 00 50DFWWDG_CRWWDG window register0xXX <sup>(2)</sup> 0x00 50E1IWDG<br>IWDG<br>IWDG_RRIWDG key register0xXX <sup>(2)</sup> 0x00 50E1WWDGIWDG_PRIWDG prescaler register0x000x00 50E1WWDGReservet area (13 byte)0x000x00 50E1WWDGAWU_CSR1AWU control/status register 10x000x00 50F1AWUAWU_CSR1AWU asynchronous prescaler<br>buffer register0x3F0x00 50F2BEEPBEEP_CSRBEEP control/status register 10x000x00 50F4 to 0x00 50F5SPI_CR1SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5074SPI_CR1SPI control register0x000x00 5075SPI_CR2SPI control register0x000x00 5076SPI_CR2SPI control register0x000x00 5071SPI_CR2SPI control register0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 50C6              |                             | CLK_CKDIVR              | Clock divider register         | 0x18                |

| 0x00 50C9CLK_CCORConfigurable clock control<br>register0x000x00 50CACLK_PCKENR2Peripheral clock gating<br>register 20xFF0x00 50CCCLK_PCKENR2Peripheral clock gating<br>register 20x000x00 50CDCLK_HSITRIMRHSI clock calibration timming<br>register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0bXXXX XXX00x00 50D1WWDGWWDG_CRWWDG control register0x7F0x00 50D2WWDGWWDG_WRWWDR window register0x7F0x00 50D2WWDGWWDG_RRWWDR window register0xXX(2)0x00 50D1IWDGIWDG_RRIWDG prescaler register0xXX(2)0x00 50E1IWDGIWDG_RLRIWDG prescaler register0x000x00 50F1AWUAWU_CSR1AWU control/status register 10x000x00 50F2AWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F3BEEPBEEP_CSRBEEP control/status register0x000x00 50F3BEEPSPI_CR2SPI control register0x000x00 50C1SPI_CR2SPI control register0x000x000x00 50F3BEEPSPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5203SPI_CR2SPI control reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x00 50C7              |                             | CLK_PCKENR1             |                                | 0xFF                |

| DX00 50C9CLN_CCORregisterDX000x00 50CACLK_PCKENR2Peripheral clock gating<br>register 20xFF0x00 50CCCLK_HSITRIMRHSI clock calibration timming<br>register0x000x00 50CDCLK_SWIMCCRSWIM clock control register0bXXXXXXXX0x00 50CDWWDG_CRWWDG control register0x7F0x00 50D1WWDGWWDG_WRWWDG window register0x7F0x00 50D2WWDGWWDG_WRWWDG window register0x7F0x00 50D2WWDGIWDG_KRIWDG key register0xXX <sup>(2)</sup> 0x00 50E1IWDGIWDG_RRIWDG prescaler register0x000x00 50E2IWDG_RLRIWDG prescaler register0x000x00 50F1AWUAWU_CSR1AWU control/status register 10x000x00 50F2AWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F3BEEPBEEP_CSRBEEP control/status register0x000x00 50F3BEEPSPI_CR1SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5020SPI_CRCPRSPI control register0x000x00 5020SPI_CR2SPI control register0x000x00 5203SPI_CRCPRSPI control register0x000x00 5204SPI_CRCPRSPI control register0x000x00 5205SPI_CRCPRSPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 50C8              | CLK                         | CLK_CSSR                | Clock security system register | 0x00                |

| 0x00 S0CA      cLL_PCRENK2      register 2      0x0FP        0x00 50CC      CLK_HSITRIMR      HSI clock calibration trimming<br>register      0x00        0x00 50CD      CLK_SWIMCCR      SWIM clock control register      0bXXXX XXX0        0x00 50CD      Reserved area (3 byte)      0bXXXX XXX0        0x00 50D1      WWDG      WWDG_CR      WWDR window register      0x7F        0x00 50D2      WWDG      WWDG_LWR      WWDR window register      0x7F        0x00 50D2      WWDG      IWDG_LWR      WWDG key register      0xXXX <sup>(2)</sup> 0x00 50D5      IWDG      IWDG perscaler register      0x0X        0x00 50E1      IWDG      IWDG_RLR      IWDG reload register      0x0X        0x00 50E2      IWDG      AWU_CSR1      AWU control/status register      0x0X        0x00 50F1      AWU      AWU_APR      AWU asynchronous prescaler<br>buffer register      0x00        0x00 50F2      BEEP      AWU_TBR      AWU asynchronous prescaler<br>register      0x00        0x00 50F3      BEEP      BEEP_CSR      BEEP control/status register      0x00        0x00 50F4      SPI_CR2      SPI_CR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 50C9              |                             | CLK_CCOR                |                                | 0x00                |

| $ \begin{array}{c c c c c c } \hline \begin{tabular}{ c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 50CA              |                             | CLK_PCKENR2             |                                | 0xFF                |

| 0x00 50CE to 0x00 50D0      Reserved area (3 byte)        0x00 50D1      WWDG      WWDG_CR      WWDG control register      0x7F        0x00 50D2      WWDG      WWDG_WR      WWDR window register      0x7F        0x00 50D2      WWDG      Reserved area (13 byte)      0x7F      0x7F        0x00 50D3 to 00 50DF      Reserved area (13 byte)      0xXX <sup>(2)</sup> 0xXX <sup>(2)</sup> 0x00 50E0      IWDG      IWDG_PR      IWDG prescater register      0xXX <sup>(2)</sup> 0x00 50E2      IWDG      IWDG_RLR      IWDG prescater register      0x00        0x00 50F1      IWDG      AWU      AWU_CSR1      AWU control/status register 1      0x00        0x00 50F2      AWU      AWU_APR      AWU asynchronous prescaler buffer register      0x3F        0x00 50F2      AWU_TBR      AWU timebase selection register      0x00      0x00        0x00 50F3      BEEP      BEEP_CSR      BEEP control/status register      0x1F        0x00 5201      SPI_CR1      SPI control register 1      0x00      0x00        0x00 5203      SPI_CR2      SPI control register 1      0x00        0x00 5203<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 50CC              |                             | CLK_HSITRIMR            | •                              | 0x00                |

| 0x00 50D1      WWDG      WWDG_CR      WWDG control register      0x7F        0x00 50D2      WWDG_WR      WWDR window register      0x7F        0x00 50D3 to 00 50DF      Reserved area (13 byte)      0x7F        0x00 50E0      IWDG_KR      IWDG key register      0x7X <sup>(2)</sup> 0x00 50E1      IWDG      IWDG_RR      IWDG prescaler register      0x0X <sup>(2)</sup> 0x00 50E2      IWDG      IWDG_RLR      IWDG reload register      0x00        0x00 50F0      Reserved area (13 byte)      0x00      0x00      0x00        0x00 50F1      AWU      AWU_CSR1      AWU control/status register      0x00        0x00 50F1      AWU      AWU_APR      AWU asynchronous prescaler buffer register      0x3F        0x00 50F2      AWU_TBR      AWU timebase selection register      0x00        0x00 50F3      BEEP      BEEP_CSR      BEEP control/status register      0x1F        0x00 5201      SPI_CR1      SPI control register 1      0x00      0x00        0x00 5202      SPI_CR2      SPI control register 2      0x00        0x00 5203      SPI_SR      SPI data register      0x00<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 50CD              |                             | CLK_SWIMCCR             | SWIM clock control register    | 0bXXXX XXX0         |

| 0x00 50D2      WWDG      Image: Constraint of the sector of the sec | 0x00 50CE to 0x00 50D0 |                             | Rese                    |                                |                     |

| 0x00 50D2MWDG_WRWWDR window register0x7F0x00 50D3 to 00 50DFReserved area (13 byte)0xXX(2)0x00 50E0IWDGIWDG_KRIWDG key register0xXX(2)0x00 50E1IWDGIWDG_RLRIWDG reload register0x000x00 50E2IWDG_RLRIWDG reload register0x000x00 50E3 to 0x00 50EFReserved area (13 byte)0x000x00 50F0AWU_CSR1AWU control/status register 10x000x00 50F1AWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F3BEEPBEEP_CSRBEEP control/status register0x000x00 50F4 to 0x00 50FFSPI_CR1SPI control register0x000x00 5201SPI_CR2SPI control register0x000x00 5203SPI_CR2SPI control register0x000x00 5203SPI_CR2SPI control register0x000x00 5204SPI_CR2SPI control register0x000x00 5205SPI_CR2SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00 50D1              |                             | WWDG_CR                 | WWDG control register          | 0x7F                |

| 0x00 50E0<br>0x00 50E1IWDGIWDG_KRIWDG key register0xXX(2)0x00 50E1IWDGIWDG_PRIWDG prescaler register0x000x00 50E2IWDG_RLRIWDG reload register0xFF0x00 50E3 to 0x00 50EFReserved area (13 byte)0x000x00 50F0AWU_CSR1AWU control/status register 10x000x00 50F1AWUAWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FFSPI_CR1SPI control register 10x000x00 5200SPI_CR2SPI control register 20x000x00 5201SPI_SRSPI status register0x000x00 5203SPI_DRSPI data register0x020x00 5204SPI_DRSPI control register0x020x00 5205SPI_CRCPRSPI CRC polynomial register0x070x00 5206SPI_RXCRCRSPI RX CRC register0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 50D2              | WWDG                        | WWDG_WR                 | WWDR window register           | 0x7F                |

| 0x00 50E1      IWDG      IWDG_PR      IWDG prescaler register      0x00        0x00 50E2      IWDG_RLR      IWDG reload register      0xFF        0x00 50E3 to 0x00 50EF      Reserved area (13 byte)      0x00        0x00 50F0      AWU_APR      AWU control/status register 1      0x00        0x00 50F1      AWU      AWU_APR      AWU asynchronous prescaler buffer register      0x3F        0x00 50F2      AWU_APR      AWU timebase selection register      0x00      0x00        0x00 50F3      BEEP      BEEP_CSR      BEEP control/status register      0x1F        0x00 50F4 to 0x00 50FF      Reserved area (12 byte)      0x00      0x00      0x00      0x00        0x00 5201      SPI_CR1      SPI control register 1      0x00      0x00        0x00 5202      SPI_CR2      SPI control register 2      0x00        0x00 5203      SPI_SR      SPI status register      0x02        0x00 5204      SPI_CRCPR      SPI data register      0x00        0x00 5205      SPI_CRCPR      SPI CRC polynomial register      0x07        0x00 5205      SPI_CRCPR      SPI CRC polynomial register <td< td=""><td>0x00 50D3 to 00 50DF</td><td></td><td colspan="3">Reserved area (13 byte)</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 50D3 to 00 50DF   |                             | Reserved area (13 byte) |                                |                     |

| 0x00 50E2IWDG_RLRIWDG reload register0xFF0x00 50E3 to 0x00 50EFReserved area (13 byte)0x00 50F00x00 50F0AWU_CSR1AWU control/status register 10x000x00 50F1AWUAWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register 10x000x00 50F4 to 0x00 50FFSPI_CR1SPI control register 10x000x00 5200SPI_CR2SPI control register 10x000x00 5202SPI_SRSPI status register 10x000x00 5203SPI_SPI_DRSPI data register0x020x00 5204SPI_CR2RSPI cRC polynomial register0x000x00 5205SPI_RXCRCRSPI Rx CRC register0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 50E0              |                             | IWDG_KR                 | IWDG key register              | 0xXX <sup>(2)</sup> |

| 0x00 50E3 to 0x00 50EFReserved area (13 byte)0x00 50F0AWU_CSR1AWU control/status register 10x000x00 50F1AWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FFVReserved area (12 byte)0x000x00 5200SPI_CR1SPI control register 10x000x00 5201SPI_CR2SPI control register 20x000x00 5202SPI_SRSPI status register0x020x00 5203SPI_DRSPI control register0x020x00 5204SPI_CRPRSPI data register0x020x00 5205SPI_CRCPRSPI CRC polynomial register0x070x00 5205SPI_RXCRCRSPI Rx CRC register0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 50E1              | IWDG                        | IWDG_PR                 | IWDG prescaler register        | 0x00                |

| 0x00 50F0AWUAWU_CSR1AWU control/status register 10x000x00 50F1AWUAWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FFReserved area (12 byte)0x000x000x00 5200SPI_CR1SPI control register 10x000x00 5201SPI_CR2SPI control register 20x000x00 5202SPI_ICRSPI interrupt control register 20x000x00 5203SPI_SRSPI status register0x020x00 5204SPI_DRSPI data register0x000x00 5205SPI_CR2RSPI CRC polynomial register0x000x00 5205SPI_RXCRCRSPI Rx CRC register0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 50E2              |                             | IWDG_RLR                | IWDG reload register           | 0xFF                |

| 0x00 50F1AWUAWU_APRAWU asynchronous prescaler<br>buffer register0x3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 50E3 to 0x00 50EF |                             | Reser                   | ved area (13 byte)             | ·                   |

| AWUAWU_APRbuffer register0X3F0x00 50F2AWU_TBRAWU timebase selection<br>register0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 50F0              |                             | AWU_CSR1                | AWU control/status register 1  | 0x00                |

| 0x00 50F2AWU_IBRregister0x000x00 50F3BEEPBEEP_CSRBEEP control/status register0x1F0x00 50F4 to 0x00 50FFReserved area (12 byte)0x000x00 5200\$PI_CR1SPI control register 10x000x00 5201\$PI_CR2SPI control register 20x000x00 5202\$PI_ICRSPI interrupt control register 20x000x00 5203\$PI_SRSPI status register0x020x00 5204\$PI_CRCPRSPI data register0x000x00 5205\$PI_CRCPRSPI CRC polynomial register0x070x00 5206\$PI_RXCRCRSPI Rx CRC register0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 50F1              | AWU                         | AWU_APR                 |                                | 0x3F                |

| 0x00 50F4 to 0x00 50FF      Reserved area (12 byte)        0x00 5200      \$\$PI_CR1      \$\$PI control register 1      0x00        0x00 5201      \$\$PI_CR2      \$\$PI control register 2      0x00        0x00 5202      \$\$\$PI_ICR2      \$\$\$PI interrupt control register 2      0x00        0x00 5203      \$\$\$\$PI_SR      \$\$\$\$PI status register      0x02        0x00 5204      \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 50F2              | WWDG                        | AWU_TBR                 |                                | 0x00                |

| 0x00 5200SPI_CR1SPI control register 10x000x00 5201SPI_CR2SPI control register 20x000x00 5202SPI_ICRSPI interrupt control register0x000x00 5203SPI_SRSPI status register0x020x00 5204SPI_DRSPI data register0x000x00 5205SPI_CRCPRSPI CRC polynomial register0x070x00 5206SPI_RXCRCRSPI Rx CRC register0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x00 50F3              | BEEP                        | BEEP_CSR                | BEEP control/status register   | 0x1F                |

| Ox00 5201SPI_CR2SPI control register 2Ox000x00 5202SPI_ICRSPI interrupt control register0x000x00 5203SPI_SRSPI status register0x020x00 5204SPI_DRSPI data register0x000x00 5205SPI_CRCPRSPI CRC polynomial register0x070x00 5206SPI_RXCRCRSPI Rx CRC register0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 50F4 to 0x00 50FF |                             | Reser                   | ved area (12 byte)             |                     |

| Ox00 5202  SPI_ICR  SPI interrupt control register  Ox00    0x00 5203  SPI_SR  SPI status register  0x02    0x00 5204  SPI_DR  SPI data register  0x00    0x00 5205  SPI_CRCPR  SPI CRC polynomial register  0x07    0x00 5206  SPI_RXCRCR  SPI Rx CRC register  0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 5200              |                             | SPI_CR1                 | SPI control register 1         | 0x00                |

| Ox00 5203  SPI    0x00 5204  SPI_SR    0x00 5205  SPI_CRCPR    0x00 5206  SPI_RXCRCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5201              |                             | SPI_CR2                 | SPI control register 2         | 0x00                |

| SPI  SPI    0x00 5204  SPI_DR    0x00 5205  SPI_CRCPR    0x00 5206  SPI_RXCRCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 5202              |                             | SPI_ICR                 | SPI interrupt control register | 0x00                |

| 0x00 5204  SPI_DR  SPI data register  0x00    0x00 5205  SPI_CRCPR  SPI CRC polynomial register  0x07    0x00 5206  SPI_RXCRCR  SPI Rx CRC register  0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 5203              | 0.01                        | SPI_SR                  | SPI status register            | 0x02                |

| 0x00 5206  SPI_RXCRCR  SPI Rx CRC register  0xFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 5204              | SPI                         | SPI_DR                  | SPI data register              | 0x00                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00 5205              |                             | SPI_CRCPR               | SPI CRC polynomial register    | 0x07                |