#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 28                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 640 x 8                                                               |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 4x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s103k3t3c |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

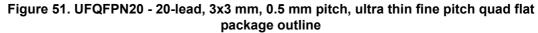

|            | package outline                                                           |

|------------|---------------------------------------------------------------------------|

| Figure 49. | UFQFPN32 - 32-pin, 5 x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat  |

| -          | package recommended footprint                                             |

| Figure 50. | UFQFPN32 marking example (package top view)94                             |

| Figure 51. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|            | package outline                                                           |

| Figure 52. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|            | package recommended footprint                                             |

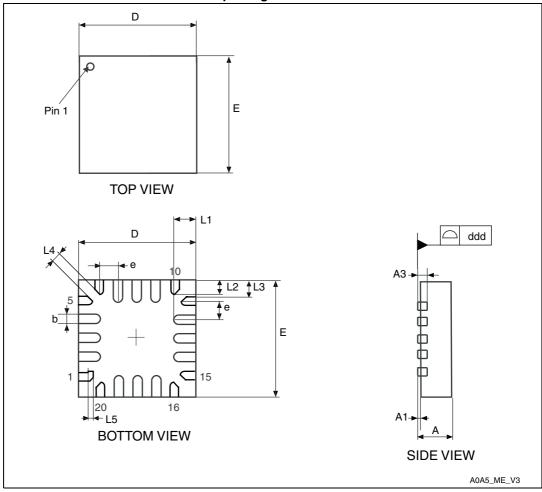

| Figure 53. | UFQFPN20 marking example (package top view)                               |

| Figure 54. | SDIP32 package outline                                                    |

| Figure 55. | SDIP32 marking example (package top view)                                 |

| Figure 56. | TSSOP20 package outline 100                                               |

| Figure 57. | TSSOP20 recommended package footprint 101                                 |

| Figure 58. | TSSOP20 marking example (package top view) 102                            |

| Figure 59. | SO20 package outline                                                      |

| Figure 60. | SO20 marking example (package top view) 104                               |

| Figure 61. | UFQFPN recommended footprint for on-board emulation                       |

| Figure 62. | UFQFPN recommended footprint without on-board emulation                   |

| Figure 63. | STM8S103F2/x3 access line ordering information scheme <sup>(1)</sup>      |

# 5 Pinout and pin description

| Туре                           | I= Input, O = Output, S = Power supply                                                                                                                                                                |                                                                                                                                                                          |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Level                          | Input                                                                                                                                                                                                 | CM = CMOS                                                                                                                                                                |  |  |

| Level                          | Output                                                                                                                                                                                                | HS = High sink                                                                                                                                                           |  |  |

| Output speed                   | O1 = Slow (up to 2 MHz)<br>O2 = Fast (up to 10 MHz)<br>O3 = Fast/slow programmability with slow as default state after reset<br>O4 = Fast/slow programmability with fast as default state after reset |                                                                                                                                                                          |  |  |

| Dent and a sector              | Input                                                                                                                                                                                                 | float = floating,<br>wpu = weak pull-up                                                                                                                                  |  |  |

| Port and control configuration | T = True open drain,OutputOD = Open drain,PP = Push pull                                                                                                                                              |                                                                                                                                                                          |  |  |

| Reset state                    | Unless otherwise specified, the pin s                                                                                                                                                                 | d <b>X</b> (pin state after internal reset release).<br>ess otherwise specified, the pin state is the same during the reset<br>use and after the internal reset release. |  |  |

#### Table 4. Legend/abbreviations for pin description tables

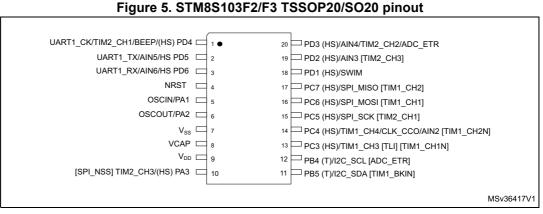

# 5.2 STM8S103F2/F3 TSSOP20/SO20/UFQFPN20 pinout and pin description

### 5.2.1 STM8S103F2/F3 TSSOP20/SO20 pinout

1. HS high sink capability.

2. (T) True open drain (P-buffer and protection diode to VDD not implemented).

3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function)

| Address                | Block | Register label                     | Register name                      | Reset status |

|------------------------|-------|------------------------------------|------------------------------------|--------------|

| 0x00 5208 to 0x00 520F |       | Rese                               | rved area (8 byte)                 |              |

| 0x00 5210              |       | I2C_CR1                            | I2C control register 1             | 0x00         |

| 0x00 5211              |       | I2C_CR2                            | I2C control register 2             | 0x00         |

| 0x00 5212              |       | I2C_FREQR                          | I2C frequency register             | 0x00         |

| 0x00 5213              |       | I2C_OARL                           | I2C Own address register low       | 0x00         |

| 0x00 5214              |       | I2C_OARH                           | I2C Own address register<br>high   | 0x00         |

| 0x00 5215              |       |                                    | Reserved                           |              |

| 0x00 5216              |       | I2C_DR                             | I2C data register                  | 0x00         |

| 0x00 5217              | I2C   | I2C_SR1                            | I2C status register 1              | 0x00         |

| 0x00 5218              |       | I2C_SR2                            | I2C status register 2              | 0x00         |

| 0x00 5219              |       | I2C_SR3                            | I2C status register 3              | 0x0X         |

| 0x00 521A              |       | I2C_ITR                            | I2C interrupt control register     | 0x00         |

| 0x00 521B              |       | I2C_CCRL                           | I2C Clock control register low     | 0x00         |

| 0x00 521C              |       | I2C_CCRH                           | I2C Clock control register high    | 0x00         |

| 0x00 521D              |       | I2C_TRISER                         | I2C TRISE register                 | 0x02         |

| 0x00 521E              |       | I2C_PECR                           | I2C packet error checking register | 0x00         |

| 0x00 521F to 0x00 522F |       | Reser                              | ved area (17 byte)                 |              |

| 0x00 5230              |       | UART1_SR                           | UART1 status register              | 0xC0         |

| 0x00 5231              |       | UART1_DR                           | UART1 data register                | 0xXX         |

| 0x00 5232              |       | UART1_BRR1                         | UART1 baud rate register 1         | 0x00         |

| 0x00 5233              |       | UART1_BRR2                         | UART1 baud rate register 2         | 0x00         |

| 0x00 5234              |       | UART1_CR1                          | UART1 control register 1           | 0x00         |

| 0x00 5235              | UART1 | UART1_CR2                          | UART1 control register 2           | 0x00         |

| 0x00 5236              |       | UART1_CR3                          | UART1 control register 3           | 0x00         |

| 0x00 5237              |       | UART1_CR4                          | UART1 control register 4           | 0x00         |

| 0x00 5238              |       | UART1_CR5 UART1 control register 5 |                                    | 0x00         |

| 0x00 5239              |       | UART1_GTR                          | UART1 guard time register          | 0x00         |

| 0x00 523A              |       | UART1_PSCR                         | UART1 prescaler register           | 0x00         |

| 0x00 523B to 0x00 523F |       | Reser                              | ved area (21 byte)                 |              |

Table 8. General hardware register map (continued)

# 6.2.3 CPU/SWIM/debug module/interrupt controller registers

| Table 9. CPU/SWIM/debug module/interrupt controller registers |                    |                                   |                                           |                 |  |

|---------------------------------------------------------------|--------------------|-----------------------------------|-------------------------------------------|-----------------|--|

| Address                                                       | Block              | Register label                    | Register name                             | Reset<br>status |  |

| 0x00 7F00                                                     |                    | А                                 | Accumulator                               | 0x00            |  |

| 0x00 7F01                                                     |                    | PCE                               | Program counter extended                  | 0x00            |  |

| 0x00 7F02                                                     |                    | PCH                               | Program counter high                      | 0x00            |  |

| 0x00 7F03                                                     |                    | PCL                               | Program counter low                       | 0x00            |  |

| 0x00 7F04                                                     |                    | ХН                                | X index register high                     | 0x00            |  |

| 0x00 7F05                                                     | CPU <sup>(1)</sup> | XL                                | X index register low                      | 0x00            |  |

| 0x00 7F06                                                     |                    | YH                                | Y index register high                     | 0x00            |  |

| 0x00 7F07                                                     |                    | YL                                | Y index register low                      | 0x00            |  |

| 0x00 7F08                                                     |                    | SPH                               | Stack pointer high                        | 0x03            |  |

| 0x00 7F09                                                     |                    | SPL                               | Stack pointer low                         | 0xFF            |  |

| 0x00 7F0A                                                     |                    | CCR                               | Condition code register                   | 0x28            |  |

| 0x00 7F0B to 0x00 7F5F                                        |                    | Reserved                          | area (85 byte)                            |                 |  |

| 0x00 7F60                                                     | CPU                | CFG_GCR                           | Global configuration register             | 0x00            |  |

| 0x00 7F70                                                     |                    | ITC_SPR1                          | Interrupt software priority<br>register 1 | 0xFF            |  |

| 0x00 7F71                                                     |                    | ITC_SPR2                          | Interrupt software priority register 2    | 0xFF            |  |

| 0x00 7F72                                                     |                    | ITC_SPR3                          | Interrupt software priority<br>register 3 | 0xFF            |  |

| 0x00 7F73                                                     | ITC                | ITC_SPR4                          | Interrupt software priority<br>register 4 | 0xFF            |  |

| 0x00 7F74                                                     |                    | ITC_SPR5                          | Interrupt software priority<br>register 5 | 0xFF            |  |

| 0x00 7F75                                                     |                    | ITC_SPR6                          | Interrupt software priority<br>register 6 | 0xFF            |  |

| 0x00 7F76                                                     |                    | ITC_SPR7                          | Interrupt software priority<br>register 7 | 0xFF            |  |

| 0x00 7F77                                                     |                    | ITC_SPR8                          | Interrupt software priority<br>register 8 | 0xFF            |  |

| 0x00 7F78 to 0x00 7F79                                        |                    | Reserved                          | area (2 byte)                             |                 |  |

| 0x00 7F80                                                     | SWIM               | SWIM_CSR SWIM control status 0x00 |                                           |                 |  |

| 0x00 7F81 to 0x00 7F8F                                        |                    | Reserved                          | area (15 byte)                            |                 |  |

#### Table 9. CPU/SWIM/debug module/interrupt controller registers

| Option byte no. | Description                                                                                                                                                                                                                                     |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | <b>EXTCLK:</b> External clock selection<br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                                                                                   |  |

| OPT4            | CKAWUSEL: Auto wake-up unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU<br>PRSC[1:0] AWU clock prescaler<br>0x: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler |  |

|                 | 11: 4 MHz to 128 kHz prescaler                                                                                                                                                                                                                  |  |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>0x00: 2048 HSE cycles<br>0xB4: 128 HSE cycles<br>0xD2: 8 HSE cycles<br>0xE1: 0.5 HSE cycles                                                                                           |  |

Table 12. Option byte description (continued)

# 8.1 Alternate function remapping bits

### Table 13. STM8S103K3 alternate function remapping bits for 32-pin devices

| Option byte no. | Description <sup>(1)</sup>                                                                                                                                                                                                |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | AFR7 Alternate function remapping option 7<br>Reserved.                                                                                                                                                                   |

|                 | <ul> <li>AFR6 Alternate function remapping option 6</li> <li>0: AFR6 remapping option inactive: Default alternate function.<sup>(2)</sup></li> <li>1: Port D7 alternate function = TIM1_CH4.</li> </ul>                   |

| OPT2            | <ul> <li>AFR5 Alternate function remapping option 5</li> <li>0: AFR5 remapping option inactive: Default alternate function.<sup>(2)</sup></li> <li>1: Port D0 alternate function = CLK_CCO.</li> </ul>                    |

|                 | <b>AFR[4:2]</b> Alternate function remapping options 4:2 Reserved.                                                                                                                                                        |

|                 | <b>AFR1</b> Alternate function remapping option 1<br>0: AFR1 remapping option inactive: Default alternate functions. <sup>(2)</sup><br>1: Port A3 alternate function = SPI_NSS; port D2 alternate function =<br>TIM2_CH3. |

|                 | AFR0 Alternate function remapping option 0<br>Reserved.                                                                                                                                                                   |

1. Do not use more than one remapping option in the same port. It is forbidden to enable both AFR1 and AFR0.

2. Refer to pinout description.

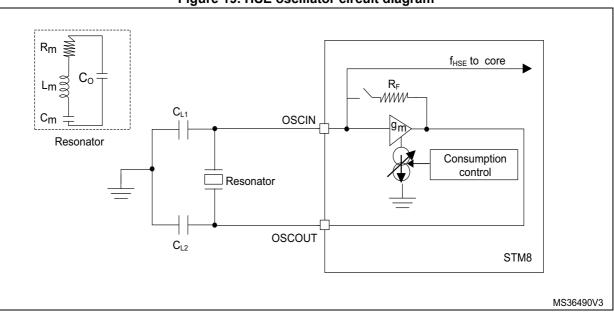

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                             | Min | Тур | Мах                                             | Unit |

|-------------------------------------|---------------------------------------------|----------------------------------------|-----|-----|-------------------------------------------------|------|

| f <sub>HSE</sub>                    | External high speed oscillator frequency    | -                                      | 1   | -   | 16                                              | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                      | -   | 220 | -                                               | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance <sup>(2)</sup> | -                                      | -   | -   | 20                                              | pF   |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption            | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up)<br>1.6 (stabilized) <sup>(3)</sup> | mA   |

|                                     |                                             | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz | -   | -   | 6 (start up)<br>1.2 (stabilized) <sup>(3)</sup> | mA   |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance              | -                                      | 5   | -   | -                                               | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | V <sub>DD</sub> is stabilized          | -   | 1   | -                                               | ms   |

| Table | 33.         | HSE | oscillator | characteristics |

|-------|-------------|-----|------------|-----------------|

| Table | <b>UU</b> . |     | oscillator | characteristics |

1. C is approximately equivalent to 2 x crystal Cload.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small Rm value. Refer to crystal manufacturer for more details

3. Guaranteed by characterization results.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Figure 19. HSE oscillator circuit diagram

### HSE oscillator critical ${\boldsymbol{g}}_{m}$ equation

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

### 10.3.5 Memory characteristics

#### **RAM** and hardware registers

#### Table 36. RAM and hardware registers

| Symbol   | Parameter                          | Conditions           | Min                                | Unit |

|----------|------------------------------------|----------------------|------------------------------------|------|

| $V_{RM}$ | Data retention mode <sup>(1)</sup> | Halt mode (or reset) | V <sub>IT-max</sub> <sup>(2)</sup> | V    |

1. Minimum supply voltage without losing data stored in RAM (in halt mode or under reset) or in hardware registers (only in halt mode). Guaranteed by design, not tested in production.

2. Refer to Section 10.3: Operating conditions for the value of V<sub>IT-max</sub>.

#### Flash program memory/data EEPROM memory

| Symbol             | Parameter                                                                                              | Conditions                | Min <sup>(1)</sup> | Тур | Max  | Unit  |  |

|--------------------|--------------------------------------------------------------------------------------------------------|---------------------------|--------------------|-----|------|-------|--|

| V <sub>DD</sub>    | Operating voltage<br>(all modes, execution/write/erase)                                                | f <sub>CPU</sub> ≤ 16 MHz | 2.95               | -   | 5.5  | V     |  |

| t <sub>prog</sub>  | Standard programming time (including<br>erase) for byte/word/block<br>(1 byte/4 byte/64 byte)          | -                         | - 6 6.6            |     |      |       |  |

| 1 0                | Fast programming time for 1 block (64 byte)                                                            | -                         | -                  | 3   | 3.33 | ms    |  |

| t <sub>erase</sub> | Erase time for 1 block (64 byte)                                                                       | -                         | -                  | 3   | 3.33 |       |  |

| N <sub>RW</sub>    | Erase/write cycles<br>(program memory) <sup>(2)</sup>                                                  | T <sub>A</sub> = +85 °C   | 100k               | -   | -    | cycle |  |

|                    | Erase/write cycles (data memory) <sup>(2)</sup>                                                        | T <sub>A</sub> = +125 °C  | 300k               | 1M  | -    |       |  |

| +                  | Data retention (program and data<br>memory) after 10k erase/write cycles<br>at T <sub>A</sub> = +55 °C | T <sub>RET</sub> = 55 °C  | 20                 | -   | -    | VOOL  |  |

| t <sub>RET</sub>   | Data retention (data memory) after<br>300k erase/write cycles at<br>T <sub>A</sub> = +125°C            | T <sub>RET</sub> = 85 °C  | 1                  | -   | -    | year  |  |

| I <sub>DD</sub>    | Supply current (Flash programming or erasing for 1 to 128 byte)                                        | -                         | -                  | 2   | -    | mA    |  |

#### Table 37. Flash program memory/data EEPROM memory

1. Guaranteed by characterization results.

2. The physical granularity of the memory is 4 byte, so cycling is performed on 4 byte even when a write/erase operation addresses a single byte.

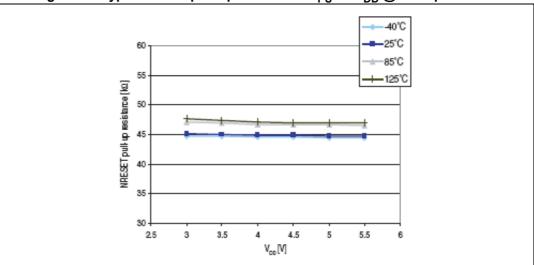

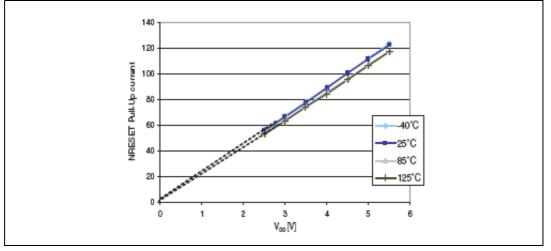

Figure 36. Typical NRST pull-up resistance R<sub>PU</sub> vs V<sub>DD</sub> @ 4 temperatures

Figure 37. Typical NRST pull-up current I<sub>pu</sub> vs V<sub>DD</sub> @ 4 temperatures

The reset network shown in *Figure 38* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below  $V_{IL(NRST)}$  max (see *Table 42: NRST pin characteristics*), otherwise the reset is not taken into account internally.

For power consumption sensitive applications, the external reset capacitor value can be reduced to limit the charge/discharge current. If NRST signal is used to reset external circuitry, attention must be taken to the charge/discharge time of the external capacitor to fulfill the external devices reset timing conditions. Minimum recommended capacity is 100 nF.

| Ourstal Deservator Ocardities (Continued)                                  |                              |                                   |                          |                          |      |

|----------------------------------------------------------------------------|------------------------------|-----------------------------------|--------------------------|--------------------------|------|

| Symbol                                                                     | Parameter                    | Conditions <sup>(1)</sup>         | Min                      | Max                      | Unit |

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                | SPI clock rise and fall time | Capacitive load:<br>C = 30 pF     | -                        | 25                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                        | NSS setup time               | Slave mode                        | 4 * t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                         | NSS hold time                | Slave mode                        | 70                       | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time        | Master mode                       | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input setup time        | Master mode                       | 5                        | -                        |      |

| t <sub>su(MI)</sub> <sup>(2)</sup><br>t <sub>su(SI)</sub> <sup>(2)</sup>   | Data input setup time        | Slave mode                        | 5                        | -                        |      |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)                           | Data input hold time         | Master mode                       | 7                        | -                        |      |

| t <sub>h(SI)</sub> (2)                                                     |                              | Slave mode                        | 10                       | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                       | Data output access time      | Slave mode                        | -                        | 3* t <sub>MASTER</sub>   |      |

| $t_{dis(SO)}^{(2)(4)}$                                                     | Data output disable time     | Slave mode                        | 25                       | -                        |      |

| $t_{v(SO)}^{(2)}$                                                          | Data output valid time       | Slave mode<br>(after enable edge) | -                        | 65                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time       | Master mode (after enable edge)   | -                        | 30                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time        | Slave mode (after enable edge)    | 27                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time        | Master mode (after enable edge)   | 11                       | -                        |      |

Table 43. SPI characteristics (continued)

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

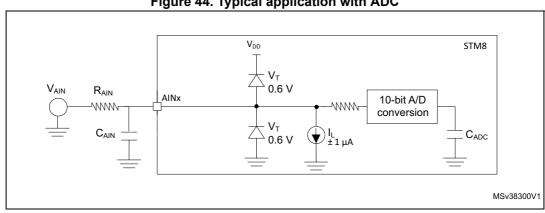

Figure 44. Typical application with ADC

1. Legend:  $R_{AIN}$  = external resistance,  $C_{AIN}$  = capacitors,  $C_{samp}$  = internal sample and hold capacitor.

# 11 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

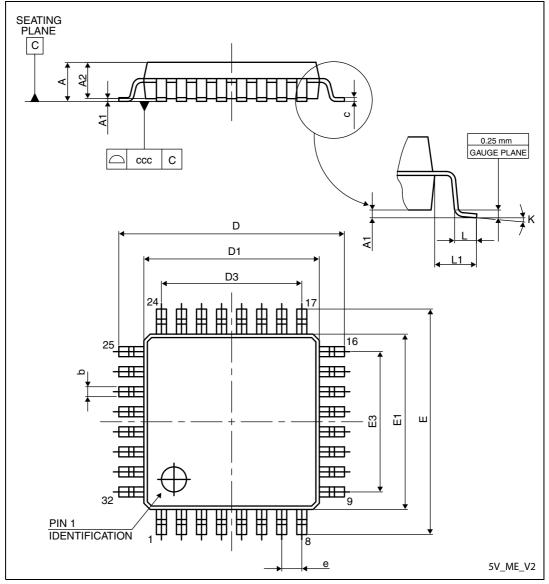

# 11.1 LQFP32 package information

Figure 45. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

DocID15441 Rev 14

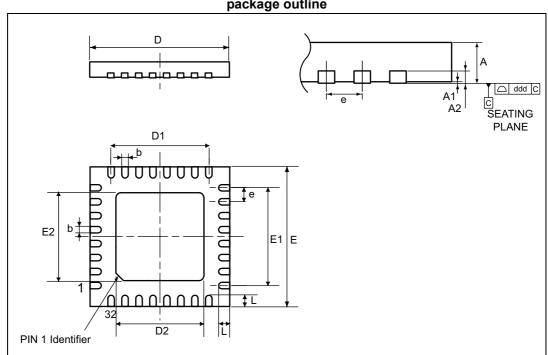

# 11.2 UFQFPN32 package information

Figure 48. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this backside pad to PCB ground.

- 4. Dimensions are in millimeters.

A0B8\_ME\_V2

# 11.3 UFQFPN20 package information

1. Drawing is not to scale.

# Table 54. UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

| Dim. | mm    |       |       | inches <sup>(1)</sup> |        |        |  |  |

|------|-------|-------|-------|-----------------------|--------|--------|--|--|

|      | Min   | Тур   | Мах   | Min                   | Тур    | Max    |  |  |

| A    | 0.500 | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |

| A1   | 0.000 | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |  |

| A3   | -     | 0.152 | -     | -                     | 0.060  | -      |  |  |

| D    | 2.900 | 3.000 | 3.100 | 0.1142                | 0.1181 | 0.1220 |  |  |

| E    | 2.900 | 3.000 | 3.100 | 0.1142                | 0.1181 | 0.1220 |  |  |

| L1   | 0.500 | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |

| L2   | 0.300 | 0.350 | 0.400 | 0.0118                | 0.0138 | 0.0157 |  |  |

Figure 53. UFQFPN20 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| rabio del obli del publicajo internante a data (continued) |       |         |        |                       |        |        |  |  |

|------------------------------------------------------------|-------|---------|--------|-----------------------|--------|--------|--|--|

| Dim.                                                       | mm    |         |        | inches <sup>(1)</sup> |        |        |  |  |

|                                                            | Min   | Тур Мах |        | Min                   | Тур    | Max    |  |  |

| eB                                                         | -     | -       | 12.700 | -                     | -      | 0.5000 |  |  |

| L                                                          | 2.540 | 3.048   | 3.810  | 0.1000                | 0.1200 | 0.1500 |  |  |

#### Table 55. SDIP32 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits

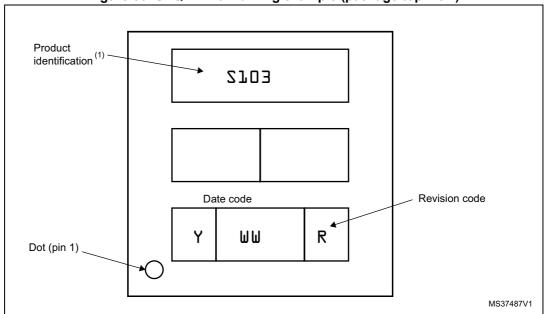

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 55. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# **13** Ordering information

| Figure 63. STM8S103F2                 |      |   |     |   |   |   |   |      |

|---------------------------------------|------|---|-----|---|---|---|---|------|

| Example:                              | STM8 | S | 103 | К | 3 | Т | 6 | TF   |

| Product class                         |      |   |     |   |   |   |   |      |

| STM8 microcontroller                  |      |   |     |   |   |   |   |      |

| Family type                           |      |   |     |   |   |   |   |      |

| S = Standard                          |      |   |     |   |   |   |   |      |

|                                       |      |   |     |   |   |   |   |      |

| Sub-family type                       |      |   |     |   |   |   |   |      |

| 10x = Access line                     |      |   |     |   |   |   |   |      |

| 103 sub-family                        |      |   |     |   |   |   |   |      |

| Pin count                             |      |   |     |   |   |   |   |      |

| K = 32 pins                           |      |   |     |   |   |   |   |      |

| F= 20 pins                            |      |   |     |   |   |   |   |      |

| Program memory size                   |      |   |     |   |   |   |   |      |

| 3 = 8 Kbytes                          |      |   |     |   |   |   |   |      |

| 2 = 4 Kbytes                          |      |   |     |   |   |   |   |      |

| Package type                          |      |   |     |   |   |   |   |      |

| B = SDIP                              |      |   |     |   |   |   |   |      |

|                                       |      |   |     |   |   |   |   |      |

| J = UFQFPN<br>P = TSSOP               |      |   |     |   |   |   |   |      |

| M = SO                                |      |   |     |   |   |   |   |      |

| Temperature range                     |      |   |     |   |   |   |   |      |

| 3 = -40 to 125 °C                     |      |   |     |   |   |   |   |      |

| 6 = -40 to 85 °C                      |      |   |     |   |   |   |   |      |

| Package pitch                         |      |   |     |   |   |   |   |      |

| Blank = 0.5 to 0.65 mm <sup>(2)</sup> |      |   |     |   |   |   |   |      |

| C = 0.8 mm <sup>(3)</sup>             |      |   |     |   |   |   |   |      |

| Packing                               |      |   |     |   |   |   |   |      |

| No character = Tray or tube           |      |   |     |   |   |   |   | <br> |

| TR = Tape and reel                    |      |   |     |   |   |   |   |      |

A dedicated ordering information scheme will be released if, in the future, memory programming service (FastROM) is required The letter "P" will be added after STM8S. Three unique letters identifying the customer application code will also be visible in the codification. Example: STM8SP103K3MACTR.

2. UFQFPN, TSSOP, and SO packages.

3. LQFP package.

# 14 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

# 14.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet your development requirements and to adapt your emulation system to support existing and future ST microcontrollers.

### 14.1.1 STice key features

- Occurrence and time profiling and code coverage (new features),

- Advanced breakpoints with up to 4 levels of conditions,

- Data breakpoints,

- Program and data trace recording up to 128 KB records,

- Read/write on the fly of memory during emulation,

- In-circuit debugging/programming via SWIM protocol,

- 8-bit probe analyzer,

- 1 input and 2 output triggers,

- Power supply follower managing application voltages between 1.62 to 5.5 V,

- Modularity that allows you to specify the components you need to meet your development requirements and adapt to future requirements.

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

## 14.3 **Programming tools**

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the application board via the SWIM protocol. Additional tools include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for the STM8 programming.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.