Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 40MHz                                                                                    |

| Connectivity               | EBI/EMI, Serial Port                                                                     |

| Peripherals                | POR, WDT                                                                                 |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                              |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w77e532a40fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4. PIN DESCRIPTION

| I   | <b>EXTERNAL ACCESS ENABLE:</b> This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address and data will not be present on the bus if $\overline{EA}$ pin is high.                                                                                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | <b>PROGRAM STORE ENABLE:</b> PSEN enables the external ROM data onto the Port 0 address/data bus during fetch and MOVC operations. When internal ROM access is performed, no PSEN strobe signal outputs from this pin.                                                                                                                                                                                                                                                    |

| 0   | ADDRESS LATCH ENABLE: ALE is used to enable the address latch that separates the address from the data on Port 0.                                                                                                                                                                                                                                                                                                                                                         |

| I   | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                                                                                                                                                                                |

| I   | <b>CRYSTAL1:</b> This is the crystal oscillator input. This pin may be driven by an external clock.                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                                                                                                                                                                                                                                                                            |

| I   | GROUND: Ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I   | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I/O | <b>PORT 0:</b> Port 0 is an open-drain bi-directional I/O port. This port also provides a multiplexed low order address/data bus during accesses to external memory.                                                                                                                                                                                                                                                                                                      |

|     | Port 0 has internal pull-up resisters enabled by software.                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O | PORT 1: Port 1 is a bi-directional I/O port with internal pull-ups. The bits have<br>alternate functions which are described below:<br>T2(P1.0): Timer/Counter 2 external count input<br>T2EX(P1.1): Timer/Counter 2 Reload/Capture/Direction control<br>RXD1(P1.2): Serial port 2 RXD<br>TXD1(P1.3): Serial port 2 TXD<br>INT2(P1.4): External Interrupt 2<br>INT3 (P1.5): External Interrupt 3<br>INT4(P1.6): External Interrupt 4<br>INT5 (P1.7): External Interrupt 5 |

| I/O | <b>PORT 2:</b> Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.                                                                                                                                                                                                                                                                                                                |

|     | 0<br>1<br>1<br>1<br>1<br>1/0                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## nuvoton

### 5. FUNCTIONAL DESCRIPTION

The W77E532A is 8052 pin compatible and instruction set compatible. It includes the resources of the standard 8052 such as four 8-bit I/O Ports, three 16-bit timer/counters, full duplex serial port and interrupt sources.

The W77E532A features a faster running and better performance 8-bit CPU with a redesigned core processor without wasted clock and memory cycles. it improves the performance not just by running at high frequency but also by reducing the machine cycle duration from the standard 8052 period of twelve clocks to four clock cycles for the majority of instructions. This improves performance by an average of 1.5 to 3 times. The W77E532A also provides dual Data Pointers (DPTRs) to speed up block data memory transfers. It can also adjust the duration of the MOVX instruction (access to off-chip data memory) between two machine cycles and nine machine cycles. This flexibility allows the W77E532A to work efficiently with both fast and slow RAMs and peripheral devices. In addition, the W77E532A contains on-chip 1KB MOVX SRAM, the address of which is between 0000H and 03FFH. It only can be accessed by MOVX instruction; this on-chip SRAM is optional under software control.

The W77E532A is an 8052 compatible device that gives the user the features of the original 8052 device, but with improved speed and power consumption characteristics. It has the same instruction set as the 8051 family, with one addition: DEC DPTR (op-code A5H, the DPTR is decreased by 1). While the original 8051 family was designed to operate at 12 clock periods per machine cycle, the W77E532A operates at a much reduced clock rate of only 4 clock periods per machine cycle. This naturally speeds up the execution of instructions. Consequently, the W77E532A can run at a higher speed as compared to the original 8052, even if the same crystal is used. Since the W77E532A is a fully static CMOS design, it can also be operated at a lower crystal clock, giving the same throughput in terms of instruction execution, yet reducing the power consumption.

The 4 clocks per machine cycle feature in the W77E532A is responsible for a three-fold increase in execution speed. The W77E532A has all the standard features of the 8052, and has a few extra peripherals and features as well.

#### I/O Ports

The W77E532A has four 8-bit ports and one extra 4-bit port. Port 0 can be used as an Address/Data bus when external program is running or external memory/device is accessed by MOVC or MOVX instruction. In these cases, it has strong pull-ups and pull-downs, and does not need any external pullups. Otherwise it can be used as a general I/O port with open-drain circuit. Port 2 is used chiefly as the upper 8-bits of the Address bus when port 0 is used as an address/data bus. It also has strong pull-ups and pull-downs when it serves as an address bus. Port 1 and 3 act as I/O ports with alternate functions. Port 4 is only available on 44-pin PLCC/QFP package type. It serves as a general purpose I/O port as Port 1 and Port 3. The P4.0 has an alternate function CP/RL2 which is the wait state control signal. When wait state control signal is enabled, P4.0 is input only.

#### Serial I/O

The W77E532A has two enhanced serial ports that are functionally similar to the serial port of the original 8052 family. However the serial ports on the W77E532A can operate in different modes in order to obtain timing similarity as well. Note that the serial port 0 can use Timer 1 or 2 as baud rate generator, but the serial port 1 can only use Timer 1 as baud rate generator. The serial ports have A. s of r the enhanced features of Automatic Address recognition and Frame Error detection.

- 6 -

| WD1 | WD0 | INTERRUPT TIME-OUT | RESET TIME-OUT        |

|-----|-----|--------------------|-----------------------|

| 0   | 0   | 2 <sup>17</sup>    | 2 <sup>17</sup> + 512 |

| 0   | 1   | 2 <sup>20</sup>    | 2 <sup>20</sup> + 512 |

| 1   | 0   | 2 <sup>23</sup>    | 2 <sup>23</sup> + 512 |

| 1   | 1   | 2 <sup>26</sup>    | 2 <sup>26</sup> + 512 |

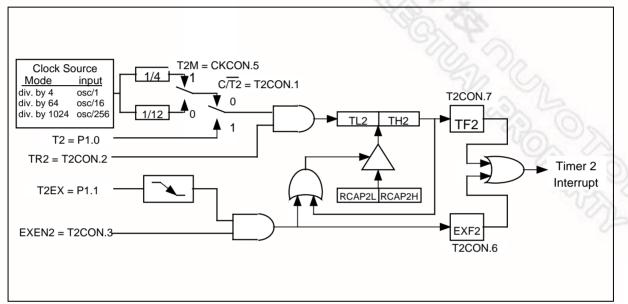

- T2M: Timer 2 clock select: When T2M is set to 1, timer 2 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T1M: Timer 1 clock select: When T1M is set to 1, timer 1 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T0M: Timer 0 clock select: When T0M is set to 1, timer 0 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- MD2–0: Stretch MOVX select bits: These three bits are used to select the stretch value for the MOVX instruction. Using a variable MOVX length enables the user to access slower external memory devices or peripherals without the need for external circuits. The RD or WR strobe will be stretched by the selected interval. When accessing the on-chip SRAM, the MOVX instruction is always in 2 machine cycles regardless of the stretch setting. By default, the stretch has value of 1. If the user needs faster accessing, then a stretch value of 0 should be selected.

| MD2 | MD1 | MD0 | Stretch value | MOVX duration              |

|-----|-----|-----|---------------|----------------------------|

| 0   | 0   | 0   | 0             | 2 machine cycles           |

| 0   | 0   | 1   | 1             | 3 machine cycles (Default) |

| 0   | 1   | 0   | 2             | 4 machine cycles           |

| 0   | 1   | 1   | 3             | 5 machine cycles           |

| 1   | 0   | 0   | 4             | 6 machine cycles           |

| 1   | 0   | 1   | 5             | 7 machine cycles           |

| 1   | 1   | 0   | 6             | 8 machine cycles           |

| 1   | 1   | 1   | 7             | 9 machine cycles           |

Publication Release Date: June 30, 2009 Revision A10

#### **Software Reset**

Set CHPCON = 0X83, timer and enter IDLE mode. CPU will reset and restart from APFLASH after time out.

#### Port 2

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2.0 |

|      |      |      |      |      |      |      |      |      |

Mnemonic: P2

Address: A0h

P2.7-0: Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.

#### Port 4 Chip-select Polarity

| Bit: | 7      | 6      | 5      | 4      | 3 | 2 | 201 | 0    |

|------|--------|--------|--------|--------|---|---|-----|------|

|      | P43INV | P42INV | P42INV | P40INV | - | - | 6   | POUP |

Mnemonic: P4CSIN

Address: A2h

P4xINV: The active polarity of P4.x when set it as chip-select signal. High = Active High. Low = Active Low.

POUP: Enable Port 0 weak pull up.

#### Port 4

| Bit: | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------|---|---|---|---|------|------|------|------|

|      | - | - | - | - | P4.3 | P4.2 | P4.1 | P4.0 |

|      |   |   |   |   |      |      |      |      |

Mnemonic: P4

Address: A5h

P4.3-0: Port 4 is a bi-directional I/O port with internal pull-ups. Port 4 can not use bit-addressable instruction (SETB or CLR).

| Interi                    | Interrupt Enable                                                 |            |     |     |    |     |     |     |     |  |  |  |

|---------------------------|------------------------------------------------------------------|------------|-----|-----|----|-----|-----|-----|-----|--|--|--|

|                           | Bit:                                                             | 7          | 6   | 5   | 4  | 3   | 2   | 1   | 0   |  |  |  |

|                           |                                                                  | EA         | ES1 | ET2 | ES | ET1 | EX1 | ET0 | EX0 |  |  |  |

| Mnemonic: IE Address: A8h |                                                                  |            |     |     |    |     |     |     |     |  |  |  |

| EA:                       | EA: Global enable. Enable/disable all interrupts except for PFI. |            |     |     |    |     |     |     |     |  |  |  |

| ES1:                      | Enable Serial Port                                               | 1 interrup | t.  |     |    |     |     |     |     |  |  |  |

| ET2:                      | Enable Timer 2 inte                                              | errupt.    |     |     |    |     |     |     |     |  |  |  |

| ES:                       | S: Enable Serial Port 0 interrupt.                               |            |     |     |    |     |     |     |     |  |  |  |

| ET1:                      | T1: Enable Timer 1 interrupt                                     |            |     |     |    |     |     |     |     |  |  |  |

| EX1:                      | Enable external inte                                             | errupt 1   |     |     |    |     |     |     |     |  |  |  |

- ET0: Enable Timer 0 interrupt

- EX0: Enable external interrupt 0

#### **Slave Address Mask Enable 1**

SADEN1:This register enables the Automatic Address Recognition feature of the Serial port 1. When a bit in the SADEN1 is set to 1, the same bit location in SADDR1 will be compared with the incoming serial data. When SADEN1.n is 0, then the bit becomes a "don't care" in the comparison. This register enables the Automatic Address Recognition feature of the Serial port 1. When all the bits of SADEN1 are 0, interrupt will occur for any incoming address.

#### **Serial Port Control 1**

| Bit: | 7          | 6         | 5     | 4            | 3     | 2     | all. | 0    |

|------|------------|-----------|-------|--------------|-------|-------|------|------|

|      | SM0_1/FE_1 | SM1_1     | SM2_1 | REN_1        | TB8_1 | RB8_1 | TI_1 | RI_1 |

|      | Mnemon     | ic: SCON1 |       | Address: C0h |       |       |      |      |

SM0\_1/FE\_1: Serial port 1, Mode 0 bit or Framing Error Flag 1: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0\_1 or as FE\_1. the operation of SM0\_1 is described below. When used as FE\_1, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE\_1 condition.

SM1\_1: Serial port 1 Mode bit 1:

| SM0_1 S | M1_1 | Mode | Description  | Length | Baud rate  |

|---------|------|------|--------------|--------|------------|

| 0       | 0    | 0    | Synchronous  | 8      | 4/12 Tclk  |

| 0       | 1    | 1    | Asynchronous | 10     | variable   |

| 1       | 0    | 2    | Asynchronous | 11     | 64/32 Tclk |

| 1       | 1    | 3    | Asynchronous | 11     | variable   |

SM2\_1: Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2\_1 is set to 1, then RI\_1 will not be activated if the received 9<sup>th</sup> data bit (RB8\_1) is 0. In mode 1, if SM2\_1 = 1, then RI\_1 will not be activated if a valid stop bit was not received. In mode 0, the SM2\_1 bit controls the serial port 1 clock. If set to 0, then the serial port 1 runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication.

REN\_1: Receive enable: When set to 1 serial reception is enabled, otherwise reception is disabled.

- TB8\_1: This is the 9<sup>th</sup> bit to be transmitted in modes 2 and 3. This bit is set and cleared by software as desired.

- RB8\_1: In modes 2 and 3 this is the received 9<sup>th</sup> data bit. In mode 1, if SM2\_1 = 0, RB8\_1 is the stop bit that was received. In mode 0 it has no function.

- TI\_1: Transmit interrupt flag: This flag is set by hardware at the end of the 8<sup>th</sup> bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.

| Bit:   | 7       | 6    | 5    | 4    | 3    | 2         | 1    | 0     |

|--------|---------|------|------|------|------|-----------|------|-------|

|        | TA.7    | TA.6 | TA.5 | TA.4 | TA.3 | TA.2      | TA.1 | TfA.0 |

| Mnemor | nic: TA |      | 1    | 200  | Ac   | dress: C7 | 'n   |       |

TA: The Timed Access register controls the access to protected bits. To access protected bits, the user must first write AAH to the TA. This must be immediately followed by a write of 55H to TA. Now a window is opened in the protected bits for three machine cycles, during which the user can write to these bits.

#### **Timer 2 Control**

| Bit: | 7   | 6    | 5    | 4    | 3     | 2       | 1    | 0      |

|------|-----|------|------|------|-------|---------|------|--------|

|      | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2     | C/T2 | CP/RL2 |

|      |     |      |      |      |       | × ( ( ) |      |        |

Mnemonic: T2CON

Address: C8h

- TF2: Timer 2 overflow flag: This bit is set when Timer 2 overflows. It is also set when the count is equal to the capture register in down count mode. It can be set only if RCLK and TCLK are both 0. It is cleared only by software. Software can also set or clear this bit.

- EXF2: Timer 2 External Flag: A negative transition on the T2EX pin (P1.1) or timer 2 overflow will cause this flag to set based on the CP/RL2, EXEN2 and DCEN bits. If set by a negative transition, this flag must be cleared by software. Setting this bit in software or detection of a negative transition on T2EX pin will force a timer interrupt if enabled.

- RCLK: Receive Clock Flag: This bit determines the serial port 0 time-base when receiving data in serial modes 1 or 3. If it is 0, then timer 1 overflow is used for baud rate generation, otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- TCLK: Transmit Clock Flag: This bit determines the serial port 0 time-base when transmitting data in modes 1 and 3. If it is set to 0, the timer 1 overflow is used to generate the baud rate clock otherwise timer 2 overflow is used. Setting this bit forces timer 2 in baud rate generator mode.

- EXEN2: Timer 2 External Enable. This bit enables the capture/reload function on the T2EX pin if Timer 2 is not generating baud clocks for the serial port. If this bit is 0, then the T2EX pin will be ignored, otherwise a negative transition detected on the T2EX pin will result in capture or reload.

- TR2: Timer 2 Run Control. This bit enables/disables the operation of timer 2. Clearing this bit will halt the timer 2 and preserve the current count in TH2, TL2.

- C / T2 : Counter/Timer Select. This bit determines whether timer 2 will function as a timer or a counter. Independent of this bit, the timer will run at 2 clocks per tick when used in baud rate generator mode. If it is set to 0, then timer 2 operates as a timer at a speed depending on T2M bit (CKCON.5), otherwise it will count negative edges on T2 pin.

- CP / RL2: Capture/Reload Select. This bit determines whether the capture or reload function will be used for timer 2. If either RCLK or TCLK is set, this bit will be ignored and the timer will function in an auto-reload mode following each overflow. If the bit is 0 then auto-reload will occur when timer 2 overflows or a falling edge is detected on T2EX pin if EXEN2 = 1. If this bit is 1, then timer 2 captures will occur when a falling edge is detected on T2EX pin if EXEN2 = 1.

- 27 -

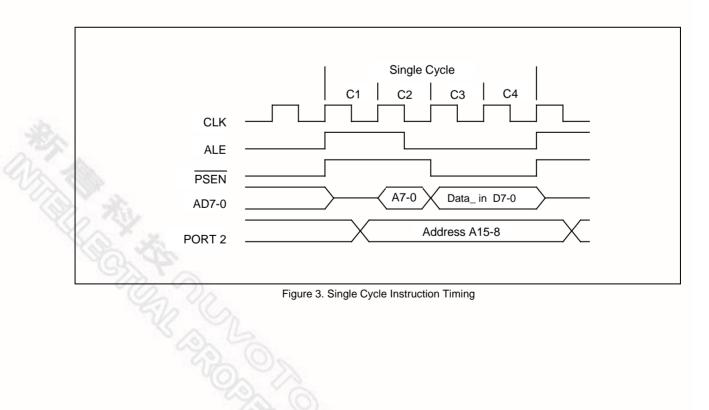

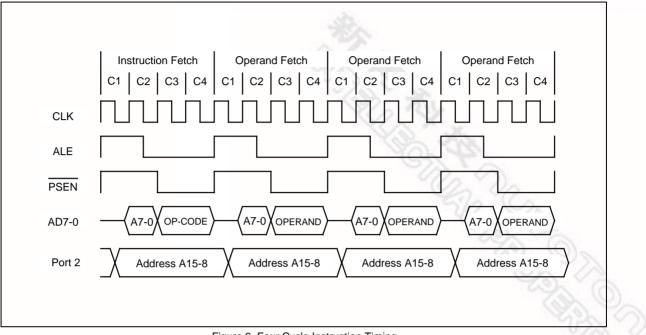

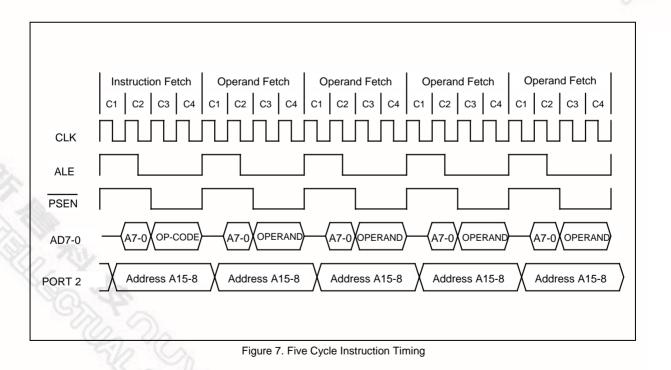

### 8. INSTRUCTION TIMING

The instruction timing for the W77E532A is an important aspect, especially for those users who wish to use software instructions to generate timing delays. Also, it provides the user with an insight into the timing differences between the W77E532A and the standard 8032. In the W77E532A each machine cycle is four clock periods long. Each clock period is designated a state. Thus each machine cycle is made up of four states, C1, C2 C3 and C4, in that order. Due to the reduced time for each instruction execution, both the clock edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. As mentioned earlier, the W77E532A does one op-code fetch per machine cycle. Therefore, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction. Of the 256 available op-codes, 128 of them are single cycle instructions. Thus more than half of all opcodes in the W77E532A are executed in just four clock periods. Most of the two-cycle instructions are those that have two byte instruction codes. However there are some instructions that have only one byte instructions, yet they are two cycle instructions. One instruction which is of importance is the MOVX instruction. In the standard 8032, the MOVX instruction is always two machine cycles long. However in the W77E532A, the user has a facility to stretch the duration of this instruction from 2 machine cycles to 9 machine cycles. The RD and WR strobe lines are also proportionately elongated. This gives the user flexibility in accessing both fast and slow peripherals without the use of external circuitry and with minimum software overhead. The rest of the instructions are either three, four or five machine cycle instructions. Note that in the W77E532A, based on the number of machine cycles, there are five different types, while in the standard 8032 there are only three. However, in the W77E532A each machine cycle is made of only 4 clock periods compared to the 12 clock periods for the standard 8032. Therefore, even though the number of categories has increased, each instruction is at least 1.5 to 3 times faster than the standard 8032 in terms of clock periods.

Publication Release Date: June 30, 2009 Revision A10

### W77E532/W77E532A

## nuvoTon

Figure 6. Four Cycle Instruction Timing

Publication Release Date: June 30, 2009 Revision A10

- 35 -

#### Wait State Control Signal

Either with the software using stretch value to change the required machine cycle of MOVX instruction, the W77E532A provides another hardware signal WAIT to implement the wider duration of external data access timing. This wait state control signal is the alternate function of P4.0 such that it can only be invoked to 44-pin PLCC/QFP package type. The wait state control signal can be enabled by setting WS (WSCON.7) bit. When enabled, the setting of stretch value decides the minimum length of MOVX instruction cycle and the device will sample the WAIT pin at each C3 state before the rising edge of read/write strobe signal during MOVX instruction. Once this signal being recognized, one more machine cycle (wait state cycle) will be inserted into next cycle. The inserted wait state cycles are unlimited, so the MOVX instruction cycle will end in which the wait state control signal is deactivated. Using wait state control signal allows a dynamically access timing to a selected external peripheral. The WS bit is accessed by the Timed Access Protection procedure.

Set WS bit and stretch value = 0 to enable wait signal.

### W77E532/W77E532A

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

|       | External reset | Watchdo   | Watchdog reset |  |  |

|-------|----------------|-----------|----------------|--|--|

| WDCON | 0x0x0xx0b      | 0x0x01x0b | 0100000b       |  |  |

The POR bit WDCON.6 is set only by the power on reset. The PFI bit WDCON.4 is set when the power fail condition occurs. However, a power-on reset will clear this bit. The WTRF bit WDCON.2 is set when the Watchdog timer causes a reset. A power on reset will also clear this bit. The EWT bit WDCON.1 is cleared by power on resets. This disables the Watchdog timer resets. A watchdog or external reset does not affect the EWT bit.

| SOURCE               | VECTOR ADDRESS | SOURCE               | VECTOR ADDRESS |  |  |

|----------------------|----------------|----------------------|----------------|--|--|

| Timer 0 Overflow     | 000Bh          | External Interrupt 0 | 0003h          |  |  |

| Timer 1 Overflow     | 001Bh          | External Interrupt 1 | 0013h          |  |  |

| Timer 2 Interrupt    | 002Bh          | Serial Port          | 0023h          |  |  |

| External Interrupt 2 | 0043h          | Serial Port 1        | 003Bh          |  |  |

| External Interrupt 4 | 0053h          | External Interrupt 3 | 004Bh          |  |  |

| Watchdog Timer       | 0063h          | External Interrupt 5 | 005Bh          |  |  |

#### Table 8. Vector locations for interrupt sources

The vector table is not evenly spaced; this is to accommodate future expansions to the device family.

Execution continues from the vectored address till an RETI instruction is executed. On execution of the RETI instruction the processor pops the Stack and loads the PC with the contents at the top of the stack. The user must take care that the status of the stack is restored to what is was after the hardware LCALL, if the execution is to return to the interrupted program. The processor does not notice anything if the stack contents are modified and will proceed with execution from the address put back into PC. Note that a RET instruction would perform exactly the same process as a RETI instruction, but it would not inform the Interrupt Controller that the interrupt service routine is completed, and would leave the controller still thinking that the service routine is underway.

#### Interrupt Response Time

The response time for each interrupt source depends on several factors, such as the nature of the interrupt and the instruction underway. In the case of external interrupts  $\overline{\text{INT0}}$  to  $\overline{\text{INT5}}$ , they are sampled at C3 of every machine cycle and then their corresponding interrupt flags lex will be set or reset. The Timer 0 and 1 overflow flags are set at C3 of the machine cycle in which overflow has occurred. These flag values are polled only in the next machine cycle. If a request is active and all three conditions are met, then the hardware generated LCALL is executed. This LCALL itself takes four machine cycles to be completed. Thus there is a minimum time of five machine cycles between the interrupt flag being set and the interrupt service routine being executed.

A longer response time should be anticipated if any of the three conditions are not met. If a higher or equal priority is being serviced, then the interrupt latency time obviously depends on the nature of the service routine currently being executed. If the polling cycle is not the last machine cycle of the instruction being executed, then an additional delay is introduced. The maximum response time (if no other interrupt is in service) occurs if the W77E532A is performing a write to IE, IP, EIE or EIP and then executes a MUL or DIV instruction. From the time an interrupt source is activated, the longest reaction time is 12 machine cycles. This includes 1 machine cycle to detect the interrupt, 2 machine cycles to complete the IE, IP, EIE or EIP access, 5 machine cycles to complete the MUL or DIV instruction and 4 machine cycles to complete the hardware LCALL to the interrupt vector location.

Thus in a single-interrupt system the interrupt response time will always be more than 5 machine cycles and not more than 12 machine cycles. The maximum latency of 12 machine cycle is 48 clock cycles. Note that in the standard 8051 the maximum latency is 8 machine cycles which equals 96 machine cycles. This is a 50% reduction in terms of clock periods.

#### Auto-reload Mode, Counting up

The auto-reload mode as an up counter is enabled by clearing the CP / RL2 bit in the T2CON register and clearing the DCEN bit in T2MOD register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFh, a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers. The reload action also sets the TF2 bit. If the EXEN2 bit is set, then a negative transition of T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

Figure 15. 16-Bit Auto-reload Mode, Counting Up

The Watchdog timer should first be restarted by using RWT. This ensures that the timer starts from a known state. The RWT bit is used to restart the watchdog timer. This bit is self clearing, i.e. after writing a 1 to this bit the software will automatically clear it. The watchdog timer will now count clock cycles. The time-out interval is selected by the two bits WD1 and WD0 (CKCON.7 and CKCON.6). When the selected time-out occurs, the Watchdog interrupt flag WDIF (WDCON.3) is set. After the time-out has occurred, the watchdog timer waits for an additional 512 clock cycles. If the Watchdog Reset EWT (WDCON.1) is enabled, then 512 clocks after the time-out, if there is no RWT, a system reset due to Watchdog timer will occur. This will last for two machine cycles, and the Watchdog timer reset flag WTRF (WDCON.2) will be set. This indicates to the software that the watchdog was the cause of the reset.

When used as a simple timer, the reset and interrupt functions are disabled. The timer will set the WDIF flag each time the timer completes the selected time interval. The WDIF flag is polled to detect a time-out and the RWT allows software to restart the timer. The Watchdog timer can also be used as a very long timer. The interrupt feature is enabled in this case. Every time the time-out occurs an interrupt will occur if the global interrupt enable EA is set.

The main use of the Watchdog timer is as a system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash. Using the watchdog timer interrupt during software development will allow the user to select ideal watchdog reset locations. The code is first written without the watchdog interrupt or reset. Then the watchdog interrupt is enabled to identify code locations where interrupt occurs. The user can now insert instructions to reset the watchdog timer which will allow the code to run without any watchdog timer interrupts. Now the watchdog timer reset is enabled and the watchdog interrupt may be disabled. If any errant code is executed now, then the reset watchdog timer instructions will not be executed at the required instants and watchdog reset will occur.

The watchdog time-out selection will result in different time-out values depending on the clock speed. The reset, when enabled, will occur 512 clocks after the time-out has occurred.

| Pr  |     |                      |                     |                      |                  |                  |

|-----|-----|----------------------|---------------------|----------------------|------------------|------------------|

| WD1 | WD0 | WATCHDOG<br>INTERVAL | NUMBER OF<br>CLOCKS | TIME<br>@ 1.8432 MHZ | TIME<br>@ 10 MHZ | TIME<br>@ 25 MHZ |

| 0   | 0   | 2 <sup>17</sup>      | 131072              | 71.11 mS             | 13.11 mS         | 5.24 mS          |

| 0   | 1   | 2 <sup>20</sup>      | 1048576             | 568.89 mS            | 104.86 mS        | 41.94 mS         |

| 1   | 0   | 2 <sup>23</sup>      | 8388608             | 4551.11 mS           | 838.86 mS        | 335.54 mS        |

| 1   | 1   | 2 <sup>26</sup>      | 67108864            | 36408.88 mS          | 6710.89 mS       | 2684.35 mS       |

#### Table 9. Time-out values for the Watchdog timer

The Watchdog timer will de disabled by a power-on/fail reset. The Watchdog timer reset does not disable the watchdog timer, but will restart it. In general, software should restart the timer to put it into a known state.

that s. The control bits that support the Watchdog timer are discussed below.

### **13. TIMED ACCESS PROTECTION**

The W77E532A has several new features, like the Watchdog timer, on-chip ROM size adjustment, wait state control signal and Power on/fail reset flag, which are crucial to proper operation of the system. If left unprotected, errant code may write to the Watchdog control bits resulting in incorrect operation and loss of control. In order to prevent this, the W77E532A has a protection scheme which controls the write access to critical bits. This protection scheme is done using a timed access.

In this method, the bits which are to be protected have a timed write enable window. A write is successful only if this window is active, otherwise the write will be discarded. This write enable window is open for 3 machine cycles if certain conditions are met. After 3 machine cycles, this window automatically closes. The window is opened by writing Aah and immediately 55h to the Timed Access(TA) SFR. This SFR is located at address C7h. The suggested code for opening the timed access window is

TA REG 0C7h ;define new register TA, located at 0C7h

MOV TA, #0Aah

MOV TA, #055h

When the software writes Aah to the TA SFR, a counter is started. This counter waits for 3 machine cycles looking for a write of 55h to TA. If the second write (55h) occurs within 3 machine cycles of the first write (Aah), then the timed access window is opened. It remains open for 3 machine cycles, during which the user may write to the protected bits. Once the window closes the procedure must be repeated to access the other protected bits.

### **18. ELECTRICAL CHARACTERISTICS**

### **18.1 Absolute Maximum Ratings**

| SYMBOL                | PARAMETER | CONDITION | RATING   | UNIT |

|-----------------------|-----------|-----------|----------|------|

| DC Power Supply       | VDD – VSS | -0.3      | +7.0     | V    |

| Input Voltage         | Vin       | Vss -0.3  | VDD +0.3 | V    |

| Operating Temperature | ТА        | 0         | +70      | °C   |

| Storage Temperatute   | Tst       | -55       | +150     | °C   |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliability of the device.

### **18.2 DC Characteristics**

(VDD – Vss = 5V  $\pm$ 10%, TA = 25°C, Fosc = 20 MHz, unless otherwise specified.)

|   | DADAMETED                                     | CYMPO               | SYMPOL |          |      | TEST CONDITIONS                              |

|---|-----------------------------------------------|---------------------|--------|----------|------|----------------------------------------------|

|   | PARAMETER                                     | SYMBOL              | MIN.   | MAX.     | UNIT | TEST CONDITIONS                              |

|   | Operating Voltage                             | Vdd                 | 4.5    | 5.5      | V    | (Q)                                          |

|   | Operating Current                             | IDD                 | -      | 30       | mA   | No load<br>VDD = RST = 5.5V                  |

|   | Idle Current                                  | lidle               | -      | 24       | mA   | Idle mode<br>VDD = 5.5V                      |

|   | Power Down Current                            | IPWDN               | -      | 10       | μA   | Power-down mode<br>VDD = 5.5V                |

|   | Input Current<br>P1, P2, P3                   | lin1                | -50    | +10      | μA   | VDD = 5.5V<br>VIN = 0V or VDD                |

|   | Input Current RST <sup>[*1]</sup>             | lin2                | -10    | +120     | μA   | VDD = 5.5V<br>0 <vin<vdd< td=""></vin<vdd<>  |

|   | Input Leakage Current<br>P0, EA               | Ilk                 | -10    | +10      | μA   | VDD = 5.5V<br>0V <vin<vdd< td=""></vin<vdd<> |

| 3 | Logic 1 to 0 Transition<br>Current P1, P2, P3 | ITL <sup>[*4]</sup> | -500   | -200     | μA   | VDD = 5.5V<br>VIN = 2.0V                     |

| 2 | Input Low Voltage<br>P0, P1, P2, P3, EA       | VIL1                | 0      | 0.8      | V    | Vdd = 4.5V                                   |

| Ľ | Input Low Voltage<br>RST <sup>[*1]</sup>      | VIL2                | 0      | 0.8      | V    | VDD = 4.5V                                   |

|   | Input Low Voltage<br>XTAL1 <sup>['3]</sup>    | VIL3                | 0      | 0.8      | V    | VDD = 4.5V                                   |

|   | Input High Voltage<br>P0, P1, P2, P3, EA      | VIH1                | 2.4    | VDD +0.2 | V    | Vdd = 5.5V                                   |

|   | Input High Voltage RST                        | VIH2                | 3.5    | VDD +0.2 | V    | VDD = 5.5V                                   |

|   | Input High Voltage<br>XTAL1 <sup>[*3]</sup>   | VIH3                | 3.5    | VDD +0.2 | V    | Vdd = 5.5V                                   |

| M2 | M1 | MO | MOVX CYCLES      | T <sub>MCS</sub>     |

|----|----|----|------------------|----------------------|

| 0  | 0  | 0  | 2 machine cycles | 0                    |

| 0  | 0  | 1  | 3 machine cycles | 4 t <sub>CLCL</sub>  |

| 0  | 1  | 0  | 4 machine cycles | 8 t <sub>CLCL</sub>  |

| 0  | 1  | 1  | 5 machine cycles | 12 t <sub>CLCL</sub> |

| 1  | 0  | 0  | 6 machine cycles | 16 t <sub>CLCL</sub> |

| 1  | 0  | 1  | 7 machine cycles | 20 t <sub>CLCL</sub> |

| 1  | 1  | 0  | 8 machine cycles | 24 t <sub>CLCL</sub> |

| 1  | 1  | 1  | 9 machine cycles | 28 t <sub>CLCL</sub> |

### **Explanation of Logics Symbols**

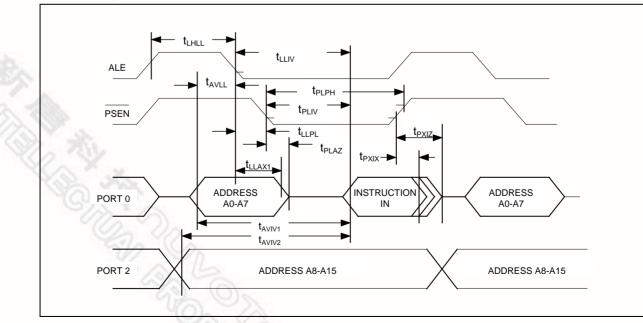

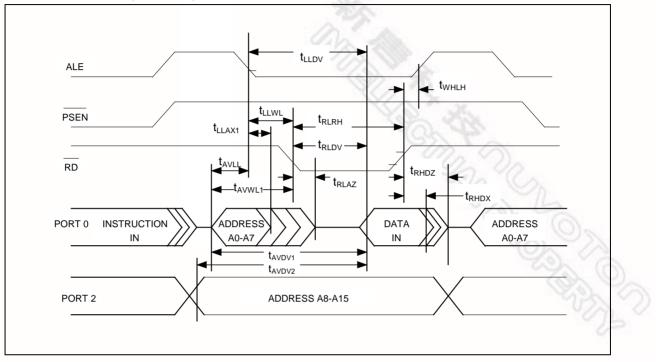

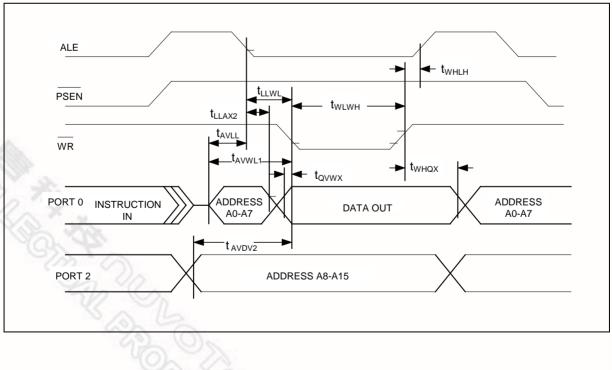

In order to maintain compatibility with the original 8051 family, this device specifies the same parameter for each device, using the same symbols. The explanation of the symbols is as follows.

Input Data

Logic level low

- T Time

- A Address

- C Clock

**Output Data**

- H Logic level high

- I Instruction

- P PSEN

D

L

W

Ζ

R RD signal

V Valid

Q

- X No longer a valid state

- WR signal

- Tri-state

18.3.3 Program Memory Read Cycle

### 18.3.4 Data Memory Read Cycle

### 18.3.5 Data Memory Write Cycle

Publication Release Date: June 30, 2009 Revision A10

#### - 75 -

### **19. TYPICAL APPLICATION CIRCUITS**

### **19.1 Crystal connections**

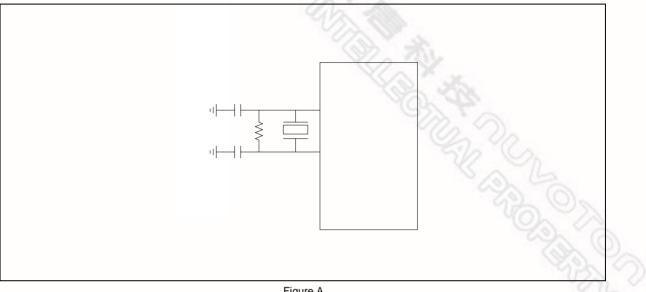

#### Figure A

| CRYSTAL | C1  | C2  | R  |

|---------|-----|-----|----|

| 16 MHz  | 20P | 20P | -  |

| 24 MHz  | 12P | 12P | -  |

| 33 MHz  | 10P | 10P | ЗK |

| 40 MHz  | 1P  | 1P  | ЗK |

The above table shows the reference values for crystal applications.

Note: C1, C2, R components refer to Figure A.

|                                                                                                         |                                                                                                                      | IND ADDRESS = FFFFH                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| BLANK_CHECK_F<br>JMP \$                                                                                 | ERROR:                                                                                                               |                                                                                                                                                     |

| •*************************************                                                                  | *****                                                                                                                | **********                                                                                                                                          |

| ;* RE-PROGRAM                                                                                           | MING 64KB APFLASH BANK                                                                                               | *****                                                                                                                                               |

| ,<br>PROGRAM_64KR                                                                                       | OM:                                                                                                                  |                                                                                                                                                     |

| MOV R2,#<br>MOV R1,#<br>MOV DPT<br>MOV SFR<br>MOV SFR                                                   | 00H ; TARGET H<br>R,#0H<br>AH,R1 ; SFRAH, TA                                                                         | OW BYTE ADDRESS<br>HIGH BYTE ADDRESS<br>ARGET HIGH ADDRESS                                                                                          |

| MOV SFRO<br>MOV R6,#<br>MOV R7,#<br>MOV R7,#<br>MOV TL0,R                                               | ; SFRCN = /<br>9CH ; SET TIME<br>FFH<br>R6                                                                           | 21H, PROGRAM 64K APFLASH0<br>A1H, PROGRAM 64K APFLASH1<br>R FOR PROGRAMMING, ABOUT 50 μS.                                                           |

| PROG_D_64K:                                                                                             |                                                                                                                      |                                                                                                                                                     |

| MOV @DPT<br>MOV SFRFI<br>MOV TCON<br>MOV PCON<br>INC DPTR<br>INC R2<br>CJNE R2,#0<br>INC R1<br>MOV SFRA | BYTE_FROM_PC_TO_ACC<br>TR,A ; SAVE DAT<br>D,A ; SFRFD = E<br>,#10H ; TCON = 10<br>,#01H ; ENTER IDI<br>DH,PROG_D_64K | OW BYTE ADDRESS<br>; THIS PROGRAM IS BASED ON USER'S CIRCUIT.<br>TA INTO SRAM TO VERIFY CODE.<br>DATA IN<br>DH, TR0 = 1,GO<br>LE MODE (PRORGAMMING) |

| ·*************************************                                                                  | ***********                                                                                                          | ********                                                                                                                                            |

|                                                                                                         | APFLASH BANK                                                                                                         | ********                                                                                                                                            |

| , MOV R4,#0<br>MOV R6,#F<br>MOV R7,#F<br>MOV TL0,R<br>MOV TH0,R                                         | DH ; SET TIMEF<br>FH<br>6                                                                                            | OUNTER<br>R FOR READ VERIFY, ABOUT 1.5 μS.                                                                                                          |

| MOV DPTR<br>MOV R2,#0<br>MOV R1,#0<br>MOV SFRA<br>MOV SFRC                                              | ,#0H ; The start a<br>H ; Target low<br>H ; Target hig<br>H,R1 ; SFRAH, Ta<br>N,#00H ; SFRCN = 0                     | ddress of sample code<br>/ byte address<br>h byte address<br>arget high address<br>00H, Read APFLASH0                                               |

| READ_VERIFY_6                                                                                           |                                                                                                                      | 0H , Read APFLASH1                                                                                                                                  |

| MOV SFRA<br>MOV TCON<br>MOV PCON                                                                        | L,R2 ; SFRAL = L<br>,#10H ; TCON = 10                                                                                | OW ADDRESS<br>DH, TR0 = 1,GO                                                                                                                        |

### 22. REVISION HISTORY

| VERSION | DATE                 | PAGE              | DESCRIPTION                                                                                              |

|---------|----------------------|-------------------|----------------------------------------------------------------------------------------------------------|

| A1      | May 30, 2003         | -                 | Initial Issued                                                                                           |

| A2      | March 2, 2005        | 2                 | Add lead free package part number                                                                        |

| A3      | April 18, 2005       | 83                | Add Important Notice                                                                                     |

| A4      | Aug. 23, 2005        | 2, 4,<br>12<br>67 | Add Port 0 pull-up resisters information<br>Remove encrypt function of Security bits B2 description      |

| A5      | Sep. 29, 2006        |                   | Remove block diagram                                                                                     |

| A6      | Dec. 4, 2006         | 2                 | Remove all Leaded package parts                                                                          |

| A7      | February 1, 2007     | 14                | Revise the Timer Mode Setting to "Mode 1: 16-bits, no prescale".                                         |

| A8      | April 17, 2007       | 45                | Revise that Power Down Mode is released by external interrupt configured as either level or edge detect. |

| 4.0     | November 19,<br>2007 | -                 | Remove NVM description                                                                                   |

| A9      |                      | 76                | Change chapter 19.1 Figure A to crystal connections                                                      |

| A10     | June 30, 2009        | 2                 | Remove 64 Byte NVM description in FEATURES.                                                              |