Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Obsolete                                                           |

| Core Processor             | ST6                                                                |

| Core Size                  | 8-Bit                                                              |

| Speed                      | 8MHz                                                               |

| Connectivity               | SPI                                                                |

| Peripherals                | LED, LVD, POR, WDT                                                 |

| Number of I/O              | 21                                                                 |

| Program Memory Size        | 3.8KB (3.8K x 8)                                                   |

| Program Memory Type        | OTP                                                                |

| EEPROM Size                | 128 x 8                                                            |

| RAM Size                   | 128 x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                            |

| Data Converters            | A/D 13x8b                                                          |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Through Hole                                                       |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                           |

| Supplier Device Package    | -                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st62t65cb6 |

|       | lable of Contents                               | Document<br>Page |

|-------|-------------------------------------------------|------------------|

| ST62  | 2T55C                                           | i age            |

| _     | 2T65C/E65C                                      | 1                |

|       |                                                 |                  |

|       | ERAL DESCRIPTION                                |                  |

|       | INTRODUCTION                                    |                  |

| 1.2   | PIN DESCRIPTIONS                                | 6                |

| 1.3   | MEMORY MAP                                      | 7                |

|       | 1.3.1 Introduction                              | 7                |

|       | 1.3.2 Program Space                             |                  |

|       | 1.3.3 Data Space                                |                  |

|       | 1.3.4 Stack Space                               |                  |

|       | 1.3.5 Data Window Register (DWR)                |                  |

|       | 1.3.6 Data RAM/EEPROM Bank Register (DRBR)      |                  |

| 1 4   | PROGRAMMING MODES                               |                  |

|       | 1.4.1 Option Bytes                              |                  |

|       | 1.4.2 EPROM Erasing                             |                  |

| 2 CEN | TRAL PROCESSING UNIT                            |                  |

| 2.1   | INTRODUCTION                                    | 16               |

| 2.2   | CPU REGISTERS                                   | 16               |

|       | CKS, RESET, INTERRUPTS AND POWER SAVING MODES   |                  |

|       | CLOCK SYSTEM                                    |                  |

|       | 3.1.1 Main Oscillator                           |                  |

|       | 3.1.2 Low Frequency Auxiliary Oscillator (LFAO) |                  |

|       | 3.1.3 Oscillator Safe Guard                     |                  |

| 3.2   | RESETS                                          | 23               |

|       | 3.2.1 RESET Input                               | 23               |

|       | 3.2.2 Power-on Reset                            | 23               |

|       | 3.2.3 Watchdog Reset                            |                  |

|       | 3.2.4 LVD Reset                                 |                  |

|       | 3.2.5 Application Notes                         |                  |

| 3.3   | 3.2.6 MCU Initialization Sequence               |                  |

| 3.3   |                                                 |                  |

|       | 3.3.1 Digital Watchdog Register (DWDR)          |                  |

| 3.4   | INTERRUPTS                                      |                  |

| 0.4   | 3.4.1 Interrupt request                         |                  |

|       | 3.4.2 Interrupt Procedure                       |                  |

|       | 3.4.3 Interrupt Option Register (IOR)           |                  |

|       | 3.4.4 Interrupt sources                         |                  |

| 3.5   | POWER SAVING MODES                              |                  |

|       | 3.5.1 WAIT Mode                                 | 35               |

|       | 3.5.2 STOP Mode                                 | 35               |

|       | 3.5.3 Exit from WAIT and STOP Modes             | 36               |

|        | Table of Contents                        | Documen<br>Page |

|--------|------------------------------------------|-----------------|

| 4 ON-0 | CHIP PERIPHERALS                         | 37              |

| 4.1    | I/O PORTS                                | 37              |

|        | 4.1.1 Operating Modes                    |                 |

|        | 4.1.2 Safe I/O State Switching Sequence  |                 |

|        | 4.1.3 Timer 1 Alternate function Option  |                 |

|        | 4.1.4 AR Timer Alternate function Option |                 |

| 42     | TIMER                                    |                 |

| 7.2    | 4.2.1 Timer Operating Modes              |                 |

|        | 4.2.2 Timer Interrupt                    |                 |

|        | 4.2.3 Application Notes                  |                 |

|        | 4.2.4 Timer Registers                    |                 |

| 4.3    | AUTO-RELOAD TIMER                        | 46              |

|        | 4.3.1 AR Timer Description               |                 |

|        | 4.3.2 Timer Operating Modes              |                 |

| 4.4    | 4.3.3 AR Timer Registers                 |                 |

| 4.4    | A/D CONVERTER (ADC)                      |                 |

| 4.5    | 4.4.1 Application Notes                  | 54              |

|        | 4.5.1 SPI Registers                      |                 |

|        | SPI TIMING DIAGRAMS                      |                 |

|        | TWARE                                    |                 |

| 5.1    | ST6 ARCHITECTURE                         |                 |

| 5.2    | ADDRESSING MODES                         | 59              |

|        | INSTRUCTION SET                          |                 |

|        | CTRICAL CHARACTERISTICS                  |                 |

|        | ABSOLUTE MAXIMUM RATINGS                 |                 |

| 6.2    | RECOMMENDED OPERATING CONDITIONS         | 66              |

| 6.3    | DC ELECTRICAL CHARACTERISTICS            | 67              |

| 6.4    | AC ELECTRICAL CHARACTERISTICS            | 68              |

| 6.5    | A/D CONVERTER CHARACTERISTICS            | 69              |

| 6.6    | TIMER CHARACTERISTICS                    | 69              |

| 6.7    | SPI CHARACTERISTICS                      | 69              |

| 6.8    | ARTIMER ELECTRICAL CHARACTERISTICS       | 69              |

| 7 GEN  | ERAL INFORMATION                         | 75              |

| 7.1    | PACKAGE MECHANICAL DATA                  | 75              |

| 7.2    | ORDERING INFORMATION                     | 77              |

| Table of Contents               | Documer<br>Page |

|---------------------------------|-----------------|

| ST62P55C<br>ST62P65C            | _               |

| 1.1 INTRODUCTION                | 80              |

| 1.2.1 Transfer of Customer Code | 80              |

| ST6255C<br>ST6265B              | 81              |

| 1.1 INTRODUCTION                |                 |

| 1.2 ROM READOUT PROTECTION      | 83              |

| 1.3.1 Transfer of Customer Code | 83              |

# **MEMORY MAP** (Cont'd)

### 1.3.3 Data Space

Data Space accommodates all the data necessary for processing the user program. This space comprises the RAM resource, the processor core and peripheral registers, as well as read-only data such as constants and look-up tables in OTP/EPROM.

#### 1.3.3.1 Data ROM

All read-only data is physically stored in program memory, which also accommodates the Program Space. The program memory consequently contains the program code to be executed, as well as the constants and look-up tables required by the application.

The Data Space locations in which the different constants and look-up tables are addressed by the processor core may be thought of as a 64-byte window through which it is possible to access the read-only data stored in OTP/EPROM.

#### 1.3.3.2 Data RAM/EEPROM

In ST62T55C, ST62T65C and ST62E65C devices, the data space includes 60 bytes of RAM, the accumulator (A), the indirect registers (X), (Y), the short direct registers (V), (W), the I/O port registers, the peripheral data and control registers, the interrupt option register and the Data ROM Window register (DRW register).

Additional RAM and EEPROM pages can also be addressed using banks of 64 bytes located between addresses 00h and 3Fh.

# 1.3.4 Stack Space

Stack space consists of six 12-bit registers which are used to stack subroutine and interrupt return addresses, as well as the current program counter contents.

Table 1. Additional RAM/EEPROM Banks

| Device        | RAM          | EEPROM       |

|---------------|--------------|--------------|

| ST62T55C      | 1 x 64 bytes | -            |

| ST62T65C/E65C | 1 x 64 bytes | 2 x 64 bytes |

Table 2. ST62T55C, ST62T65C and ST62E65C Data Memory Space

| DAM and EEDDOM                    | 000h  |

|-----------------------------------|-------|

| RAM and EEPROM                    | 03Fh  |

|                                   | 040h  |

| DATA ROM WINDOW AREA              |       |

|                                   | 07Fh  |

| X REGISTER                        | 080h  |

| Y REGISTER                        | 081h  |

| V REGISTER                        | 082h  |

| W REGISTER                        | 083h  |

|                                   | 084h  |

| DATA RAM 60 BYTES                 | 0BFh  |

| PORT A DATA REGISTER              | 0C0h  |

| PORT B DATA REGISTER              | 0C1h  |

| PORT C DATA REGISTER              | 0C2h  |

| RESERVED                          | 0C3h  |

| PORT A DIRECTION REGISTER         | 0C4h  |

| PORT B DIRECTION REGISTER         | 0C5h  |

| PORT C DIRECTION REGISTER         | 0C6h  |

| RESERVED                          | 0C7h  |

| INTERRUPT OPTION REGISTER         | 0C8h* |

| DATA ROM WINDOW REGISTER          | 0C9h* |

|                                   | 0CAh  |

| RESERVED                          | 0CBh  |

| PORT A OPTION REGISTER            | 0CCh  |

| PORT B OPTION REGISTER            | 0CDh  |

| PORT C OPTION REGISTER            | 0CEh  |

| RESERVED                          | 0CFh  |

| A/D DATA REGISTER                 | 0D0h  |

| A/D CONTROL REGISTER              | 0D0h  |

| TIMER PRESCALER REGISTER          | 0D1h  |

| TIMER COUNTER REGISTER            | 0D3h  |

| TIMER STATUS CONTROL REGISTER     | 0D4h  |

| AR TIMER MODE CONTROL REGISTER    | 0D5h  |

| AR TIMER STATUS/CONTROL REGISTER1 | 0D6h  |

| AR TIMER STATUS/CONTROL REGISTER2 | 0D7h  |

| WATCHDOG REGISTER                 | 0D8h  |

| AR TIMER RELOAD/CAPTURE REGISTER  | 0D9h  |

| AR TIMER COMPARE REGISTER         | 0DAh  |

| AR TIMER LOAD REGISTER            | 0DBh  |

| OSCILLATOR CONTROL REGISTER       | 0DCh* |

| MISCELLANEOUS                     | 0DDh  |

|                                   | 0DEh  |

| RESERVED                          | 0DFh  |

| SPI DATA REGISTER                 | 0E0h  |

| SPI DIVIDER REGISTER              | 0E1h  |

| SPI MODE REGISTER                 | 0E2h  |

|                                   | 0E3h  |

| RESERVED                          | 0E7h  |

| DATA RAM/EEPROM REGISTER          | 0E8h* |

| RESERVED                          | 0E9h  |

| EEPROM CONTROL REGISTER           | 0EAh  |

| DE0ED /50                         | 0EBh  |

| RESERVED                          | 0FEh  |

| ACCUMULATOR                       | 0FFh  |

| * WRITE ONLY REGISTER             | •     |

WRITE ONLY REGISTER

<u> 577</u>

#### **MEMORY MAP** (Cont'd)

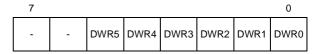

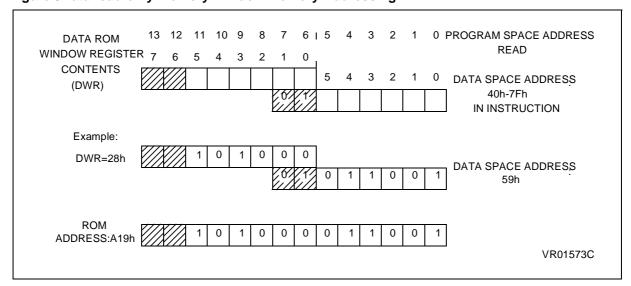

## 1.3.5 Data Window Register (DWR)

The Data read-only memory window is located from address 0040h to address 007Fh in Data space. It allows direct reading of 64 consecutive bytes located anywhere in program memory, between address 0000h and 0FFFh (top memory address depends on the specific device). All the program memory can therefore be used to store either instructions or read-only data. Indeed, the window can be moved in steps of 64 bytes along the program memory by writing the appropriate code in the Data Window Register (DWR).

The DWR can be addressed like any RAM location in the Data Space, it is however a write-only register and therefore cannot be accessed using singlebit operations. This register is used to position the 64-byte read-only data window (from address 40h to address 7Fh of the Data space) in program memory in 64-byte steps. The effective address of the byte to be read as data in program memory is obtained by concatenating the 6 least significant bits of the register address given in the instruction (as least significant bits) and the content of the DWR register (as most significant bits), as illustrated in Figure 5 below. For instance, when addressing location 0040h of the Data Space, with 0 loaded in the DWR register, the physical location addressed in program memory is 00h. The DWR register is not cleared on reset, therefore it must be written to prior to the first access to the Data readonly memory window area.

# Data Window Register (DWR)

Address: 0C9h — Write Only

Bits 6, 7 = Not used.

Bit 5-0 = **DWR5-DWR0**: *Data read-only memory Window Register Bits*. These are the Data read-only memory Window bits that correspond to the upper bits of the data read-only memory space.

**Caution:** This register is undefined on reset. Neither read nor single bit instructions may be used to address this register.

**Note:** Care is required when handling the DWR register as it is write only. For this reason, the DWR contents should not be changed while executing an interrupt service routine, as the service routine cannot save and then restore the register's previous contents. If it is impossible to avoid writing to the DWR during the interrupt service routine, an image of the register must be saved in a RAM location, and each time the program writes to the DWR, it must also write to the image register. The image register must be written first so that, if an interrupt occurs between the two instructions, the DWR is not affected.

Figure 5Data read-only memory Window Memory Addressing

# PROGRAMMING MODES (Cont'd)

### 1.4.2 EPROM Erasing

The EPROM of the windowed package of the MCUs may be erased by exposure to Ultra Violet light. The erasure characteristic of the MCUs is such that erasure begins when the memory is exposed to light with a wave lengths shorter than approximately 4000Å. It should be noted that sunlights and some types of fluorescent lamps have wavelengths in the range 3000-4000Å.

It is thus recommended that the window of the MCUs packages be covered by an opaque label to

prevent unintentional erasure problems when testing the application in such an environment.

The recommended erasure procedure of the MCUs EPROM is the exposure to short wave ultraviolet light which have a wave-length 2537A. The integrated dose (i.e. U.V. intensity x exposure time) for erasure should be a minimum of 15W-sec/cm<sup>2</sup>. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000µW/cm<sup>2</sup> power rating. The ST62E65C should be placed within 2.5cm (1Inch) of the lamp tubes during erasure.

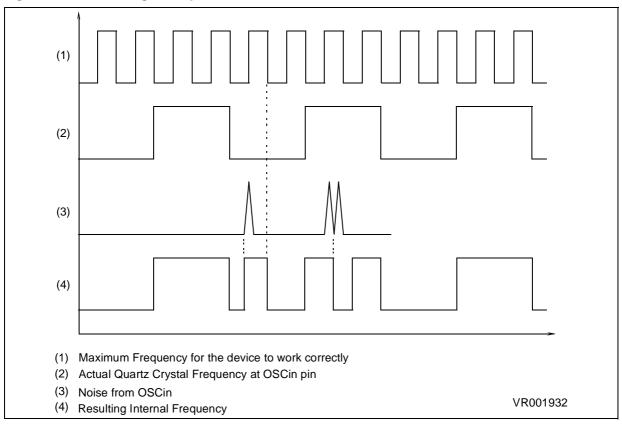

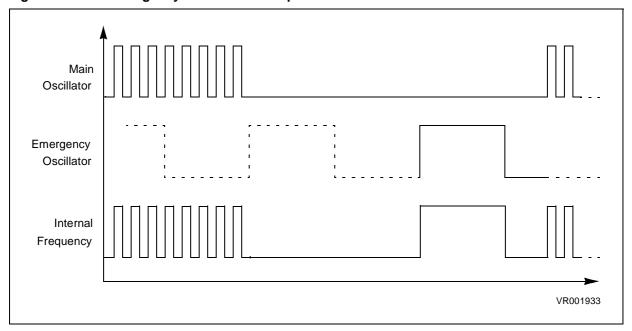

# **CLOCK SYSTEM** (Cont'd)

Figure 9. OSG Filtering Principle

Figure 10. OSG Emergency Oscillator Principle

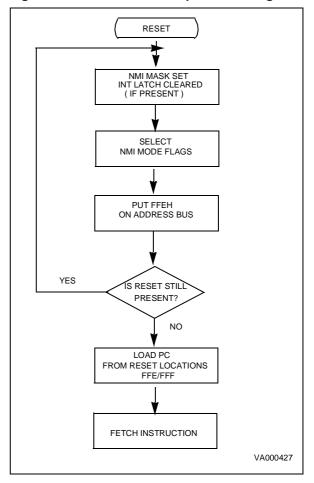

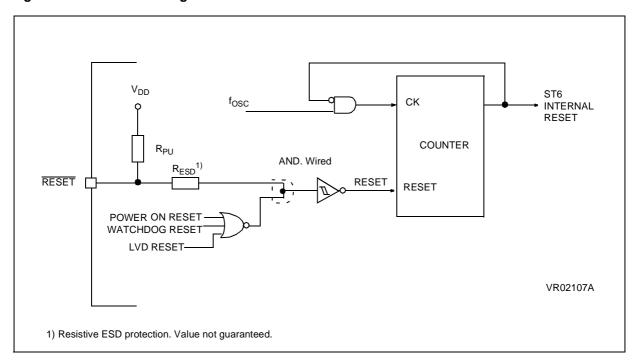

## 3.2 RESETS

The MCU can be reset in four ways:

- by the external Reset input being pulled low;

- by Power-on Reset:

- by the digital Watchdog peripheral timing out.

- by Low Voltage Detection (LVD)

#### 3.2.1 RESET Input

The RESET pin may be connected to a device of the application board in order to reset the MCU if required. The RESET pin may be pulled low in RUN, WAIT or STOP mode. This input can be used to reset the MCU internal state and ensure a correct start-up procedure. The pin is active low and features a Schmitt trigger input. The internal Reset signal is generated by adding a delay to the external signal. Therefore even short pulses on the RESET pin are acceptable, provided V<sub>DD</sub> has completed its rising phase and that the oscillator is running correctly (normal RUN or WAIT modes). The MCU is kept in the Reset state as long as the RESET pin is held low.

If RESET activation occurs in the RUN or WAIT modes, processing of the user program is stopped (RUN mode only), the Inputs and Outputs are configured as inputs with pull-up resistors and the main Oscillator is restarted. When the level on the RESET pin then goes high, the initialization sequence is executed following expiry of the internal delay period.

If RESET pin activation occurs in the STOP mode, the oscillator starts up and all Inputs and Outputs are configured as inputs with pull-up resistors. When the level of the RESET pin then goes high, the initialization sequence is executed following expiry of the internal delay period.

## 3.2.2 Power-on Reset

The function of the POR circuit consists in waking up the MCU by detecting around 2V a dynamic (rising edge) variation of the VDD Supply. At the beginning of this sequence, the MCU is configured in the Reset state: all I/O ports are configured as inputs with pull-up resistors and no instruction is executed. When the power supply voltage rises to a sufficient level, the oscillator starts to operate, whereupon an internal delay is initiated, in order to allow the oscillator to fully stabilize before executing the first instruction. The initialization sequence

is executed immediately following the internal delay.

To ensure correct start-up, the user should take care that the VDD Supply is stabilized at a sufficient level for the chosen frequency (see recommended operation) before the reset signal is released. In addition, supply rising must start from OV

As a consequence, the POR does not allow to supervise static, slowly rising, or falling, or noisy (presenting oscillation) VDD supplies.

An external RC network connected to the RESET pin, or the LVD reset can be used instead to get the best performances.

Figure 13. Reset and Interrupt Processing

# RESETS (Cont'd)

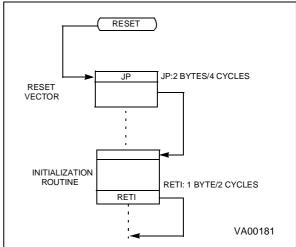

## 3.2.6 MCU Initialization Sequence

When a reset occurs the stack is reset, the PC is loaded with the address of the Reset Vector (located in program ROM starting at address 0FFEh). A jump to the beginning of the user program must be coded at this address. Following a Reset, the Interrupt flag is automatically set, so that the CPU is in Non Maskable Interrupt mode; this prevents the initialisation routine from being interrupted. The initialisation routine should therefore be terminated by a RETI instruction, in order to revert to normal mode and enable interrupts. If no pending interrupt is present at the end of the initialisation routine, the MCU will continue by processing the instruction immediately following the RETI instruction. If, however, a pending interrupt is present, it will be serviced.

Figure 15. Reset and Interrupt Processing

Figure 16. Reset Block Diagram

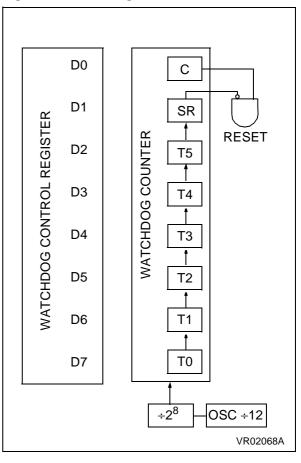

### 3.3 DIGITAL WATCHDOG

The digital Watchdog consists of a reloadable downcounter timer which can be used to provide controlled recovery from software upsets.

The Watchdog circuit generates a Reset when the downcounter reaches zero. User software can prevent this reset by reloading the counter, and should therefore be written so that the counter is regularly reloaded while the user program runs correctly. In the event of a software mishap (usually caused by externally generated interference), the user program will no longer behave in its usual fashion and the timer register will thus not be reloaded periodically. Consequently the timer will decrement down to 00h and reset the MCU. In order to maximise the effectiveness of the Watchdog function, user software must be written with this concept in mind.

Watchdog behaviour is governed by two options, known as "WATCHDOG ACTIVATION" (i.e. HARDWARE or SOFTWARE) and "EXTERNAL STOP MODE CONTROL" (see Table 6).

In the SOFTWARE option, the Watchdog is disabled until bit C of the DWDR register has been set.

When the Watchdog is disabled, low power Stop mode is available. Once activated, the Watchdog cannot be disabled, except by resetting the MCU.

In the HARDWARE option, the Watchdog is permanently enabled. Since the oscillator will run continuously, low power mode is not available. The STOP instruction is interpreted as a WAIT instruction, and the Watchdog continues to countdown.

However, when the EXTERNAL STOP MODE CONTROL option has been selected low power consumption may be achieved in Stop Mode.

Execution of the STOP instruction is then governed by a secondary function associated with the NMI pin. If a STOP instruction is encountered when the NMI pin is low, it is interpreted as WAIT, as described above. If, however, the STOP instruction is encountered when the NMI pin is high, the Watchdog counter is frozen and the CPU enters STOP mode.

When the MCU exits STOP mode (i.e. when an interrupt is generated), the Watchdog resumes its activity.

**Table 6. Recommended Option Choices**

| Functions Required   | Recommended Options                        |

|----------------------|--------------------------------------------|

| Stop Mode & Watchdog | "EXTERNAL STOP MODE" & "HARDWARE WATCHDOG" |

| Stop Mode            | "SOFTWARE WATCHDOG"                        |

| Watchdog             | "HARDWARE WATCHDOG"                        |

# **DIGITAL WATCHDOG** (Cont'd)

The Watchdog is associated with a Data space register (Digital WatchDog Register, DWDR, location 0D8h) which is described in greater detail in Section 3.3.1 Digital Watchdog Register (DWDR). This register is set to 0FEh on Reset: bit C is cleared to "0", which disables the Watchdog; the timer downcounter bits, T0 to T5, and the SR bit are all set to "1", thus selecting the longest Watchdog timer period. This time period can be set to the user's requirements by setting the appropriate value for bits T0 to T5 in the DWDR register. The SR bit must be set to "1", since it is this bit which generates the Reset signal when it changes to "0"; clearing this bit would generate an immediate Reset

It should be noted that the order of the bits in the DWDR register is inverted with respect to the associated bits in the down counter: bit 7 of the DWDR register corresponds, in fact, to T0 and bit 2 to T5. The user should bear in mind the fact that these bits are inverted and shifted with respect to the physical counter bits when writing to this register. The relationship between the DWDR register bits and the physical implementation of the Watchdog timer downcounter is illustrated in Figure 17.

Only the 6 most significant bits may be used to define the time period, since it is bit 6 which triggers the Reset when it changes to "0". This offers the user a choice of 64 timed periods ranging from 3,072 to 196,608 clock cycles (with an oscillator frequency of 8MHz, this is equivalent to timer periods ranging from 384 µs to 24.576 ms).

Figure 17. Watchdog Counter Control

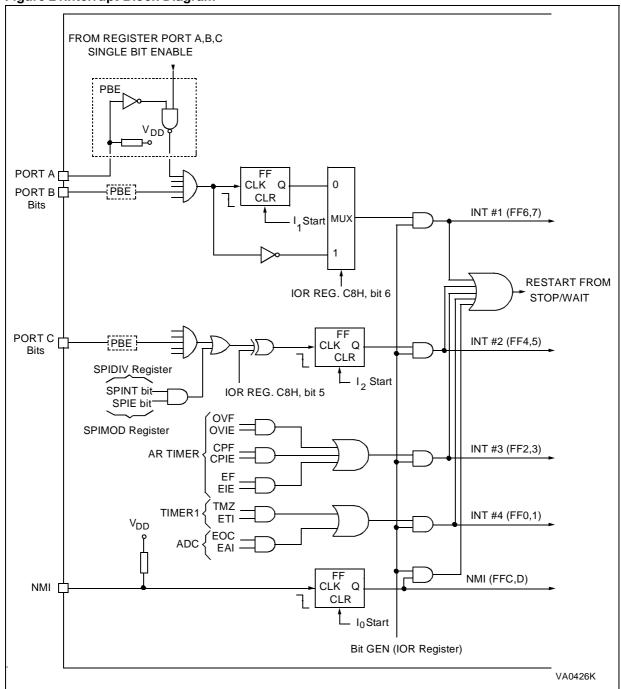

# **INTERRUPTS** (Cont'd)

Figure 21Interrupt Block Diagram

# **4 ON-CHIP PERIPHERALS**

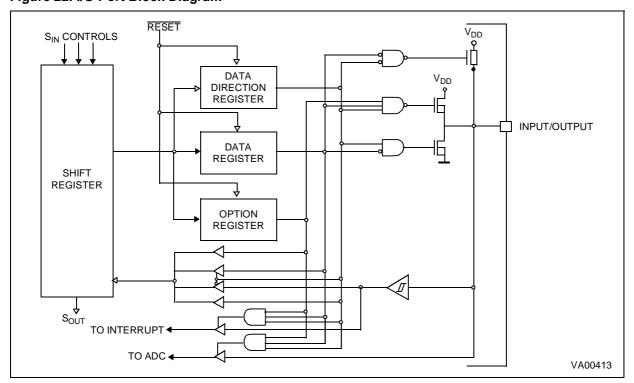

#### **4.1 I/O PORTS**

The MCU features Input/Output lines which may be individually programmed as any of the following input or output configurations:

- Input without pull-up or interrupt

- Input with pull-up and interrupt

- Input with pull-up, but without interrupt

- Analog input

- Push-pull output

- Open drain output

The lines are organised as bytewise Ports.

Each port is associated with 3 registers in Data space. Each bit of these registers is associated with a particular line (for instance, bits 0 of Port A Data, Direction and Option registers are associated with the PA0 line of Port A).

The DATA registers (DRx), are used to read the voltage level values of the lines which have been configured as inputs, or to write the logic value of the signal to be output on the lines configured as outputs. The port data registers can be read to get the effective logic levels of the pins, but they can

be also written by user software, in conjunction with the related option registers, to select the different input mode options.

Single-bit operations on I/O registers are possible but care is necessary because reading in input mode is done from I/O pins while writing will directly affect the Port data register causing an undesired change of the input configuration.

The Data Direction registers (DDRx) allow the data direction (input or output) of each pin to be set.

The Option registers (ORx) are used to select the different port options available both in input and in output mode.

All I/O registers can be read or written to just as any other RAM location in Data space, so no extra RAM cells are needed for port data storage and manipulation. During MCU initialization, all I/O registers are cleared and the input mode with pull-ups and no interrupt generation is selected for all the pins, thus avoiding pin conflicts.

Figure 22. I/O Port Block Diagram

## I/O PORTS (Cont'd)

### 4.1.1 Operating Modes

Each pin may be individually programmed as input or output with various configurations.

This is achieved by writing the relevant bit in the Data (DR), Data Direction (DDR) and Option registers (OR). Table 1 illustrates the various port configurations which can be selected by user software.

## 4.1.1.1 Input Options

Pull-up, High Impedance Option. All input lines can be individually programmed with or without an internal pull-up by programming the OR and DR registers accordingly. If the pull-up option is not selected, the input pin will be in the high-impedance state.

## 4.1.1.2 Interrupt Options

All input lines can be individually connected by software to the interrupt system by programming the OR and DR registers accordingly. The interrupt trigger modes (falling edge, rising edge and low level) can be configured by software as described in the Interrupt Chapter for each port.

## 4.1.1.3 Analog Input Options

Some pins can be configured as analog inputs by programming the OR and DR registers accordingly. These analog inputs are connected to the onchip 8-bit Analog to Digital Converter. *ONLY ONE* pin should be programmed as an analog input at any time, since by selecting more than one input simultaneously their pins will be effectively shorted.

Table 10. I/O Port Option Selection

| DDR | OR | DR | Mode   | Option                                              |  |  |  |

|-----|----|----|--------|-----------------------------------------------------|--|--|--|

| 0   | 0  | 0  | Input  | With pull-up, no interrupt                          |  |  |  |

| 0   | 0  | 1  | Input  | Input No pull-up, no interrupt                      |  |  |  |

| 0   | 1  | 0  | Input  | Input With pull-up and with interrupt               |  |  |  |

| 0   | 1  | 1  | Input  | Input Analog input (when available)                 |  |  |  |

| 1   | 0  | Х  | Output | Output Open-drain output (20mA sink when available) |  |  |  |

| 1   | 1  | Х  | Output | Push-pull output (20mA sink when available)         |  |  |  |

**Note:** X = Don't care

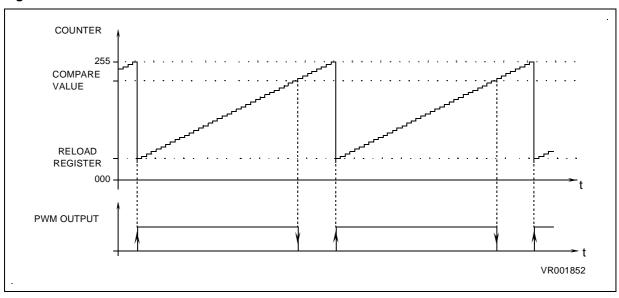

# AUTO-RELOAD TIMER (Cont'd)

It should be noted that the reload values will also affect the value and the resolution of the duty cycle of PWM output signal. To obtain a signal on ARTI-Mout, the contents of the ARCP register must be greater than the contents of the ARRC register.

The maximum available resolution for the ARTI-Mout duty cycle is:

Resolution = 1/[255-(ARRC)]

Where ARRC is the content of the Reload/Capture register. The compare value loaded in the Compare Register, ARCP, must be in the range from (ARRC) to 255.

The ARTC counter is initialized by writing to the ARRC register and by then setting the TCLD (Timer Load) and the TEN (Timer Clock Enable) bits in the Mode Control register, ARMC.

Enabling and selection of the clock source is controlled by the CC0, CC1, SL0 and SL1 bits in the Status Control Register, ARSC1. The prescaler division ratio is selected by the PS0, PS1 and PS2 bits in the ARSC1 register.

In Auto-reload Mode, any of the three available clock sources can be selected: Internal Clock, Internal Clock divided by 3 or the clock signal present on the ARTIMin pin.

Figure 28. Auto-reload Timer PWM Function

# **INSTRUCTION SET (Cont'd)**

Conditional Branch. The branch instructions achieve a branch in the program when the selected condition is met.

Bit Manipulation Instructions. These instructions can handle any bit in data space memory. One group either sets or clears. The other group (see Conditional Branch) performs the bit test branch operations.

Control Instructions. The control instructions control the MCU operations during program execution.

Jump and Call. These two instructions are used to perform long (12-bit) jumps or subroutines call inside the whole program space.

**Table 20. Conditional Branch Instructions**

| Instruction   | Branch If | Putos | Cycles | Flags |   |

|---------------|-----------|-------|--------|-------|---|

| instruction   | Dianon II | Bytes |        | Z     | С |

| JRC e         | C = 1     | 1     | 2      | *     | * |

| JRNC e        | C = 0     | 1     | 2      | *     | * |

| JRZ e         | Z = 1     | 1     | 2      | *     | * |

| JRNZ e        | Z = 0     | 1     | 2      | *     | * |

| JRR b, rr, ee | Bit = 0   | 3     | 5      | *     | Δ |

| JRS b, rr, ee | Bit = 1   | 3     | 5      | *     | Δ |

#### Notes:

- 3-bit address

- 5 bit signed displacement in the range -15 to +16<F128M>

- ee. 8 bit signed displacement in the range -126 to +129

- rr. Data space register

- Affected. The tested bit is shifted into carry. Δ.

- Not Affected

**Table 21. Bit Manipulation Instructions**

| Instruction  | Addressing Mode | Bytes | Cycles | Fla | igs |

|--------------|-----------------|-------|--------|-----|-----|

| ilistruction |                 | bytes | Cycles | Z   | С   |

| SET b,rr     | Bit Direct      | 2     | 4      | *   | *   |

| RES b,rr     | Bit Direct      | 2     | 4      | *   | *   |

- Notes: b. 3-bit address;

- Data space register;

\* . Not<M> Affected

**Table 22. Control Instructions**

| Instruction | Addressing Made | Duttee | Cycles | Flags |   |

|-------------|-----------------|--------|--------|-------|---|

| instruction | Addressing Mode | Bytes  |        | Z     | С |

| NOP         | Inherent        | 1      | 2      | *     | * |

| RET         | Inherent        | 1      | 2      | *     | * |

| RETI        | Inherent        | 1      | 2      | Δ     | Δ |

| STOP (1)    | Inherent        | 1      | 2      | *     | * |

| WAIT        | Inherent        | 1      | 2      | *     | * |

## Notes:

- This instruction is deactivated<N>and a WAIT is automatically executed instead of a STOP if the watchdog function is selected.

- Affected

- Not Affected

Table 23. Jump & Call Instructions

| Instruction | Addressing Mede | Bytes Cyc | Cycles | Flags |   |

|-------------|-----------------|-----------|--------|-------|---|

|             | Addressing Mode |           | Cycles | Z     | С |

| CALL abc    | Extended        | 2         | 4      | *     | * |

| JP abc      | Extended        | 2         | 4      | *     | * |

abc. 12-bit address;

. Not Affected

Opcode Map Summary. The following table contains an opcode map for the instructions used by the ST6

| LOW                                     | Ė  |      | T ' |           |    |           |    | Contain   |   |           |            |   |           |       |    |           |      |   |           | LOW       |

|-----------------------------------------|----|------|-----|-----------|----|-----------|----|-----------|---|-----------|------------|---|-----------|-------|----|-----------|------|---|-----------|-----------|

| Н                                       |    | 0000 |     | 1<br>0001 |    | 2<br>0010 |    | 3<br>0011 |   | 4<br>0100 | )          |   | 5<br>0101 |       |    | 6<br>0110 | ,    |   | 7<br>0111 | Н         |

| _                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  | JRR       | 2 |           | JRZ        |   |           |       | 2  | ,         | JRC  | 4 | LD        | _         |

| 0<br>0000                               |    | е    |     | abc       |    | е         |    | b0,rr,ee  |   | е         |            |   | #         |       |    | е         |      |   | a,(x)     | 0<br>0000 |

| 0000                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  | bt        | 1 |           | pcr        |   |           |       | 1  |           | prc  | 1 | ind       | 0000      |

|                                         | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  | JRS       | 2 |           | JRZ        | 4 |           | INC   | 2  |           | JRC  | 4 | LDI       |           |

| 1<br>0001                               |    | е    |     | abc       |    | е         |    | b0,rr,ee  |   | е         |            |   | х         |       |    | е         |      |   | a,nn      | 1<br>0001 |

| 0001                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  | bt        | 1 |           | pcr        | 1 |           | sd    | 1  |           | prc  | 2 | imm       | 0001      |

|                                         | 2  | JRNZ |     | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        |   |           |       | 2  |           | JRC  | 4 | CP        |           |

| 2                                       |    | е    |     | abc       |    | е         |    | b4,rr,ee  |   | е         |            |   | #         |       |    | е         |      |   | a,(x)     | 2         |

| 0010                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  |           | 1 |           | pcr        |   |           |       | 1  |           | prc  | 1 | ind       | 0010      |

|                                         | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  |           | _ |           | JRZ        | 4 |           | LD    | 2  |           | JRC  | 4 | CPI       |           |

| 3                                       | -  | e    | ١.  | abc       | _  | е         | ľ  | b4,rr,ee  | e |           | 0          | • | а,х       |       | _  | е         |      | • | a,nn      | 3         |

| 0011                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 2  |           |   |           | pcr        | 1 | u,x       | sd    | 1  | Ü         | prc  | 2 | imm       | 0011      |

|                                         | 2  | JRNZ | _   | CALL      | -  | JRNC      | _  |           | _ |           | JRZ        | _ |           | Su    | 2  |           | JRC  | 4 | ADD       |           |

| 4                                       | _  | e    | 4   | abc       | _  |           | 3  |           | 2 |           | JKZ        |   | #         |       | _  |           | JAC  | 4 |           | 4         |

| 0100                                    | ,  |      | _   |           | ,  | е         | ١, | b2,rr,ee  | , | е         |            |   | #         |       | ,  | е         |      | , | a,(x)     | 0100      |

|                                         | 1  | pcr  | _   | ext       | _  | pcr       | _  |           |   |           | pcr        | _ |           | INIO  | 1  |           | prc  |   | ind       |           |

| 5                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        | 4 |           | INC   | 2  |           | JRC  | 4 | ADDI      | 5         |

| 0101                                    |    | е    | _   | abc       |    | е         | _  | b2,rr,ee  |   | е         |            |   | У         |       | ١. | е         |      | _ | a,nn      | 0101      |

|                                         | 1  | pcr  | _   | ext       | _  | pcr       | 3  |           |   |           | pcr        | 1 |           | sd    | 1  |           | prc  | 2 | imm       |           |

| 6                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        |   |           |       | 2  |           | JRC  | 4 | INC       | 6         |

| 0110                                    |    | е    |     | abc       |    | е         |    | b6,rr,ee  |   | е         |            |   | #         |       |    | е         |      |   | (x)       | 0110      |

|                                         | 1  | pcr  |     | ext       |    | pcr       | _  |           |   |           | pcr        |   |           |       | 1  |           | prc  | 1 | ind       |           |

| 7                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  | JRS       | 2 |           | JRZ        | 4 |           | LD    | 2  |           | JRC  |   |           | 7         |

| 0111                                    |    | е    |     | abc       |    | е         |    | b6,rr,ee  |   | е         |            |   | a,y       |       |    | е         |      |   | #         | 0111      |

| • • • • • • • • • • • • • • • • • • • • | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  | bt        | 1 |           | pcr        | 1 |           | sd    | 1  |           | prc  |   |           | 0111      |

| _                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  | JRR       | 2 |           | JRZ        |   |           |       | 2  | ,         | JRC  | 4 | LD        | _         |

| 8<br>1000                               |    | е    |     | abc       |    | е         |    | b1,rr,ee  |   | е         |            |   | #         |       |    | е         |      |   | (x),a     | 8<br>1000 |

| 1000                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  | bt        | 1 |           | pcr        |   |           |       | 1  |           | prc  | 1 | ind       | 1000      |

|                                         | 2  | RNZ  | 4   | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        | 4 |           | INC   | 2  |           | JRC  |   |           |           |

| 9                                       |    | е    |     | abc       |    | е         |    | b1,rr,ee  |   | е         |            |   | V         |       |    | е         |      |   | #         | 9         |

| 1001                                    | 1  | pcr  | 2   | ext       | 1  |           | 3  | bt        | 1 |           | pcr        | 1 |           | sd    | 1  |           | prc  |   |           | 1001      |

|                                         | 2  | JRNZ | _   | CALL      |    |           | _  | JRR       |   |           | JRZ        |   |           |       | 2  |           | JRC  | 4 | AND       |           |

| Α                                       | -  | e    |     | abc       | -  | е         | ľ  | b5,rr,ee  | _ | е         | J. 1.      |   | #         |       | -  | е         |      | · | a,(x)     | Α         |

| 1010                                    | 1  | pcr  | 2   | ext       | 1  | pcr       | 3  |           | 1 | Ü         | pcr        |   | "         |       | 1  | Ü         | prc  | 1 | ind       | 1010      |

|                                         | 2  | JRNZ |     | CALL      | 2  | JRNC      | 5  |           |   |           | JRZ        | 4 |           | LD    | 2  |           | JRC  | 4 | ANDI      |           |

| В                                       | _  | e    | 4   | abc       | _  | e         | ٦  | b5,rr,ee  | _ | е         | JINZ       | 7 | a,v       | LD    | _  | е         | JING | 4 | a,nn      | В         |

| 1011                                    | 1  | -    | 2   |           | 4  |           | 3  |           | 1 | C         | nor        | 1 | a,v       | cd    | 1  | 6         | nro  | 2 | imm       | 1011      |

|                                         | 2  | pcr  |     | ext       |    | pcr       | 5  |           | _ |           | pcr<br>JRZ | - |           | sd    | 2  |           | prc  | 4 |           |           |

| С                                       | _  | JRNZ | 4   | CALL      | 2  | JRNC      | э  |           | 2 |           | JKZ        |   | ,,        |       | 2  |           | JRC  | 4 | SUB       | С         |

| 1100                                    | ١. | е    |     | abc .     | ١. | е         | _  | b3,rr,ee  |   | е         |            |   | #         |       | ١. | е         |      |   | a,(x)     | 1100      |

|                                         | 1  | pcr  | _   | ext       |    | pcr       | 3  |           |   |           | pcr        | Ļ |           | 11.10 | 1  |           | prc  | 1 | ind       |           |

| D                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        | 4 |           | INC   | 2  |           | JRC  | 4 | SUBI      | D         |

| 1101                                    |    | е    |     | abc       |    | е         |    | b3,rr,ee  |   | е         |            |   | W         |       |    | е         |      |   | a,nn      | 1101      |

|                                         | 1  | pcr  | _   | ext       | _  | pcr       | 3  |           | _ |           | pcr        | 1 |           | sd    | 1  |           | prc  | 2 | imm       |           |

| E                                       | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  |           | 2 |           | JRZ        |   |           |       | 2  |           | JRC  | 4 | DEC       | E         |

| 1110                                    |    | е    |     | abc       |    | е         |    | b7,rr,ee  |   | е         |            |   | #         |       |    | е         |      |   | (x)       | 1110      |

|                                         | 1  | pcr  | 2   | ext       | 1  | pcr       |    |           | 1 |           | pcr        | L |           |       | 1  |           | prc  | 1 | ind       |           |

|                                         | 2  | JRNZ | 4   | CALL      | 2  | JRNC      | 5  | JRS       | 2 |           | JRZ        | 4 |           | LD    | 2  |           | JRC  |   |           |           |

| F<br>1111                               |    | е    |     | abc       |    | е         |    | b7,rr,ee  |   | е         |            |   | a,w       |       |    | е         |      |   | #         | F<br>1111 |

| 1111                                    | 1  | pcr  | 2   | ext       | 1  | pcr       |    | bt        | 1 |           | pcr        | 1 |           | sd    | 1  |           | prc  |   |           | ''''      |

|                                         | •  | -    | •   |           |    |           | •  |           | _ |           | •          | • |           |       | •  |           | •    |   |           |           |

# Abbreviations for Addressing Modes: Legend:

Direct Short Direct dir sd imm Immediate inh Inherent Extended ext b.d Bit Direct Bit Test bt

Indicates Illegal Instructions 5 Bit Displacement 3 Bit Address е b 1 byte dataspace address 1 byte immediate data 12 bit address rr nn abc

8 bit Displacement

ee

Cycle Mnemonic JRC Operand prc Bytes Addressing Mode

**Program Counter Relative**

pcr ind Indirect

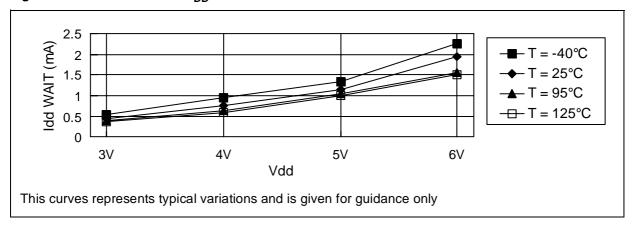

Figure 42. Idd WAIT versus  $V_{DD}$  at 8 Mhz for OTP devices

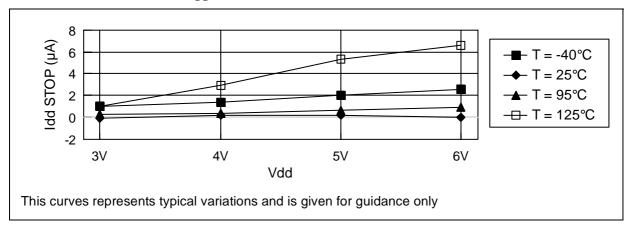

Figure 43. Idd STOP versus  $V_{DD}$  for OTP devices

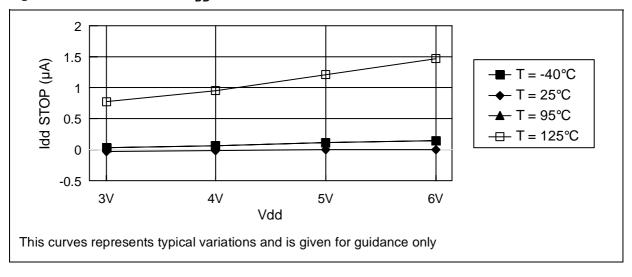

Figure 44. Idd STOP versus  $V_{DD}$  for ROM devices

Notes:

| Customer:             |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|

| Address:              |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

|                       |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Contact:              |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Phone:                |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Reference:            |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

|                       |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| STMicroelectronic     | s references:                        |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Device:               |                                      | [] ST6255C (4 KB)<br>[] ST62P55C (4 KB)                                                                                       | [] ST6265B (4 KB)<br>[] ST62P65C (4 KB) |  |  |  |  |  |  |  |

| Package:              |                                      | [ ] Dual in Line Plastic<br>[ ] Small Outline Plastic with conditioning<br>[ ] Shrink Small Outline Plastic with conditioning |                                         |  |  |  |  |  |  |  |

| Conditioning option   |                                      | [] Standard (Tube)                                                                                                            | [] Tape & Reel                          |  |  |  |  |  |  |  |

| Temperature Range     |                                      | [] 0°C to + 70°C                                                                                                              | [] - 40°C to + 85°C                     |  |  |  |  |  |  |  |

| . Simporaturo italigi | <b>~.</b>                            | [] - 40°C to + 125°C                                                                                                          | [] 40 0 10 1 00 0                       |  |  |  |  |  |  |  |

| Marking:              |                                      | PSO28 (8 char. m                                                                                                              | max):                                   |  |  |  |  |  |  |  |

| Authorized characte   | ers are letters, digi                | \$\$OP28 (11 char<br>ts, '.', '-', '/' and spaces only.                                                                       | r. max):                                |  |  |  |  |  |  |  |

| Oscillator Safeguar   |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| Oscillator Selection  | :                                    | [] Quartz crystal / Ceramic<br>[] RC network                                                                                  | resonator                               |  |  |  |  |  |  |  |

| Reset Delay           |                                      | [] 32768 cycle delay                                                                                                          | [] 2048 cycle delay                     |  |  |  |  |  |  |  |

| Watchdog Selection    | ı.                                   | [] Software Activation                                                                                                        | [] Hardware Activation                  |  |  |  |  |  |  |  |

| PB1:PB0 pull-up at    |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| PB3:PB2 pull-up at    |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| External STOP Mod     |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| Readout Protection    | · <b>Γ</b> Δ <b>ς</b> Τ              | ROM:                                                                                                                          |                                         |  |  |  |  |  |  |  |

| readout i lototilli   | . 1731                               | [] Enabled                                                                                                                    | [ ] Disabled                            |  |  |  |  |  |  |  |

|                       | ROM:                                 | • •                                                                                                                           | [15.646.64                              |  |  |  |  |  |  |  |

|                       | T COIVI                              | [] Enabled:                                                                                                                   |                                         |  |  |  |  |  |  |  |

|                       |                                      | = =                                                                                                                           | by STMicroelectronics                   |  |  |  |  |  |  |  |

|                       | [] Fuse can be blown by the customer |                                                                                                                               |                                         |  |  |  |  |  |  |  |

|                       |                                      | [] Disabled                                                                                                                   |                                         |  |  |  |  |  |  |  |

| Low Voltage Detect    | or*:                                 | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| NMI pull-up*:         |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| ADC Synchro*:         |                                      | [] Enabled                                                                                                                    | [] Disabled                             |  |  |  |  |  |  |  |

| *except on ST6265     | В                                    |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Comments:             |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Oscillator Frequenc   | y in the application                 | n:                                                                                                                            |                                         |  |  |  |  |  |  |  |

| Supply Operating R    | ange in the applic                   | ation:                                                                                                                        |                                         |  |  |  |  |  |  |  |

| Maria                 |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |

| Date:                 |                                      |                                                                                                                               |                                         |  |  |  |  |  |  |  |