# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 833MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR, SDRAM                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8541pxapf |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Selectable hardware-enforced coherency

- Selectable clock source (SYSCLK or independent PCI\_CLK)

- Power management

- Fully static 1.2-V CMOS design with 3.3- and 2.5-V I/O

- Supports power save modes: doze, nap, and sleep

- Employs dynamic power management

- Selectable clock source (sysclk or independent PCI\_CLK)

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter specific events

- Supports 64 reference events that can be counted on any of the 8 counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- IEEE Std 1149.1<sup>TM</sup>-compatible, JTAG boundary scan

- 783 FC-PBGA package

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8541E. The MPC8541E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

Electrical Characteristics

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

| Table 1. Absolute Maximum Ratings <sup>1</sup> | Table | 1. Absolu | ute Maximum | Ratings <sup>1</sup> | l |

|------------------------------------------------|-------|-----------|-------------|----------------------|---|

|------------------------------------------------|-------|-----------|-------------|----------------------|---|

| Cha                                                                | aracteristic                                                                                                    | Symbol            | Max Value                                    | Unit | Notes |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------|------|-------|

| Core supply voltage                                                |                                                                                                                 | V <sub>DD</sub>   | -0.3 to 1.32<br>0.3 to 1.43 (for 1 GHz only) | V    |       |

| PLL supply voltage                                                 |                                                                                                                 | AV <sub>DD</sub>  | -0.3 to 1.32<br>0.3 to 1.43 (for 1 GHz only) | V    |       |

| DDR DRAM I/O voltage                                               |                                                                                                                 | GV <sub>DD</sub>  | -0.3 to 3.63                                 | V    |       |

| Three-speed Ethernet I/O, I                                        | /III management voltage                                                                                         | LV <sub>DD</sub>  | -0.3 to 3.63<br>-0.3 to 2.75                 | V    |       |

| CPM, PCI, local bus, DUAR<br>management, I <sup>2</sup> C, and JTA | T, system control and power<br>G I/O voltage                                                                    | OV <sub>DD</sub>  | -0.3 to 3.63                                 | V    | 3     |

| Input voltage                                                      | DDR DRAM signals                                                                                                | MV <sub>IN</sub>  | -0.3 to (GV <sub>DD</sub> + 0.3)             | V    | 2, 5  |

|                                                                    | DDR DRAM reference                                                                                              | MV <sub>REF</sub> | -0.3 to (GV <sub>DD</sub> + 0.3)             | V    | 2, 5  |

|                                                                    | Three-speed Ethernet signals                                                                                    | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3)             | V    | 4, 5  |

|                                                                    | CPM, Local bus, DUART,<br>SYSCLK, system control and<br>power management, I <sup>2</sup> C, and<br>JTAG signals | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)1            | V    | 5     |

|                                                                    | PCI                                                                                                             | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3)             | V    | 6     |

| Storage temperature range                                          | ·                                                                                                               | T <sub>STG</sub>  | -55 to 150                                   | °C   |       |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. **Caution:** LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

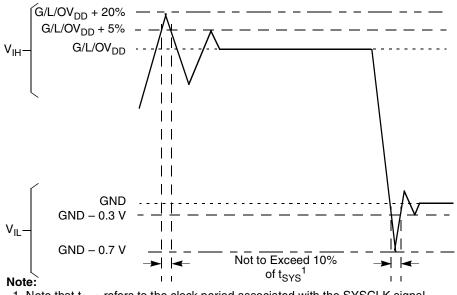

- 5. (M,L,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

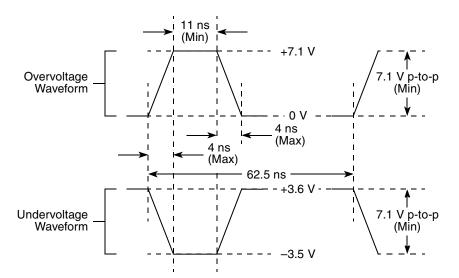

- 6. OV<sub>IN</sub> on the PCI interface may overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 3.

## 2.1.2 Power Sequencing

The MPC8541Erequires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1.  $V_{DD}$ ,  $AV_{DDn}$

- 2. GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub> (I/O supplies)

#### **Electrical Characteristics**

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8541E.

1. Note that  $t_{SYS}$  refers to the clock period associated with the SYSCLK signal.

### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The MPC8541E core voltage must always be provided at nominal 1.2 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied MV<sub>REF</sub> signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8541E for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI interface for 3.3-V Signaling

## 2.1.4 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable Output<br>Impedance (Ω) | Supply<br>Voltage            | Notes |

|---------------------------------------|--------------------------------------|------------------------------|-------|

| Local bus interface utilities signals | 25                                   | OV <sub>DD</sub> = 3.3 V     | 1     |

|                                       | 42 (default)                         |                              |       |

| PCI signals                           | 25                                   |                              | 2     |

|                                       | 42 (default)                         |                              |       |

| DDR signal                            | 20                                   | GV <sub>DD</sub> = 2.5 V     |       |

| TSEC/10/100 signals                   | 42                                   | LV <sub>DD</sub> = 2.5/3.3 V |       |

| DUART, system control, I2C, JTAG      | 42                                   | OV <sub>DD</sub> = 3.3 V     |       |

### Table 3. Output Drive Capability

#### Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

# 6.2 DDR SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

## 6.2.1 DDR SDRAM Input AC Timing Specifications

Table 13 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 13. DDR SDRAM Input AC Timing Specifications

At recommended operating conditions with  $\text{GV}_{\text{DD}}$  of 2.5 V  $\pm$  5%.

| Parameter                                                 | Symbol              | Min                      | Мах                      | Unit | Notes |

|-----------------------------------------------------------|---------------------|--------------------------|--------------------------|------|-------|

| AC input low voltage                                      | V <sub>IL</sub>     | —                        | MV <sub>REF</sub> – 0.31 | V    | —     |

| AC input high voltage                                     | V <sub>IH</sub>     | MV <sub>REF</sub> + 0.31 | GV <sub>DD</sub> + 0.3   | V    | —     |

| MDQS—MDQ/MECC input skew per<br>byte<br>For DDR = 333 MHz | <sup>t</sup> DISKEW | _                        | 750                      | ps   | 1     |

| For DDR <u>&lt;</u> 266 MHz                               |                     |                          | 1125                     |      |       |

Note:

1. Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n + {0...7}] if 0 <= n <= 7) or ECC (MECC[{0...7}] if n = 8).

## 6.2.2 DDR SDRAM Output AC Timing Specifications

Table 14 and Table 15 provide the output AC timing specifications and measurement conditions for the DDR SDRAM interface.

## Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode

At recommended operating conditions with  $\text{GV}_{\text{DD}}$  of 2.5 V  $\pm$  5%.

| Parameter                                                                  | Symbol <sup>1</sup> | Min                     | Max               | Unit | Notes |

|----------------------------------------------------------------------------|---------------------|-------------------------|-------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                | <sup>t</sup> мск    | 6                       | 10                | ns   | 2     |

| Skew between any MCK to ADDR/CMD<br>333 MHz<br>266 MHz<br>200 MHz          | t <sub>aoskew</sub> | -1000<br>-1100<br>-1200 | 200<br>300<br>400 | ps   | 3     |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz | t <sub>DDKHAS</sub> | 2.8<br>3.45<br>4.6      | _                 | ns   | 4     |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz  | t <sub>DDKHAX</sub> | 2.0<br>2.65<br>3.8      | _                 | ns   | 4     |

| MCS(n) output setup with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz   | <sup>t</sup> DDKHCS | 2.8<br>3.45<br>4.6      | _                 | ns   | 4     |

# 8.2 GMII, MII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

## 8.2.2 GMII Transmit AC Timing Specifications

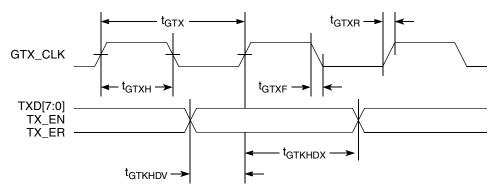

Table 20 provides the GMII transmit AC timing specifications.

### Table 20. GMII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                               | Symbol <sup>1</sup>                                               | Min | Тур | Max | Unit |

|---------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period                              | t <sub>GTX</sub>                                                  | _   | 8.0 | _   | ns   |

| GTX_CLK duty cycle                                | t <sub>GTXH</sub> /t <sub>GTX</sub>                               | 40  | —   | 60  | %    |

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | <sup>t</sup> GTKHDV                                               | 2.5 | —   | -   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX                                               | 0.5 | —   | 5.0 | ns   |

| GTX_CLK data clock rise and fall times            | t <sub>GTXR</sub> <sup>3</sup> , t <sub>GTXR</sub> <sup>2,4</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

- 3. Guaranteed by characterization.

- 4. Guaranteed by design.

Figure 7 shows the GMII transmit AC timing diagram.

Figure 7. GMII Transmit AC Timing Diagram

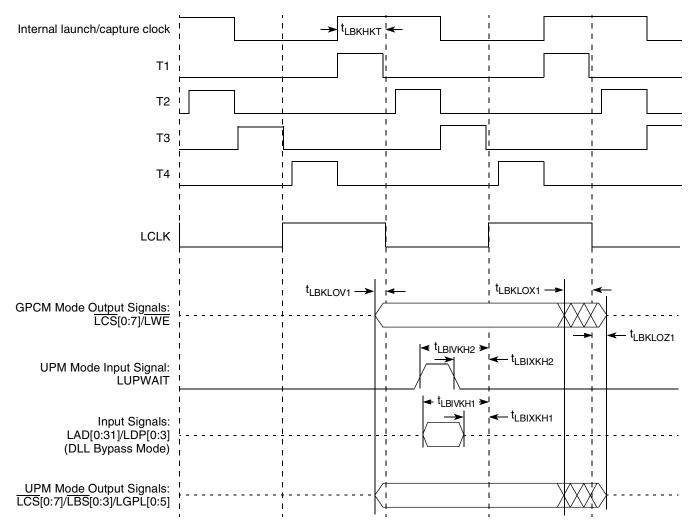

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Bypass Mode)

### JTAG

# 11 JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8541E.

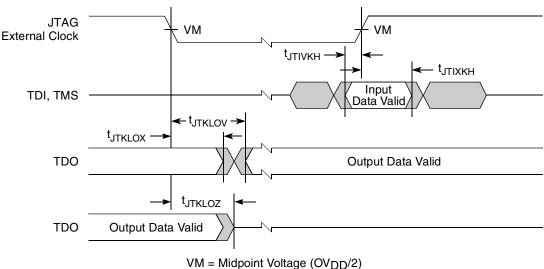

Table 38 provides the JTAG AC timing specifications as defined in Figure 32 through Figure 35.

## Table 38. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V                          | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —     |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       | —        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 | _        | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | _        | _        | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

### Notes:

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 31). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the t<sub>t</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 35 provides the test access port timing diagram.

Figure 35. Test Access Port Timing Diagram

# 12 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface of the MPC8541E.

# 12.1 I<sup>2</sup>C DC Electrical Characteristics

Table 39 provides the DC electrical characteristics for the  $I^2C$  interface of the MPC8541E.

## Table 39. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                                                                                               | Symbol              | Min                   | Max                                | Unit | Notes |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                | V <sub>IH</sub>     | $0.7 \times OV_{DD}$  | OV <sub>DD</sub> + 0.3             | V    | —     |

| Input low voltage level                                                                                 | V <sub>IL</sub>     | -0.3                  | $0.3 \times \text{OV}_{\text{DD}}$ | V    | —     |

| Low level output voltage                                                                                | V <sub>OL</sub>     | 0                     | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Output fall time from $V_{IH}(min)$ to $V_{IL}(max)$ with a bus capacitance from 10 to 400 pF           | <sup>t</sup> I2KLKV | $20 + 0.1 \times C_B$ | 250                                | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                                      | t <sub>I2KHKL</sub> | 0                     | 50                                 | ns   | 3     |

| Input current each I/O pin (input voltage is between 0.1 $\times$ OV_{DD} and 0.9 $\times$ OV_{DD}(max) | lı                  | -10                   | 10                                 | μA   | 4     |

| Capacitance for each I/O pin                                                                            | CI                  | —                     | 10                                 | pF   | —     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. Refer to the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for information on the digital filter used.

4. I/O pins obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

Package and Pin Listings

# 14.3 Pinout Listings

Table 43 provides the pin-out listing for the MPC8541E, 783 FC-PBGA package.

## Table 43. MPC8541E Pinout Listing

| Signal                            | Package Pin Number                                                                                                                                                                              | Pin Type | Power<br>Supply  | Notes |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|                                   | PCI1 and PCI2 (one 64-bit or two 32-bit)                                                                                                                                                        |          | ·                |       |

| PCI1_AD[63:32],<br>PCI2_AD[31:0]  | AA14, AB14, AC14, AD14, AE14, AF14, AG14, AH14,<br>V15, W15, Y15, AA15, AB15, AC15, AD15, AG15,<br>AH15, V16, W16, AB16, AC16, AD16, AE16, AF16,<br>V17, W17, Y17, AA17, AB17, AE17, AF17, AF18 | I/O      | OV <sub>DD</sub> | 17    |

| PCI1_AD[31:0]                     | AH6, AD7, AE7, AH7, AB8, AC8, AF8, AG8, AD9,<br>AE9, AF9, AG9, AH9, W10, Y10, AA10, AE11, AF11,<br>AG11, AH11, V12, W12, Y12, AB12, AD12, AE12,<br>AG12, AH12, V13, Y13, AB13, AC13             | I/O      | OV <sub>DD</sub> | 17    |

| PCI_C_BE64[7:4]<br>PCI2_C_BE[3:0] | AG13, AH13, V14, W14                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 17    |

| PCI_C_BE64[3:0]<br>PCI1_C_BE[3:0] | AH8, AB10, AD11, AC12                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17    |

| PCI1_PAR                          | AA11                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | —     |

| PCI1_PAR64/PCI2_PAR               | Y14                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —     |

| PCI1_FRAME                        | AC10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_TRDY                         | AG10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_IRDY                         | AD10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_STOP                         | V11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_DEVSEL                       | AH10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_IDSEL                        | AA9                                                                                                                                                                                             | I        | OV <sub>DD</sub> | —     |

| PCI1_REQ64/PCI2_FRAME             | AE13                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL            | AD13                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_PERR                         | W11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_SERR                         | Y11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4  |

| PCI1_REQ[0]                       | AF5                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —     |

| PCI1_REQ[1:4]                     | AF3, AE4, AG4, AE5                                                                                                                                                                              | Ι        | OV <sub>DD</sub> | —     |

| PCI1_GNT[0]                       | AE6                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —     |

| PCI1_GNT[1:4]                     | AG5, AH5, AF6, AG6                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9  |

| PCI1_CLK                          | AH25                                                                                                                                                                                            | ļ        | OV <sub>DD</sub> | —     |

| PCI2_CLK                          | AH27                                                                                                                                                                                            | Ι        | OV <sub>DD</sub> | —     |

| PCI2_GNT[0]                       | AC18                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | —     |

## Table 43. MPC8541E Pinout Listing (continued)

| Signal        | Package Pin Number                                                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PCI2_GNT[1:4] | AD18, AE18, AE19, AD19                                                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9  |

| PCI2_IDSEL    | AC22                                                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | _     |

| PCI2_IRDY     | AD20                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI2_PERR     | AC20                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI2_REQ[0]   | AD21                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _     |

| PCI2_REQ[1:4] | AE21, AD22, AE22, AC23                                                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | —     |

| PCI2_SERR     | AE20                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2,4   |

| PCI2_STOP     | AC21                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI2_TRDY     | AC19                                                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

|               | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                                                       |          |                  | 1     |

| MDQ[0:63]     | M26, L27, L22, K24, M24, M23, K27, K26, K22, J28,<br>F26, E27, J26, J23, H26, G26, C26, E25, C24, E23,<br>D26, C25, A24, D23, B23, F22, J21, G21, G22, D22,<br>H21, E21, N18, J18, D18, L17, M18, L18, C18, A18,<br>K17, K16, C16, B16, G17, L16, A16, L15, G15, E15,<br>C14, K13, C15, D15, E14, D14, D13, E13, D12, A11,<br>F13, H13, A13, B12 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7]     | N20, M20, L19, E19, C21, A21, G19, A19                                                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | _     |

| MDM[0:8]      | L24, H28, F24, L21, E18, E16, G14, B13, M19                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | _     |

| MDQS[0:8]     | L26, J25, D25, A22, H18, F16, F14, C13, C20                                                                                                                                                                                                                                                                                                      | I/O      | GV <sub>DD</sub> | _     |

| MBA[0:1]      | B18, B19                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —     |

| MA[0:14]      | N19, B21, F21, K21, M21, C23, A23, B24, H23, G24,<br>K19, B25, D27, J14, J13                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | —     |

| MWE           | D17                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | _     |

| MRAS          | F17                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | _     |

| MCAS          | J16                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | _     |

| MCS[0:3]      | H16, G16, J15, H15                                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _     |

| MCKE[0:1]     | E26, E28                                                                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | 11    |

| MCK[0:5]      | J20, H25, A15, D20, F28, K14                                                                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MCK[0:5]      | F20, G27, B15, E20, F27, L14                                                                                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MSYNC_IN      | M28                                                                                                                                                                                                                                                                                                                                              | I        | GV <sub>DD</sub> | 22    |

| MSYNC_OUT     | N28                                                                                                                                                                                                                                                                                                                                              | 0        | GV <sub>DD</sub> | 22    |

|               | Local Bus Controller Interface                                                                                                                                                                                                                                                                                                                   |          |                  |       |

| LA[27]        | U18                                                                                                                                                                                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9  |

Package and Pin Listings

| Signal                            | Package Pin Number                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| LA[28:31]                         | T18, T19, T20, T21                                                                                                                                                               | 0        | OV <sub>DD</sub> | 5, 7, 9 |

| LAD[0:31]                         | AD26, AD27, AD28, AC26, AC27, AC28, AA22,<br>AA23, AA26, Y21, Y22, Y26, W20, W22, W26, V19,<br>T22, R24, R23, R22, R21, R18, P26, P25, P20, P19,<br>P18, N22, N23, N24, N25, N26 | I/O      | OV <sub>DD</sub> | _       |

| LALE                              | V21                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                             | V20                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 9       |

| LCKE                              | U23                                                                                                                                                                              | 0        | OV <sub>DD</sub> | _       |

| LCLK[0:2]                         | U27, U28, V18                                                                                                                                                                    | 0        | OV <sub>DD</sub> | _       |

| LCS[0:4]                          | Y27, Y28, W27, W28, R27                                                                                                                                                          | 0        | OV <sub>DD</sub> | _       |

| LCS5/DMA_DREQ2                    | R28                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2                    | P27                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2                   | P28                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 1       |

| LDP[0:3]                          | AA27, AA28, T26, P21                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _       |

| LGPL0/LSDA10                      | U19                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE                       | U22                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS                  | V28                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS                      | V27                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/<br>LPBSE      | V23                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 21      |

| LGPL5                             | V22                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9    |

| LSYNC_IN                          | T27                                                                                                                                                                              | I        | OV <sub>DD</sub> | _       |

| LSYNC_OUT                         | T28                                                                                                                                                                              | 0        | OV <sub>DD</sub> | _       |

| LWE[0:1]/LSDDQM[0:1]/<br>LBS[0:1] | AB28, AB27                                                                                                                                                                       | 0        | OV <sub>DD</sub> | 1, 5, 9 |

| LWE[2:3]/LSDDQM[2:3]/<br>LBS[2:3] | T23, P24                                                                                                                                                                         | 0        | OV <sub>DD</sub> | 1, 5, 9 |

|                                   | DMA                                                                                                                                                                              |          |                  |         |

| DMA_DREQ[0:1]                     | H5, G4                                                                                                                                                                           | I        | OV <sub>DD</sub> | _       |

| DMA_DACK[0:1]                     | H6, G5                                                                                                                                                                           | 0        | OV <sub>DD</sub> | —       |

| DMA_DDONE[0:1]                    | H7, G6                                                                                                                                                                           | 0        | OV <sub>DD</sub> | -       |

|                                   | Programmable Interrupt Controller                                                                                                                                                |          |                  |         |

| MCP                               | AG17                                                                                                                                                                             | I        | OV <sub>DD</sub> | _       |

| UDE                               | AG16                                                                                                                                                                             | I        | OV <sub>DD</sub> | _       |

|                                   | 1                                                                                                                                                                                |          | I                |         |

## Table 43. MPC8541E Pinout Listing (continued)

# 15 Clocking

This section describes the PLL configuration of the MPC8541E. Note that the platform clock is identical to the CCB clock.

# 15.1 Clock Ranges

Table 44 provides the clocking specifications for the processor core and Table 44 provides the clocking specifications for the memory bus.

|                                     | Maximum Processor Core Frequency |     |         |     |         |     |         |     |          |      |      |         |

|-------------------------------------|----------------------------------|-----|---------|-----|---------|-----|---------|-----|----------|------|------|---------|

| Characteristic                      | 533 MHz                          |     | 600 MHz |     | 667 MHz |     | 833 MHz |     | 1000 MHz |      | Unit | Notes   |

|                                     | Min                              | Max | Min     | Max | Min     | Max | Min     | Max | Min      | Max  |      |         |

| e500 core<br>processor<br>frequency | 400                              | 533 | 400     | 600 | 400     | 667 | 400     | 833 | 400      | 1000 | MHz  | 1, 2, 3 |

**Table 44. Processor Core Clocking Specifications**

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

2.) The minimum e500 core frequency is based on the minimum platform frequency of 200 MHz.

3. 1000 MHz frequency supports only a 1.3 V core.

## Table 45. Memory Bus Clocking Specifications

| Characteristic       | Maximum Processor Core<br>Frequency<br>533, 600, 667, 883, 1000 MHz |     |     | Notes   |  |

|----------------------|---------------------------------------------------------------------|-----|-----|---------|--|

|                      | Min                                                                 | Max |     |         |  |

| Memory bus frequency | 100                                                                 | 166 | MHz | 1, 2, 3 |  |

Notes:

- 1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR data rate, hence, half of the platform clock frequency.

- 3. 1000 MHz frequency supports only a 1.3 V core.

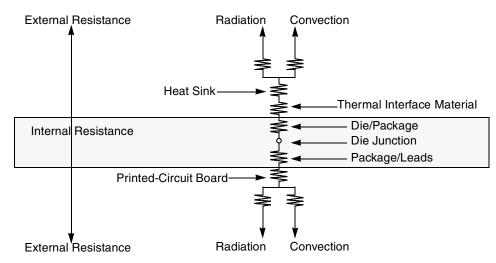

# 16.2.2 Internal Package Conduction Resistance

For the packaging technology, shown in Table 49, the intrinsic internal conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-board thermal resistance

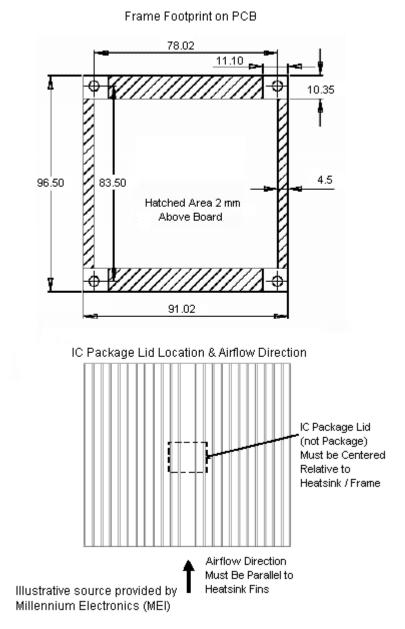

Figure 44 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

(Note the internal versus external package resistance)

## Figure 44. Package with Heat Sink Mounted to a Printed-Circuit Board

The heat sink removes most of the heat from the device. Heat generated on the active side of the chip is conducted through the silicon and through the lid, then through the heat sink attach material (or thermal interface material), and finally to the heat sink. The junction-to-case thermal resistance is low enough that the heat sink attach material and heat sink thermal resistance are the dominant terms.

## 16.2.3 Thermal Interface Materials

A thermal interface material is required at the package-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 45 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. The bare joint results in a thermal resistance approximately six times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 41). Therefore, the synthetic grease offers the best thermal performance, especially at the low interface pressure.

When removing the heat sink for re-work, it is preferable to slide the heat sink off slowly until the thermal interface material loses its grip. If the support fixture around the package prevents sliding off the heat sink,

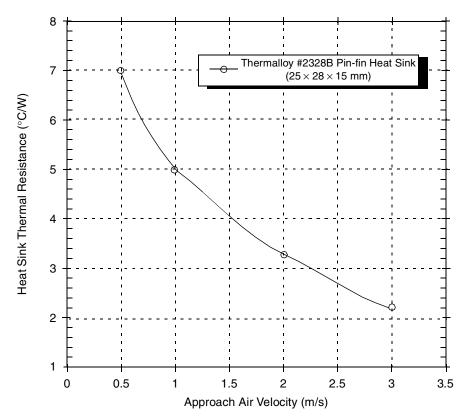

Figure 46. Thermalloy #2328B Heat Sink-to-Ambient Thermal Resistance Versus Airflow Velocity

## 16.2.4.2 Case 2

Every system application has different conditions that the thermal management solution must solve. As an alternate example, assume that the air reaching the component is 85 °C with an approach velocity of 1 m/sec. For a maximum junction temperature of 105 °C at 8 W, the total thermal resistance of junction to case thermal resistance plus thermal interface material plus heat sink thermal resistance must be less than 2.5 °C/W. The value of the junction to case thermal resistance in Table 49 includes the thermal interface resistance of a thin layer of thermal grease as documented in footnote 4 of the table. Assuming that the heat sink is flat enough to allow a thin layer of grease or phase change material, then the heat sink must be less than 1.5 °C/W.

Millennium Electronics (MEI) has tooled a heat sink MTHERM-1051 for this requirement assuming a compactPCI environment at 1 m/sec and a heat sink height of 12 mm. The MEI solution is illustrated in Figure 47 and Figure 48. This design has several significant advantages:

- The heat sink is clipped to a plastic frame attached to the application board with screws or plastic inserts at the corners away from the primary signal routing areas.

- The heat sink clip is designed to apply the force holding the heat sink in place directly above the die at a maximum force of less than 10 lbs.

- For applications with significant vibration requirements, silicone damping material can be applied between the heat sink and plastic frame.

#### Thermal

The spring mounting should be designed to apply the force only directly above the die. By localizing the force, rocking of the heat sink is minimized. One suggested mounting method attaches a plastic fence to the board to provide the structure on which the heat sink spring clips. The plastic fence also provides the opportunity to minimize the holes in the printed-circuit board and to locate them at the corners of the package. Figure 47 and provide exploded views of the plastic fence, heat sink, and spring clip.

Figure 47. Exploded Views (1) of a Heat Sink Attachment using a Plastic Fence

# NP

### System Design Information

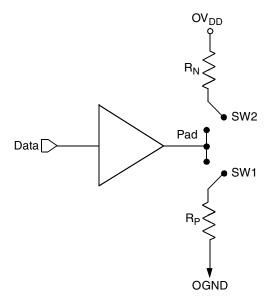

When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 50. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = 1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

Table 50 summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART, Control, Configuration, Power<br>Management | PCI       | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------|-----------|-----------|-------------------|------|

| R <sub>N</sub> | 43 Target                                                               | 25 Target | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 43 Target                                                               | 25 Target | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | NA                                                                      | NA        | NA        | Z <sub>DIFF</sub> | Ω    |

| Table 50 | . Impedance | Characteristics |

|----------|-------------|-----------------|

|----------|-------------|-----------------|

**Note:** Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

## 17.8.1 Termination of Unused Signals

If the JTAG interface and COP header are not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 52. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- Tie TCK to  $OV_{DD}$  through a 10 k $\Omega$  resistor. This prevents TCK from changing state and reading incorrect data into the device.

- No connection is required for TDI, TMS, or TDO.

# **18 Document Revision History**

Table 51 provides a revision history for this hardware specification.

| Rev. No. | Date      | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4.2      | 1/2008    | Added "Note: Rise/Fall Time on CPM Input Pins" and following note text to Section 10.2, "CPM AC Timing Specifications."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 4.1      | 07/2007   | Inserted Figure 3, ""Maximum AC Waveforms on PCI interface for 3.3-V Signaling."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 4        | 12/2006   | Updated Section 2.1.2, "Power Sequencing."<br>Updated back page information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 3.2      | 11/2006   | Updated Section 2.1.2, "Power Sequencing."<br>Replaced Section 17.8, "JTAG Configuration Signals."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 3.1      | 10/2005   | Table 4: Added footnote 2 about junction temperature.Table 4: Added max. power values for 1000 MHz core frequency.Removed Figure 3, "Maximum AC Waveforms on PCI Interface for 3.3-V Signaling."Table 30: Modified note to tLBKSKEW from 8 to 9Table 30: Changed tLBKHOZ1 and tLBKHOV2 values.Table 30: Added note 3 to tLBKHOV1.Table 30 and Table 31: Modified note 3.Table 31: Added note 3 to tLBKLOV1.Table 31: Added note 3 to tLBKHKT, tLBKLOV1, tLBKLOV2, tLBKLOV3, tLBKLOZ1, and tLBKLOZ2.Figure 21: Changed Input Signals: LAD[0:31]/LDP[0:3].Table 43: Modified note for signal CLK_OUT.Table 43: PCI1_CLK and PCI2_CLK changed from I/O to I.Table 52: Added column for Encryption Acceleration. |  |  |  |  |

| 3        | 8/29/2005 | Table 4: Modified max. power values.         Table 43: Modified notes for signals TSEC1_TXD[3:0], TSEC2_TXD[3:0], TRIG_OUT/READY,         MSRCID4, and MDVAL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 2        | 8/2005    | Previous revision's history listed incorrect cross references. Table 2 is now correctly listed as<br>Table 27 and Table 31 is now listed as Table 31.<br>Table 7: Added note 2.<br>Table 14: Modified min and max values for t <sub>DDKHMP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 1        | 6/2005    | Table 27: Changed LV <sub>dd</sub> to OV <sub>dd</sub> for the supply voltage Ethernet management interface.Table 4: Modified footnote 4 and changed typical power for the 1000MHz core frequency.Table 31: Corrected symbols for body rows 9–15, effectively changing them from a high state to a low state.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 0        | 6/2005    | Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

Device Nomenclature

# **19 Device Nomenclature**

Ordering information for the parts fully covered by this specification document is provided in Section 19.1, "Nomenclature of Parts Fully Addressed by this Document."

# **19.1** Nomenclature of Parts Fully Addressed by this Document

Table 52 provides the Freescale part numbering nomenclature for the MPC8541E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn |                                         | t                                      | рр                                          | aa                                                                            | а                                         | r                              |

|-----------------|------|-----------------------------------------|----------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|

| Product<br>Code |      | Encryption<br>Acceleration              | Temperature<br>Range <sup>1</sup>      | Package <sup>2</sup>                        | Processor<br>Frequency <sup>3</sup>                                           | Platform<br>Frequency                     | Revision<br>Level <sup>4</sup> |

| MPC             |      | Blank = not<br>included<br>E = included | Blank = 0 to 105°C<br>C = −40 to 105°C | PX = FC-PBGA<br>VT = FC-PBGA<br>(lead free) | AJ = 533 MHz<br>AK = 600 MHz<br>AL = 667 MHz<br>AP = 833 MHz<br>AQ = 1000 MHZ | D = 266 MHz<br>E = 300 MHz<br>F = 333 MHz |                                |

### Table 52. Part Numbering Nomenclature

Notes:

1. For Temperature Range=C, Processor Frequency is limited to 667 MHz with a Platform Frequency selector of 333 MHz, Processor Frequency is limited to 533 MHz with a Platform Frequency selector of 266 MHz.

2. See Section 14, "Package and Pin Listings," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

4. Contact you local Freescale field applications engineer (FAE).