# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 667MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR, SDRAM                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8541vtalf |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Overview

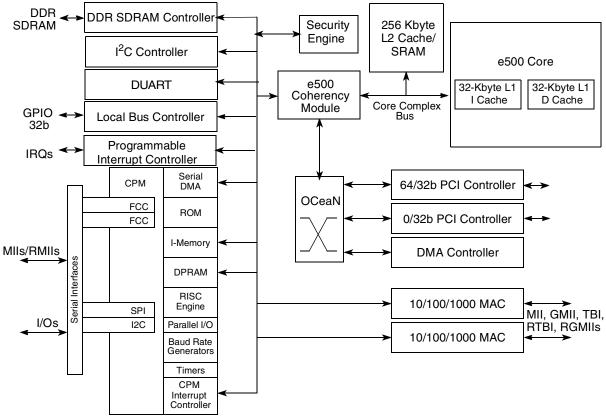

The following section provides a high-level overview of the MPC8541E features. Figure 1 shows the major functional units within the MPC8541E.

Figure 1. MPC8541E Block Diagram

## 1.1 Key Features

The following lists an overview of the MPC8541E feature set.

- Embedded e500 Book E-compatible core

- High-performance, 32-bit Book E-enhanced core that implements the PowerPC architecture

- Dual-issue superscalar, 7-stage pipeline design

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection

- Lockable L1 caches—entire cache or on a per-line basis

- Separate locking for instructions and data

- Single-precision floating-point operations

- Memory management unit especially designed for embedded applications

- Enhanced hardware and software debug support

- Dynamic power management

- Performance monitor facility

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90 percent of their value before the voltage rails on the current step reach ten percent of theirs.

#### NOTE

If the items on line 2 must precede items on line 1, please ensure that the delay does not exceed 500 ms and the power sequence is not done greater than once per day in production environment.

#### NOTE

From a system standpoint, if the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os on the MPC8541E may drive a logic one or zero during power-up.

## 2.1.3 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8541E. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                                   |                                                                                                                 | Symbol              | Recommended Value                                   | Unit     |                                                |   |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------------------|----------|------------------------------------------------|---|

| Core supply voltage PLL supply voltage                           |                                                                                                                 | Core supply voltage |                                                     | $V_{DD}$ | 1.2 V ± 60 mV<br>1.3 V± 50 mV (for 1 GHz only) | V |

|                                                                  |                                                                                                                 | AV <sub>DD</sub>    | $1.2 V \pm 60 mV$<br>1.3 V ± 50 mV (for 1 GHz only) | V        |                                                |   |

| DDR DRAM I/O voltage                                             |                                                                                                                 | GV <sub>DD</sub>    | 2.5 V ± 125 mV                                      | V        |                                                |   |

| Three-speed Ethernet I/O voltage                                 |                                                                                                                 | LV <sub>DD</sub>    | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                    | V        |                                                |   |

| PCI, local bus, DUART, s<br>I <sup>2</sup> C, and JTAG I/O volta | system control and power management,<br>ge                                                                      | $OV_{DD}$           | 3.3 V ± 165 mV                                      | V        |                                                |   |

| Input voltage                                                    | DDR DRAM signals                                                                                                | MV <sub>IN</sub>    | GND to GV <sub>DD</sub>                             | V        |                                                |   |

|                                                                  | DDR DRAM reference                                                                                              | MV <sub>REF</sub>   | GND to GV <sub>DD</sub>                             | V        |                                                |   |

|                                                                  | Three-speed Ethernet signals                                                                                    | LV <sub>IN</sub>    | GND to LV <sub>DD</sub>                             | V        |                                                |   |

|                                                                  | PCI, local bus, DUART,<br>SYSCLK, system control and<br>power management, I <sup>2</sup> C, and<br>JTAG signals | OV <sub>IN</sub>    | GND to OV <sub>DD</sub>                             | V        |                                                |   |

| Die-junction Temperatu                                           | re                                                                                                              | Тj                  | 0 to 105                                            | °C       |                                                |   |

#### **Table 2. Recommended Operating Conditions**

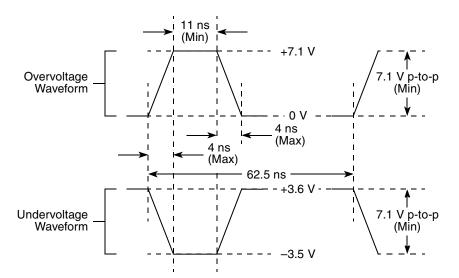

Figure 3 shows the undershoot and overshoot voltage of the PCI interface of the MPC8541E for the 3.3-V signals, respectively.

Figure 3. Maximum AC Waveforms on PCI interface for 3.3-V Signaling

### 2.1.4 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable Output<br>Impedance (Ω) | Supply<br>Voltage            | Notes |

|---------------------------------------|--------------------------------------|------------------------------|-------|

| Local bus interface utilities signals | 25                                   | OV <sub>DD</sub> = 3.3 V     | 1     |

|                                       | 42 (default)                         |                              |       |

| PCI signals                           | 25                                   |                              | 2     |

|                                       | 42 (default)                         |                              |       |

| DDR signal                            | 20                                   | GV <sub>DD</sub> = 2.5 V     |       |

| TSEC/10/100 signals                   | 42                                   | LV <sub>DD</sub> = 2.5/3.3 V |       |

| DUART, system control, I2C, JTAG      | 42                                   | OV <sub>DD</sub> = 3.3 V     |       |

#### Table 3. Output Drive Capability

#### Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

#### DDR SDRAM

#### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                                | Мах                              | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------|----------------------------------|------|-------|

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz            | <sup>t</sup> оокнсх                         | 2.0<br>2.65<br>3.8                 | _                                | ns   | 4     |

| MCK to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                                       | <sup>t</sup> ddкнмн                         | -0.9<br>-1.1<br>-1.2               | 0.3<br>0.5<br>0.6                | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz | <sup>t</sup> ddkhds,<br><sup>t</sup> ddklds | 900<br>900<br>1200                 | _                                | ps   | 6     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 900<br>900<br>1200                 | _                                | ps   | 6     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.5 \times t_{\text{MCK}} - 0.9$ | $-0.5 	imes t_{\text{MCK}}$ +0.3 | ns   | 7     |

| MDQS epilogue end                                                                  | t <sub>DDKLME</sub>                         | -0.9                               | 0.3                              | ns   | 7     |

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/ $\overline{MCK}$  referenced measurements are made from the crossing of the two signals  $\pm 0.1$  V.

- In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the Clock Control Register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the Clock Control register is set to adjust the memory clocks by 1/2 applied cycle. The MCSx pins are separated from the ADDR/CMD (address and command) bus in the HW spec. This was separated because the MCSx pins typically have different loadings than the rest of the address and command bus, even though they have the same timings.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). In the source synchronous mode, MDQS can launch later than MCK by 0.3 ns at the maximum. However, MCK may launch later than MDQS by as much as 0.9 ns. t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this typically is set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the *MPC8555E PowerQUICC™ III Integrated Communications Processor Reference Manual* for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8541E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8541E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

## 7.2 DUART AC Electrical Specifications

Table 17 provides the AC timing parameters for the DUART interface of the MPC8541E.

| Parameter         | Value                          | Unit | Notes |

|-------------------|--------------------------------|------|-------|

| Minimum baud rate | f <sub>CCB_CLK</sub> / 1048576 | baud | 3     |

| Maximum baud rate | f <sub>CCB_CLK</sub> / 16      | baud | 1, 3  |

| Oversample rate   | 16                             | —    | 2, 3  |

#### Table 17. DUART AC Timing Specifications

#### Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

- The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

- 3. Guaranteed by design.

## 8 Ethernet: Three-Speed, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

## 8.1 Three-Speed Ethernet Controller (TSEC) (10/100/1000 Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all GMII (gigabit media independent interface), the MII (media independent interface), TBI (ten-bit interface), RGMII (reduced gigabit media independent interface), and RTBI (reduced ten-bit interface) signals except MDIO (management data input/output) and MDC (management data clock). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII and TBI interfaces can be operated at 3.3 V or 2.5 V. Whether the GMII, MII, or TBI interface is operated at 3.3 or 2.5 V, the timing is compliant with the IEEE 802.3 standard. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 TSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 18 and Table 19. The potential applied to the input of a GMII, MII, TBI, RGMII, or RTBI receiver may exceed the potential of the receiver's power supply (for example, a GMII driver powered from a 3.6-V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5-V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

### 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.3.1 MII Transmit AC Timing Specifications

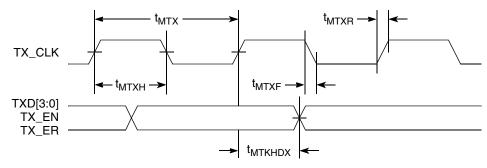

Table 22 provides the MII transmit AC timing specifications.

#### Table 22. MII Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD} of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                                  | Min | Тур | Мах | Unit |

|-------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> 2                                   | _   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                                     | _   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH/</sub> t <sub>MTX</sub>                  | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                                  | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise and fall time            | t <sub>MTXR</sub> , t <sub>MTXF</sub> <sup>2,3</sup> | 1.0 | _   | 4.0 | ns   |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

- 3. Guaranteed by design.

Figure 10 shows the MII transmit AC timing diagram.

Figure 10. MII Transmit AC Timing Diagram

## 8.2.5 RGMII and RTBI AC Timing Specifications

Table 26 presents the RGMII and RTBI AC timing specifications.

#### Table 26. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 2.5 V ± 5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>                                                 | Min  | Тур | Мах  | Unit |

|-----------------------------------------------------|---------------------------------------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)          | tskrgt <sup>5</sup>                                                 | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>                                                  | 1.0  |     | 2.8  | ns   |

| Clock cycle duration <sup>3</sup>                   | t <sub>RGT</sub> 6                                                  | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub> 6                               | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> 6                               | 40   | 50  | 60   | %    |

| Rise and fall times                                 | t <sub>RGTR</sub> <sup>6,7</sup> , t <sub>RGTF</sub> <sup>6,7</sup> | —    | —   | 0.75 | ns   |

Notes:

Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

The RGMII specification requires that PC board designer add 1.5 ns or greater in trace delay to the RX\_CLK in order to meet this specification. However, as stated above, this device functions with only 1.0 ns of delay.

3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5. Guaranteed by characterization.

6. Guaranteed by design.

7. Signal timings are measured at 0.5 and 2.0 V voltage levels.

| Parameter          | Parameter Symbol |                        | Conditions              |      | Мах | Unit |

|--------------------|------------------|------------------------|-------------------------|------|-----|------|

| Input high current | I <sub>IH</sub>  | LV <sub>DD</sub> = Max | $V_{IN}^{1} = 2.1 V$    | _    | 40  | μA   |

| Input low current  | IIL              | LV <sub>DD</sub> = Max | V <sub>IN</sub> = 0.5 V | -600 | —   | μA   |

| Table 27. MII Management DC Electrical Character | istics (continued) |

|--------------------------------------------------|--------------------|

|                                                  |                    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

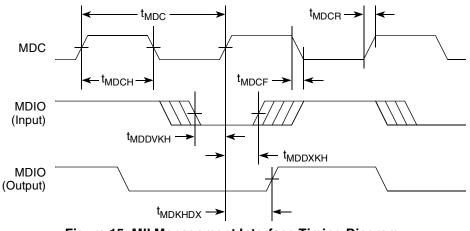

### 8.3.2 MII Management AC Electrical Specifications

Table 28 provides the MII management AC timing specifications.

#### Table 28. MII Management AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> is 3.3 V  $\pm$  5%.

| Parameter/Condition        | Symbol <sup>1</sup> | Min   | Тур | Мах                             | Unit | Notes |

|----------------------------|---------------------|-------|-----|---------------------------------|------|-------|

| MDC frequency              | f <sub>MDC</sub>    | 0.893 | —   | 10.4                            | MHz  | 2     |

| MDC period                 | t <sub>MDC</sub>    | 96    | —   | 1120                            | ns   |       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32    | —   | _                               | ns   |       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> |       |     | 2*[1/(f <sub>ccb_clk</sub> /8)] | ns   | 3     |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | 10    | —   | 2*[1/(f <sub>ccb_clk</sub> /8)] | ns   | 3     |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5     | —   | —                               | ns   |       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0     | —   | —                               | ns   |       |

| MDC rise time              | t <sub>MDCR</sub>   | _     | —   | 10                              | ns   |       |

| MDC fall time              | t <sub>MDHF</sub>   |       |     | 10                              | ns   |       |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. This parameter is dependent on the system clock speed (that is, for a system clock of 267 MHz, the delay is 70 ns and for a system clock of 333 MHz, the delay is 58 ns).

3. This parameter is dependent on the CCB clock speed (that is, for a CCB clock of 267 MHz, the delay is 60 ns and for a CCB clock of 333 MHz, the delay is 48 ns).

4. Guaranteed by design.

Local Bus

Figure 15 shows the MII management AC timing diagram.

Figure 15. MII Management Interface Timing Diagram

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8541E.

## 9.1 Local Bus DC Electrical Characteristics

Table 29 provides the DC electrical characteristics for the local bus interface.

| Parameter                 | Symbol          | Test Condition                                     | Min                   | Мах                    | Unit |

|---------------------------|-----------------|----------------------------------------------------|-----------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                      | 2                     | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | V <sub>OUT</sub> ≤ V <sub>OL</sub> (max)           | -0.3                  | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}$ <sup>1</sup> = 0 V or $V_{IN}$ = $V_{DD}$ | —                     | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | $OV_{DD} = min,$<br>$I_{OH} = -2mA$                | OV <sub>DD</sub> -0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min, I <sub>OL</sub> = 2mA      | _                     | 0.2                    | V    |

### Table 29. Local Bus DC Electrical Characteristics

#### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

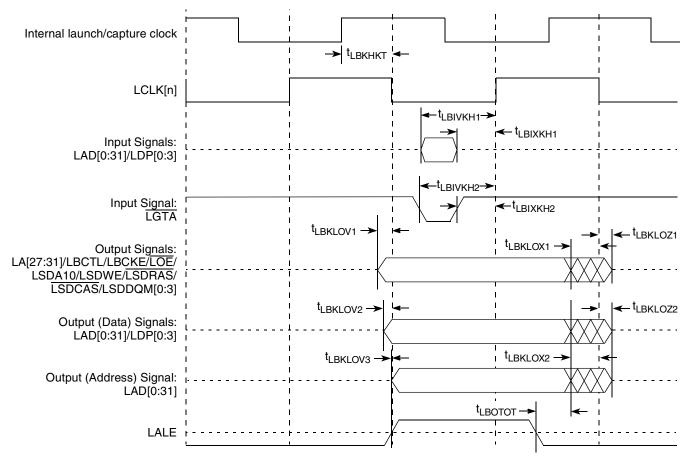

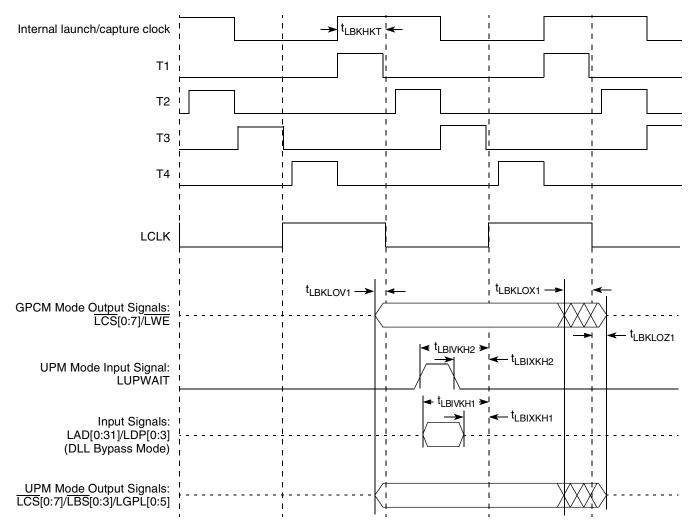

Table 30. Local Bus General Timing Parameters—DLL Enabled (continued)

| Parameter                                    | Configuration <sup>7</sup>           | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|----------------------------------------------|--------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for | $\overline{LWE[0:1]} = 00$           | t <sub>LBKHOZ2</sub> | _   | 2.8 | ns   | 5, 9  |

| LAD/LDP                                      | $\overline{LWE[0:1]} = 11$ (default) |                      |     | 4.2 |      |       |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for DLL enabled mode.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN for DLL enabled to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- The value of t<sub>LBOTOT</sub> is defined as the sum of 1/2 or 1 ccb\_clk cycle as programmed by LBCR[AHD], and the number of local bus buffer delays used as programmed at power-on reset with configuration pins LWE[0:1].

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at OV<sub>DD</sub>/2.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

Table 31 describes the general timing parameters of the local bus interface of the MPC8541E with the DLL bypassed.

| Table 31. Local Bus General Timing Parameters—DLL Bypa | issed |

|--------------------------------------------------------|-------|

|--------------------------------------------------------|-------|

| Parameter                                                             | Configuration <sup>7</sup>           | Symbol <sup>1</sup>  | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|--------------------------------------|----------------------|------|-----|------|-------|

| Local bus cycle time                                                  | _                                    | t <sub>LBK</sub>     | 6.0  |     | ns   | 2     |

| Internal launch/capture clock to LCLK delay                           | _                                    | t <sub>LBKHKT</sub>  | 1.8  | 3.4 | ns   | 8     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | _                                    | t <sub>LBKSKEW</sub> | _    | 150 | ps   | 7, 9  |

| Input setup to local bus clock (except LUPWAIT)                       | _                                    | t <sub>LBIVKH1</sub> | 5.2  | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                | _                                    | t <sub>LBIVKH2</sub> | 5.1  | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                      | _                                    | t <sub>LBIXKH1</sub> | -1.3 | _   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                               | _                                    | t <sub>LBIXKH2</sub> | -0.8 | _   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | _                                    | t <sub>LBOTOT</sub>  | 1.5  | _   | ns   | 6     |

| Local bus clock to output valid (except                               | $\overline{LWE[0:1]} = 00$           | t <sub>LBKLOV1</sub> | _    | 0.5 | ns   | 3     |

| LAD/LDP and LALE)                                                     | LWE[0:1] = 11 (default)              |                      |      | 2.0 |      |       |

| Local bus clock to data valid for LAD/LDP                             | LWE[0:1] = 00                        | t <sub>LBKLOV2</sub> | —    | 0.7 | ns   | 3     |

|                                                                       | $\overline{LWE[0:1]} = 11$ (default) |                      |      | 2.2 |      |       |

Figure 18. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Bypass Mode)

Table 33. CPM Input AC Timing Specifications <sup>1</sup> (continued)

#### Notes:

- 1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

- 2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>FIIVKH</sub> symbolizes the FCC inputs internal timing (FI) with respect to the time the input signals (I) reaching the valid state (V) relative to the reference clock t<sub>FCC</sub> (K) going to the high (H) state or setup time.

- 3. PIO and TIMER inputs and outputs are asynchronous to SYSCLK or any other externally visible clock. PIO/TIMER inputs are internally synchronized to the CPM internal clock. PIO/TIMER outputs should be treated as asynchronous.

| Characteristic                          | Symbol <sup>2</sup> | Min | Мах | Unit |

|-----------------------------------------|---------------------|-----|-----|------|

| FCC outputs—internal clock (NMSI) delay | t <sub>FIKHOX</sub> | 1   | 5.5 | ns   |

| FCC outputs—external clock (NMSI) delay | t <sub>FEKHOX</sub> | 2   | 8   | ns   |

| SPI outputs—internal clock (NMSI) delay | t <sub>NIKHOX</sub> | 0.5 | 10  | ns   |

| SPI outputs—external clock (NMSI) delay | t <sub>NEKHOX</sub> | 2   | 8   | ns   |

| PIO outputs delay                       | t <sub>PIKHOX</sub> | 1   | 11  | ns   |

#### Table 34. CPM Output AC Timing Specifications <sup>1</sup>

#### Notes:

- 1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>FIKHOX</sub> symbolizes the FCC inputs internal timing (FI) for the time t<sub>FCC</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

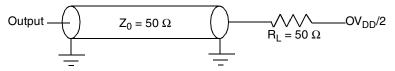

Figure 23 provides the AC test load for the CPM.

Figure 23. CPM AC Test Load

MPC8541E PowerQUICC™ III Integrated Communications Processor Hardware Specification, Rev. 4.2

СРМ

#### JTAG

## 11 JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8541E.

Table 38 provides the JTAG AC timing specifications as defined in Figure 32 through Figure 35.

#### Table 38. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  |       |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       | —        | ns   |       |

| JTAG external clock pulse width measured at 1.4 V                          | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | _     |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   |       |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       | _        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 |          | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> |          |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

#### Notes:

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 31). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the t<sub>ime</sub> data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4. Non-JTAG signal input timing with respect to  $t_{TCLK}$ .

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Package and Pin Listings

## 14.3 Pinout Listings

Table 43 provides the pin-out listing for the MPC8541E, 783 FC-PBGA package.

### Table 43. MPC8541E Pinout Listing

| Signal                            | Package Pin Number                                                                                                                                                                              | Pin Type | Power<br>Supply  | Notes |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|--|

|                                   | PCI1 and PCI2 (one 64-bit or two 32-bit)                                                                                                                                                        |          | ·                |       |  |

| PCI1_AD[63:32],<br>PCI2_AD[31:0]  | AA14, AB14, AC14, AD14, AE14, AF14, AG14, AH14,<br>V15, W15, Y15, AA15, AB15, AC15, AD15, AG15,<br>AH15, V16, W16, AB16, AC16, AD16, AE16, AF16,<br>V17, W17, Y17, AA17, AB17, AE17, AF17, AF18 | I/O      | OV <sub>DD</sub> | 17    |  |

| PCI1_AD[31:0]                     | AH6, AD7, AE7, AH7, AB8, AC8, AF8, AG8, AD9,<br>AE9, AF9, AG9, AH9, W10, Y10, AA10, AE11, AF11,<br>AG11, AH11, V12, W12, Y12, AB12, AD12, AE12,<br>AG12, AH12, V13, Y13, AB13, AC13             | I/O      | OV <sub>DD</sub> | 17    |  |

| PCI_C_BE64[7:4]<br>PCI2_C_BE[3:0] | AG13, AH13, V14, W14                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 17    |  |

| PCI_C_BE64[3:0]<br>PCI1_C_BE[3:0] | AH8, AB10, AD11, AC12                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17    |  |

| PCI1_PAR                          | AA11                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | —     |  |

| PCI1_PAR64/PCI2_PAR               | Y14                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —     |  |

| PCI1_FRAME                        | AC10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_TRDY                         | AG10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_IRDY                         | AD10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_STOP                         | V11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_DEVSEL                       | AH10                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_IDSEL                        | AA9                                                                                                                                                                                             | I        | OV <sub>DD</sub> | —     |  |

| PCI1_REQ64/PCI2_FRAME             | AE13                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 5, 10 |  |

| PCI1_ACK64/PCI2_DEVSEL            | AD13                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_PERR                         | W11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |  |

| PCI1_SERR                         | Y11                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4  |  |

| PCI1_REQ[0]                       | AF5                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —     |  |

| PCI1_REQ[1:4]                     | AF3, AE4, AG4, AE5                                                                                                                                                                              | Ι        | OV <sub>DD</sub> | -     |  |

| PCI1_GNT[0]                       | AE6                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | -     |  |

| PCI1_GNT[1:4]                     | AG5, AH5, AF6, AG6                                                                                                                                                                              | 0        | OV <sub>DD</sub> | 5, 9  |  |

| PCI1_CLK                          | AH25                                                                                                                                                                                            | ļ        | OV <sub>DD</sub> | -     |  |

| PCI2_CLK                          | AH27                                                                                                                                                                                            | Ι        | OV <sub>DD</sub> |       |  |

| PCI2_GNT[0]                       | AC18                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | —     |  |

## 15.2 Platform/System PLL Ratio

The platform clock is the clock that drives the L2 cache, the DDR SDRAM data rate, and the e500 core complex bus (CCB), and is also called the CCB clock. The values are determined by the binary value on LA[28:31] at power up, as shown in Table 46.

There is no default for this PLL ratio; these signals must be pulled to the desired values.

For specifications on the PCI\_CLK, refer to the PCI 2.2 Specification.

| Binary Value of<br>LA[28:31] Signals | Ratio Description                      |

|--------------------------------------|----------------------------------------|

| 0000                                 | 16:1 ratio CCB clock: SYSCLK (PCI bus) |

| 0001                                 | Reserved                               |

| 0010                                 | 2:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0011                                 | 3:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0100                                 | 4:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0101                                 | 5:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0110                                 | 6:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0111                                 | Reserved                               |

| 1000                                 | 8:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1001                                 | 9:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1010                                 | 10:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1011                                 | Reserved                               |

| 1100                                 | 12:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1101                                 | Reserved                               |

| 1110                                 | Reserved                               |

| 1111                                 | Reserved                               |

| Table | 46. | CCB | Clock | Ratio  |

|-------|-----|-----|-------|--------|

| Tuble | -0. | 000 | 01000 | ilulio |

FC-PBGA Package Heat Sink Clip Thermal Interface Material

Printed-Circuit Board

#### Figure 42. Package Exploded Cross-Sectional View with Several Heat Sink Options

The system board designer can choose between several types of heat sinks to place on the MPC8541E. There are several commercially-available heat sinks from the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                                | 603-224-9988 |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                               | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com   | 818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-millennium.com | 408-436-8770 |

| Tyco Electronics<br>Chip Coolers™<br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com               | 800-522-6752 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                      | 603-635-5102 |

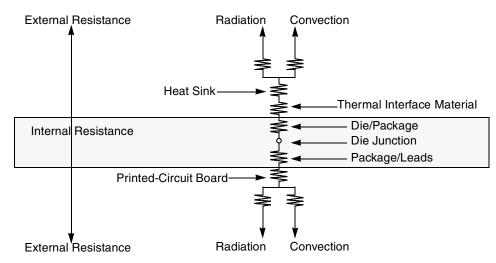

## 16.2.2 Internal Package Conduction Resistance

For the packaging technology, shown in Table 49, the intrinsic internal conduction thermal resistance paths are as follows:

- The die junction-to-case thermal resistance

- The die junction-to-board thermal resistance

Figure 44 depicts the primary heat transfer path for a package with an attached heat sink mounted to a printed-circuit board.

(Note the internal versus external package resistance)

### Figure 44. Package with Heat Sink Mounted to a Printed-Circuit Board

The heat sink removes most of the heat from the device. Heat generated on the active side of the chip is conducted through the silicon and through the lid, then through the heat sink attach material (or thermal interface material), and finally to the heat sink. The junction-to-case thermal resistance is low enough that the heat sink attach material and heat sink thermal resistance are the dominant terms.

## 16.2.3 Thermal Interface Materials

A thermal interface material is required at the package-to-heat sink interface to minimize the thermal contact resistance. For those applications where the heat sink is attached by spring clip mechanism, Figure 45 shows the thermal performance of three thin-sheet thermal-interface materials (silicone, graphite/oil, floroether oil), a bare joint, and a joint with thermal grease as a function of contact pressure. As shown, the performance of these thermal interface materials improves with increasing contact pressure. The use of thermal grease significantly reduces the interface thermal resistance. The bare joint results in a thermal resistance approximately six times greater than the thermal grease joint.

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 41). Therefore, the synthetic grease offers the best thermal performance, especially at the low interface pressure.

When removing the heat sink for re-work, it is preferable to slide the heat sink off slowly until the thermal interface material loses its grip. If the support fixture around the package prevents sliding off the heat sink,

## **18 Document Revision History**

Table 51 provides a revision history for this hardware specification.

| Rev. No. | Date      | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2      | 1/2008    | Added "Note: Rise/Fall Time on CPM Input Pins" and following note text to Section 10.2, "CPM AC Timing Specifications."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.1      | 07/2007   | Inserted Figure 3, ""Maximum AC Waveforms on PCI interface for 3.3-V Signaling."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4        | 12/2006   | Updated Section 2.1.2, "Power Sequencing."<br>Updated back page information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2      | 11/2006   | Updated Section 2.1.2, "Power Sequencing."<br>Replaced Section 17.8, "JTAG Configuration Signals."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1      | 10/2005   | Table 4: Added footnote 2 about junction temperature.Table 4: Added max. power values for 1000 MHz core frequency.Removed Figure 3, "Maximum AC Waveforms on PCI Interface for 3.3-V Signaling."Table 30: Modified note to tLBKSKEW from 8 to 9Table 30: Changed tLBKHOZ1 and tLBKHOV2 values.Table 30: Added note 3 to tLBKHOV1.Table 30 and Table 31: Modified note 3.Table 31: Added note 3 to tLBKLOV1.Table 31: Added note 3 to tLBKHKT, tLBKLOV1, tLBKLOV2, tLBKLOV3, tLBKLOZ1, and tLBKLOZ2.Figure 21: Changed Input Signals: LAD[0:31]/LDP[0:3].Table 43: Modified note for signal CLK_OUT.Table 43: PCI1_CLK and PCI2_CLK changed from I/O to I.Table 52: Added column for Encryption Acceleration. |

| 3        | 8/29/2005 | Table 4: Modified max. power values.         Table 43: Modified notes for signals TSEC1_TXD[3:0], TSEC2_TXD[3:0], TRIG_OUT/READY,         MSRCID4, and MDVAL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2        | 8/2005    | Previous revision's history listed incorrect cross references. Table 2 is now correctly listed as<br>Table 27 and Table 31 is now listed as Table 31.<br>Table 7: Added note 2.<br>Table 14: Modified min and max values for t <sub>DDKHMP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1        | 6/2005    | Table 27: Changed LV <sub>dd</sub> to OV <sub>dd</sub> for the supply voltage Ethernet management interface.Table 4: Modified footnote 4 and changed typical power for the 1000MHz core frequency.Table 31: Corrected symbols for body rows 9–15, effectively changing them from a high state to a low state.                                                                                                                                                                                                                                                                                                                                                                                                |

| 0        | 6/2005    | Initial Release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Device Nomenclature

## **19 Device Nomenclature**

Ordering information for the parts fully covered by this specification document is provided in Section 19.1, "Nomenclature of Parts Fully Addressed by this Document."

## **19.1** Nomenclature of Parts Fully Addressed by this Document

Table 52 provides the Freescale part numbering nomenclature for the MPC8541E. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part numbering scheme also includes an application modifier which may specify special application conditions. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn |                                         | t                                      | рр                                          | aa                                                                            | а                                         | r                              |

|-----------------|------|-----------------------------------------|----------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|

| Product<br>Code |      | Encryption<br>Acceleration              | Temperature<br>Range <sup>1</sup>      | Package <sup>2</sup>                        | Processor<br>Frequency <sup>3</sup>                                           | Platform<br>Frequency                     | Revision<br>Level <sup>4</sup> |

| MPC             |      | Blank = not<br>included<br>E = included | Blank = 0 to 105°C<br>C = −40 to 105°C | PX = FC-PBGA<br>VT = FC-PBGA<br>(lead free) | AJ = 533 MHz<br>AK = 600 MHz<br>AL = 667 MHz<br>AP = 833 MHz<br>AQ = 1000 MHZ | D = 266 MHz<br>E = 300 MHz<br>F = 333 MHz |                                |

#### Table 52. Part Numbering Nomenclature

Notes:

1. For Temperature Range=C, Processor Frequency is limited to 667 MHz with a Platform Frequency selector of 333 MHz, Processor Frequency is limited to 533 MHz with a Platform Frequency selector of 266 MHz.

2. See Section 14, "Package and Pin Listings," for more information on available package types.

Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies.

4. Contact you local Freescale field applications engineer (FAE).