#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| 2 0 0 0 0 0                     |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Active                                                    |

| Core Processor                  | PowerPC e500                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 667MHz                                                    |

| Co-Processors/DSP               | -                                                         |

| RAM Controllers                 | DDR, SDRAM                                                |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10/100/1000Mbps (2)                                       |

| SATA                            | -                                                         |

| USB                             | -                                                         |

| Voltage - I/O                   | 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | Cryptography, Random Number Generator                     |

| Package / Case                  | 783-BBGA, FCBGA                                           |

| Supplier Device Package         | 783-FCPBGA (29x29)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8541pxalf |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

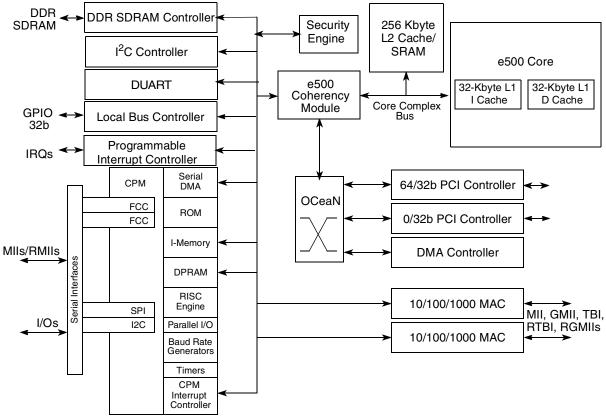

The following section provides a high-level overview of the MPC8541E features. Figure 1 shows the major functional units within the MPC8541E.

Figure 1. MPC8541E Block Diagram

## 1.1 Key Features

The following lists an overview of the MPC8541E feature set.

- Embedded e500 Book E-compatible core

- High-performance, 32-bit Book E-enhanced core that implements the PowerPC architecture

- Dual-issue superscalar, 7-stage pipeline design

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection

- Lockable L1 caches—entire cache or on a per-line basis

- Separate locking for instructions and data

- Single-precision floating-point operations

- Memory management unit especially designed for embedded applications

- Enhanced hardware and software debug support

- Dynamic power management

- Performance monitor facility

- Four global high resolution timers/counters that can generate interrupts

- Supports additional internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs

- Interrupt summary registers allow fast identification of interrupt source

- Two I<sup>2</sup>C controllers (one is contained within the CPM, the other is a stand-alone controller which is not part of the CPM)

- Two-wire interface

- Multiple master support

- Master or slave  $I^2C$  mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the stand-alone I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (RXD, TXD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 166 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Two Three-speed (10/100/1000)Ethernet controllers (TSECs)

- Dual IEEE 802.3, 802.3u, 802.3x, 802.3z AC compliant controllers

- Support for Ethernet physical interfaces:

- 10/100/1000 Mbps IEEE 802.3 GMII

- 10/100 Mbps IEEE 802.3 MII

- 10 Mbps IEEE 802.3 MII

## 4.3 Real Time Clock Timing

Table 8 provides the real time clock (RTC) AC timing specifications.

**Table 8. RTC AC Timing Specifications**

| Parameter/Condition | Symbol            | Min                         | Typical | Max | Unit | Notes |

|---------------------|-------------------|-----------------------------|---------|-----|------|-------|

| RTC clock high time | t <sub>RTCH</sub> | 2 х<br>t <sub>CCB_CLK</sub> | _       | _   | ns   | —     |

| RTC clock low time  | <sup>t</sup> RTCL | 2 х<br><sup>t</sup> ссв_ськ | —       | —   | ns   | _     |

# 5 **RESET Initialization**

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8541E. Table 9 provides the RESET initialization AC timing specifications.

### Table 9. RESET Initialization Timing Specifications

| Parameter/Condition                                                                                     | Min | Мах | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | —   | μs      | —     |

| Minimum assertion time for SRESET                                                                       | 512 | —   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 | _   | μs      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for POR configs (including PLL config) with respect to negation of HRESET               | 2   | —   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

Notes:

1. SYSCLK is identical to the PCI\_CLK signal and is the primary clock input for the MPC8541E. See the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for more details.

## Table 10 provides the PLL and DLL lock times.

#### Table 10. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit       | Notes |

|---------------------|------|---------|------------|-------|

| PLL lock times      | —    | 100     | μs         | _     |

| DLL lock times      | 7680 | 122,880 | CCB Clocks | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the platform (or CCB) clock. A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The CCB clock is determined by the SYSCLK  $\times$  platform PLL ratio.

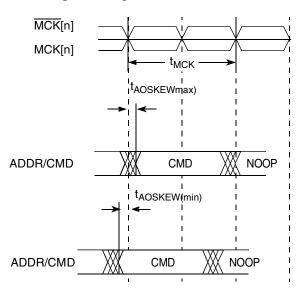

Figure 4 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 4. Timing Diagram for  $t_{\mbox{AOSKEW}}$  Measurement

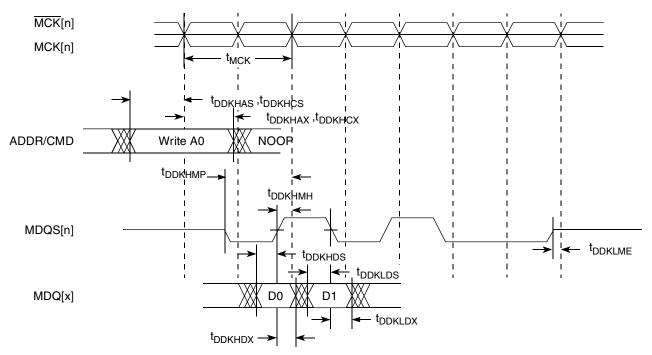

Figure 5 shows the DDR SDRAM output timing diagram for the source synchronous mode.

Figure 5. DDR SDRAM Output Timing Diagram for Source Synchronous Mode

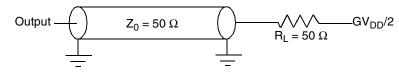

Figure 6 provides the AC test load for the DDR bus.

Figure 6. DDR AC Test Load

Table 15. DDR SDRAM Measurement Conditions

| Symbol           | DDR                        | Unit | Notes |

|------------------|----------------------------|------|-------|

| V <sub>TH</sub>  | MV <sub>REF</sub> ± 0.31 V | V    | 1     |

| V <sub>OUT</sub> | $0.5 	imes GV_{DD}$        | V    | 2     |

Notes:

1. Data input threshold measurement point.

2. Data output measurement point.

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8541E.

## 7.1 DUART DC Electrical Characteristics

Table 16 provides the DC electrical characteristics for the DUART interface of the MPC8541E.

Table 16. DUART DC Electrical Characteristics

| Parameter                 | Symbol          | Test Condition                                     | Min                    | Мах                    | Unit |

|---------------------------|-----------------|----------------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                      | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | $V_{OUT} \le V_{OL}$ (max)                         | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}$ <sup>1</sup> = 0 V or $V_{IN}$ = $V_{DD}$ | _                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | $OV_{DD} = min,$<br>$I_{OH} = -100 \ \mu A$        | OV <sub>DD</sub> - 0.2 | —                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | $OV_{DD}$ = min, $I_{OL}$ = 100 $\mu$ A            | _                      | 0.2                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

## 7.2 DUART AC Electrical Specifications

Table 17 provides the AC timing parameters for the DUART interface of the MPC8541E.

| Parameter         | Value                          | Unit | Notes |  |

|-------------------|--------------------------------|------|-------|--|

| Minimum baud rate | f <sub>CCB_CLK</sub> / 1048576 | baud | 3     |  |

| Maximum baud rate | f <sub>CCB_CLK</sub> / 16      | baud | 1, 3  |  |

| Oversample rate   | 16                             | —    | 2, 3  |  |

## Table 17. DUART AC Timing Specifications

#### Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

- The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

- 3. Guaranteed by design.

# 8 Ethernet: Three-Speed, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

## 8.1 Three-Speed Ethernet Controller (TSEC) (10/100/1000 Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all GMII (gigabit media independent interface), the MII (media independent interface), TBI (ten-bit interface), RGMII (reduced gigabit media independent interface), and RTBI (reduced ten-bit interface) signals except MDIO (management data input/output) and MDC (management data clock). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII and TBI interfaces can be operated at 3.3 V or 2.5 V. Whether the GMII, MII, or TBI interface is operated at 3.3 or 2.5 V, the timing is compliant with the IEEE 802.3 standard. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

## 8.1.1 TSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 18 and Table 19. The potential applied to the input of a GMII, MII, TBI, RGMII, or RTBI receiver may exceed the potential of the receiver's power supply (for example, a GMII driver powered from a 3.6-V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5-V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

# 8.2 GMII, MII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

## 8.2.1 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

## 8.2.2 GMII Transmit AC Timing Specifications

Table 20 provides the GMII transmit AC timing specifications.

### Table 20. GMII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                               | Symbol <sup>1</sup>                                               | Min | Тур | Max | Unit |

|---------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period                              | t <sub>GTX</sub>                                                  | _   | 8.0 | _   | ns   |

| GTX_CLK duty cycle                                | t <sub>GTXH</sub> /t <sub>GTX</sub>                               | 40  | —   | 60  | %    |

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | <sup>t</sup> GTKHDV                                               | 2.5 | —   | -   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX                                               | 0.5 | —   | 5.0 | ns   |

| GTX_CLK data clock rise and fall times            | t <sub>GTXR</sub> <sup>3</sup> , t <sub>GTXR</sub> <sup>2,4</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

- 3. Guaranteed by characterization.

- 4. Guaranteed by design.

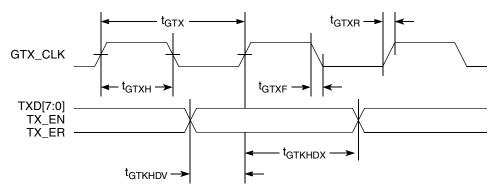

Figure 7 shows the GMII transmit AC timing diagram.

Figure 7. GMII Transmit AC Timing Diagram

## 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

## 8.2.3.1 MII Transmit AC Timing Specifications

Table 22 provides the MII transmit AC timing specifications.

#### Table 22. MII Transmit AC Timing Specifications

At recommended operating conditions with LV\_{DD} of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup>                                  | Min | Тур | Мах | Unit |

|-------------------------------------------------|------------------------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>                        | _   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                                     | _   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH/</sub> t <sub>MTX</sub>                  | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                                  | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise and fall time            | t <sub>MTXR</sub> , t <sub>MTXF</sub> <sup>2,3</sup> | 1.0 | _   | 4.0 | ns   |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

- 3. Guaranteed by design.

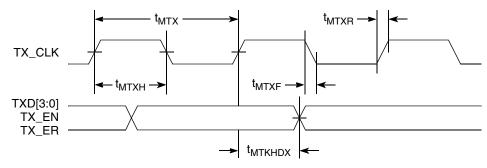

Figure 10 shows the MII transmit AC timing diagram.

Figure 10. MII Transmit AC Timing Diagram

Table 30. Local Bus General Timing Parameters—DLL Enabled (continued)

| Parameter                                    | Configuration <sup>7</sup>           | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|----------------------------------------------|--------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for | $\overline{LWE[0:1]} = 00$           | t <sub>LBKHOZ2</sub> | _   | 2.8 | ns   | 5, 9  |

| LAD/LDP                                      | $\overline{LWE[0:1]} = 11$ (default) |                      |     | 4.2 |      |       |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for DLL enabled mode.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN for DLL enabled to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- The value of t<sub>LBOTOT</sub> is defined as the sum of 1/2 or 1 ccb\_clk cycle as programmed by LBCR[AHD], and the number of local bus buffer delays used as programmed at power-on reset with configuration pins LWE[0:1].

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at OV<sub>DD</sub>/2.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

Table 31 describes the general timing parameters of the local bus interface of the MPC8541E with the DLL bypassed.

| Table 31. Local Bus General Timing Parameters—DLL Bypa | issed |

|--------------------------------------------------------|-------|

|--------------------------------------------------------|-------|

| Parameter                                                             | Configuration <sup>7</sup>           | Symbol <sup>1</sup>  | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|--------------------------------------|----------------------|------|-----|------|-------|

| Local bus cycle time                                                  | _                                    | t <sub>LBK</sub>     | 6.0  | —   | ns   | 2     |

| Internal launch/capture clock to LCLK delay                           | _                                    | t <sub>LBKHKT</sub>  | 1.8  | 3.4 | ns   | 8     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | _                                    | t <sub>LBKSKEW</sub> | _    | 150 | ps   | 7, 9  |

| Input setup to local bus clock (except LUPWAIT)                       | _                                    | t <sub>LBIVKH1</sub> | 5.2  | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                | _                                    | t <sub>LBIVKH2</sub> | 5.1  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                      | _                                    | t <sub>LBIXKH1</sub> | -1.3 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                               | _                                    | t <sub>LBIXKH2</sub> | -0.8 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | _                                    | t <sub>LBOTOT</sub>  | 1.5  | —   | ns   | 6     |

| Local bus clock to output valid (except                               | $\overline{LWE[0:1]} = 00$           | t <sub>LBKLOV1</sub> | _    | 0.5 | ns   | 3     |

| LAD/LDP and LALE)                                                     | $\overline{LWE[0:1]} = 11$ (default) |                      |      | 2.0 |      |       |

| Local bus clock to data valid for LAD/LDP                             | LWE[0:1] = 00                        | t <sub>LBKLOV2</sub> | _    | 0.7 | ns   | 3     |

|                                                                       | $\overline{LWE[0:1]} = 11$ (default) |                      |      | 2.2 |      |       |

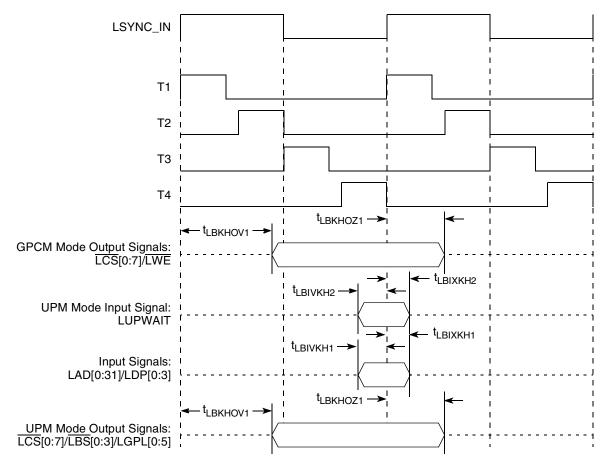

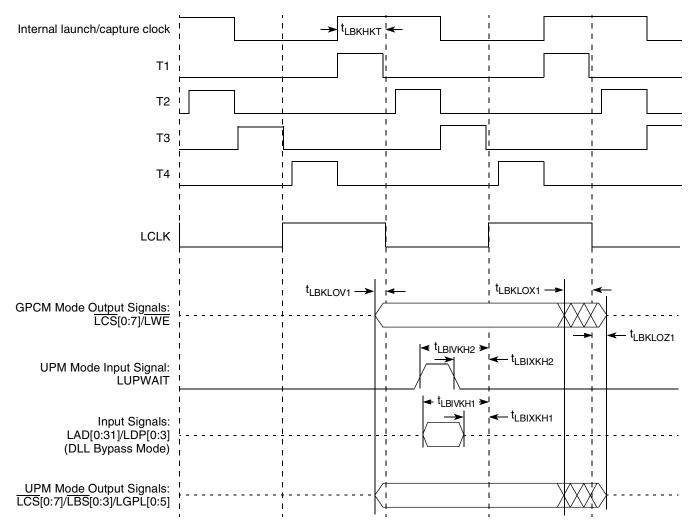

Local Bus

Figure 21. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Enabled)

Figure 22. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Bypass Mode)

### JTAG

# 11 JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8541E.

Table 38 provides the JTAG AC timing specifications as defined in Figure 32 through Figure 35.

## Table 38. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 2).

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation                                 | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time                                             | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V                          | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —     |

| JTAG external clock rise and fall times                                    | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                                                           | t <sub>TRST</sub>                          | 25       | _        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI                       | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI                        | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 |          | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | _        |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

#### Notes:

All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 31). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

2. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the t<sub>ime</sub> data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

4. Non-JTAG signal input timing with respect to  $t_{TCLK}$ .

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Package and Pin Listings

| Table 43. | MPC8541E | Pinout | Listing | (continued) |

|-----------|----------|--------|---------|-------------|

|-----------|----------|--------|---------|-------------|

| Signal             | Package Pin Number       | Pin Type                      | Power<br>Supply    | Notes |

|--------------------|--------------------------|-------------------------------|--------------------|-------|

|                    | JTAG                     |                               |                    | •     |

| ТСК                | AF21                     | I                             | $OV_{DD}$          | —     |

| TDI                | AG21                     | I                             | OV <sub>DD</sub>   | 12    |

| TDO                | AF19                     | 0                             | OV <sub>DD</sub>   | 11    |

| TMS                | AF23                     | I                             | OV <sub>DD</sub>   | 12    |

| TRST               | AG23                     | I                             | OV <sub>DD</sub>   | 12    |

|                    | DFT                      |                               |                    |       |

| LSSD_MODE          | AG19                     | I                             | OV <sub>DD</sub>   | 20    |

| L1_TSTCLK          | AB22                     | I                             | OV <sub>DD</sub>   | 20    |

| L2_TSTCLK          | AG22                     | I                             | OV <sub>DD</sub>   | 20    |

| TEST_SEL0          | AH20                     | I                             | OV <sub>DD</sub>   | 3     |

| TEST_SEL1          | AG26                     | I                             | OV <sub>DD</sub>   | 3     |

|                    | Thermal Management       |                               |                    |       |

| THERMO             | AG2                      | —                             |                    | 14    |

| THERM1             | AH3                      | —                             | _                  | 14    |

|                    | Power Management         |                               |                    |       |

| ASLEEP             | AG18                     | —                             | _                  | 9, 18 |

|                    | Power and Ground Signals |                               |                    |       |

| AV <sub>DD</sub> 1 | AH19                     | Power for e500<br>PLL (1.2 V) | AV <sub>DD</sub> 1 | -     |

| AV <sub>DD</sub> 2 | AH18                     | Power for CCB<br>PLL (1.2 V)  | $AV_{DD}2$         | -     |

| AV <sub>DD</sub> 3 | AH17                     | Power for CPM<br>PLL (1.2 V)  | AV <sub>DD</sub> 3 | -     |

| AV <sub>DD</sub> 4 | AF28                     | Power for PCI1<br>PLL (1.2 V) | $AV_{DD}4$         | -     |

| AV <sub>DD</sub> 5 | AE28                     | Power for PCI2<br>PLL (1.2 V) | $AV_{DD}5$         | -     |

the heat sink should be slowly removed. Heating the heat sink to 40–50°C with an air gun can soften the interface material and make the removal easier. The use of an adhesive for heat sink attach is not recommended.

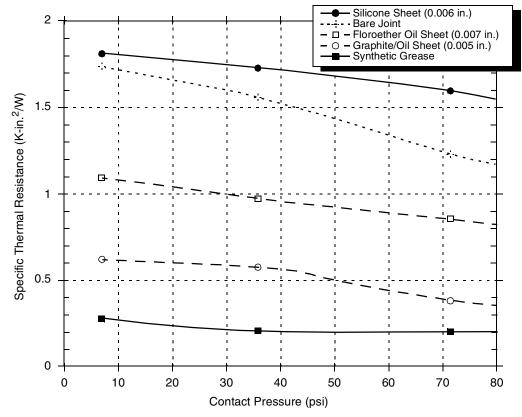

Figure 45. Thermal Performance of Select Thermal Interface Materials

The system board designer can choose between several types of thermal interface. There are several commercially-available thermal interfaces provided by the following vendors:

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                                      | 781-935-4850 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                                | 888-642-7674 |

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.                                                                                      | 800-347-4572 |

Chanhassen, MN 55317 Internet: www.bergquistcompany.com Thermagon Inc. 4707 Detroit Ave. Cleveland, OH 44102 Internet: www.thermagon.com

888-246-9050

## 16.2.4 Heat Sink Selection Examples

The following section provides a heat sink selection example using one of the commercially available heat sinks.

## 16.2.4.1 Case 1

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_J = T_I + T_R + (\theta_{JC} + \theta_{INT} + \theta_{SA}) \times P_D$$

where

$T_J$  is the die-junction temperature

T<sub>I</sub> is the inlet cabinet ambient temperature

$T_R$  is the air temperature rise within the computer cabinet

$\theta_{IC}$  is the junction-to-case thermal resistance

$\theta_{INT}$  is the adhesive or interface material thermal resistance

$\theta_{SA}$  is the heat sink base-to-ambient thermal resistance

$P_D$  is the power dissipated by the device. See Table 4 and Table 5.

During operation the die-junction temperatures  $(T_J)$  should be maintained within the range specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_A)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_R)$  may be in the range of 5° to 10°C. The thermal resistance of some thermal interface material ( $\theta_{INT}$ ) may be about 1°C/W. For the purposes of this example, the  $\theta_{JC}$  value given in Table 49 that includes the thermal grease interface and is documented in note 4 is used. If a thermal pad is used,  $\theta_{INT}$  must be added.

Assuming a T<sub>I</sub> of 30°C, a T<sub>R</sub> of 5°C, a FC-PBGA package  $\theta_{JC} = 0.96$ , and a power consumption (P<sub>D</sub>) of 8.0 W, the following expression for T<sub>J</sub> is obtained:

Die-junction temperature:  $T_J = 30^{\circ}C + 5^{\circ}C + (0.96^{\circ}C/W + \theta_{SA}) \times 8.0 W$

The heat sink-to-ambient thermal resistance ( $\theta_{SA}$ ) versus airflow velocity for a Thermalloy heat sink #2328B is shown in Figure 46.

Assuming an air velocity of 2 m/s, we have an effective  $\theta_{SA+}$  of about 3.3°C/W, thus

$T_{\rm J} = 30^{\circ}\text{C} + 5^{\circ}\text{C} + (0.96^{\circ}\text{C/W} + 3.3^{\circ}\text{C/W}) \times 8.0 \text{ W},$

resulting in a die-junction temperature of approximately 69°C which is well within the maximum operating temperature of the component.

System Design Information

# 17 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8541E.

# 17.1 System Clocking

The MPC8541E includes five PLLs.

- 1. The platform PLL (AV<sub>DD</sub>1) generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 15.2, "Platform/System PLL Ratio."

- 2. The e500 Core PLL (AV<sub>DD</sub>2) generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 15.3, "e500 Core PLL Ratio."

- 3. The CPM PLL ( $AV_{DD}$ 3) is slaved to the platform clock and is used to generate clocks used internally by the CPM block. The ratio between the CPM PLL and the platform clock is fixed and not under user control.

- 4. The PCI1 PLL (AV<sub>DD</sub>4) generates the clocking for the first PCI bus.

- 5. The PCI2 PLL (AV<sub>DD</sub>5) generates the clock for the second PCI bus.

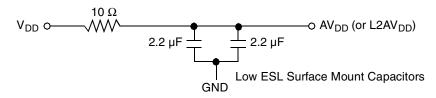

# 17.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, AV<sub>DD</sub>3, AV<sub>DD</sub>4, and AV<sub>DD</sub>5 respectively). The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages are derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide five independent filter circuits as illustrated in Figure 49, one to each of the five  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the 783 FC-PBGA footprint, without the inductance of vias.

System Design Information

Figure 49 shows the PLL power supply filter circuit.

Figure 49. PLL Power Supply Filter Circuit

# 17.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the MPC8541E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8541E system, and the MPC8541E itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pins of the MPC8541E. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $OV_{DD}$ , OV

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

## 17.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8541E.

# 17.5 Output Buffer DC Impedance

The MPC8541E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 50). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices.

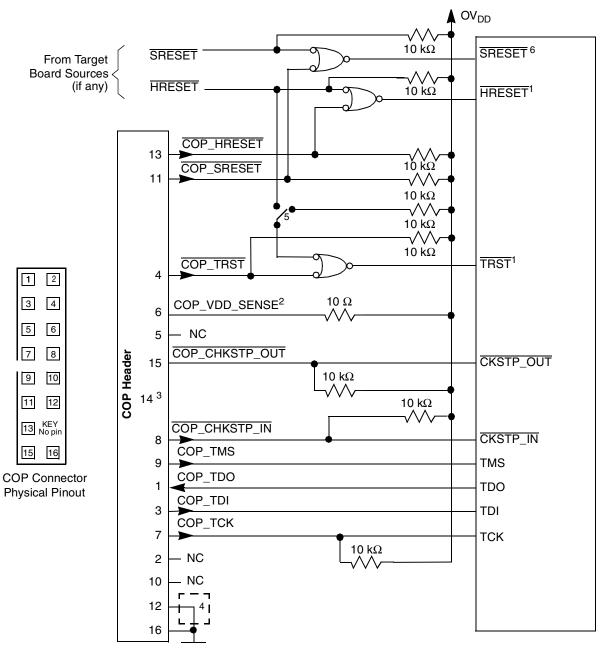

## 17.8.1 Termination of Unused Signals

If the JTAG interface and COP header are not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 52. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- Tie TCK to  $OV_{DD}$  through a 10 k $\Omega$  resistor. This prevents TCK from changing state and reading incorrect data into the device.

- No connection is required for TDI, TMS, or TDO.

System Design Information

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10  $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch should be open during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed or removed.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

#### Figure 52. JTAG Interface Connection

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. IEEE 802.3 and 1149.1 are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Document Number: MPC8541EEC Rev. 4.2 1/2008