Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorColdfire V2Core Size32-Bit Single-CoreSpeed100MHzConnectivityEBI/EMI, Ethernet, I²C, SPI, UART/USARTPeripheralsDMA, WDTNumber of I/O39 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Core Size32-Bit Single-CoreSpeed100MHzConnectivityEBI/EMI, Ethernet, I²C, SPI, UART/USARTPeripheralsDMA, WDT                                                               |  |

| Speed100MHzConnectivityEBI/EMI, Ethernet, I²C, SPI, UART/USARTPeripheralsDMA, WDT                                                                                          |  |

| ConnectivityEBI/EMI, Ethernet, I²C, SPI, UART/USARTPeripheralsDMA, WDT                                                                                                     |  |

| Peripherals DMA, WDT                                                                                                                                                       |  |

|                                                                                                                                                                            |  |

| Number of I/O 39                                                                                                                                                           |  |

|                                                                                                                                                                            |  |

| Program Memory Size -                                                                                                                                                      |  |

| Program Memory Type ROMless                                                                                                                                                |  |

| EEPROM Size -                                                                                                                                                              |  |

| RAM Size 64K x 8                                                                                                                                                           |  |

| Voltage - Supply (Vcc/Vdd) 1.4V ~ 1.6V                                                                                                                                     |  |

| Data Converters -                                                                                                                                                          |  |

| Oscillator Type External                                                                                                                                                   |  |

| Operating Temperature 0°C ~ 70°C (TA)                                                                                                                                      |  |

| Mounting Type Surface Mount                                                                                                                                                |  |

| Package / Case 160-BQFP                                                                                                                                                    |  |

| Supplier Device Package160-QFP (28x28)                                                                                                                                     |  |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf5270ab100                                                                                          |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MCF5271 Family Configurations

## 1 MCF5271 Family Configurations

Table 1. MCF5271 Family Configurations

| Module MCF5270 MCF52                              |                        |                        |  |  |  |

|---------------------------------------------------|------------------------|------------------------|--|--|--|

| Module                                            |                        | WICF52/1               |  |  |  |

| ColdFire V2 Core with EMAC and<br>Hardware Divide | х                      | х                      |  |  |  |

| System Clock                                      | 150                    | MHz                    |  |  |  |

| Performance (Dhrystone/2.1 MIPS)                  | 14                     | 14                     |  |  |  |

| Instruction/Data Cache                            | 8 Kt                   | oytes                  |  |  |  |

| Static RAM (SRAM)                                 | 64 K                   | bytes                  |  |  |  |

| Interrupt Controllers (INTC)                      | 2                      | 2                      |  |  |  |

| Edge Port Module (EPORT)                          | х                      | х                      |  |  |  |

| External Interface Module (EIM)                   | х                      | х                      |  |  |  |

| 4-channel Direct-Memory Access (DMA)              | х                      | х                      |  |  |  |

| SDRAM Controller                                  | х                      | х                      |  |  |  |

| Fast Ethernet Controller (FEC)                    | х                      | х                      |  |  |  |

| Hardware Encryption                               | _                      | х                      |  |  |  |

| Watchdog Timer (WDT)                              | х                      | х                      |  |  |  |

| Four Periodic Interrupt Timers (PIT)              | х                      | х                      |  |  |  |

| 32-bit DMA Timers                                 | 4                      | 4                      |  |  |  |

| QSPI                                              | х                      | х                      |  |  |  |

| UART(s)                                           | 3                      | 3                      |  |  |  |

| I <sup>2</sup> C                                  | х                      | х                      |  |  |  |

| General Purpose I/O Module (GPIO)                 | х                      | х                      |  |  |  |

| JTAG - IEEE 1149.1 Test Access Port               | х                      | х                      |  |  |  |

| Package                                           | 160 QFP,<br>196 MAPBGA | 160 QFP,<br>196 MAPBGA |  |  |  |

## 2 Block Diagram

The superset device in the MCF5271 family comes in a 196 mold array plastic ball grid array (MAPBGA) package. Figure 1 shows a top-level block diagram of the MCF5271.

Features

## 3 Features

For a detailed feature list see the MCF5271 Reference Manual (MCF5271RM).

## 4 Signal Descriptions

This section describes signals that connect off chip, including a table of signal properties. For a more detailed discussion of the MCF5271 signals, consult the *MCF5271 Reference Manual* (MCF5271RM).

### 4.1 Signal Properties

Table 4 lists all of the signals grouped by function. The "Dir" column is the direction for the primary function of the pin. Refer to Section 6, "Mechanicals/Pinouts and Part Numbers," for package diagrams.

### NOTE

In this table and throughout this document a single signal within a group is designated without square brackets (i.e., A24), while designations for multiple signals within a group use brackets (i.e., A[23:21]) and is meant to include all signals within the two bracketed numbers when these numbers are separated by a colon.

### NOTE

The primary functionality of a pin is not necessarily its default functionality. Pins that are muxed with GPIO will default to their GPIO functionality.

| Signal Name | GPIO                                | Alternate 1     | Alternate 2   | Dir. <sup>1</sup> | MCF5270<br>MCF5271<br>160 QFP | MCF5270<br>MCF5271<br>196 MAPBGA |  |  |

|-------------|-------------------------------------|-----------------|---------------|-------------------|-------------------------------|----------------------------------|--|--|

|             | Reset                               |                 |               |                   |                               |                                  |  |  |

| RESET       | —                                   | —               | —             | I                 | 83                            | N13                              |  |  |

| RSTOUT      | _                                   | _               |               | 0                 | 82                            | P13                              |  |  |

| Clock       |                                     |                 |               |                   |                               |                                  |  |  |

| EXTAL       | _                                   | —               | _             | I                 | 86                            | M14                              |  |  |

| XTAL        | _                                   | _               | _             | 0                 | 85                            | N14                              |  |  |

| CLKOUT      | _                                   | _               | _             | 0                 | 89                            | K14                              |  |  |

|             |                                     | Мс              | ode Selection | n                 |                               |                                  |  |  |

| CLKMOD[1:0] | _                                   | —               | _             | I                 | 20,21                         | G5,H5                            |  |  |

| RCON        | _                                   | —               | _             | Ι                 | 79                            | K10                              |  |  |

|             | External Memory Interface and Ports |                 |               |                   |                               |                                  |  |  |

| A[23:21]    | PADDR[7:5]                          | <u>CS</u> [6:4] |               | 0                 | 126, 125, 124                 | B11, C11, D11                    |  |  |

Table 2. MCF5270 and MCF5271 Signal Information and Muxing

| Signal Name     | GPIO        | Alternate 1 | Alternate 2 | Dir. <sup>1</sup> | MCF5270<br>MCF5271<br>160 QFP | MCF5270<br>MCF5271<br>196 MAPBGA                                                                                          |  |  |  |

|-----------------|-------------|-------------|-------------|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A[20:0]         |             | Ι           | Ι           | 0                 | 123:115,<br>112:106, 102:98   | A12, B12, C12,<br>A13, B13, B14,<br>C13, C14, D12,<br>D13, D14, E11,<br>E12, E13, E14,<br>F12, F13, F14,<br>G11, G12, G13 |  |  |  |

| D[31:16]        | _           | _           | _           | 0                 | 22:30, 33:39                  | G1, G2, H1, H2,<br>H3, H4, J1, J2,<br>J3, J4, K1, K2,<br>K3, K4, L1, L2                                                   |  |  |  |

| D[15:8]         | PDATAH[7:0] | _           | _           | 0                 | 42:49                         | M1, N1, M2, N2,<br>P2, L3, M3, N3                                                                                         |  |  |  |

| D[7:0]          | PDATAL[7:0] | _           | _           | 0                 | 50:52, 56:60                  | P3, M4, N4, P4,<br>L5, M5, N5, P5                                                                                         |  |  |  |

| BS[3:0]         | PBS[7:4]    | CAS[3:0]    | _           | 0                 | 143:140                       | B6, C6, D7, C7                                                                                                            |  |  |  |

| OE              | PBUSCTL7    | _           | _           | 0                 | 62                            | N6                                                                                                                        |  |  |  |

| TA              | PBUSCTL6    | _           | _           | Ι                 | 96                            | H11                                                                                                                       |  |  |  |

| TEA             | PBUSCTL5    | DREQ1       |             | Ι                 | —                             | J14                                                                                                                       |  |  |  |

| R/W             | PBUSCTL4    | _           | _           | 0                 | 95                            | J13                                                                                                                       |  |  |  |

| TSIZ1           | PBUSCTL3    | DACK1       |             | 0                 | —                             | P6                                                                                                                        |  |  |  |

| TSIZ0           | PBUSCTL2    | DACK0       |             | 0                 | —                             | P7                                                                                                                        |  |  |  |

| TS              | PBUSCTL1    | DACK2       | _           | 0                 | 97                            | H13                                                                                                                       |  |  |  |

| TIP             | PBUSCTL0    | DREQ0       |             | 0                 |                               | H12                                                                                                                       |  |  |  |

|                 |             | C           | hip Selects |                   |                               |                                                                                                                           |  |  |  |

| <u>CS</u> [7:4] | PCS[7:4]    | _           | _           | 0                 | _                             | B9, A10, C10,<br>A11                                                                                                      |  |  |  |

| <u>CS</u> [3:2] | PCS[3:2]    | SD_CS[1:0]  | -           | 0                 | 132,131                       | A9, C9                                                                                                                    |  |  |  |

| CS1             | PCS1        | _           | _           | 0                 | 130                           | B10                                                                                                                       |  |  |  |

| CS0             |             |             |             | 0                 | 129                           | D10                                                                                                                       |  |  |  |

|                 |             | SDR         | AM Control  | ler               |                               |                                                                                                                           |  |  |  |

| SD_WE           | PSDRAM5     |             | —           | 0                 | 92                            | K13                                                                                                                       |  |  |  |

| SD_SCAS         | PSDRAM4     | —           | —           | 0                 | 91                            | K12                                                                                                                       |  |  |  |

| SD_SRAS         | PSDRAM3     | —           | —           | 0                 | 90                            | K11                                                                                                                       |  |  |  |

| SD_CKE          | PSDRAM2     | —           | _           | 0                 | —                             | E8                                                                                                                        |  |  |  |

| SD_CS[1:0]      | PSDRAM[1:0] |             |             | 0                 | _                             | L12, L13                                                                                                                  |  |  |  |

#### Table 2. MCF5270 and MCF5271 Signal Information and Muxing (continued)

#### **Design Recommendations**

will be undesired high current in the ESD protection diodes. There are no requirements for the fall times of the power supplies.

The recommended power down sequence is as follows:

- 1. Drop  $V_{DD}$  to 0 V.

- 2. Drop  $OV_{DD}/V_{DDPLL}$  supplies.

### 5.3 Decoupling

- Place the decoupling caps as close to the pins as possible, but they can be outside the footprint of the package.

- 0.1  $\mu$ F and 0.01  $\mu$ F at each supply input

### 5.4 Buffering

• Use bus buffers on all data/address lines for all off-board accesses and for all on-board accesses when excessive loading is expected. See Section 7, "Electrical Characteristics."

### 5.5 Pull-up Recommendations

• Use external pull-up resistors on unused inputs. See pin table.

### 5.6 Clocking Recommendations

- Use a multi-layer board with a separate ground plane.

- Place the crystal and all other associated components as close to the EXTAL and XTAL (oscillator pins) as possible.

- Do not run a high frequency trace around crystal circuit.

- Ensure that the ground for the bypass capacitors is connected to a solid ground trace.

- Tie the ground trace to the ground pin nearest EXTAL and XTAL. This prevents large loop currents in the vicinity of the crystal.

- Tie the ground pin to the most solid ground in the system.

- Do not connect the trace that connects the oscillator and the ground plane to any other circuit element. This tends to make the oscillator unstable.

- Tie XTAL to ground when an external oscillator is clocking the device.

### 5.7 Interface Recommendations

### 5.7.1 SDRAM Controller

### 5.7.1.1 SDRAM Controller Signals in Synchronous Mode

Table 3 shows the behavior of SDRAM signals in synchronous mode.

| r          |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal     | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SD_SRAS    | Synchronous row address strobe. Indicates a valid SDRAM row address is present and can be latched by the SDRAM. SD_SRAS should be connected to the corresponding SDRAM SD_SRAS. Do not confuse SD_SRAS with the DRAM controller's SD_CS[1:0], which should not be interfaced to the SDRAM SD_SRAS signals.                                                                                                                       |

| SD_SCAS    | Synchronous column address strobe. Indicates a valid column address is present and can be latched by the SDRAM. SD_SCAS should be connected to the corresponding signal labeled SD_SCAS on the SDRAM.                                                                                                                                                                                                                            |

| DRAMW      | DRAM read/write. Asserted for write operations and negated for read operations.                                                                                                                                                                                                                                                                                                                                                  |

| SD_CS[1:0] | Row address strobe. Select each memory block of SDRAMs connected to the MCF5271. One SD_CS signal selects one SDRAM block and connects to the corresponding $\overline{CS}$ signals.                                                                                                                                                                                                                                             |

| SD_CKE     | Synchronous DRAM clock enable. Connected directly to the CKE (clock enable) signal of SDRAMs. Enables and disables the clock internal to SDRAM. When CKE is low, memory can enter a power-down mode where operations are suspended or they can enter self-refresh mode. SD_CKE functionality is controlled by DCR[COC]. For designs using external multiplexing, setting COC allows SD_CKE to provide command-bit functionality. |

| BS[3:0]    | Column address strobe. For synchronous operation, $\overline{\text{BS}}$ [3:0] function as byte enables to the SDRAMs. They connect to the DQM signals (or mask qualifiers) of the SDRAMs.                                                                                                                                                                                                                                       |

| CLKOUT     | Bus clock output. Connects to the CLK input of SDRAMs.                                                                                                                                                                                                                                                                                                                                                                           |

#### Table 3. Synchronous DRAM Signal Connections

### 5.7.1.2 Address Multiplexing

See the SDRAM controller module chapter in the *MCF5271 Reference Manual* for details on address multiplexing.

### 5.7.2 Ethernet PHY Transceiver Connection

The FEC supports both an MII interface for 10/100 Mbps Ethernet and a seven-wire serial interface for 10 Mbps Ethernet. The interface mode is selected by R\_CNTRL[MII\_MODE]. In MII mode, the 802.3 standard defines and the FEC module supports 18 signals. These are shown in Table 4.

| Signal Description | MCF5271 Pin |

|--------------------|-------------|

| Transmit clock     | ETXCLK      |

| Transmit enable    | ETXEN       |

| Transmit data      | ETXD[3:0]   |

| Transmit error     | ETXER       |

| Collision          | ECOL        |

| Carrier sense      | ECRS        |

| Receive clock      | ERXCLK      |

| Receive enable     | ERXDV       |

| Receive data       | ERXD[3:0]   |

#### Table 4. MII Mode

#### Mechanicals/Pinouts and Part Numbers

| Signal Description             | MCF5271 Pin |

|--------------------------------|-------------|

| Receive error                  | ERXER       |

| Management channel clock       | EMDC        |

| Management channel serial data | EMDIO       |

Table 4. MII Mode (continued)

The serial mode interface operates in what is generally referred to as AMD mode. The MCF5271 configuration for seven-wire serial mode connections to the external transceiver are shown in Table 5.

| Signal Description                   | MCF5271 Pin |

|--------------------------------------|-------------|

| Transmit clock                       | ETXCLK      |

| Transmit enable                      | ETXEN       |

| Transmit data                        | ETXD[0]     |

| Collision                            | ECOL        |

| Receive clock                        | ERXCLK      |

| Receive enable                       | ERXDV       |

| Receive data                         | ERXD[0]     |

| Unused, configure as PB14            | ERXER       |

| Unused input, tie to ground          | ECRS        |

| Unused, configure as PB[13:11]       | ERXD[3:1]   |

| Unused output, ignore                | ETXER       |

| Unused, configure as PB[10:8]        | ETXD[3:1]   |

| Unused, configure as PB15            | EMDC        |

| Input after reset, connect to ground | EMDIO       |

Table 5. Seven-Wire Mode Configuration

Refer to the M5271EVB evaluation board user's manual for an example of how to connect an external PHY. Schematics for this board are accessible at the MCF5271 site by navigating to: http://www.freescale.com/coldfire.

### 5.7.3 BDM

Use the BDM interface as shown in the M5271EVB evaluation board user's manual. The schematics for this board are accessible at the Freescale website at: http://www.freescale.com/coldfire.

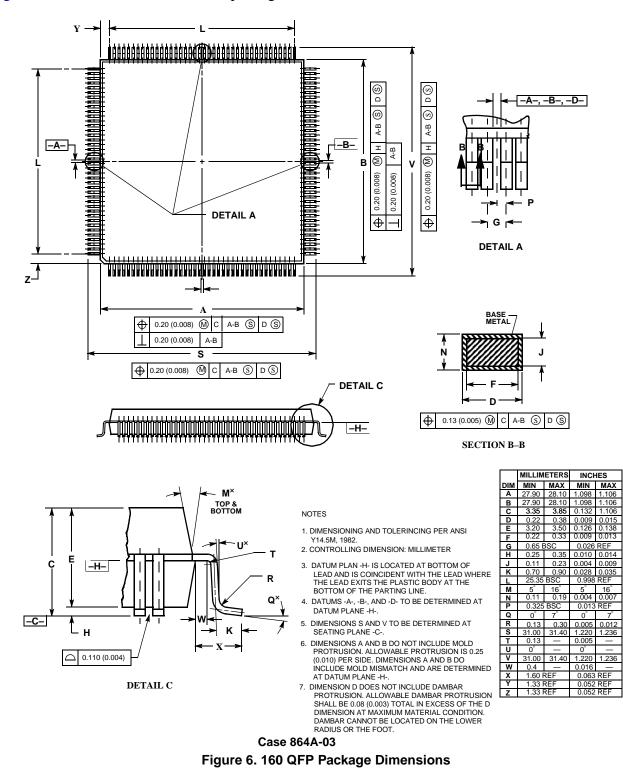

## 6 Mechanicals/Pinouts and Part Numbers

This section contains drawings showing the pinout and the packaging and mechanical characteristics of the MCF5271 devices. See Table 4 for a list the signal names and pin locations for each device.

**Mechanicals/Pinouts and Part Numbers**

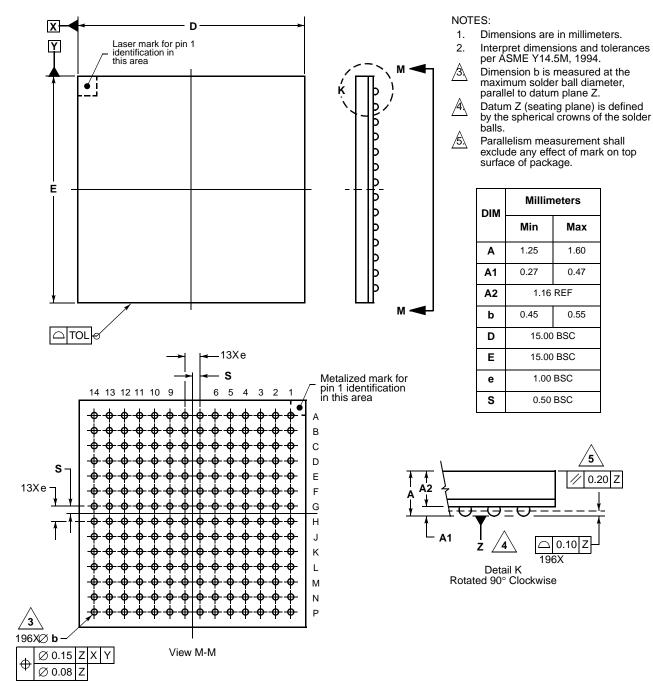

### 6.2 Package Dimensions—196 MAPBGA

Figure 4 shows MCF5270/71CVMxxx package dimensions.

Figure 4. 196 MAPBGA Package Dimensions (Case No. 1128A-01)

**Mechanicals/Pinouts and Part Numbers**

### 6.4 Package Dimensions—160 QFP

Figure 6 shows MCF5270/71CAB80 package dimensions.

### 6.5 Ordering Information

Table 6. Orderable Part Numbers

| Freescale Part<br>Number | Description                 | Package    | Speed  | Lead-Free? | Temperature    |

|--------------------------|-----------------------------|------------|--------|------------|----------------|

| MCF5270AB100             | MCF5270 RISC Microprocessor | 160 QFP    | 100MHz | Yes        | 0° to +70° C   |

| MCF5270CAB100            | MCF5270 RISC Microprocessor | 160 QFP    | 100MHz | Yes        | -40° to +85° C |

| MCF5270VM100             | MCF5270 RISC Microprocessor | 196 MAPBGA | 100MHz | Yes        | 0° to +70° C   |

| MCF5270CVM150            | MCF5270 RISC Microprocessor | 196 MAPBGA | 150MHz | Yes        | -40° to +85° C |

| MCF5271CAB100            | MCF5271 RISC Microprocessor | 160 QFP    | 100MHz | Yes        | -40° to +85° C |

| MCF5271CVM100            | MCF5271 RISC Microprocessor | 196 MAPBGA | 100MHz | Yes        | -40° to +85° C |

| MCF5271CVM150            | MCF5271 RISC Microprocessor | 196 MAPBGA | 150MHz | Yes        | -40° to +85° C |

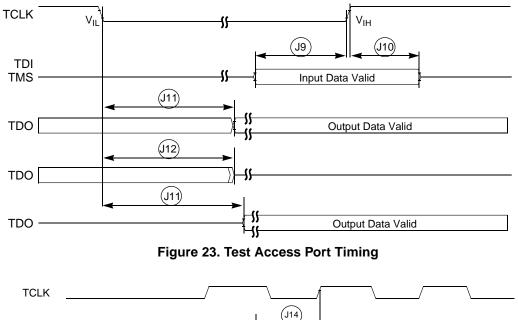

## 7 Electrical Characteristics

This chapter contains electrical specification tables and reference timing diagrams for the MCF5271 microcontroller unit. This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications of MCF5271.

#### NOTE

The parameters specified in this processor document supersede any values found in the module specifications.

### 7.1 Maximum Ratings

Table 7. Absolute Maximum Ratings<sup>1, 2</sup>

| Rating                                                                                   | Symbol                                               | Value          | Unit |

|------------------------------------------------------------------------------------------|------------------------------------------------------|----------------|------|

| Core Supply Voltage                                                                      | V <sub>DD</sub>                                      | - 0.5 to +2.0  | V    |

| Pad Supply Voltage                                                                       | OV <sub>DD</sub>                                     | – 0.3 to +4.0  | V    |

| PLL Supply Voltage                                                                       | V <sub>DDPLL</sub>                                   | – 0.3 to +4.0  | V    |

| Digital Input Voltage <sup>3</sup>                                                       | V <sub>IN</sub>                                      | – 0.3 to + 4.0 | V    |

| Instantaneous Maximum Current<br>Single pin limit (applies to all pins) <sup>3,4,5</sup> | Ι <sub>D</sub>                                       | 25             | mA   |

| Operating Temperature Range (Packaged)                                                   | T <sub>A</sub><br>(T <sub>L</sub> - T <sub>H</sub> ) | – 40 to 85     | °C   |

| Storage Temperature Range                                                                | T <sub>stg</sub>                                     | – 65 to 150    | °C   |

Functional operating conditions are given in DC Electrical Specifications. Absolute Maximum Ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Continued operation at these levels may affect device reliability or cause permanent damage to the device.

1

- <sup>2</sup> This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or OV<sub>DD</sub>).

- <sup>3</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>4</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and OV<sub>DD</sub>.

- <sup>5</sup> Power supply must maintain regulation within operating  $OV_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > OV_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $OV_{DD}$  and could result in external power supply going out of regulation. Insure external  $OV_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the processor is not consuming power (ex; no clock).Power supply must maintain regulation within operating  $OV_{DD}$  range during instantaneous and operating maximum current conditions.

### 7.2 Thermal Characteristics

The below table lists thermal resistance values.

| Characteristic                          |                         | Symbol          | 196<br>MAPBGA     | 160QFP            | Unit |

|-----------------------------------------|-------------------------|-----------------|-------------------|-------------------|------|

| Junction to ambient, natural convection | Four layer board (2s2p) | $\theta_{JMA}$  | 32 <sup>1,2</sup> | 40 <sup>1,2</sup> | °C/W |

| Junction to ambient (@200 ft/min)       | Four layer board (2s2p) | $\theta_{JMA}$  | 29 <sup>1,2</sup> | 36 <sup>1,2</sup> | °C/W |

| Junction to board                       |                         | $\theta_{JB}$   | 20 <sup>3</sup>   | 25 <sup>3</sup>   | °C/W |

| Junction to case                        |                         | θ <sub>JC</sub> | 10 <sup>4</sup>   | 10 <sup>4</sup>   | °C/W |

| Junction to top of package              |                         | Ψ <sub>jt</sub> | 2 <sup>1,5</sup>  | 2 <sup>1,5</sup>  | °C/W |

| Maximum operating junction temperature  |                         | Тj              | 104               | 105               | °C   |

#### **Table 8. Thermal Characteristics**

$\theta_{JMA}$  and  $\Psi_{jt}$  parameters are simulated in conformance with EIA/JESD Standard 51-2 for natural convection. Motorola recommends the use of  $\theta_{JmA}$  and power dissipation specifications in the system design to prevent device junction temperatures from exceeding the rated specification. System designers should be aware that device junction temperatures can be significantly influenced by board layout and surrounding devices. Conformance to the device junction temperature specification can be verified by physical measurement in the customer's system using the  $\Psi_{jt}$  parameter, the device power dissipation, and the method described in EIA/JESD Standard 51-2.

- <sup>2</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>3</sup> Thermal resistance between the die and the printed circuit board in conformance with JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>4</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written in conformance with Psi-JT.

The average chip-junction temperature  $(T_I)$  in °C can be obtained from:

$$\Gamma_{J} = T_{A} + (P_{D} \times \Theta_{JMA}) (1)$$

Where:

| Characteristic                                                                                                                                                                                                              | Symbol           | Min         | Typical    | Max       | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------------|-----------|----------|

| Load Capacitance <sup>4</sup><br>Low drive strength<br>High drive strength                                                                                                                                                  | CL               |             |            | 25<br>50  | pF<br>pF |

| Core Operating Supply Current <sup>5</sup><br>Master Mode                                                                                                                                                                   | I <sub>DD</sub>  | _           | 135        | 150       | mA       |

| Pad Operating Supply Current<br>Master Mode<br>Low Power Modes                                                                                                                                                              | OI <sub>DD</sub> |             | 100<br>TBD |           | mA<br>μA |

| DC Injection Current <sup>3, 6, 7, 8</sup><br>V <sub>NEGCLAMP</sub> =V <sub>SS</sub> - 0.3 V, V <sub>POSCLAMP</sub> = V <sub>DD</sub> + 0.3<br>Single Pin Limit<br>Total processor Limit, Includes sum of all stressed pins | IIC              | -1.0<br>-10 |            | 1.0<br>10 | mA<br>mA |

#### Table 9. DC Electrical Specifications<sup>1</sup> (continued)

<sup>1</sup> Refer to Table 10 for additional PLL specifications.

<sup>2</sup> Refer to the MCF5271 signals section for pins having weak internal pull-up devices.

<sup>3</sup> This parameter is characterized before qualification rather than 100% tested.

<sup>4</sup> pF load ratings are based on DC loading and are provided as an indication of driver strength. High speed interfaces require transmission line analysis to determine proper drive strength and termination. See <u>High Speed Signal Propagation:</u> <u>Advanced Black Magic</u> by Howard W. Johnson for design guidelines.

<sup>5</sup> Current measured at maximum system clock frequency, all modules active, and default drive strength with matching load.

$^{6}$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and their respective V<sub>DD</sub>.

<sup>7</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

<sup>8</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Insure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the processor is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which would reduce overall power consumption. Also, at power-up, system clock is not present during the power-up sequence until the PLL has attained lock.

### 7.4 Oscillator and PLLMRFM Electrical Characteristics

#### Table 10. HiP7 PLLMRFM Electrical Specifications<sup>1</sup>

| Num | Characteristic                                                                                                                      | Symbol                                                                   | Min.<br>Value              | Max.<br>Value   | Unit              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|-----------------|-------------------|

| 1   | PLL Reference Frequency Range<br>Crystal reference<br>External reference<br>1:1 mode (NOTE: $f_{sys/2} = 2 \times f_{ref_{-1:1}}$ ) | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub><br>f <sub>ref_1:1</sub> | 8<br>8<br>24               | 25<br>25<br>75  | MHz               |

| 2   | Core frequency<br>CLKOUT Frequency <sup>2</sup><br>External reference<br>On-Chip PLL Frequency                                      | f <sub>sys</sub><br>f <sub>sys/2</sub>                                   | 0<br>f <sub>ref</sub> ÷ 32 | 150<br>75<br>75 | MHz<br>MHz<br>MHz |

| 3   | Loss of Reference Frequency <sup>3, 5</sup>                                                                                         | f <sub>LOR</sub>                                                         | 100                        | 1000            | kHz               |

| 4   | Self Clocked Mode Frequency <sup>4, 5</sup>                                                                                         | f <sub>SCM</sub>                                                         | 10.25                      | 15.25           | MHz               |

| 5   | Crystal Start-up Time <sup>5, 6</sup>                                                                                               | t <sub>cst</sub>                                                         | —                          | 10              | ms                |

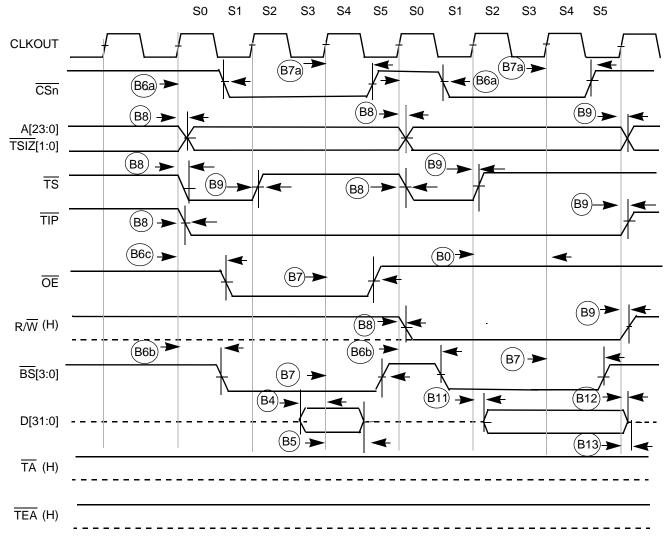

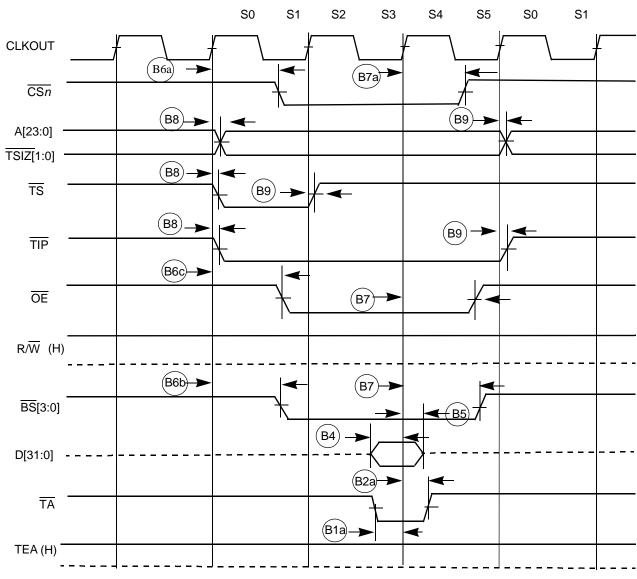

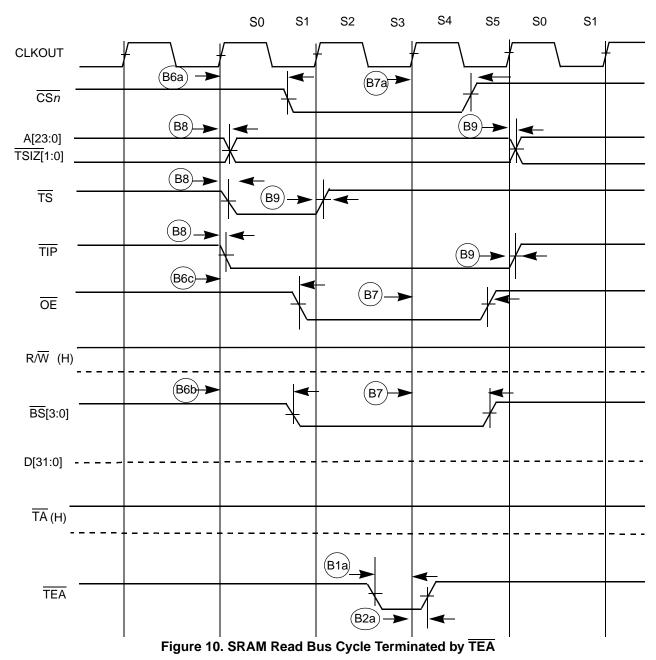

Read/write bus timings listed in Table 12 are shown in Figure 8, Figure 9, and Figure 10.

Figure 8. Read/Write (Internally Terminated) SRAM Bus Timing

Figure 9 shows a bus cycle terminated by  $\overline{TA}$  showing timings listed in Table 12.

Figure 9. SRAM Read Bus Cycle Terminated by  $\overline{TA}$

Figure 10 shows an SRAM bus cycle terminated by  $\overline{\text{TEA}}$  showing timings listed in Table 12.

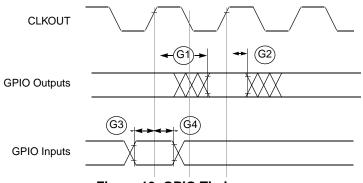

### Figure 13. GPIO Timing

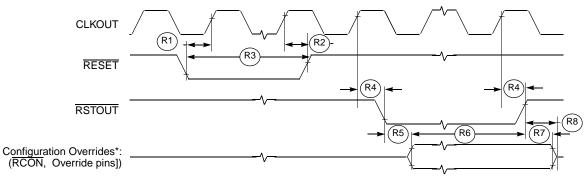

### 7.8 Reset and Configuration Override Timing

# Table 15. Reset and Configuration Override Timing $(V_{DD} = 2.7 \text{ to } 3.6 \text{ V}, \text{ V}_{SS} = 0 \text{ V}, \text{ T}_{A} = \text{T}_{L} \text{ to } \text{T}_{H})^{1}$

| NUM | Characteristic                                          | Symbol             | Min | Max | Unit             |

|-----|---------------------------------------------------------|--------------------|-----|-----|------------------|

| R1  | RESET Input valid to CLKOUT High                        | t <sub>RVCH</sub>  | 9   |     | ns               |

| R2  | CLKOUT High to RESET Input invalid                      | t <sub>CHRI</sub>  | 1.5 |     | ns               |

| R3  | RESET Input valid Time <sup>2</sup>                     | t <sub>RIVT</sub>  | 5   | —   | t <sub>CYC</sub> |

| R4  | CLKOUT High to RSTOUT Valid                             | t <sub>CHROV</sub> | _   | 10  | ns               |

| R5  | RSTOUT valid to Config. Overrides valid                 | t <sub>ROVCV</sub> | 0   | —   | ns               |

| R6  | Configuration Override Setup Time to RSTOUT invalid     | t <sub>cos</sub>   | 20  | —   | t <sub>CYC</sub> |

| R7  | Configuration Override Hold Time after RSTOUT invalid   | t <sub>COH</sub>   | 0   |     | ns               |

| R8  | RSTOUT invalid to Configuration Override High Impedance | t <sub>ROICZ</sub> | _   | 1   | t <sub>CYC</sub> |

<sup>1</sup> All AC timing is shown with respect to 50%  $V_{DD}$  levels unless otherwise noted.

<sup>2</sup> During low power STOP, the synchronizers for the RESET input are bypassed and RESET is asserted asynchronously to the system. Thus, RESET must be held a minimum of 100 ns.

Figure 14. RESET and Configuration Override Timing

Refer to the chip configuration module (CCM) chapter in the device's reference manual for more information.

## 7.9 I<sup>2</sup>C Input/Output Timing Specifications

Table 16 lists specifications for the  $I^2C$  input timing parameters shown in Figure 15.

| Table 16. I <sup>2</sup> C Input Timing | Specifications between I2C | _SCL and I2C_SDA |

|-----------------------------------------|----------------------------|------------------|

|-----------------------------------------|----------------------------|------------------|

| Num | Characteristic                                                                    | Min | Max | Units            |

|-----|-----------------------------------------------------------------------------------|-----|-----|------------------|

| 11  | Start condition hold time                                                         | 2   | —   | t <sub>cyc</sub> |

| 12  | Clock low period                                                                  | 8   | —   | t <sub>cyc</sub> |

| 13  | I2C_SCL/I2C_SDA rise time ( $V_{IL} = 0.5 \text{ V to } V_{IH} = 2.4 \text{ V}$ ) | —   | 1   | ms               |

| 14  | Data hold time                                                                    | 0   | —   | ns               |

| 15  | I2C_SCL/I2C_SDA fall time ( $V_{IH} = 2.4$ V to $V_{IL} = 0.5$ V)                 | —   | 1   | ms               |

| 16  | Clock high time                                                                   | 4   | —   | t <sub>cyc</sub> |

| 17  | Data setup time                                                                   | 0   | —   | ns               |

| 18  | Start condition setup time (for repeated start condition only)                    | 2   | —   | t <sub>cyc</sub> |

| 19  | Stop condition setup time                                                         | 2   | _   | t <sub>cyc</sub> |

Table 17 lists specifications for the  $I^2C$  output timing parameters shown in Figure 15.

| Table 17. I <sup>2</sup> C Output Timing Specifications between I2C | SCL and I2C_SDA |

|---------------------------------------------------------------------|-----------------|

|---------------------------------------------------------------------|-----------------|

| Num             | Characteristic                                                                 | Min | Max | Units            |

|-----------------|--------------------------------------------------------------------------------|-----|-----|------------------|

| 11 <sup>1</sup> | Start condition hold time                                                      | 6   | —   | t <sub>cyc</sub> |

| l2 <sup>1</sup> | Clock low period                                                               | 10  | —   | t <sub>cyc</sub> |

| 13 <sup>2</sup> | I2C_SCL/I2C_SDA rise time (V <sub>IL</sub> = 0.5 V to V <sub>IH</sub> = 2.4 V) | _   | —   | μs               |

| 14 <sup>1</sup> | Data hold time                                                                 | 7   | —   | t <sub>cyc</sub> |

| 15 <sup>3</sup> | I2C_SCL/I2C_SDA fall time ( $V_{IH}$ = 2.4 V to $V_{IL}$ = 0.5 V)              | _   | 3   | ns               |

| l6 <sup>1</sup> | Clock high time                                                                | 10  | —   | t <sub>cyc</sub> |

| 17 <sup>1</sup> | Data setup time                                                                | 2   | —   | t <sub>cyc</sub> |

| 18 <sup>1</sup> | Start condition setup time (for repeated start condition only)                 | 20  | —   | t <sub>cyc</sub> |

| 19 <sup>1</sup> | Stop condition setup time                                                      | 10  | —   | t <sub>cyc</sub> |

Note: Output numbers depend on the value programmed into the IFDR; an IFDR programmed with the maximum frequency (IFDR = 0x20) results in minimum output timings as shown in Table 17. The  $I^2C$  interface is designed to scale the actual data transition time to move it to the middle of the I2C\_SCL low period. The actual position is affected by the prescale and division values programmed into the IFDR; however, the numbers given in Table 17 are minimum values.

<sup>2</sup> Because I2C\_SCL and I2C\_SDA are open-collector-type outputs, which the processor can only actively drive low, the time I2C\_SCL or I2C\_SDA take to reach a high level depends on external signal capacitance and pull-up resistor values.

<sup>3</sup> Specified at a nominal 50-pF load.

Figure 15 shows timing for the values in Table 16 and Table 17.

1

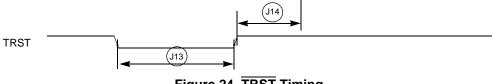

Figure 24. TRST Timing

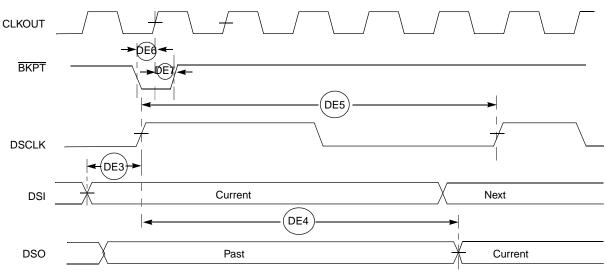

Figure 26. BDM Serial Port AC Timing

## 8 Documentation

Documentation regarding the MCF5271 and their development support tools is available from a local Freescale distributor, a Freescale semiconductor sales office, the Freescale Literature Distribution Center, or through the Freescale web address at http://www.freescale.com/coldfire.

## 9 Document Revision History

The below table provides a revision history for this document.

| Rev. No. | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1        | <ul><li>Fixed several clock values.</li><li>Updated Signal List table</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1.1      | • Removed duplicate information in the module description sections. The information is all in the Signals Description Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 1.2      | <ul> <li>Removed detailed signal description section. This information can be found in the MCF5271RM Chapter 2.</li> <li>Removed detailed feature list. This information can be found in the MCF5271RM Chapter 1.</li> <li>Changed instances of Motorola to Freescale</li> <li>Added values for 'Maximum operating junction temperature' in Table 8.</li> <li>Added typical values for 'Core operating supply current (master mode)' in Table 9.</li> <li>Added typical values for 'Pad operating supply current (master mode)' in Table 9.</li> <li>Removed unnecessary PLL specifications, #6-9, in Table 10.</li> </ul> |  |  |

#### **Document Revision History**

| Rev. No. | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.3      | <ul> <li>Device is now available in 150 MHz versions. Updated specs where necessary to reflect this improvement.</li> <li>Added 2 new part numbers to Table 6: MCF5270CVM150 and MCF5271CVM150.</li> <li>Removed features list. This information can be found in the MCF5271RM.</li> <li>Removed SDRAM address multiplexing section. This information can be found in the MCF5271RM.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 1.4      | <ul> <li>Added Section 5.2.1, "Supply Voltage Sequencing and Separation Cautions."</li> <li>Updated 196MAPBGA package dimensions, Figure 4.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2        | <ul> <li>Table 2: Changed SD_CKE pin location from 139 to "—" for the 160QFP device.</li> <li>Table 2: Changed QSPI_CS1 pin location from "—" to 139 for the 160QFP device.</li> <li>Table 2: Changed DT3IN pin's alternate 2 function from "—" to QSPI_CS2.</li> <li>Table 2: Changed DT3OUT pin's alternate 2 function from "—" to QSPI_CS3.</li> <li>Figure 5: Changed pin 139 label from "SD_CKE/QSPI_CS1" to "QSPI_CS1/SD_CKE".</li> <li>Removed second sentence from Section 7.10.1, "MII Receive Signal Timing (ERXD[3:0], ERXDV, ERXER, and ERXCLK)," and Section 7.10.2, "MII Transmit Signal Timing (ETXD[3:0], ETXEN, ETXER, ETXCLK)," regarding no minimum frequency requirement for TXCLK.</li> <li>Removed third and fourth paragraphs from Section 7.10.2, "MII Transmit Signal Timing (ETXD[3:0], ETXD[3:0], ETXEN, ETXER, ETXCLK)," as this feature is not supported on this device.</li> </ul> |  |  |

| 3        | <ul> <li>Section 5.2.1, "Supply Voltage Sequencing and Separation Cautions" changed PLLV<sub>DD</sub> to V<sub>DDPLL</sub> to match rest of document.</li> <li>Section 5.2.1, "Supply Voltage Sequencing and Separation Cautions" Changed V<sub>DDPLL</sub> voltage level from 1.5V to 3.3V throughout section.</li> <li>Section 5.2.1.1, "Power Up Sequence" first bullet, changed "Use 1 µs" to "Use 1 ms".</li> <li>Corrected position of spec D5 in Figure 11.</li> <li>Figure 3: Corrected M4 ball location from DATA5 to DATA6, changed DATA<i>n</i> labels to D<i>n</i> for consistency</li> <li>Table 14: Added DACK<i>n</i> and DREQ<i>n</i> to footnote.</li> <li>Table 9, added PLL supply voltage row</li> </ul>                                                                                                                                                                                     |  |  |

| 4        | Added part number MCF5270CAB100 in Table 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Table 26. MCF5271EC | <b>Revision History</b> | (continued) |

|---------------------|-------------------------|-------------|

|---------------------|-------------------------|-------------|

**Document Revision History**