# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                       |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 72MHz                                                                     |

| Connectivity               | Ethernet, I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 58K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                 |

| Data Converters            | A/D 6x10b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

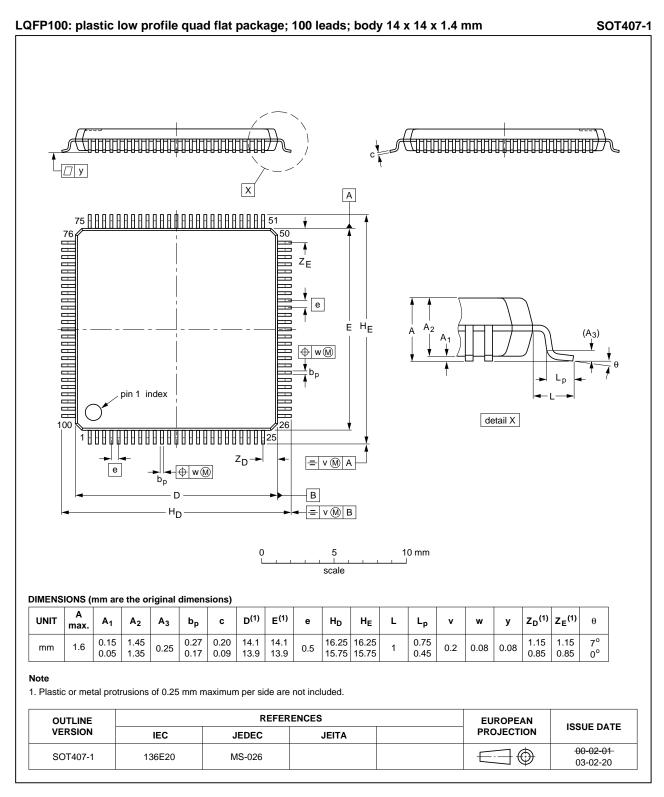

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2365fbd100-551 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.1 Ordering options

| LPC2364_65_66 | 4<br>Table 2. Orderin |       |              | ng optic            | ons     |     |       |          |                          |        |        |     |       |     |                   |

|---------------|-----------------------|-------|--------------|---------------------|---------|-----|-------|----------|--------------------------|--------|--------|-----|-------|-----|-------------------|

| 67_68         | Type number           | Flash |              |                     | SRAM (k | B)  |       | Ethernet | USB                      | SD/MMC | GP DMA | C   | hanne | ls  | Temp range        |

|               |                       | (kB)  | Local<br>bus | Ethernet<br>buffers | GP/USB  | RTC | Total |          | device +<br>4 kB<br>FIFO |        |        | CAN | ADC   | DAC | -                 |

|               | LPC2364FBD100         | 128   | 8            | 16                  | 8       | 2   | 34    | RMII     | yes                      | no     | yes    | 2   | 6     | 1   | –40 °C to +85 °C  |

|               | LPC2364HBD100         | 128   | 8            | 16                  | 8       | 2   | 34    | RMII     | yes                      | no     | yes    | 2   | 6     | 1   | –40 °C to +125 °C |

|               | LPC2364FET100         | 128   | 8            | 16                  | 8       | 2   | 34    | RMII     | yes                      | no     | yes    | 2   | 6     | 1   | –40 °C to +85 °C  |

|               | LPC2365FBD100         | 256   | 32           | 16                  | 8       | 2   | 58    | RMII     | no                       | no     | yes    | -   | 6     | 1   | –40 °C to +85 °C  |

|               | LPC2366FBD100         | 256   | 32           | 16                  | 8       | 2   | 58    | RMII     | yes                      | no     | yes    | 2   | 6     | 1   | –40 °C to +85 °C  |

| A             | LPC2367FBD100         | 512   | 32           | 16                  | 8       | 2   | 58    | RMII     | no                       | yes    | yes    | -   | 6     | 1   | –40 °C to +85 °C  |

| informa       | LPC2368FBD100         | 512   | 32           | 16                  | 8       | 2   | 58    | RMII     | yes                      | yes    | yes    | 2   | 6     | 1   | –40 °C to +85 °C  |

| ution prov    | LPC2368FET100         | 512   | 32           | 16                  | 8       | 2   | 58    | RMII     | yes                      | yes    | yes    | 2   | 6     | 1   | –40 °C to +85 °C  |

Rev. 7.1 — 16 October 2013 rided in this document is subject to legal disclaimers

Product data sheet

### Single-chip 16-bit/32-bit microcontrollers

|     | e 3. Pin allocation ta              |     |                                   |     |                                   |     |                                   |

|-----|-------------------------------------|-----|-----------------------------------|-----|-----------------------------------|-----|-----------------------------------|

|     | Symbol                              | Pin | Symbol                            | Pin | Symbol                            | Pin | Symbol                            |

| Rov | / A                                 |     |                                   |     |                                   |     |                                   |

| 1   | TDO                                 | 2   | P0[3]/RXD0                        | 3   | V <sub>DD(3V3)</sub>              | 4   | P1[4]/ENET_TX_EN                  |

| 5   | P1[10]/ENET_RXD1                    | 6   | P1[16]/ENET_MDC                   | 7   | V <sub>DD(DCDC)(3V3)</sub>        | 8   | P0[4]/I2SRX_CLK/<br>RD2/CAP2[0]   |

| 9   | P0[7]/I2STX_CLK/<br>SCK1/MAT2[1]    | 10  | P0[9]/I2STX_SDA/<br>MOSI1/MAT2[3] | 11  | -                                 | 12  | -                                 |

| Rov | ιВ                                  |     |                                   |     |                                   |     |                                   |

| 1   | TMS                                 | 2   | RTCK                              | 3   | V <sub>SS</sub>                   | 4   | P1[1]/ENET_TXD1                   |

| 5   | P1[9]/ENET_RXD0                     | 6   | P1[17]/<br>ENET_MDIO              | 7   | V <sub>SS</sub>                   | 8   | P0[6]/I2SRX_SDA/<br>SSEL1/MAT2[0] |

| 9   | P2[0]/PWM1[1]/<br>TXD1/TRACECLK     | 10  | P2[1]/PWM1[2]/<br>RXD1/PIPESTAT0  | 11  | -                                 | 12  | -                                 |

| Rov | / C                                 | !   |                                   | _!  |                                   | _!  |                                   |

| 1   | ТСК                                 | 2   | TRST                              | 3   | TDI                               | 4   | P0[2]/TXD0                        |

| 5   | P1[8]/ENET_CRS                      | 6   | P1[15]/<br>ENET_REF_CLK           | 7   | P4[28]/MAT2[0]/<br>TXD3           | 8   | P0[8]/I2STX_WS/<br>MISO1/MAT2[2]  |

| 9   | V <sub>SS</sub>                     | 10  | V <sub>DD(3V3)</sub>              | 11  | -                                 | 12  | -                                 |

| Rov | <i>i</i> D                          | I   |                                   |     |                                   |     |                                   |

| 1   | P0[24]/AD0[1]/<br>I2SRX_WS/CAP3[1]  | 2   | P0[25]/AD0[2]/<br>I2SRX_SDA/TXD3  | 3   | P0[26]/AD0[3]/<br>AOUT/RXD3       | 4   | DBGEN                             |

| 5   | P1[0]/ENET_TXD0                     | 6   | P1[14]/ENET_RX_ER                 | 7   | P0[5]/l2SRX_WS/<br>TD2/CAP2[1]    | 8   | P2[2]/PWM1[3]/<br>CTS1/PIPESTAT1  |

| 9   | P2[4]/PWM1[5]/<br>DSR1/TRACESYNC    | 10  | P2[5]/PWM1[6]/<br>DTR1/TRACEPKT0  | 11  | •                                 | 12  | -                                 |

| Rov | / E                                 |     |                                   |     |                                   |     |                                   |

| 1   | V <sub>SSA</sub>                    | 2   | V <sub>DDA</sub>                  | 3   | VREF                              | 4   | V <sub>DD(DCDC)(3V3)</sub>        |

| 5   | P0[23]/AD0[0]/<br>I2SRX_CLK/CAP3[0] | 6   | P4[29]/MAT2[1]/<br>RXD3           | 7   | P2[3]/PWM1[4]/<br>DCD1/PIPESTAT2  | 8   | P2[6]/PCAP1[0]/RI1/<br>TRACEPKT1  |

| 9   | P2[7]/RD2/<br>RTS1/TRACEPKT2        | 10  | P2[8]/TD2/<br>TXD2/TRACEPKT3      | 11  | -                                 | 12  | -                                 |

| Rov | / F                                 |     |                                   |     |                                   |     |                                   |

| 1   | V <sub>SS</sub>                     | 2   | RTCX1                             | 3   | RESET                             | 4   | P1[31]/SCK1/<br>AD0[5]            |

| 5   | P1[21]/PWM1[3]/<br>SSEL0            | 6   | P0[18]/DCD1/<br>MOSI0/MOSI        | 7   | P2[9]/USB_CONNECT/<br>RXD2/EXTIN0 | 8   | P0[16]/RXD1/<br>SSEL0/SSEL        |

| 9   | P0[17]/CTS1/<br>MISO0/MISO          | 10  | P0[15]/TXD1/<br>SCK0/SCK          | 11  | -                                 | 12  | -                                 |

| Rov | / G                                 |     |                                   |     |                                   |     |                                   |

| 1   | RTCX2                               | 2   | VBAT                              | 3   | XTAL2                             | 4   | P0[30]/USB_D-                     |

| 5   | P1[25]/MAT1[1]                      | 6   | P1[29]/PCAP1[1]/<br>MAT0[1]       | 7   | V <sub>SS</sub>                   | 8   | P0[21]/RI1/<br>MCIPWR/RD1         |

| 9   | P0[20]/DTR1/<br>MCICMD/SCL1         | 10  | P0[19]/DSR1/<br>MCICLK/SDA1       | 11  | -                                 | 12  | -                                 |

#### Table 3. Pin allocation table

Row H

#### Single-chip 16-bit/32-bit microcontrollers

| Pin | Symbol                             | Pin | Symbol                            | Pin | Symbol                      | Pin | Symbol                  |  |  |

|-----|------------------------------------|-----|-----------------------------------|-----|-----------------------------|-----|-------------------------|--|--|

| Rov | v J                                |     |                                   |     |                             |     |                         |  |  |

| 1   | P0[28]/SCL0                        | 2   | P0[27]/SDA0                       | 3   | P0[29]/USB_D+               | 4   | P1[19]/CAP1[1]          |  |  |

| 5   | P1[22]/MAT1[0]                     | 6   | V <sub>SS</sub>                   | 7   | P1[28]/PCAP1[0]/<br>MAT0[0] | 8   | P0[1]/TD1/RXD3/SCL1     |  |  |

| 9   | P2[13]/EINT3/<br>MCIDAT3/I2STX_SDA | 10  | P2[10]/EINT0                      | 11  | -                           | 12  | -                       |  |  |

| Rov | v K                                |     |                                   |     |                             |     |                         |  |  |

| 1   | P3[26]/MAT0[1]/<br>PWM1[3]         | 2   | V <sub>DD(3V3)</sub>              | 3   | V <sub>SS</sub>             | 4   | P1[20]/PWM1[2]/<br>SCK0 |  |  |

| 5   | P1[23]/PWM1[4]/<br>MISO0           | 6   | P1[26]/PWM1[6]/<br>CAP0[0]        | 7   | P1[27]/CAP0[1]              | 8   | P0[0]/RD1/TXD3/SDA1     |  |  |

| 9   | P0[11]/RXD2/<br>SCL2/MAT3[1]       | 10  | P2[12]/EINT2/<br>MCIDAT2/I2STX_WS | 11  | -                           | 12  | -                       |  |  |

#### Table 3. Pin allocation table ...continued

### 6.2 Pin description

| Symbol                      | Pin           | Ball              | Туре                                              | Description                                                                                                                                                                                                                                       |

|-----------------------------|---------------|-------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[0] to P0[31]             |               |                   | I/O                                               | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of Port 0 pins depends upon the pin function selected via the pin connect block. Pins 12, 13, 14, and 31 of this port are not available |

| P0[0]/RD1/TXD3/ 46[1] K8[1] |               | I/O               | P0[0] — General purpose digital input/output pin. |                                                                                                                                                                                                                                                   |

| SDA1                        |               |                   | I                                                 | RD1 — CAN1 receiver input. (LPC2364/66/68 only)                                                                                                                                                                                                   |

|                             |               |                   | 0                                                 | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                              |

|                             |               |                   | I/O                                               | <b>SDA1</b> — I <sup>2</sup> C1 data input/output (this is not an open-drain pin).                                                                                                                                                                |

| P0[1]/TD1/RXD3/             | 47 <u>[1]</u> | J8 <u>[1]</u>     | I/O                                               | P0[1] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| SCL1                        |               |                   | 0                                                 | TD1 — CAN1 transmitter output. (LPC2364/66/68 only)                                                                                                                                                                                               |

|                             |               |                   | Ι                                                 | <b>RXD3</b> — Receiver input for UART3.                                                                                                                                                                                                           |

|                             |               |                   | I/O                                               | SCL1 — I <sup>2</sup> C1 clock input/output (this is not an open-drain pin).                                                                                                                                                                      |

| P0[2]/TXD0                  | 98 <u>[1]</u> | C4[1]             | I/O                                               | P0[2] — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                             |               |                   | 0                                                 | TXD0 — Transmitter output for UART0.                                                                                                                                                                                                              |

| P0[3]/RXD0                  | 99 <u>[1]</u> | A2[1]             | I/O                                               | P0[3] — General purpose digital input/output pin.                                                                                                                                                                                                 |

|                             |               |                   | I                                                 | <b>RXD0</b> — Receiver input for UART0.                                                                                                                                                                                                           |

| P0[4]/                      | 81 <u>[1]</u> | A8[1]             | I/O                                               | P0[4] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| I2SRX_CLK/<br>RD2/CAP2[0]   |               |                   | I/O                                               | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>P</i> S-bus specification.                                                                                        |

|                             |               |                   | Ι                                                 | RD2 — CAN2 receiver input. (LPC2364/66/68 only)                                                                                                                                                                                                   |

|                             |               |                   | Ι                                                 | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                                                                                                   |

| P0[5]/                      | 80 <u>[1]</u> | D7 <u>[1]</u>     | I/O                                               | P0[5] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| I2SRX_WS/<br>TD2/CAP2[1]    |               |                   | I/O                                               | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.                                                                                       |

|                             |               |                   | 0                                                 | TD2 — CAN2 transmitter output. (LPC2364/66/68 only)                                                                                                                                                                                               |

|                             |               |                   | Ι                                                 | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                                                                                                   |

| P0[6]/                      | 79 <u>[1]</u> | B8[1]             | I/O                                               | P0[6] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| I2SRX_SDA/<br>SSEL1/MAT2[0] |               |                   | I/O                                               | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification.                                                                         |

|                             |               |                   | I/O                                               | SSEL1 — Slave Select for SSP1.                                                                                                                                                                                                                    |

|                             |               |                   | 0                                                 | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                                                    |

| P0[7]/                      | 78 <u>[1]</u> | A9[1]             | I/O                                               | P0[7] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| I2STX_CLK/<br>SCK1/MAT2[1]  |               |                   | I/O                                               | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $l^2S$ -bus specification.                                                                                          |

|                             |               |                   | I/O                                               | SCK1 — Serial Clock for SSP1.                                                                                                                                                                                                                     |

|                             |               |                   | 0                                                 | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                                                    |

| P0[8]/                      | 77 <u>[1]</u> | C8 <sup>[1]</sup> | I/O                                               | P0[8] — General purpose digital input/output pin.                                                                                                                                                                                                 |

| I2STX_WS/<br>MISO1/MAT2[2]  |               |                   | I/O                                               | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification.                                                                                        |

|                             |               |                   | I/O                                               | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                                                                             |

|                             |               |                   | 0                                                 | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                                                                                                    |

#### Single-chip 16-bit/32-bit microcontrollers

| Table 4.         Pin descriptioncontinued |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

| Symbol                | Pin             | Ball                     | Туре | Description                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|-----------------------|-----------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[21]/RI1/           | 57 <u>[1]</u>   | G8 <u>[1]</u>            | I/O  | P0[21] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| MCIPWR/RD1            |                 |                          | I    | RI1 — Ring Indicator input for UART1.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | 0    | <b>MCIPWR</b> — Power Supply Enable for external SD/MMC power supply. (LPC2367/68 only)                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I    | RD1 — CAN1 receiver input. (LPC2364/66/68 only)                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[22]/RTS1/          | 56 <u>[1]</u>   | H10 <sup>[1]</sup>       | I/O  | P0[22] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| MCIDAT0/TD1           |                 |                          | 0    | RTS1 — Request to Send output for UART1.                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | 0    | MCIDAT0 — Data line for SD/MMC interface. (LPC2367/68 only)                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | 0    | TD1 — CAN1 transmitter output. (LPC2364/66/68 only)                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[23]/AD0[0]/        | 9 <u>[2]</u>    | E5[2]                    | I/O  | P0[23] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| I2SRX_CLK/<br>CAP3[0] |                 |                          | I    | AD0[0] — A/D converter 0, input 0.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| CAPS[0]               |                 |                          | I/O  | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $l^2$ S-bus specification.                                                                                                       |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I    | CAP3[0] — Capture input for Timer 3, channel 0.                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[24]/AD0[1]/        |                 |                          | I/O  | P0[24] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| I2SRX_WS/<br>CAP3[1]  |                 |                          | I    | AD0[1] — A/D converter 0, input 1.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| AF3[1]                |                 |                          | I/O  | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> S-bus specification.                                                                                   |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I    | CAP3[1] — Capture input for Timer 3, channel 1.                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[25]/AD0[2]/        | 7 <u>[2]</u>    | 7[2] D2[2]               |      | P0[25] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| 2SRX_SDA/<br>TXD3     |                 |                          | I    | AD0[2] — A/D converter 0, input 2.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| 1703                  |                 |                          |      |                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  | I/O | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification. |

|                       |                 |                          | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[26]/AD0[3]/        | 6 <u>[3]</u>    | D3 <u>[3]</u>            | I/O  | P0[26] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| AOUT/RXD3             |                 |                          | I    | AD0[3] — A/D converter 0, input 3.                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | 0    | AOUT — D/A converter output.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I    | <b>RXD3</b> — Receiver input for UART3.                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[27]/SDA0           | 25 <u>[4]</u>   | J2[4]                    | I/O  | P0[27] — General purpose digital input/output pin. Output is open-drain.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I/O  | <b>SDA0</b> — I <sup>2</sup> C0 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                   |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[28]/SCL0           | 24 <u>[4]</u>   | J1 <u><sup>[4]</sup></u> | I/O  | P0[28] — General purpose digital input/output pin. Output is open-drain.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I/O  | <b>SCL0</b> — I <sup>2</sup> C0 clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                                                  |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       | - 29 <u>[5]</u> | J3[5]                    | I/O  | P0[29] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I/O  | USB_D+ — USB bidirectional D+ line. (LPC2364/66/68 only)                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P0[30]/USB_D-         | - 30 <u>[5]</u> | G4 <u><sup>[5]</sup></u> | I/O  | P0[30] — General purpose digital input/output pin.                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

|                       |                 |                          | I/O  | USB_D- — USB bidirectional D- line. (LPC2364/66/68 only)                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

| P1[0] to P1[31]       |                 |                          | I/O  | <b>Port 1:</b> Port 1 is a 32-bit I/O port with individual direction controls for each bit. The operation of Port 1 pins depends upon the pin function selected via the pin connect block. Pins 2, 3, 5, 6, 7, 11, 12, and 13 of this port are not available. |  |  |  |  |  |  |  |  |  |     |                                                                                                                                                           |

#### Single-chip 16-bit/32-bit microcontrollers

| Table 4. Pin de             | scriptior     | <b>1</b> continue         | ed                                                |                                                                                                                                                          |  |  |  |   |                                                                                                                                                                           |

|-----------------------------|---------------|---------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                      | Pin           | Ball                      | Туре                                              | Description                                                                                                                                              |  |  |  |   |                                                                                                                                                                           |

| P2[3]/PWM1[4]/              | 70 <u>[1]</u> | E7 <u>[1]</u>             | I/O                                               | P2[3] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

| DCD1/<br>PIPESTAT2          |               |                           | 0                                                 | PWM1[4] — Pulse Width Modulator 1, channel 4 output.                                                                                                     |  |  |  |   |                                                                                                                                                                           |

| FIFLOIAIZ                   |               |                           | I                                                 | DCD1 — Data Carrier Detect input for UART1.                                                                                                              |  |  |  |   |                                                                                                                                                                           |

|                             |               | 0                         | PIPESTAT2 — Pipeline Status, bit 2.               |                                                                                                                                                          |  |  |  |   |                                                                                                                                                                           |

| P2[4]/PWM1[5]/              | 69 <u>[1]</u> | D9 <u>[1]</u>             | I/O                                               | P2[4] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

| DSR1/<br>TRACESYNC          |               |                           | 0                                                 | PWM1[5] — Pulse Width Modulator 1, channel 5 output.                                                                                                     |  |  |  |   |                                                                                                                                                                           |

| TRACESTINC                  |               |                           | I                                                 | DSR1 — Data Set Ready input for UART1.                                                                                                                   |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | TRACESYNC — Trace Synchronization.                                                                                                                       |  |  |  |   |                                                                                                                                                                           |

| P2[5]/PWM1[6]/              | 68 <u>[1]</u> | D10 <sup>[1]</sup>        | I/O                                               | P2[5] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

| DTR1/<br>TRACEPKT0          |               |                           | 0                                                 | PWM1[6] — Pulse Width Modulator 1, channel 6 output.                                                                                                     |  |  |  |   |                                                                                                                                                                           |

| TRACEPKIU                   |               |                           | 0                                                 | DTR1 — Data Terminal Ready output for UART1.                                                                                                             |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | TRACEPKT0 — Trace Packet, bit 0.                                                                                                                         |  |  |  |   |                                                                                                                                                                           |

| P2[6]/PCAP1[0]/             | 67 <u>[1]</u> | E8[1]                     | I/O                                               | P2[6] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

| RI1/                        |               |                           | I                                                 | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                            |  |  |  |   |                                                                                                                                                                           |

| TRACEPKT1                   |               |                           | I                                                 | RI1 — Ring Indicator input for UART1.                                                                                                                    |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | TRACEPKT1 — Trace Packet, bit 1.                                                                                                                         |  |  |  |   |                                                                                                                                                                           |

| 2[7]/RD2/ 66[1] E9[1]       |               | I/O                       | P2[7] — General purpose digital input/output pin. |                                                                                                                                                          |  |  |  |   |                                                                                                                                                                           |

| RTS1/<br>TRACEPKT2          |               |                           | I                                                 | RD2 — CAN2 receiver input. (LPC2364/66/68 only)                                                                                                          |  |  |  |   |                                                                                                                                                                           |

| TRAGEFR12                   |               |                           | 0                                                 | RTS1 — Request to Send output for UART1.                                                                                                                 |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | TRACEPKT2 — Trace Packet, bit 2.                                                                                                                         |  |  |  |   |                                                                                                                                                                           |

| P2[8]/TD2/                  | 65 <u>[1]</u> | E10 <sup>[1]</sup>        | I/O                                               | P2[8] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

| TXD2/<br>TRACEPKT3          |               |                           | 0                                                 | TD2 — CAN2 transmitter output. (LPC2364/66/68 only)                                                                                                      |  |  |  |   |                                                                                                                                                                           |

| TRACEFRIS                   |               |                           | 0                                                 | <b>TXD2</b> — Transmitter output for UART2.                                                                                                              |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | TRACEPKT3 — Trace Packet, bit 3.                                                                                                                         |  |  |  |   |                                                                                                                                                                           |

| P2[9]/                      | 64 <u>[1]</u> | F7 <u>[1]</u>             | I/O                                               | P2[9] — General purpose digital input/output pin.                                                                                                        |  |  |  |   |                                                                                                                                                                           |

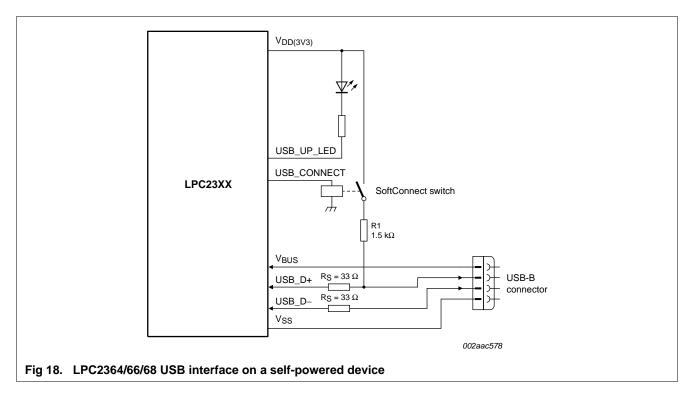

| USB_CONNECT/<br>RXD2/EXTIN0 |               |                           |                                                   |                                                                                                                                                          |  |  |  | 0 | <b>USB_CONNECT</b> — Signal used to switch an external $1.5 \text{ k}\Omega$ resistor under software control. Used with the SoftConnect USB feature. (LPC2364/66/68 only) |

|                             |               |                           | I                                                 | <b>RXD2</b> — Receiver input for UART2.                                                                                                                  |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | I                                                 | EXTINO — External Trigger Input.                                                                                                                         |  |  |  |   |                                                                                                                                                                           |

| P2[10]/EINT0                | 53 <u>[6]</u> | J10 <u><sup>[6]</sup></u> | I/O                                               | P2[10] — General purpose digital input/output pin.                                                                                                       |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           |                                                   | <b>Note:</b> LOW on this pin while RESET is LOW forces on-chip bootloader to take over control of the part after a reset.                                |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | I                                                 | EINT0 — External interrupt 0 input.                                                                                                                      |  |  |  |   |                                                                                                                                                                           |

| P2[11]/EINT1/               | 52 <u>[6]</u> | H8 <u><sup>[6]</sup></u>  | I/O                                               | P2[11] — General purpose digital input/output pin.                                                                                                       |  |  |  |   |                                                                                                                                                                           |

| MCIDAT1/<br>I2STX_CLK       |               |                           | Ι                                                 | EINT1 — External interrupt 1 input.                                                                                                                      |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | 0                                                 | MCIDAT1 — Data line for SD/MMC interface. (LPC2367/68 only)                                                                                              |  |  |  |   |                                                                                                                                                                           |

|                             |               |                           | I/O                                               | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $l^2S$ -bus specification. |  |  |  |   |                                                                                                                                                                           |

#### Table 4. Pin description continued

#### Single-chip 16-bit/32-bit microcontrollers

| Table 4.                | Pin desc             | ription                                     | continued                                                  | 1    |                                                                                                                                                                                                                        |

|-------------------------|----------------------|---------------------------------------------|------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                  | Р                    | in                                          | Ball                                                       | Туре | Description                                                                                                                                                                                                            |

| RSTOUT                  | 14                   | 4                                           | -                                                          | 0    | <b>RSTOUT</b> — This is a 3.3 V pin. LOW on this pin indicates LPC2364/65/66/67/68 being in Reset state.                                                                                                               |

|                         |                      |                                             |                                                            |      | <b>Note:</b> This pin is available in LPC2364FBD100, LPC2365FBD100, LPC2366FBD100, LPC2367FBD100, and LPC2368FBD100 devices only (LQFP100 package).                                                                    |

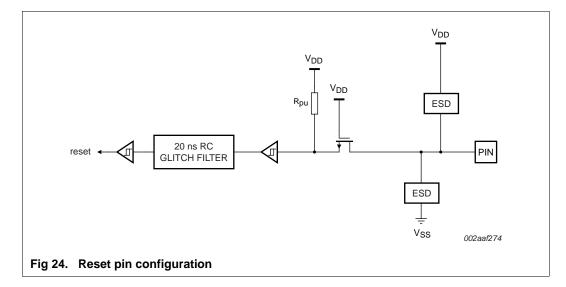

| RESET                   | 17                   | 7 <u>[9]</u>                                | F3 <sup>[9]</sup>                                          | I    | <b>External reset input:</b> A LOW on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. TTL with hysteresis, 5 V tolerant. |

| XTAL1                   | 22                   | 2[10][11]                                   | H2 <sup>[10][11]</sup>                                     | 1    | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                                 |

| XTAL2                   | 23                   | 3 <u>[10][11]</u>                           | G3 <sup>[10][11]</sup>                                     | 0    | Output from the oscillator amplifier.                                                                                                                                                                                  |

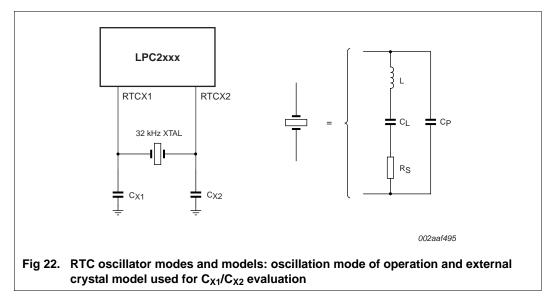

| RTCX1                   | 16                   | 6 <u>[10][12]</u>                           | F2 <sup>[10][12]</sup>                                     | I    | Input to the RTC oscillator circuit.                                                                                                                                                                                   |

| RTCX2                   | 18                   | 8 <u>[10]</u>                               | G1 <sup>[10]</sup>                                         | 0    | Output from the RTC oscillator circuit.                                                                                                                                                                                |

| V <sub>SS</sub>         | 4 <sup>-</sup><br>72 | 5, 31,<br>1, 55,<br>2, 97,<br>3 <u>[13]</u> | B3, B7,<br>C9, F1,<br>G7, J6,<br>K3 <u><sup>[13]</sup></u> | I    | ground: 0 V reference.                                                                                                                                                                                                 |

| V <sub>SSA</sub>        | 11                   | 1 <u>[14]</u>                               | E1 <sup>[14]</sup>                                         | I    | <b>analog ground:</b> 0 V reference. This should nominally be the same voltage as $V_{SS}$ , but should be isolated to minimize noise and error.                                                                       |

| V <sub>DD(3V3)</sub>    | 7                    | 8, 54,<br>1,<br>6 <u><sup>[15]</sup></u>    | A3, C10,<br>H9,<br>K2 <sup>[15]</sup>                      | I    | <b>3.3 V supply voltage:</b> This is the power supply voltage for the I/O ports.                                                                                                                                       |

| V <sub>DD(DCDC)(3</sub> |                      | 3, 42,<br>4 <u>[16]</u>                     | A7, E4,<br>H6 <u><sup>[16]</sup></u>                       | I    | <b>3.3 V DC-to-DC converter supply voltage:</b> This is the supply voltage for the on-chip DC-to-DC converter only.                                                                                                    |

| V <sub>DDA</sub>        | 10                   | 0[17]                                       | E2 <sup>[17]</sup>                                         | I    | <b>analog 3.3 V pad supply voltage:</b> This should be nominally the same voltage as $V_{DD(3V3)}$ but should be isolated to minimize noise and error. This voltage is used to power the ADC and DAC.                  |

| VREF                    | 12                   | 2[17]                                       | E3 <u>[17]</u>                                             | I    | <b>ADC reference:</b> This should be nominally the same voltage as $V_{DD(3V3)}$ but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC and DAC.                         |

| VBAT                    | 19                   | 9 <u>[17]</u>                               | G2 <sup>[17]</sup>                                         | I    | <b>RTC pin power supply:</b> 3.3 V on this pin supplies the power to the RTC peripheral.                                                                                                                               |

[1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis.

[2] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as a DAC input, digital section of the pad is disabled.

[3] 5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output, digital section of the pad is disabled.

[4] Open-drain 5 V tolerant digital I/O pad, compatible with I<sup>2</sup>C-bus 400 kHz specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I<sup>2</sup>C-bus is floating and does not disturb the I<sup>2</sup>C lines. Open-drain configuration applies to all functions on this pin.

[5] Pad provides digital I/O and USB functions (LPC2364/66/68 only). It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only).

[6] 5 V tolerant pad with 10 ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

[7] This pin has no built-in pull-up and no built-in pull-down resistor.

[8] This pin has a built-in pull-up resistor.

[9] 5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

[10] Pad provides special analog functionality.

[11] When the main oscillator is not used, connect XTAL1 and XTAL2 as follows: XTAL1 can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTAL2 should be left floating.

LPC2364 65 66 67 68

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two instruction sets:

- The standard 32-bit ARM set

- A 16-bit Thumb set

The Thumb set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM processor connected to a 16-bit memory system.

#### 7.2 On-chip flash programming memory

The LPC2364/65/66/67/68 incorporate a 128 kB, 256 kB, and 512 kB flash memory system respectively. This memory may be used for both code and data storage. Programming of the flash memory may be accomplished in several ways. It may be programmed In System via the serial port (UART0). The application program may also erase and/or program the flash while the application is running, allowing a great degree of flexibility for data storage field and firmware upgrades.

The flash memory is 128 bits wide and includes pre-fetching and buffering techniques to allow it to operate at SRAM speeds of 72 MHz. LPC2364HBD flash operates up to 72 MHz from -40 °C to +85 °C, up to 60 MHz from 85 °C to 125 °C.

#### 7.3 On-chip SRAM

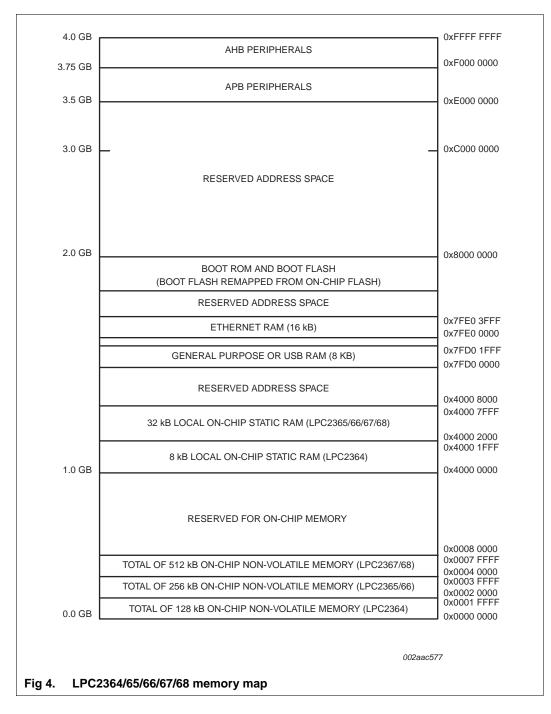

The LPC2364/65/66/67/68 include SRAM memory of 8 kB or 32 kB, reserved for the ARM processor exclusive use. This RAM may be used for code and/or data storage and may be accessed as 8 bits, 16 bits, and 32 bits.

A 16 kB SRAM block serving as a buffer for the Ethernet controller and an 8 kB SRAM used by the GPDMA controller or the USB device can be used both for data and code storage. The 2 kB RTC SRAM can be used for data storage only. The RTC SRAM is battery powered and retains the content in the absence of the main power supply.

#### 7.4 Memory map

The LPC2364/65/66/67/68 memory map incorporates several distinct regions as shown in Figure 4.

In addition, the CPU interrupt vectors may be remapped to allow them to reside in either flash memory (default), boot ROM, or SRAM (see <u>Section 7.25.6</u>).

#### Single-chip 16-bit/32-bit microcontrollers

#### 7.5 Interrupt controller

The ARM processor core has two interrupt inputs called Interrupt Request (IRQ) and Fast Interrupt Request (FIQ). The VIC takes 32 interrupt request inputs which can be programmed as FIQ or vectored IRQ types. The programmable assignment scheme means that priorities of interrupts from the various peripherals can be dynamically assigned and adjusted.

LPC2364\_65\_66\_67\_68

• Double buffer implementation for Bulk and Isochronous endpoints.

#### 7.11 CAN controller and acceptance filters (LPC2364/66/68 only)

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router among a number of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

#### 7.11.1 Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

#### 7.12 10-bit ADC

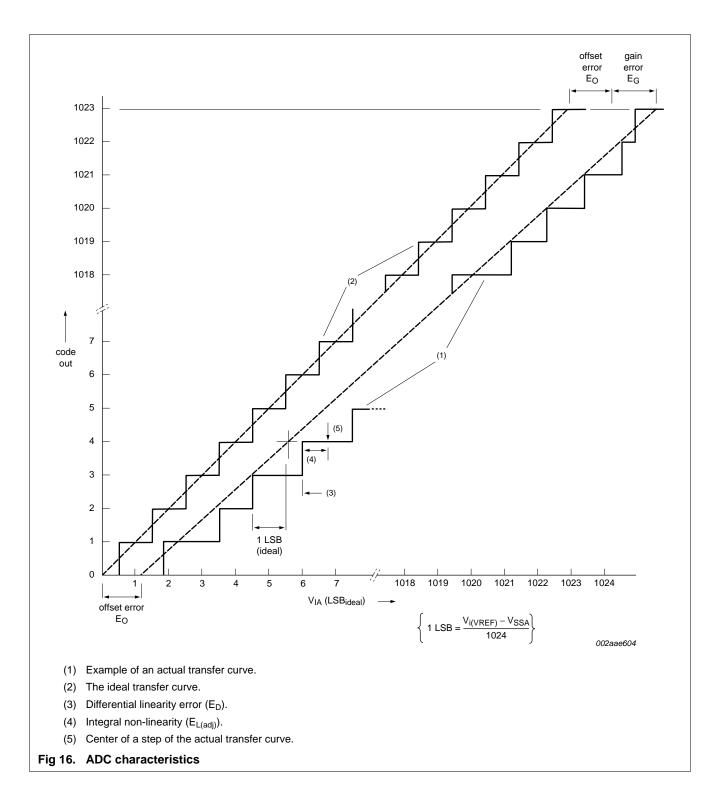

The LPC2364/65/66/67/68 contain one ADC. It is a single 10-bit successive approximation ADC with six channels.

#### 7.12.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 6 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>i(VREF)</sub>.

- 10-bit conversion time  $\geq$  2.44  $\mu$ s.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{32} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the RTC clock, the Internal RC oscillator (IRC), or the APB peripheral clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring, for increased reliability.

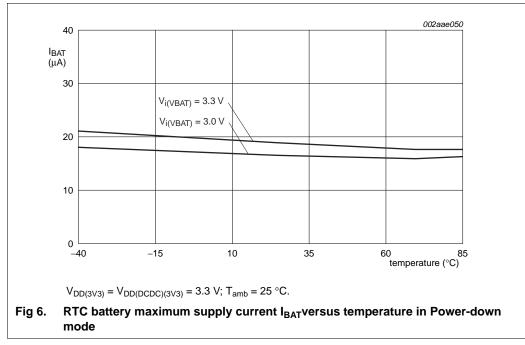

#### 7.23 RTC and battery RAM

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. It uses little power in Power-down and Deep power-down modes. On the LPC2364/65/66/67/68, the RTC can be clocked by a separate 32.768 kHz oscillator, or by a programmable prescale divider based on the APB clock. Also, the RTC is powered by its own power supply pin, VBAT, which can be connected to a battery or to the same 3.3 V supply used by the rest of the device.

The VBAT pin supplies power only to the RTC and the battery RAM. These two functions require a minimum of power to operate, which can be supplied by an external battery.

#### 7.23.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated 32 kHz oscillator or programmable prescaler from APB clock.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- Periodic interrupts can be generated from increments of any field of the time registers, and selected fractional second values.

- 2 kB data SRAM powered by VBAT.

- RTC and battery RAM power supply is isolated from the rest of the chip.

#### 7.24 Clocking and power control

#### 7.24.1 Crystal oscillators

The LPC2364/65/66/67/68 includes three independent oscillators. These are the Main Oscillator, the Internal RC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the PLL and ultimately the CPU.

Following reset, the LPC2364/65/66/67/68 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

#### 7.25.6 Memory mapping control

The memory mapping control alters the mapping of the interrupt vectors that appear at the beginning at address 0x0000 0000. Vectors may be mapped to the bottom of the Boot ROM or the SRAM. This allows code running in different memory spaces to have control of the interrupts.

#### 7.26 Emulation and debugging

The LPC2364/65/66/67/68 support emulation and debugging via a JTAG serial port. A trace port allows tracing program execution. Debugging and trace functions are multiplexed only with GPIOs on P2[0] to P2[9]. This means that all communication, timer, and interface peripherals residing on other pins are available during the development and debugging phase as they are when the application is run in the embedded system itself.