Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                           |

| Core Processor             | ARM7®                                                                         |

| Core Size                  | 16/32-Bit                                                                     |

| Speed                      | 72MHz                                                                         |

| Connectivity               | Ethernet, I <sup>2</sup> C, Microwire, Memory Card, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                  |

| Number of I/O              | 70                                                                            |

| Program Memory Size        | 512KB (512K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 58K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 6x10b; D/A 1x10b                                                          |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-LQFP                                                                      |

| Supplier Device Package    | 100-LQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2367fbd100-551     |

Table 3. Pin allocation table ...continued

| Pin | Symbol                              | Pin | Symbol                      | Pin | Symbol                       | Pin | Symbol                                |

|-----|-------------------------------------|-----|-----------------------------|-----|------------------------------|-----|---------------------------------------|

| 1   | P1[30]/V <sub>BUS</sub> /<br>AD0[4] | 2   | XTAL1                       | 3   | P3[25]/MAT0[0]/<br>PWM1[2]   | 4   | P1[18]/USB_UP_LED/<br>PWM1[1]/CAP1[0] |

| 5   | P1[24]/PWM1[5]/<br>MOSI0            | 6   | V <sub>DD(DCDC)(3V3)</sub>  | 7   | P0[10]/TXD2/<br>SDA2/MAT3[0] | 8   | P2[11]/EINT1/<br>MCIDAT1/I2STX_CLK    |

| 9   | V <sub>DD(3V3)</sub>                | 10  | P0[22]/RTS1/<br>MCIDAT0/TD1 | 11  | -                            | 12  | -                                     |

# 6.2 Pin description

Table 4. Pin description

| Symbol                      | Pin               | Ball          | Type                                                                                                                                                                                                                                               | Description                                                                                                                                                                  |  |

|-----------------------------|-------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P0[0] to P0[31]             |                   | I/O           | <b>Port 0:</b> Port 0 is a 32-bit I/O port with individual direction controls for each bit. The operation of Port 0 pins depends upon the pin function selected via the pin connect block. Pins 12, 13, 14, and 31 of this port are not available. |                                                                                                                                                                              |  |

| P0[0]/RD1/TXD3/             | 46 <sup>[1]</sup> | K8[1]         | I/O                                                                                                                                                                                                                                                | P0[0] — General purpose digital input/output pin.                                                                                                                            |  |

| SDA1                        |                   |               | 1                                                                                                                                                                                                                                                  | RD1 — CAN1 receiver input. (LPC2364/66/68 only)                                                                                                                              |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | TXD3 — Transmitter output for UART3.                                                                                                                                         |  |

|                             |                   |               | I/O                                                                                                                                                                                                                                                | SDA1 — I <sup>2</sup> C1 data input/output (this is not an open-drain pin).                                                                                                  |  |

| P0[1]/TD1/RXD3/             | 47 <u>[1]</u>     | J8 <u>[1]</u> | I/O                                                                                                                                                                                                                                                | P0[1] — General purpose digital input/output pin.                                                                                                                            |  |

| SCL1                        |                   |               | 0                                                                                                                                                                                                                                                  | TD1 — CAN1 transmitter output. (LPC2364/66/68 only)                                                                                                                          |  |

|                             |                   |               | I                                                                                                                                                                                                                                                  | RXD3 — Receiver input for UART3.                                                                                                                                             |  |

|                             |                   |               | I/O                                                                                                                                                                                                                                                | SCL1 — I <sup>2</sup> C1 clock input/output (this is not an open-drain pin).                                                                                                 |  |

| P0[2]/TXD0                  | 98 <u>[1]</u>     | C4[1]         | I/O                                                                                                                                                                                                                                                | P0[2] — General purpose digital input/output pin.                                                                                                                            |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | TXD0 — Transmitter output for UART0.                                                                                                                                         |  |

| P0[3]/RXD0                  | 99 <u>[1]</u>     | A2[1]         | I/O                                                                                                                                                                                                                                                | P0[3] — General purpose digital input/output pin.                                                                                                                            |  |

|                             |                   |               | I                                                                                                                                                                                                                                                  | <b>RXD0</b> — Receiver input for UART0.                                                                                                                                      |  |

| P0[4]/                      | 81 <u>[1]</u>     | A8[1]         | I/O                                                                                                                                                                                                                                                | P0[4] — General purpose digital input/output pin.                                                                                                                            |  |

| I2SRX_CLK/<br>RD2/CAP2[0]   |                   |               | I/O                                                                                                                                                                                                                                                | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus specification</i> .                   |  |

|                             |                   |               | I                                                                                                                                                                                                                                                  | RD2 — CAN2 receiver input. (LPC2364/66/68 only)                                                                                                                              |  |

|                             |                   |               | I                                                                                                                                                                                                                                                  | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                              |  |

| P0[5]/                      | 80 <u>[1]</u>     | D7[1]         | I/O                                                                                                                                                                                                                                                | P0[5] — General purpose digital input/output pin.                                                                                                                            |  |

| I2SRX_WS/<br>TD2/CAP2[1]    |                   |               | I/O                                                                                                                                                                                                                                                | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.                  |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | TD2 — CAN2 transmitter output. (LPC2364/66/68 only)                                                                                                                          |  |

|                             |                   |               | I                                                                                                                                                                                                                                                  | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                              |  |

| P0[6]/                      | 79 <u>[1]</u>     | B8[1]         | I/O                                                                                                                                                                                                                                                | P0[6] — General purpose digital input/output pin.                                                                                                                            |  |

| I2SRX_SDA/<br>SSEL1/MAT2[0] |                   |               | I/O                                                                                                                                                                                                                                                | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $\ell$ S-bus specification.                   |  |

|                             |                   |               | I/O                                                                                                                                                                                                                                                | SSEL1 — Slave Select for SSP1.                                                                                                                                               |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                               |  |

| P0[7]/                      | 78 <u>[1]</u>     | A9[1]         | I/O                                                                                                                                                                                                                                                | P0[7] — General purpose digital input/output pin.                                                                                                                            |  |

| I2STX_CLK/<br>SCK1/MAT2[1]  |                   |               | I/O                                                                                                                                                                                                                                                | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $\ell$ S-bus specification.                    |  |

|                             |                   |               | I/O                                                                                                                                                                                                                                                | SCK1 — Serial Clock for SSP1.                                                                                                                                                |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                               |  |

| P0[8]/                      | 77 <u>[1]</u>     | C8[1]         | I/O                                                                                                                                                                                                                                                | P0[8] — General purpose digital input/output pin.                                                                                                                            |  |

| I2STX_WS/<br>MISO1/MAT2[2]  |                   |               | I/O                                                                                                                                                                                                                                                | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>l</i> <sup>2</sup> S-bus specification. |  |

|                             |                   |               | I/O                                                                                                                                                                                                                                                | MISO1 — Master In Slave Out for SSP1.                                                                                                                                        |  |

|                             |                   |               | 0                                                                                                                                                                                                                                                  | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                               |  |

Table 4. Pin description ...continued

| Symbol                      | Pin           | Ball                     | Type | Description                                                                                                                                                   |

|-----------------------------|---------------|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0[9]/                      | 76 <u>[1]</u> | A10 <sup>[1]</sup>       | I/O  | P0[9] — General purpose digital input/output pin.                                                                                                             |

| I2STX_SDA/<br>MOSI1/MAT2[3] |               |                          | I/O  | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>PS-bus specification</i> . |

|                             |               |                          | I/O  | MOSI1 — Master Out Slave In for SSP1.                                                                                                                         |

|                             |               |                          | 0    | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                |

| P0[10]/TXD2/                | 48 <u>[1]</u> | H7 <u><sup>[1]</sup></u> | I/O  | P0[10] — General purpose digital input/output pin.                                                                                                            |

| SDA2/MAT3[0]                |               |                          | 0    | TXD2 — Transmitter output for UART2.                                                                                                                          |

|                             |               |                          | I/O  | SDA2 — I <sup>2</sup> C2 data input/output (this is not an open-drain pin).                                                                                   |

|                             |               |                          | 0    | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                |

| P0[11]/RXD2/                | 49 <u>[1]</u> | K9[1]                    | I/O  | P0[11] — General purpose digital input/output pin.                                                                                                            |

| SCL2/MAT3[1]                |               |                          | I    | RXD2 — Receiver input for UART2.                                                                                                                              |

|                             |               |                          | I/O  | SCL2 — I <sup>2</sup> C2 clock input/output (this is not an open-drain pin).                                                                                  |

|                             |               |                          | 0    | MAT3[1] — Match output for Timer 3, channel 1.                                                                                                                |

| P0[15]/TXD1/                | 62 <u>[1]</u> | F10 <sup>[1]</sup>       | I/O  | P0[15] — General purpose digital input/output pin.                                                                                                            |

| SCK0/SCK                    |               |                          | 0    | <b>TXD1</b> — Transmitter output for UART1.                                                                                                                   |

|                             |               |                          | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                 |

|                             |               |                          | I/O  | SCK — Serial clock for SPI.                                                                                                                                   |

| P0[16]/RXD1/                | 63 <u>[1]</u> | F8[1]                    | I/O  | P0[16] — General purpose digital input/output pin.                                                                                                            |

| SSEL0/SSEL                  |               |                          | 1    | RXD1 — Receiver input for UART1.                                                                                                                              |

|                             |               |                          | I/O  | SSEL0 — Slave Select for SSP0.                                                                                                                                |

|                             |               |                          | I/O  | SSEL — Slave Select for SPI.                                                                                                                                  |

| P0[17]/CTS1/                | 61 <u>[1]</u> | F9[1]                    | I/O  | P0[17] — General purpose digital input/output pin.                                                                                                            |

| MISO0/MISO                  |               |                          | I    | CTS1 — Clear to Send input for UART1.                                                                                                                         |

|                             |               |                          | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                         |

|                             |               |                          | I/O  | MISO — Master In Slave Out for SPI.                                                                                                                           |

| P0[18]/DCD1/                | 60 <u>[1]</u> | F6 <sup>[1]</sup>        | I/O  | P0[18] — General purpose digital input/output pin.                                                                                                            |

| MOSI0/MOSI                  |               |                          | I    | <b>DCD1</b> — Data Carrier Detect input for UART1.                                                                                                            |

|                             |               |                          | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                         |

|                             |               |                          | I/O  | MOSI — Master Out Slave In for SPI.                                                                                                                           |

| P0[19]/DSR1/                | 59 <u>[1]</u> | G10[1]                   | I/O  | P0[19] — General purpose digital input/output pin.                                                                                                            |

| MCICLK/SDA1                 |               |                          | I    | <b>DSR1</b> — Data Set Ready input for UART1.                                                                                                                 |

|                             |               |                          | 0    | MCICLK — Clock output line for SD/MMC interface. (LPC2367/68 only)                                                                                            |

|                             |               |                          | I/O  | SDA1 — I <sup>2</sup> C1 data input/output (this is not an open-drain pin).                                                                                   |

| P0[20]/DTR1/                | 58 <u>[1]</u> | G9 <u>[1]</u>            | I/O  | P0[20] — General purpose digital input/output pin.                                                                                                            |

| MCICMD/SCL1                 |               |                          | 0    | DTR1 — Data Terminal Ready output for UART1.                                                                                                                  |

|                             |               |                          | I    | MCICMD — Command line for SD/MMC interface. (LPC2367/68 only)                                                                                                 |

|                             |               |                          | I/O  | SCL1 — I <sup>2</sup> C1 clock input/output (this is not an open-drain pin).                                                                                  |

## 7.5 Interrupt controller

The ARM processor core has two interrupt inputs called Interrupt Request (IRQ) and Fast Interrupt Request (FIQ). The VIC takes 32 interrupt request inputs which can be programmed as FIQ or vectored IRQ types. The programmable assignment scheme means that priorities of interrupts from the various peripherals can be dynamically assigned and adjusted.

Additionally, any pin on Port 0 and Port 2 (total of 42 pins) providing a digital function can be programmed to generate an interrupt on a rising edge, a falling edge, or both. The edge detection is asynchronous, so it may operate when clocks are not present such as during Power-down mode. Each enabled interrupt can be used to wake up the chip from Power-down mode.

#### 7.8.1 Features

- Bit level set and clear registers allow a single instruction to set or clear any number of bits in one port.

- Direction control of individual bits.

- All I/O default to inputs after reset.

- Backward compatibility with other earlier devices is maintained with legacy Port 0 and Port 1 registers appearing at the original addresses on the APB.

#### 7.9 Ethernet

The Ethernet block contains a full featured 10 Mbit/s or 100 Mbit/s Ethernet MAC designed to provide optimized performance through the use of DMA hardware acceleration. Features include a generous suite of control registers, half or full duplex operation, flow control, control frames, hardware acceleration for transmit retry, receive packet filtering and wake-up on LAN activity. Automatic frame transmission and reception with scatter-gather DMA off-loads many operations from the CPU.

The Ethernet block and the CPU share a dedicated AHB subsystem that is used to access the Ethernet SRAM for Ethernet data, control, and status information. All other AHB traffic in the LPC2364/65/66/67/68 takes place on a different AHB subsystem, effectively separating Ethernet activity from the rest of the system. The Ethernet DMA can also access the USB SRAM if it is not being used by the USB block.

The Ethernet block interfaces between an off-chip Ethernet PHY using the Reduced MII (RMII) protocol and the on-chip Media Independent Interface Management (MIIM) serial bus.

#### 7.9.1 Features

- Ethernet standards support:

- Supports 10 Mbit/s or 100 Mbit/s PHY devices including 10 Base-T, 100 Base-TX, 100 Base-FX, and 100 Base-T4.

- Fully compliant with IEEE standard 802.3.

- Fully compliant with 802.3x full duplex flow control and half duplex back pressure.

- Flexible transmit and receive frame options.

- Virtual Local Area Network (VLAN) frame support.

- Memory management:

- Independent transmit and receive buffers memory mapped to shared SRAM.

- DMA managers with scatter/gather DMA and arrays of frame descriptors.

- Memory traffic optimized by buffering and pre-fetching.

- Enhanced Ethernet features:

- Receive filtering.

- Multicast and broadcast frame support for both transmit and receive.

- Optional automatic Frame Check Sequence (FCS) insertion with Circular Redundancy Check (CRC) for transmit.

- Selectable automatic transmit frame padding.

- Over-length frame support for both transmit and receive allows any length frames.

- Promiscuous receive mode.

- Automatic collision back-off and frame retransmission.

- Includes power management by clock switching.

- Wake-on-LAN power management support allows system wake-up: using the receive filters or a magic frame detection filter.

- Physical interface:

- Attachment of external PHY chip through standard RMII interface.

- PHY register access is available via the MIIM interface.

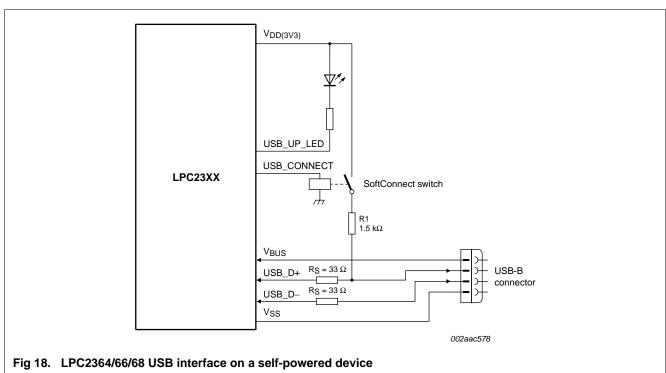

## 7.10 USB interface (LPC2364/66/68 only)

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and a number (127 maximum) of peripherals. The host controller allocates the USB bandwidth to attached devices through a token based protocol. The bus supports hot plugging, unplugging, and dynamic configuration of the devices. All transactions are initiated by the host controller.

#### 7.10.1 USB device controller

The device controller enables 12 Mbit/s data exchange with a USB host controller. It consists of register interface, serial interface engine, endpoint buffer memory, and the DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate end point buffer memory. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. The DMA controller when enabled transfers data between the endpoint buffer and the USB RAM.

#### 7.10.2 Features

- Fully compliant with *USB 2.0 specification* (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB USB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- Supports SoftConnect and GoodLink features.

- While USB is in the Suspend mode, LPC2364/65/66/67/68 can enter one of the reduced power modes and wake up on a USB activity.

- Supports DMA transfers with the DMA RAM of 8 kB on all non-control endpoints.

- Allows dynamic switching between CPU-controlled and DMA modes.

LPC2364\_65\_66\_67\_68

• Double buffer implementation for Bulk and Isochronous endpoints.

## 7.11 CAN controller and acceptance filters (LPC2364/66/68 only)

The Controller Area Network (CAN) is a serial communications protocol which efficiently supports distributed real-time control with a very high level of security. Its domain of application ranges from high-speed networks to low cost multiplex wiring.

The CAN block is intended to support multiple CAN buses simultaneously, allowing the device to be used as a gateway, switch, or router among a number of CAN buses in industrial or automotive applications.

Each CAN controller has a register structure similar to the NXP SJA1000 and the PeliCAN Library block, but the 8-bit registers of those devices have been combined in 32-bit words to allow simultaneous access in the ARM environment. The main operational difference is that the recognition of received Identifiers, known in CAN terminology as Acceptance Filtering, has been removed from the CAN controllers and centralized in a global Acceptance Filter.

#### **7.11.1** Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes 11-bit and 29-bit receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

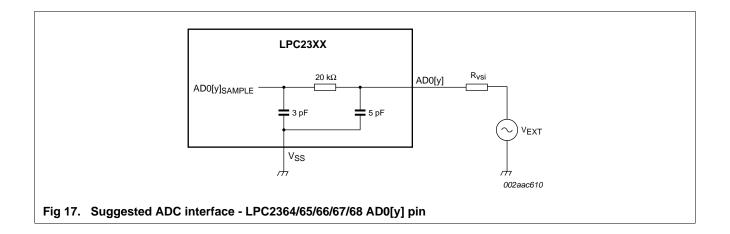

### 7.12 10-bit ADC

The LPC2364/65/66/67/68 contain one ADC. It is a single 10-bit successive approximation ADC with six channels.

#### 7.12.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 6 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>i(VREF)</sub>.

- 10-bit conversion time ≥ 2.44 μs.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from ( $T_{cy(WDCLK)} \times 256 \times 4$ ) to ( $T_{cy(WDCLK)} \times 2^{32} \times 4$ ) in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the RTC clock, the

Internal RC oscillator (IRC), or the APB peripheral clock. This gives a wide range of

potential timing choices of Watchdog operation under different power reduction

conditions. It also provides the ability to run the WDT from an entirely internal source

that is not dependent on an external crystal and its associated components and

wiring, for increased reliability.

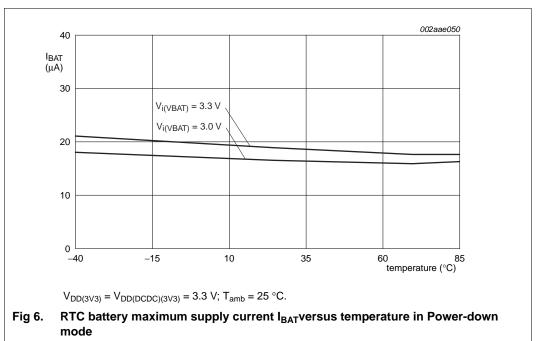

## 7.23 RTC and battery RAM

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. It uses little power in Power-down and Deep power-down modes. On the LPC2364/65/66/67/68, the RTC can be clocked by a separate 32.768 kHz oscillator, or by a programmable prescale divider based on the APB clock. Also, the RTC is powered by its own power supply pin, VBAT, which can be connected to a battery or to the same 3.3 V supply used by the rest of the device.

The VBAT pin supplies power only to the RTC and the battery RAM. These two functions require a minimum of power to operate, which can be supplied by an external battery.

#### 7.23.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated 32 kHz oscillator or programmable prescaler from APB clock.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- Periodic interrupts can be generated from increments of any field of the time registers, and selected fractional second values.

- 2 kB data SRAM powered by VBAT.

- RTC and battery RAM power supply is isolated from the rest of the chip.

#### 7.24 Clocking and power control

#### 7.24.1 Crystal oscillators

The LPC2364/65/66/67/68 includes three independent oscillators. These are the Main Oscillator, the Internal RC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the PLL and ultimately the CPU.

Following reset, the LPC2364/65/66/67/68 will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

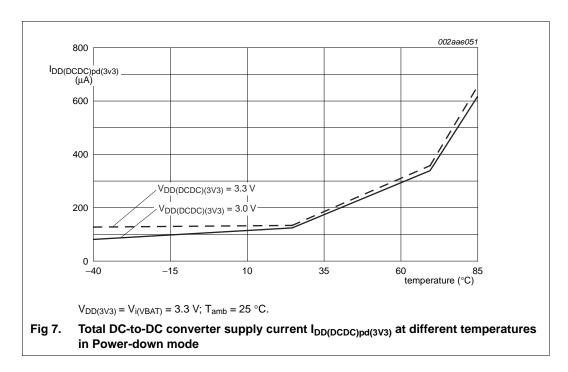

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(DCDC)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

The second option uses two power supplies; a 3.3 V supply for the I/O pads ( $V_{DD(3V3)}$ ) and a dedicated 3.3 V supply for the CPU ( $V_{DD(DCDC)(3V3)}$ ). Having the on-chip DC-to-DC converter powered independently from the I/O pad ring enables shutting down of the I/O pad power supply "on the fly", while the CPU and peripherals stay active.

The VBAT pin supplies power only to the RTC and the battery RAM. These two functions require a minimum of power to operate, which can be supplied by an external battery. When the CPU and the rest of chip functions are stopped and power removed, the RTC can supply an alarm output that may be used by external hardware to restore chip power and resume operation.

### 7.25 System control

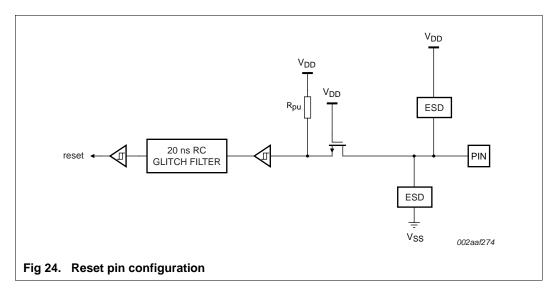

#### 7.25.1 Reset

Reset has four sources on the LPC2364/65/66/67/68: the RESET pin, the Watchdog reset, power-on reset, and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once the operating voltage attains a usable level, starts the Wake-up timer (see description in Section 7.24.3 "Wake-up timer"), causing reset to remain asserted until the external Reset is de-asserted, the oscillator is running, a fixed number of clocks have passed, and the flash controller has completed its initialization.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the Boot Block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

### 7.25.2 Brownout detection

The LPC2364/65/66/67/68 includes 2-stage monitoring of the voltage on the  $V_{DD(DCDC)(3V3)}$  pins. If this voltage falls below 2.95 V, the BOD asserts an interrupt signal to the Vectored Interrupt Controller. This signal can be enabled for interrupt in the Interrupt Enable Register in the VIC in order to cause a CPU interrupt; if not, software can monitor the signal by reading a dedicated status register.

The second stage of low-voltage detection asserts Reset to inactivate the LPC2364/65/66/67/68 when the voltage on the  $V_{DD(DCDC)(3V3)}$  pins falls below 2.65 V. This Reset prevents alteration of the flash as operation of the various elements of the chip would otherwise become unreliable due to low voltage. The BOD circuit maintains this reset down below 1 V, at which point the power-on reset circuitry maintains the overall Reset.

Both the 2.95 V and 2.65 V thresholds include some hysteresis. In normal operation, this hysteresis allows the 2.95 V detection to reliably interrupt, or a regularly executed event loop to sense the condition.

## 7.25.3 Code security (Code Read Protection - CRP)

This feature of the LPC2364/65/66/67/68 allows user to enable different levels of security in the system so that access to the on-chip flash and use of the JTAG and ISP can be restricted. When needed, CRP is invoked by programming a specific pattern into a dedicated flash location. IAP commands are not affected by the CRP.

There are three levels of the Code Read Protection.

CRP1 disables access to chip via the JTAG and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors can not be erased.

CRP2 disables access to chip via the JTAG and only allows full flash erase and update using a reduced set of the ISP commands.

Running an application with level CRP3 selected fully disables any access to chip via the JTAG pins and the ISP. This mode effectively disables ISP override using P2[10] pin, too. It is up to the user's application to provide (if needed) flash update mechanism using IAP calls or call reinvoke ISP command to enable flash update via UART0.

#### **CAUTION**

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

#### 7.25.4 AHB

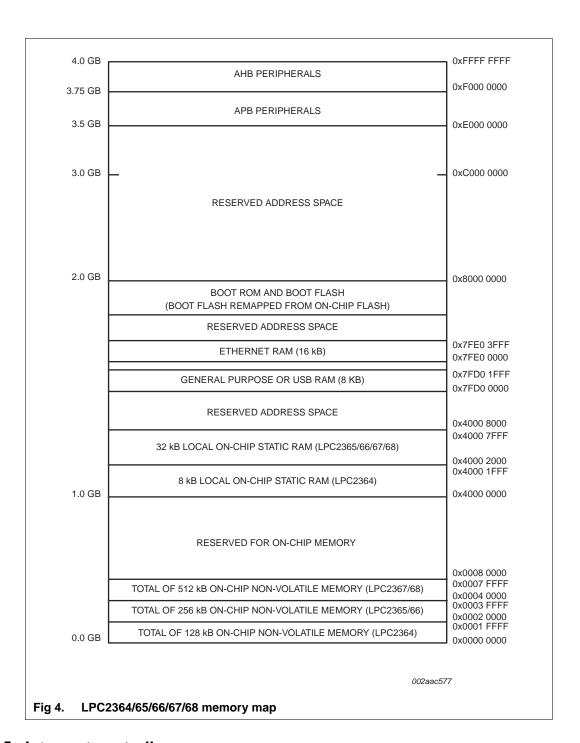

The LPC2364/65/66/67/68 implement two AHBs in order to allow the Ethernet block to operate without interference caused by other system activity. The primary AHB, referred to as AHB1, includes the Vectored Interrupt Controller, GPDMA controller, USB interface, and 8 kB SRAM primarily intended for use by the USB. The USB interface is available on LPC2364/66/68 only.

The second AHB, referred to as AHB2, includes only the Ethernet block and an associated 16 kB SRAM. In addition, a bus bridge is provided that allows the secondary AHB to be a bus master on AHB1, allowing expansion of Ethernet buffer space into unused space in memory residing on AHB1.

In summary, bus masters with access to AHB1 are the ARM7 itself, the USB block, the GPDMA function, and the Ethernet block (via the bus bridge from AHB2). Bus masters with access to AHB2 are the ARM7 and the Ethernet block.

### 7.25.5 External interrupt inputs

The LPC2364/65/66/67/68 include up to 46 edge sensitive interrupt inputs combined with up to four level sensitive external interrupt inputs as selectable pin functions. The external interrupt inputs can optionally be used to wake up the processor from Power-down mode.

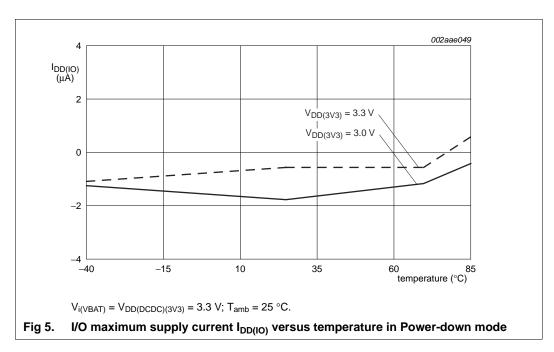

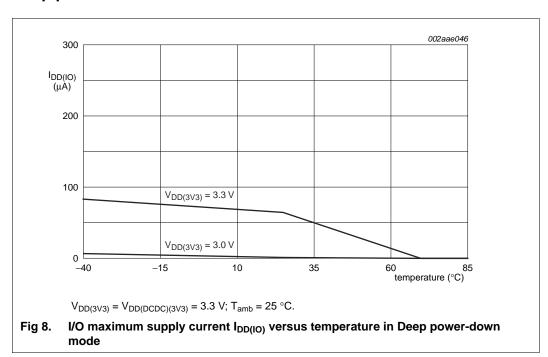

### 10.1 Power-down mode

# 10.2 Deep power-down mode

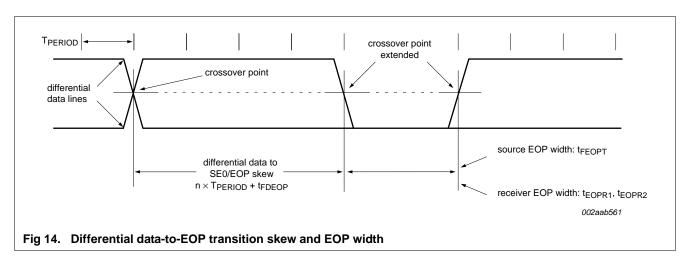

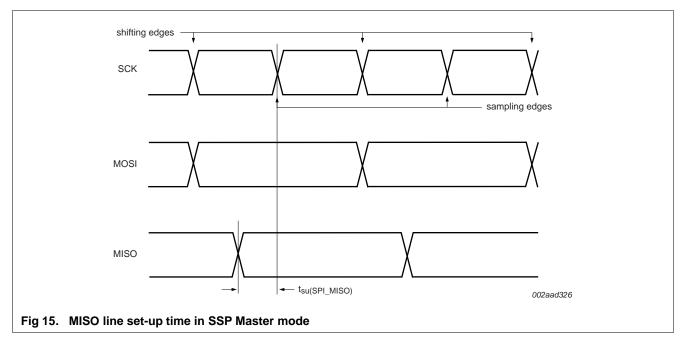

## 11.5 Timing

# 13. DAC electrical characteristics

Table 15. DAC electrical characteristics

$V_{DDA} = 3.0 \text{ V to } 3.6 \text{ V}; T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C} \text{ unless otherwise specified}$

| Symbol              | Parameter                    | Conditions | Min | Тур  | Max | Unit |

|---------------------|------------------------------|------------|-----|------|-----|------|

| E <sub>D</sub>      | differential linearity error |            | -   | ±1   | -   | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity       |            | -   | ±1.5 | -   | LSB  |

| E <sub>O</sub>      | offset error                 |            | -   | 0.6  | -   | %    |

| E <sub>G</sub>      | gain error                   |            | -   | 0.6  | -   | %    |

| C <sub>L</sub>      | load capacitance             |            | -   | 200  | -   | pF   |

| R <sub>L</sub>      | load resistance              |            | 1   | -    | -   | kΩ   |

# 14. Application information

# 14.1 Suggested USB interface solutions (LPC2364/66/68 only)

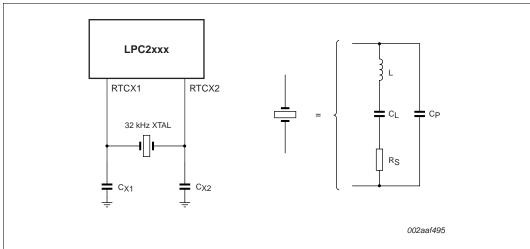

### 14.3 RTC 32 kHz oscillator component selection

Fig 22. RTC oscillator modes and models: oscillation mode of operation and external crystal model used for  $C_{X1}/C_{X2}$  evaluation

The RTC external oscillator circuit is shown in <u>Figure 22</u>. Since the feedback resistance is integrated on chip, only a crystal, the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally to the microcontroller.

$\underline{\text{Table 18}}$  gives the crystal parameters that should be used.  $C_L$  is the typical load capacitance of the crystal and is usually specified by the crystal manufacturer. The actual  $C_L$  influences oscillation frequency. When using a crystal that is manufactured for a different load capacitance, the circuit will oscillate at a slightly different frequency (depending on the quality of the crystal) compared to the specified one. Therefore for an accurate time reference it is advised to use the load capacitors as specified in  $\underline{\text{Table 18}}$  that belong to a specific  $C_L$ . The value of external capacitances  $C_{X1}$  and  $C_{X2}$  specified in this table are calculated from the internal parasitic capacitances and the  $C_L$ . Parasitics from PCB and package are not taken into account.

Table 18. Recommended values for the RTC external 32 kHz oscillator C<sub>X1</sub>/C<sub>X2</sub> components

| Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> /C <sub>X2</sub> |  |  |

|-----------------------------------------|--------------------------------------------------|-----------------------------------------------------------|--|--|

| 11 pF                                   | < 100 kΩ                                         | 18 pF, 18 pF                                              |  |  |

| 13 pF                                   | < 100 kΩ                                         | 22 pF, 22 pF                                              |  |  |

| 15 pF                                   | < 100 kΩ                                         | 27 pF, 27 pF                                              |  |  |

## 14.4 XTAL and RTCX Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{x1}$  and  $C_{x2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

# 14.6 Reset pin configuration

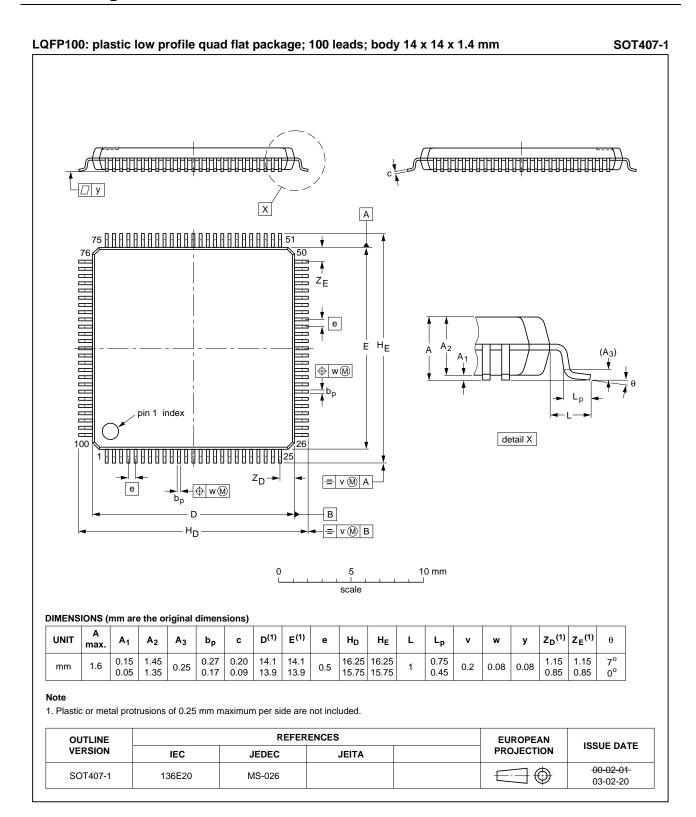

# 15. Package outline

Fig 25. Package outline SOT407-1 (LQFP100)

LPC2364\_65\_66\_67\_68

# 17. Revision history

#### Table 20. Revision history

| lable 20. Revision history |                                                                                                                                                                                                                                                                                                                                                      |                                                                    |                            |                                                           |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|-----------------------------------------------------------|--|--|--|

| Document ID                | Release date                                                                                                                                                                                                                                                                                                                                         | Data sheet status                                                  | Change notice              | Supersedes                                                |  |  |  |

| LPC2364_65_66_67_68 v.7.1  | 20131016                                                                                                                                                                                                                                                                                                                                             | Product data sheet                                                 | -                          | LPC2364_65_66_67_68 v.7                                   |  |  |  |

| Modifications:             |                                                                                                                                                                                                                                                                                                                                                      | scription", <u>Table note 6</u> : C<br>nic characteristics": Chang |                            | filter spec from 5 ns to 10 ns. cycle time from 42 to 40. |  |  |  |

| LPC2364_65_66_67_68 v.7    | 20111020                                                                                                                                                                                                                                                                                                                                             | Product data sheet                                                 | -                          | LPC2364_65_66_67_68 v.6                                   |  |  |  |

| Modifications:             | <ul> <li>Table 13 "Dynamic characteristics of flash": Added characteristics for t<sub>er</sub> and t<sub>prog</sub>.</li> <li>Table 4 "Pin description": Updated description for USB_UP_LED.</li> <li>Table 4 "Pin description": Added Table note 12 "If the RTC is not used, these pins can be left floating." for RTCX1 and RTCX2 pins.</li> </ul> |                                                                    |                            |                                                           |  |  |  |

|                            | for DBGEN, TM                                                                                                                                                                                                                                                                                                                                        | IS, TDI, $\overline{TRST}$ , and RTCK                              | Cpins.                     | has a built-in pull-up resistor."                         |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | scription": Added Table no<br>n resistor." for TCK and T           |                            | has no built-in pull-up and no                            |  |  |  |

|                            | <ul> <li>Table 5 "Limiting</li> </ul>                                                                                                                                                                                                                                                                                                                | g values": Added "non-op                                           | erating" to cor            | nditions column of T <sub>stg</sub> .                     |  |  |  |

|                            | <ul> <li>Table 5 "Limiting values": Updated Table note 5 "The maximum<br/>storage temperature is different than the temperature for require<br/>should be determined based on required shelf lifetime. Please<br/>spec (J-STD-033B.1) for further details.".</li> </ul>                                                                              |                                                                    |                            |                                                           |  |  |  |

|                            | <ul> <li>Table 5 "Limiting</li> </ul>                                                                                                                                                                                                                                                                                                                | g values": Updated storag                                          | e temperature              | e min/max to −65/+150.                                    |  |  |  |

|                            | <ul> <li>Added Table 7 '</li> </ul>                                                                                                                                                                                                                                                                                                                  | "Thermal resistance value                                          | e (C/W): ±15 %             | 0.                                                        |  |  |  |

|                            | <ul> <li>Added Table 10</li> </ul>                                                                                                                                                                                                                                                                                                                   | "Dynamic characteristic:                                           | internal oscilla           | ators".                                                   |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | "Dynamic characteristic:                                           |                            |                                                           |  |  |  |

|                            | <ul> <li>Table 8 "Static of<br/>0.05V<sub>DD(3V3)</sub>.</li> </ul>                                                                                                                                                                                                                                                                                  | characteristics": Changed                                          | V <sub>hys</sub> typ value | from 0.5V <sub>DD(3V3)</sub> to                           |  |  |  |

|                            | <ul> <li>Table 13 "Dyna</li> </ul>                                                                                                                                                                                                                                                                                                                   | mic characteristics of flasl                                       | h": Updated ta             | ıble.                                                     |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | 9 "Thermal characteristics                                         |                            |                                                           |  |  |  |

|                            | <ul> <li>Added Section</li> </ul>                                                                                                                                                                                                                                                                                                                    | 10.3 "Electrical pin charad                                        | cteristics".               |                                                           |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | 14.2 "Crystal oscillator XT                                        | •                          | •                                                         |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | 14.3 "RTC 32 kHz oscillat                                          | -                          |                                                           |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      |                                                                    |                            | soard (PCB) layout guidelines".                           |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                      | 14.5 "Standard I/O pin co                                          | -                          |                                                           |  |  |  |

|                            | <ul> <li>Added Section</li> </ul>                                                                                                                                                                                                                                                                                                                    | 14.6 "Reset pin configura                                          | tion".                     |                                                           |  |  |  |

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b)

whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

#### 18.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

### 19. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>