Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u5dvm10adr                                            |

#### Introduction

**Table 1. Example Orderable Part Numbers (continued)**

| Part Number     | i.MX6 CPU<br>Solo/<br>DualLite | Options                                                              | Speed<br>Grade <sup>1</sup> | Temperature<br>Grade   | Package                                |

|-----------------|--------------------------------|----------------------------------------------------------------------|-----------------------------|------------------------|----------------------------------------|

| MCIMX6S8DVM10AB | Solo                           | With VPU, GPU, MLB, EPDC<br>1x ARM Cortex-A9 32-bit DDR              | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S8DVM10AC | Solo                           | With VPU, GPU, MLB, EPDC<br>1x ARM Cortex-A9 32-bit DDR              | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S8DVM10AD | Solo                           | With VPU, GPU, MLB, EPDC<br>1x ARM Cortex-A9 32-bit DDR              | 1 GHz                       | Commercial             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S5DVM10AB | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S5DVM10AC | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S5DVM10AD | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Commercial             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| SCIMX6S5DVM10CB | Solo                           | HDCP enabled with VPU, GPU, MLB, no EPDC 1x ARM Cortex-A9 32-bit DDR | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| SCIMX6S5DVM10CC | Solo                           | HDCP enabled with VPU, GPU, MLB, no EPDC 1x ARM Cortex-A9 32-bit DDR | 1 GHz                       | Commercial             | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| SCIMX6S5DVM10CD | Solo                           | HDCP enabled with VPU, GPU, MLB, no EPDC 1x ARM Cortex-A9 32-bit DDR | 1 GHz                       | Commercial             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S5EVM10AB | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S5EVM10AC | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm,<br>0.8 mm pitch, MAPBGA |

| MCIMX6S5EVM10AD | Solo                           | With VPU, GPU, MLB, no EPDC<br>1x ARM Cortex-A9 32-bit DDR           | 1 GHz                       | Extended<br>Commercial | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

If a 24 MHz input clock is used (required for USB), then the maximum SoC speed is limited to 996 MHz.

Figure 1 describes the part number nomenclature to identify the characteristics of a specific part number (for example, cores, frequency, temperature grade, fuse options, and silicon revision).

The primary characteristic that differentiates which data sheet applies to a specific part is the temperature grade (junction) field. The following list describes the correct data sheet to use for a specific part:

- The *i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors* data sheet (IMX6SDLAEC) covers parts listed with an "A (Automotive temp)"

- The *i.MX* 6Solo/6DualLite Applications Processors for Consumer Products data sheet (IMX6SDLCEC) covers parts listed with a "D (Commercial temp)" or "E (Extended Commercial temp)"

#### Introduction

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (MOST25, MOST50, MOST150) with the option of DTCP cipher accelerator

The i.MX 6Solo/6DualLite processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use SW State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Solo/6DualLite processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Solo/6DualLite processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H

- GPU3Dv5—3D Graphics Processing Unit (OpenGL ES 2.0) version 5

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- PXP—PiXel Processing Pipeline. Off loading key pixel processing operations are required to support the EPD display applications.

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing cryptographic and hash engines, 16 KB secure RAM, and True and Pseudo Random Number Generator (NIST certified).

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

Table 2. i.MX 6Solo/6DualLite Modules List (continued)

| Block Mnemonic                | Block Name                                                                 | Subsystem                 | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|----------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-3<br>uSDHC-4 | SD/MMC and SDXC Enhanced Multi-Media Card / Secure Digital Host Controller | Connectivity Peripherals  | <ul> <li>i.MX 6Solo/6DualLite specific SoC characteristics: All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are: <ul> <li>Conforms to the SD Host Controller Standard Specification version 3.0.</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4/4.41 including high-capacity (size &gt; 2 GB) cards HC MMC.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB and SDXC cards up to 2 TB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO Card Specification, Part E1, v3.0</li> </ul> </li> <li>All four ports support: <ul> <li>1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> </ul> </li> <li>However, the SoC level integration and I/O muxing logic restrict the functionality to the following: <ul> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card detection" and "Write Protection" pads and do not support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve interfaces to embedded MMC memory or interfaces to on-board SDIO devices. These ports do not have "Card detection" and "Write Protection" pads and do support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power domain and port #4 shares power domain with some other interfaces.</li> </ul> </li> </ul> |

| VDOA                          | VDOA                                                                       | Multimedia<br>Peripherals | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VPU                           | Video Processing Unit                                                      | Multimedia<br>Peripherals | A high-performing video processing unit (VPU), which covers many SD-level and HD-level video decoders and SD-level encoders as a multi-standard video codec engine as well as several important video processing, such as rotation and mirroring.  See the i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM) for complete list of VPU's decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## 4.1.4 External Clock Sources

Each i.MX 6Solo/6DualLite processor has two external input system clocks: a low frequency (RTC\_XTALI) and a high frequency (XTALI).

The RTC\_XTALI is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watch-dog counters. The clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier. Additionally, there is an internal ring oscillator, which can be used instead of the RTC\_XTALI if accuracy is not important.

### NOTE

The internal RTC oscillator does not provide an accurate frequency and is affected by process, voltage, and temperature variations. NXP strongly recommends using an external crystal as the RTC\_XTALI reference. If the internal oscillator is used instead, careful consideration must be given to the timing implications on all of the SoC modules dependent on this clock.

The system clock input XTALI is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier.

Table 9 shows the interface frequency requirements.

Parameter DescriptionSymbolMinTypMaxUnitRTC\_XTALI Oscillator 1,2f ckil—32.7683/32.0—kHzXTALI Oscillator 2,4f xtal—24—MHz

**Table 9. External Input Clock Frequency**

The typical values shown in Table 9 are required for use with NXP BSPs to ensure precise time keeping and USB operation. For XTALOSC\_RTC\_XTALI operation, two clock sources are available.

- On-chip 40 kHz ring oscillator—this clock source has the following characteristics:

- Approximately 25 μA more Idd than crystal oscillator

- Approximately ±50% tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit:

- At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

- Higher accuracy than ring oscillator

- If no external crystal is present, then the ring oscillator is used

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

External oscillator or a crystal with internal oscillator amplifier.

<sup>&</sup>lt;sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>&</sup>lt;sup>3</sup> Recommended nominal frequency 32.768 kHz.

<sup>&</sup>lt;sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

### 4.3.2.2 LDO 2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 8 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. LDO\_2P5 supplies the USB Phy, LVDS Phy, HDMI Phy, MIPI Phy, E-fuse module, and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40\,\Omega$

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Solo/6DualLite reference manual.

## 4.3.2.3 LDO USB

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either USB\_VBUS supply, when both are present. If only one of the USB\_VBUS voltages is present, then, the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Solo/6DualLite reference manual.

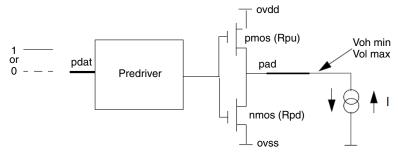

Figure 4. Circuit for Parameters Voh and Vol for I/O Cells

## 4.6.1 XTALI and RTC\_XTALI (Clock Inputs) DC Parameters

Table 22 shows the DC parameters for the clock inputs.

Table 22. XTALI and RTC\_XTALI DC Parameters

| Parameter                              | Symbol                     | Test Conditions                                                              | Min            | Тур | Max              | Unit |

|----------------------------------------|----------------------------|------------------------------------------------------------------------------|----------------|-----|------------------|------|

| XTALI high-level DC input voltage      | Vih                        | _                                                                            | 0.8 x NVCC_PLL | _   | NVCC_PLL         | V    |

| XTALI low-level DC input voltage       | Vil                        | _                                                                            | 0              | _   | 0.2V             | ٧    |

| RTC_XTALI high-level DC input voltage  | Vih                        | _                                                                            | 0.8            | _   | 1.1 <sup>1</sup> | V    |

| RTC_XTALI low-level DC input voltage   | Vil                        | _                                                                            | 0              | _   | 0.2              | V    |

| Input capacitance                      | C <sub>IN</sub>            | Simulated data                                                               | _              | 5   | _                | pF   |

| XTALI input leakage current at startup | I <sub>XTALI_STARTUP</sub> | Power-on startup for 0.15msec with a driven 24MHz clock @ 1.1V. <sup>2</sup> | _              | _   | 600              | μΑ   |

| DC input current                       | I <sub>XTALI_DC</sub>      | _                                                                            | _              | _   | 2.5              | μΑ   |

<sup>&</sup>lt;sup>1</sup> This voltage specification must not be exceeded and, as such, is an absolute maximum specification.

### **NOTE**

The Vil and Vih specifications only apply when an external clock source is used. If a crystal is used, Vil and Vih do not apply.

# 4.6.2 General Purpose I/O (GPIO) DC Parameters

Table 23 shows DC parameters for GPIO pads. The parameters in Table 23 are guaranteed per the operating ranges in Table 8, unless otherwise noted.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

This current draw is present even if an external clock source directly drives XTALI. The 24 MHz oscillator cell is powered from NVCC\_PLL\_OUT.

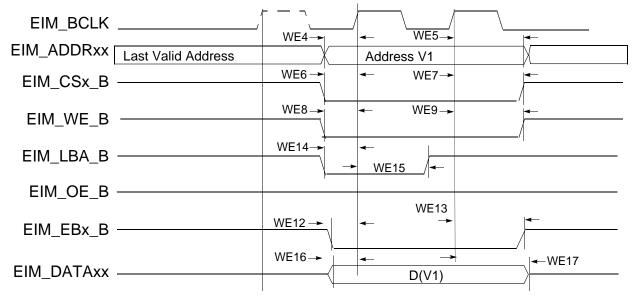

Figure 16. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

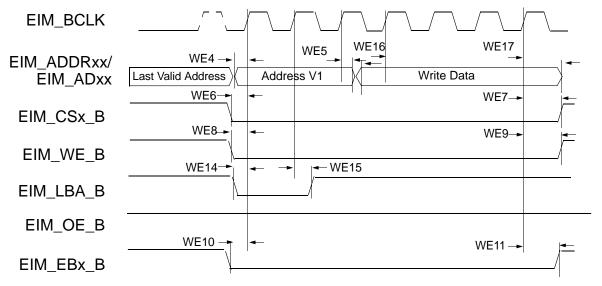

Figure 17. Muxed Address/Data (A/D) Mode, Synchronous Write Access, WSC=6,ADVA=0, ADVN=1, and ADH=1

### **NOTE**

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

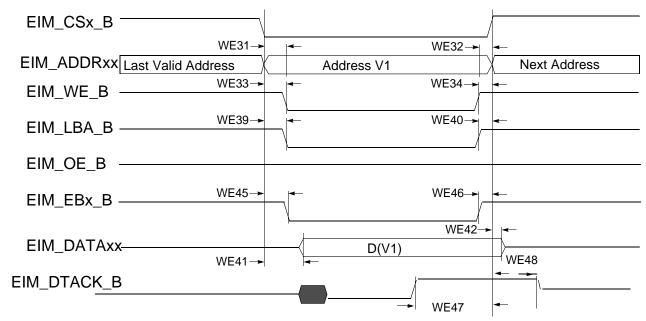

Figure 24. DTACK Mode Write Access (DAP=0)

Table 43. EIM Asynchronous Timing Parameters Table Relative Chip to Select

| Ref No. | Parameter                                              | Determination by<br>Synchronous measured<br>parameters <sup>1</sup>               | Min                                        | Max                                       | Unit |

|---------|--------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|------|

| WE31    | EIM_CSx_B valid to<br>Address Valid                    | WE4 - WE6 - CSA <sup>2</sup>                                                      | _                                          | 3 - CSA                                   | ns   |

| WE32    | Address Invalid to EIM_CSx_B invalid                   | WE7 - WE5 - CSN <sup>3</sup>                                                      | _                                          | 3 - CSN                                   | ns   |

|         | EIM_CSx_B valid to<br>Address Invalid                  | t <sup>4</sup> + WE4 - WE7 + (ADVN <sup>5</sup> +<br>ADVA <sup>6</sup> + 1 - CSA) | -3 + (ADVN +<br>ADVA + 1 - CSA)            | _                                         | ns   |

| WE33    | EIM_CSx_B Valid to<br>EIM_WE_B Valid                   | WE8 - WE6 + (WEA - WCSA)                                                          | _                                          | 3 + (WEA - WCSA)                          | ns   |

| WE34    | EIM_WE_B Invalid to<br>EIM_CSx_B Invalid               | WE7 - WE9 + (WEN - WCSN)                                                          | _                                          | 3 - (WEN_WCSN)                            | ns   |

| WE35    | EIM_CSx_B Valid to<br>EIM_OE_B Valid                   | WE10 - WE6 + (OEA - RCSA)                                                         | _                                          | 3 + (OEA - RCSA)                          | ns   |

|         | EIM_CSx_B Valid to<br>EIM_OE_B Valid                   | WE10 - WE6 + (OEA + RADVN<br>+ RADVA + ADH + 1 - RCSA)                            | -3 + (OEA +<br>RADVN+RADVA+<br>ADH+1-RCSA) | 3 + (OEA +<br>RADVN+RADVA+ADH<br>+1-RCSA) | ns   |

| WE36    | EIM_OE_B Invalid to<br>EIM_CSx_B Invalid               | WE7 - WE11 + (OEN - RCSN)                                                         | _                                          | 3 - (OEN - RCSN)                          | ns   |

| WE37    | EIM_CSx_B Valid to<br>EIM_EBx_B Valid<br>(Read access) | WE12 - WE6 + (RBEA - RCSA)                                                        | _                                          | 3 + (RBEA - RCSA)                         | ns   |

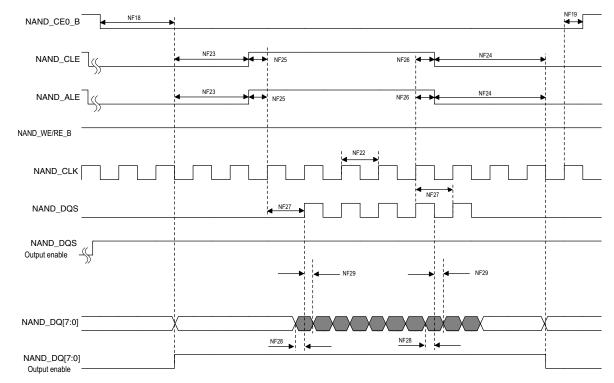

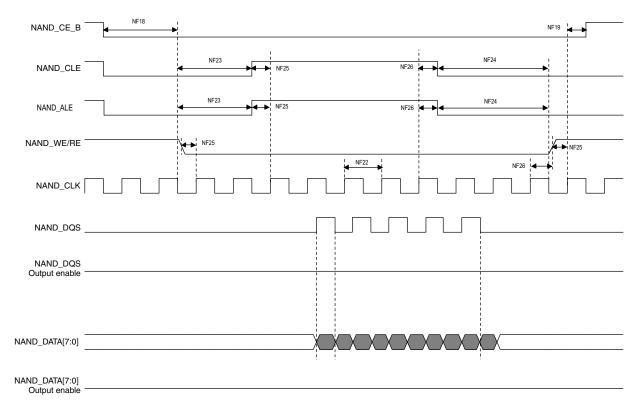

Figure 31. Source Synchronous Mode Data Write Timing Diagram

Figure 32. Source Synchronous Mode Data Read Timing Diagram

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

| Table 48. Samsung | <b>Toggle Mode</b> | <b>Timing Par</b> | rameters <sup>1</sup> | (continued) | ) |

|-------------------|--------------------|-------------------|-----------------------|-------------|---|

|-------------------|--------------------|-------------------|-----------------------|-------------|---|

| ID   | Parameter                        | Symbol             | Timing<br>T = GPMI Clock C | Cycle | Unit |

|------|----------------------------------|--------------------|----------------------------|-------|------|

|      |                                  |                    | Min                        | Max   |      |

| NF28 | Data write setup                 | tDS <sup>6</sup>   | 0.25 × tCK - 0.32          | _     | ns   |

| NF29 | Data write hold                  | tDH <sup>6</sup>   | 0.25 × tCK - 0.79          | _     | ns   |

| NF30 | NAND_DQS/NAND_DQ read setup skew | tDQSQ <sup>7</sup> | _                          | 3.18  |      |

| NF31 | NAND_DQS/NAND_DQ read hold skew  | tQHS <sup>7</sup>  | _                          | 3.27  |      |

The GPMI toggle mode output timing can be controlled by the module's internal registers

HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD.

This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

For DDR Toggle mode, Figure 33 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. The typical value of tDQSQ is 1.4 ns (max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of an delayed NAND\_DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.11 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

# 4.11.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

# 4.11.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI blocks. The ECSPI have separate timing parameters for master and slave modes.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

<sup>&</sup>lt;sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>&</sup>lt;sup>3</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

<sup>&</sup>lt;sup>4</sup> CE\_DELAY represents HW\_GPMI\_TIMING2[CE\_DELAY]. NF18 is guaranteed by the design. Read/Write operation is started with enough time of ALE/CLE assertion to low level.

<sup>&</sup>lt;sup>5</sup> PRE\_DELAY+1)  $\geq$  (AS+DS).

<sup>&</sup>lt;sup>6</sup> Shown in Figure 34, Samsung Toggle Mode Data Write Timing diagram.

Nand\_DQS/NAND\_DQ Read Valid Window. 7

Table 64. Camera Input Signal Cross Reference, Format, and Bits Per Cycle (continued)

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>1 cycle | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|-------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| IPUx_CSIx_<br>DATA13        | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                      | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| IPUx_CSIx_<br>DATA14        | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                      | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| IPUx_CSIx_<br>DATA15        | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                      | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| IPUx_CSIx_<br>DATA16        | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                      | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| IPUx_CSIx_<br>DATA17        | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                      | Y[5]                                     | Y[5]                                     | Y[7]                                     |

| IPUx_CSIx_<br>DATA18        | G[1], R[3]                   | R[3],G[4],B[3]                            | R/G/B[4]                                  | R/G/B[6]                     | Y/C[6]                                   | R[3]                                      | Y[6]                                     | Y[6]                                     | Y[8]                                     |

| IPUx_CSIx_<br>DATA19        | G[2], R[4]                   | R[4],G[5],B[4]                            | R/G/B[5]                                  | R/G/B[7]                     | Y/C[7]                                   | R[4]                                      | Y[7]                                     | Y[7]                                     | Y[9]                                     |

<sup>&</sup>lt;sup>1</sup> IPUx CSIx stands for IPUx CSI0 or IPUx CSI1.

## 4.11.10.2 Sensor Interface Timings

There are three camera timing modes supported by the IPU.

### 4.11.10.2.1 BT.656 and BT.1120 Video Mode

Smart camera sensors, which include imaging processing, usually support video mode transfer. They use an embedded timing syntax to replace the IPUx\_CSIx\_VSYNC and IPUx\_CSIx\_HSYNC signals. The timing syntax is defined by the BT.656/BT.1120 standards.

This operation mode follows the recommendations of ITU BT.656/ITU BT.1120 specifications. The only control signal used is IPUx\_CSIx\_PIX\_CLK. Start-of-frame and active-line signals are embedded in the data stream. An active line starts with a SAV code and ends with a EAV code. In some cases, digital blanking is inserted in between EAV and SAV code. The CSI decodes and filters out the timing-coding from the data stream, thus recovering IPUx\_CSIx\_VSYNC and IPUx\_CSIx\_HSYNC signals for internal use. On BT.656 one component per cycle is received over the IPUx\_CSIx\_DATA\_EN bus. On BT.1120 two components per cycle are received over the IPUx\_CSIx\_DATA\_EN bus.

<sup>&</sup>lt;sup>2</sup> The MSB bits are duplicated on LSB bits implementing color extension.

<sup>&</sup>lt;sup>3</sup> The two MSB bits are duplicated on LSB bits implementing color extension.

<sup>&</sup>lt;sup>4</sup> YCbCr, 8 bits—Supported within the BT.656 protocol (sync embedded within the data stream).

<sup>&</sup>lt;sup>5</sup> RGB 16 bits—Supported in two ways: (1) As a "generic data" input, with no on-the-fly processing; (2) With on-the-fly processing, but only under some restrictions on the control protocol.

<sup>&</sup>lt;sup>6</sup> YCbCr 16 bits—Supported as a "generic-data" input, with no on-the-fly processing.

<sup>&</sup>lt;sup>7</sup> YCbCr 16 bits—Supported as a sub-case of the YCbCr, 20 bits, under the same conditions (BT.1120 protocol).

<sup>&</sup>lt;sup>8</sup> YCbCr, 20 bits—Supported only within the BT.1120 protocol (syncs embedded within the data stream).

95

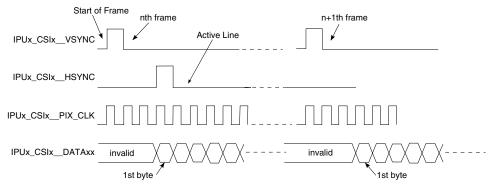

### 4.11.10.2.2 Gated Clock Mode

The IPUx\_CSIx\_VSYNC, IPUx\_CSIx\_HSYNC, and IPUx\_CSIx\_PIX\_CLK signals are used in this mode. See Figure 60.

Figure 60. Gated Clock Mode Timing Diagram

A frame starts with a rising edge on IPUx\_CSIx\_VSYNC (all the timings correspond to straight polarity of the corresponding signals). Then IPUx\_CSIx\_HSYNC goes to high and hold for the entire line. Pixel clock is valid as long as IPUx\_CSIx\_HSYNC is high. Data is latched at the rising edge of the valid pixel clocks. IPUx\_CSIx\_HSYNC goes to low at the end of line. Pixel clocks then become invalid and the CSI stops receiving data from the stream. For the next line, the IPUx\_CSIx\_HSYNC timing repeats. For the next frame, the IPUx\_CSIx\_VSYNC timing repeats.

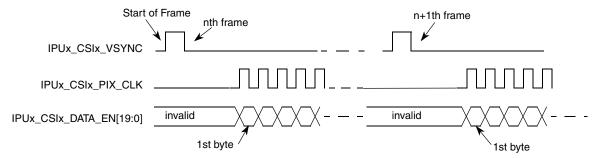

### 4.11.10.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.11.10.2.2, "Gated Clock Mode,") except for the IPUx\_CSIx\_HSYNC signal, which is not used (see Figure 61). All incoming pixel clocks are valid and cause data to be latched into the input FIFO. The IPUx\_CSIx\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 61. Non-Gated Clock Mode Timing Diagram

The timing described in Figure 61 is that of a typical sensor. Some other sensors may have a slightly different timing. The CSI can be programmed to support rising/falling-edge triggered IPUx\_CSIx\_VSYNC; active-high/low IPUx\_CSIx\_HSYNC; and rising/falling-edge triggered IPUx\_CSIx\_PIX\_CLK.

Table 66. Video Signal Cross-Reference (continued)

| i.MX 6Solo/6DualLite  |                             |               |               | LCD             |                             |                        |                 |                                  |

|-----------------------|-----------------------------|---------------|---------------|-----------------|-----------------------------|------------------------|-----------------|----------------------------------|

|                       | RGB,                        | R             | GB/TV         | Signal <i>A</i> | Illocation                  | Comment <sup>1,2</sup> |                 |                                  |

| Port Name<br>(x=0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB   | 8-bit<br>YCrCb <sup>3</sup> | 16-bit<br>YCrCb        | 20-bit<br>YCrCb |                                  |

| IPUx_DISPx_DAT07      | DAT[7]                      | G[2]          | G[1]          | B[7]            | Y/C[7]                      | C[7]                   | C[7]            | _                                |

| IPUx_DISPx_DAT08      | DAT[8]                      | G[3]          | G[2]          | G[0]            | _                           | Y[0]                   | C[8]            | _                                |

| IPUx_DISPx_DAT09      | DAT[9]                      | G[4]          | G[3]          | G[1]            | _                           | Y[1]                   | C[9]            | _                                |

| IPUx_DISPx_DAT10      | DAT[10]                     | G[5]          | G[4]          | G[2]            | _                           | Y[2]                   | Y[0]            | _                                |

| IPUx_DISPx_DAT11      | DAT[11]                     | R[0]          | G[5]          | G[3]            | _                           | Y[3]                   | Y[1]            | _                                |

| IPUx_DISPx_DAT12      | DAT[12]                     | R[1]          | R[0]          | G[4]            | _                           | Y[4]                   | Y[2]            | _                                |

| IPUx_DISPx_DAT13      | DAT[13]                     | R[2]          | R[1]          | G[5]            | _                           | Y[5]                   | Y[3]            | _                                |

| IPUx_DISPx_DAT14      | DAT[14]                     | R[3]          | R[2]          | G[6]            | _                           | Y[6]                   | Y[4]            | _                                |

| IPUx_DISPx_DAT15      | DAT[15]                     | R[4]          | R[3]          | G[7]            | _                           | Y[7]                   | Y[5]            | _                                |

| IPUx_DISPx_DAT16      | DAT[16]                     | _             | R[4]          | R[0]            | _                           | _                      | Y[6]            | _                                |

| IPUx_DISPx_DAT17      | DAT[17]                     | _             | R[5]          | R[1]            | _                           | _                      | Y[7]            | _                                |

| IPUx_DISPx_DAT18      | DAT[18]                     | _             | _             | R[2]            | _                           | _                      | Y[8]            | _                                |

| IPUx_DISPx_DAT19      | DAT[19]                     | _             | _             | R[3]            | _                           | _                      | Y[9]            | _                                |

| IPUx_DISPx_DAT20      | DAT[20]                     | _             | _             | R[4]            | _                           | _                      | _               | _                                |

| IPUx_DISPx_DAT21      | DAT[21]                     | _             | _             | R[5]            | _                           | _                      | _               | _                                |

| IPUx_DISPx_DAT22      | DAT[22]                     | _             | _             | R[6]            |                             | _                      | _               | _                                |

| IPUx_DISPx_DAT23      | DAT[23]                     | _             | _             | R[7]            |                             | _                      | _               | _                                |

| DIx_DISP_CLK          |                             | l             | 1             | PixCLK          |                             | <u> </u>               |                 | _                                |

| DIx_PIN1              |                             |               |               | _               |                             |                        |                 | May be required for anti-tearing |

| DIx_PIN2              |                             |               |               | HSYNC           |                             |                        |                 | _                                |

| DIx_PIN3              |                             |               |               | VSYNC           |                             |                        |                 | VSYNC out                        |

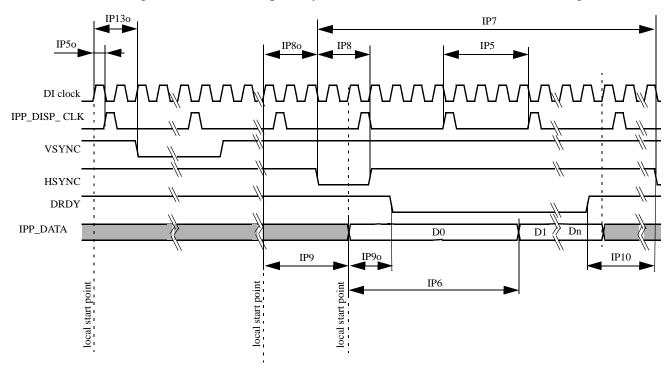

corresponding internal events—local start points. The timing diagrams correspond to inverse polarity of the IPP\_DISP\_CLK signal and active-low polarity of the HSYNC, VSYNC, and DRDY signals.

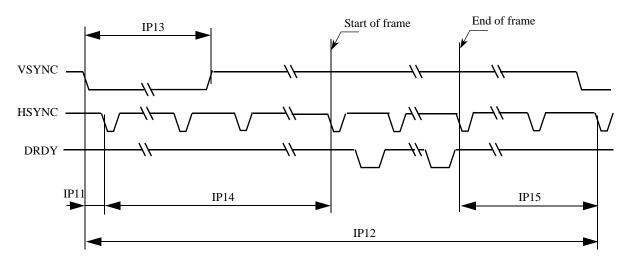

Figure 64. TFT Panels Timing Diagram—Horizontal Sync Pulse

Figure 65 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

Figure 65. TFT Panels Timing Diagram—Vertical Sync Pulse

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

Table 67. Synchronous Display Interface Timing Characteristics (Pixel Level) (continued)

| ID    | Parameter       | Symbol | Value                    | Description                                                                                                                                                                                                           | Unit |

|-------|-----------------|--------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP130 | Offset of VSYNC | Tovs   | VSYNC_OFFSET<br>× Tdiclk | VSYNC_OFFSET—offset of Vsync edges from a local start point, when a Vsync should be active, in DI_CLK×2 (0.5 DI_CLK Resolution). The VSYNC_OFFSET should be built by suitable DI's counter.                           | ns   |

| IP8o  | Offset of HSYNC | Tohs   | HSYNC_OFFSET<br>× Tdiclk | HSYNC_OFFSET—offset of Hsync edges from a local start point, when a Hsync should be active, in DI_CLK×2 (0.5 DI_CLK Resolution). The HSYNC_OFFSET should be built by suitable DI's counter.                           | ns   |

| IP9o  | Offset of DRDY  | Todrdy | DRDY_OFFSET<br>× Tdiclk  | DRDY_OFFSET—offset of DRDY edges from a suitable local start point, when a corresponding data has been set on the bus, in DI_CLK×2 (0.5 DI_CLK Resolution). The DRDY_OFFSET should be built by suitable DI's counter. | ns   |

Display interface clock period immediate value.

DISP\_CLK\_PERIOD—number of DI\_CLK per one Tdicp. Resolution 1/16 of DI\_CLK. DI\_CLK\_PERIOD—relation of between programing clock frequency and current system clock frequency Display interface clock period average value.

$$\overline{T}$$

dicp =  $T_{diclk} \times \frac{DISP\_CLK\_PERIOD}{DI\_CLK\_PERIOD}$

The maximum accuracy of UP/DOWN edge of controls is:

Accuracy =

$$(0.5 \times T_{diclk}) \pm 0.62$$

ns

The maximum accuracy of UP/DOWN edge of IPP\_DATA is:

Accuracy =

$$T_{diclk} \pm 0.62 ns$$

The DISP\_CLK\_PERIOD, DI\_CLK\_PERIOD parameters are programmed through the registers.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

DI's counter can define offset, period and UP/DOWN characteristic of output signal according to programed parameters of the counter. Same of parameters in the table are not defined by DI's registers directly (by name), but can be generated by corresponding DI's counter. The SCREEN\_WIDTH is an input value for DI's HSYNC generation counter. The distance between HSYNCs is a SCREEN\_WIDTH.

119

## 4.11.15.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

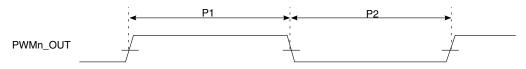

## 4.11.16 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 84 depicts the timing of the PWM, and Table 78 lists the PWM timing parameters.

Figure 84. PWM Timing

**Table 78. PWM Output Timing Parameters**

| ID | Parameter                   | Min | Max     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  | _       | ns   |

| P2 | PWM output pulse width low  | 15  | 1       | ns   |

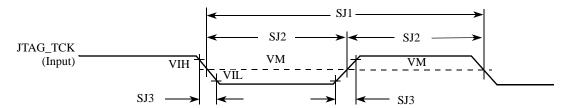

# 4.11.17 SCAN JTAG Controller (SJC) Timing Parameters

Figure 85 depicts the SJC test clock input timing. Figure 86 depicts the SJC boundary scan timing. Figure 87 depicts the SJC test access port. Signal parameters are listed in Table 79.

Figure 85. Test Clock Input Timing Diagram

Table 83. SSI Receiver Timing with Internal Clock (continued)

| ID   | Parameter                      | Min   | Max | Unit |  |  |  |  |  |  |

|------|--------------------------------|-------|-----|------|--|--|--|--|--|--|

|      | Oversampling Clock Operation   |       |     |      |  |  |  |  |  |  |

| SS47 | Oversampling clock period      | 15.04 | _   | ns   |  |  |  |  |  |  |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |  |  |  |  |  |  |

| SS49 | Oversampling clock rise time   | _     | 3.0 | ns   |  |  |  |  |  |  |

| SS50 | Oversampling clock low period  | 6.0   | _   | ns   |  |  |  |  |  |  |

| SS51 | Oversampling clock fall time   | _     | 3.0 | ns   |  |  |  |  |  |  |

### **NOTE**

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

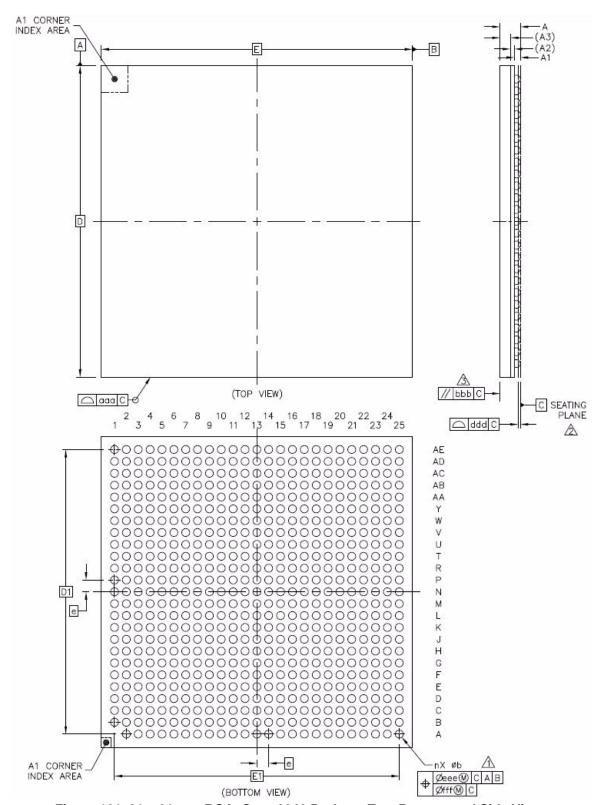

Figure 101. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 8, 09/2017

Table 95 shows the  $21 \times 21$  mm BGA package details.

Table 95. 21 x 21, 0.8 mm BGA Package Details

| Parameter                   | Symbol | Common Dimensions |          |         |

|-----------------------------|--------|-------------------|----------|---------|

| Parameter                   |        | Minimum           | Normal   | Maximum |

| Total Thickness             | Α      | _                 | _        | 1.6     |

| Stand Off                   | A1     | 0.36              | _        | 0.46    |

| Substrate Thickness         | A2     | 0.26 REF          |          |         |

| Mold Thickness              | А3     | 0.7 REF           |          |         |

| Body Size                   | D      | 21 BSC            |          |         |

|                             | E      |                   | 21 BSC   |         |

| Ball Diameter               | _      | 0.5               |          |         |

| Ball Opening                | _      | 0.4               |          |         |

| Ball Width                  | b      | 0.44              | _        | 0.64    |

| Ball Pitch                  | е      | 0.8 BSC           |          |         |

| Ball Count                  | n      | 624               |          |         |

| Edge Ball Center to Center  | D1     | 19.2 BSC          |          |         |

|                             | E1     |                   | 19.2 BSC |         |

| Body Center to Contact Ball | SD     |                   | _        |         |

|                             | SE     |                   | _        |         |

| Package Edge Tolerance      | aaa    | 0.1               |          |         |

| Mold Flatness               | bbb    | 0.2               |          |         |

| Coplanarity                 | ddd    | 0.15              |          |         |

| Ball Offset (Package)       | eee    | 0.15              |          |         |

| Ball Offset (Ball)          | fff    | 0.08              |          |         |

## **Package Information and Contact Assignments**

Table 98. Signals with Differing Before Reset and After Reset States (continued)

| Ball Name | Before Reset State |                         |  |

|-----------|--------------------|-------------------------|--|

| Dan Name  | Input/Output       | Value                   |  |

| GPIO_19   | Output             | Drive state unknown (x) |  |

| KEY_COL0  | Output             | Drive state unknown (x) |  |