Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c642-04-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

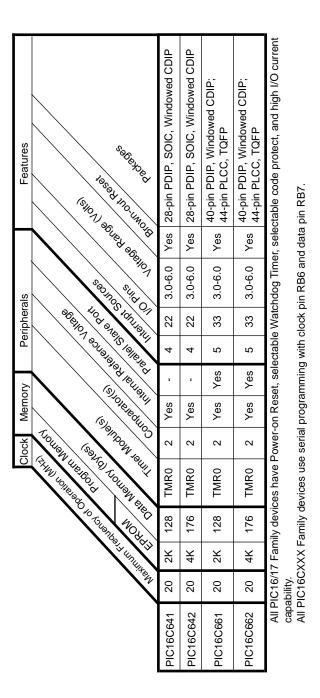

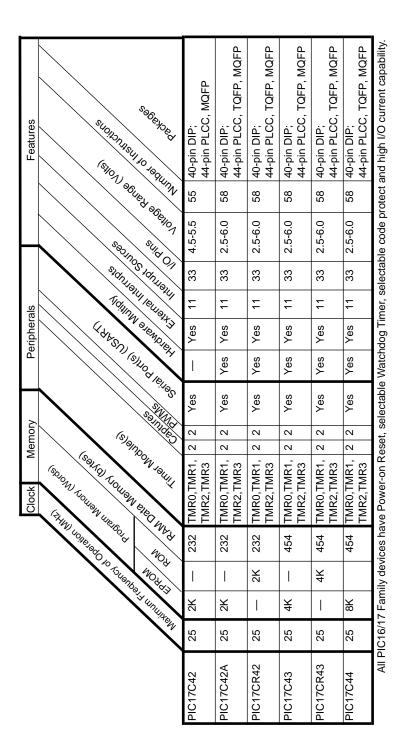

#### TABLE 1-1: PIC16C64X & PIC16C66X DEVICE FEATURES

| Address   | Name                 | Bit 7                | Bit 6              | Bit 5         | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0        | Value on<br>POR,<br>BOR,<br>PER | Value on<br>all other<br>resets <sup>(1)</sup> |

|-----------|----------------------|----------------------|--------------------|---------------|----------------|---------------|----------------|--------------|--------------|---------------------------------|------------------------------------------------|

| Bank 0    |                      |                      |                    |               | •              |               | •              |              | •            | •                               |                                                |

| 00h       | INDF                 | Addressing           | this location      | uses conte    | nts of FSR to  | address dat   | a memory (I    | not a physic | al register) | XXXX XXXX                       | xxxx xxxx                                      |

| 01h       | TMR0                 | Timer0 Mod           | dule's Regist      |               | XXXX XXXX      | uuuu uuuu     |                |              |              |                                 |                                                |

| 02h       | PCL                  | Program C            | ounter's (PC)      | ) Least Sign  | ificant Byte   |               |                |              |              | 0000 0000                       | 0000 0000                                      |

| 03h       | STATUS               | IRP <sup>(2)</sup>   | RP1 <sup>(2)</sup> | RP0           | TO             | PD            | Z              | DC           | С            | 0001 1xxx                       | 000q quuu                                      |

| 04h       | FSR                  | Indirect dat         | a memory ad        | dress point   | er             | 1             |                |              |              | XXXX XXXX                       | uuuu uuuu                                      |

| 05h       | PORTA                | _                    | _                  | PORTA Da      | ta Latch wher  | n written: PC | ORTA pins w    | hen read     |              | xx 0000                         | xu 0000                                        |

| 06h       | PORTB                | PORTB Da             | ta Latch whe       | n written: P  | ORTB pins wh   | nen read      | · ·            |              |              | XXXX XXXX                       | uuuu uuuu                                      |

| 06h       | PORTC                | PORTC Da             | ta Latch whe       | en written: P | ORTC pins wi   | nen read      |                |              |              | xxxx xxxx                       | uuuu uuuu                                      |

| 06h       | PORTD <sup>(3)</sup> | PORTD Da             | ta Latch whe       | en written: P | ORTD pins wi   | nen read      |                |              |              | XXXX XXXX                       | uuuu uuuu                                      |

| 06h       | PORTE <sup>(3)</sup> | _                    | _                  | _             |                | _             | RE2            | RE1          | RE0          | xxx                             | uuu                                            |

| 0Ah       | PCLATH               | _                    | _                  | _             | Write buffer   | for upper 5 l | bits of progra | am counter   |              | 0 0000                          | 0 0000                                         |

| 0Bh       | INTCON               | GIE                  | PEIE               | TOIE          | INTE           | RBIE          | TOIF           | INTF         | RBIF         | 0000 000x                       | 0000 000u                                      |

| 0Ch       | PIR1                 | PSPIF <sup>(4)</sup> | CMIF               | _             | _              | _             | _              | _            | _            | 00                              | 00                                             |

| 0Dh-1Eh   | Unimplemented        |                      |                    |               |                |               |                |              |              | -                               | _                                              |

| 1Fh       | CMCON                | C2OUT                | C1OUT              | _             | _              | CIS           | CM2            | CM1          | CM0          | 00 0000                         | 00 0000                                        |

| Bank 1    | •                    |                      |                    |               |                |               | •              |              |              |                                 |                                                |

| 80h       | INDF                 | Addressing           | this location      | uses conte    | nts of FSR to  | address dat   | a memory (I    | not a physic | al register) | XXXX XXXX                       | xxxx xxxx                                      |

| 81h       | OPTION               | RBPU                 | INTEDG             | TOCS          | TOSE           | PSA           | PS2            | PS1          | PS0          | 1111 1111                       | 1111 1111                                      |

| 82h       | PCL                  | Program C            | ounter's (PC)      | Least Sign    | ificant Byte   |               |                |              | 1            | 0000 0000                       | 0000 0000                                      |

| 83h       | STATUS               | IRP <sup>(2)</sup>   | RP1 <sup>(2)</sup> | RP0           | TO             | PD            | Z              | DC           | С            | 0001 1xxx                       | 000q quuu                                      |

| 84h       | FSR                  | Indirect dat         | a memory ad        | dress point   | er             |               |                |              |              | XXXX XXXX                       | uuuu uuuu                                      |

| 85h       | TRISA                | _                    | _                  | PORTA Da      | ta Direction R | egister       |                |              |              | 11 1111                         | 11 1111                                        |

| 86h       | TRISB                | PORTB Da             | ta Direction I     | Register      |                | -             |                |              |              | 1111 1111                       | 1111 1111                                      |

| 86h       | TRISC                | PORTC Da             | ta Direction       | Register      |                |               |                |              |              | 1111 1111                       | 1111 1111                                      |

| 86h       | TRISD <sup>(3)</sup> | PORTD Da             | ta Direction       | Register      |                |               |                |              |              | 1111 1111                       | 1111 1111                                      |

| 86h       | TRISE <sup>(3)</sup> | IBF                  | OBF                | IBOV          | PSPMODE        | _             | TRISE2         | TRISE1       | TRISE0       | 0000 -111                       | 0000 -111                                      |

| 8Ah       | PCLATH               | —                    | —                  | —             | Write buffer   | for upper 5 l | bits of progra | am counter   |              | 0 0000                          | 0 0000                                         |

| 8Bh       | INTCON               | GIE                  | PEIE               | TOIE          | INTE           | RBIE          | TOIF           | INTF         | RBIF         | 0000 000x                       | 0000 000x                                      |

| 8Ch       | PIE1                 | PSPIE <sup>(4)</sup> | CMIE               | —             | _              | —             | _              | —            | —            | 00                              | 00                                             |

| 8Dh       | Unimplemented        |                      |                    |               |                |               |                |              |              |                                 | -                                              |

| 8Eh       | PCON                 | MPEEN                | _                  | _             | _              | _             | PER            | POR          | BOR          | uqqq                            | uuuu                                           |

| 8Fh-9Eh   | Unimplemented        |                      |                    |               |                |               | •              |              |              | _                               | _                                              |

| 0111-9211 |                      |                      |                    |               |                |               |                |              |              |                                 |                                                |

Legend: - = unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

1: Other (non power-up) resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: The IRP and RP1 bits are reserved, always maintain these bits clear.

3: The PORTD, PORTE, TRISD, and TRISE registers are not implemented on the PIC16C641/642.

4: Bits PSPIE and PSPIF are reserved on the PIC16C641/642, always maintain these bits clear. Note

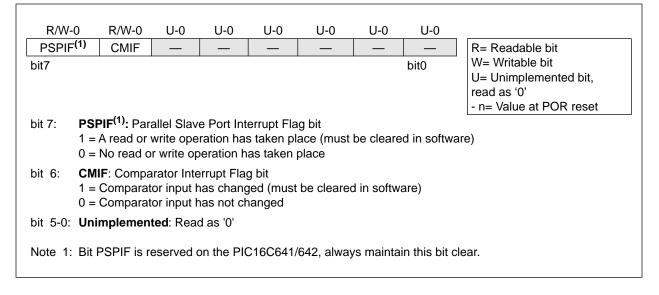

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the comparator and Parallel Slave Port interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 4-9: PIR1 REGISTER (ADDRESS 0Ch)

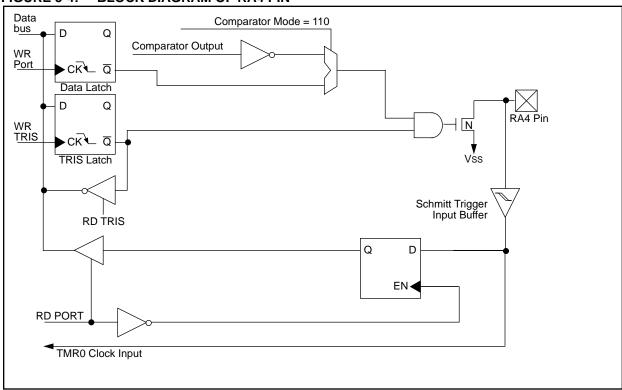

# FIGURE 5-4: BLOCK DIAGRAM OF RA4 PIN

# TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                       |

|--------------|-------|----------------|------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input.                                                              |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input.                                                              |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output.                                               |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output.                                                       |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output. Output is open drain type. |

| RA5          | bit5  | ST             | Input/output.                                                                                  |

Legend: ST = Schmitt Trigger input

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------------|

| 05h     | PORTA | —     |       | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx 0000                  | uu 0000                         |

| 85h     | TRISA | —     | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                         |

| 1Fh     | CMCON | C2OUT | C10UT | _      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                  | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000                | 000- 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

NOTES:

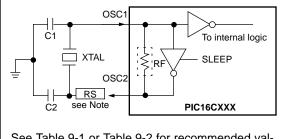

### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16CXXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 9-2). The PIC16CXXX oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 9-3).

### FIGURE 9-2: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 9-1 or Table 9-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

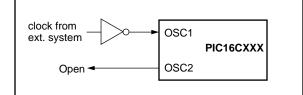

#### FIGURE 9-3: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

# TABLE 9-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges tested:                                                                                                                                                                                                                                                                                                                                                                                         |                     |                    |       |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|-------|--|--|--|--|--|

| Mode Freq OSC1                                                                                                                                                                                                                                                                                                                                                                                         |                     |                    |       |  |  |  |  |  |

| XT                                                                                                                                                                                                                                                                                                                                                                                                     | 455 kHz             | 22 - 100           |       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | 2.0 MHz             | 15 - 68 pl         | F     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | 4.0 MHz             | 15 - 68 p          | F     |  |  |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                                                                                                     | 8.0 MHz             | 8.0 MHz 10 - 68 pF |       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | 16.0 MHz 10 - 22 pF |                    |       |  |  |  |  |  |

| Note: Recommended values of C1 and C2 are identical<br>to the ranges tested table.<br>Higher capacitance increases the stability of the<br>oscillator but also increases the start-up time.<br>These values are for design guidance only. Since<br>each resonator has its own characteristics, the<br>user should consult the resonator manufacturer for<br>appropriate values of external components. |                     |                    |       |  |  |  |  |  |

| Resonators used:                                                                                                                                                                                                                                                                                                                                                                                       |                     |                    |       |  |  |  |  |  |

| 455 kHz                                                                                                                                                                                                                                                                                                                                                                                                | Panasonic EFO-A4    | 55K04B             | ±0.3% |  |  |  |  |  |

| 2.0 MHz                                                                                                                                                                                                                                                                                                                                                                                                | Murata Erie CSA2.   | 00MG               | ±0.5% |  |  |  |  |  |

| 400 KHZ                                               | Fanasonic EFO-A400K04D | ±0.3% |  |  |  |

|-------------------------------------------------------|------------------------|-------|--|--|--|

| 2.0 MHz                                               | Murata Erie CSA2.00MG  | ±0.5% |  |  |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG  | ±0.5% |  |  |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT  | ±0.5% |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ±0.5%                 |                        |       |  |  |  |

| All resonators used did not have built-in capacitors. |                        |       |  |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (PRELIMINARY)

| Mode | Freq    | OSC1        | OSC2         |

|------|---------|-------------|--------------|

| LP   | 32 kHz  | 68 - 100 pF | 68 - 100 pF  |

|      | 200 kHz | 15 - 30 pF  | 15 - 30 pF   |

| XT   | 100 kHz | 68 - 150 pF | 150 - 200 pF |

|      | 2 MHz   | 15 - 30 pF  | 15 - 30 pF   |

|      | 4 MHz   | 15 - 30 pF  | 15 - 30 pF   |

| HS   | 8 MHz   | 15 - 30 pF  | 15 - 30 pF   |

|      | 10 MHz  | 15 - 30 pF  | 15 - 30 pF   |

|      | 20 MHz  | 15 - 30 pF  | 15 - 30 pF   |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

| Crystals used: |                       |          |  |  |  |  |

|----------------|-----------------------|----------|--|--|--|--|

| 32.768 kHz     | Epson C-001R32.768K-A | ± 20 PPM |  |  |  |  |

| 100 kHz        | Epson C-2 100.00 KC-P | ± 20 PPM |  |  |  |  |

| 200 kHz        | STD XTL 200.000 kHz   | ± 20 PPM |  |  |  |  |

| 2.0 MHz        | ECS ECS-20-S-2        | ± 50 PPM |  |  |  |  |

| 4.0 MHz        | ECS ECS-40-S-4        | ± 50 PPM |  |  |  |  |

| 10.0 MHz       | ECS ECS-100-S-4       | ± 50 PPM |  |  |  |  |

| 20.0 MHz       | ECS ECS-200-S-4       | ± 50 PPM |  |  |  |  |

# 9.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) Brown-out Reset (BOR)

- f) Parity Error Reset (PER)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR, WDT reset, Brown-out Reset, Parity Error Reset, and on MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the reset. See Table 9-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 9-7.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 12-6 for pulse width specification.

# FIGURE 9-7: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# **PIC16C64X & PIC16C66X**

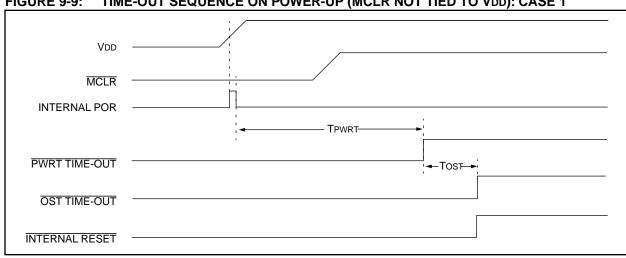

#### FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

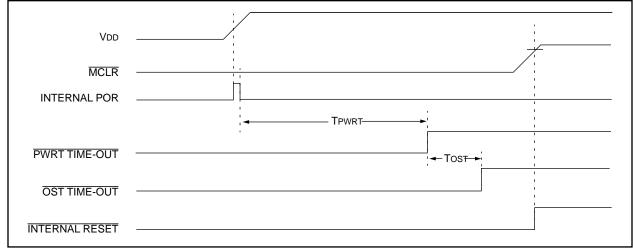

# FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

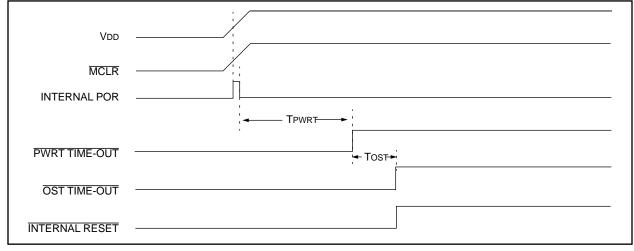

# FIGURE 9-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

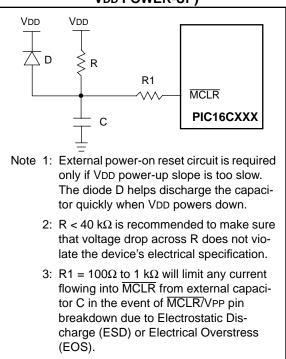

#### FIGURE 9-12: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

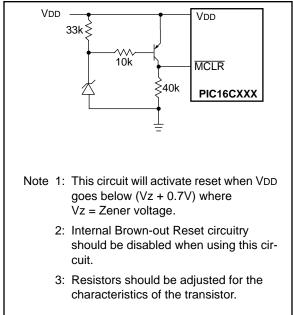

# FIGURE 9-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

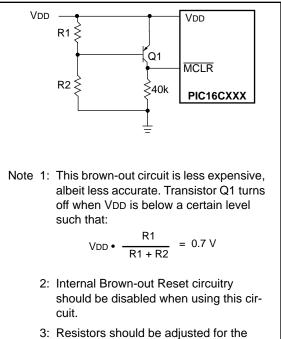

# FIGURE 9-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

characteristics of the transistor.

NOTES:

# **PIC16C64X & PIC16C66X**

#### 12.3 DC Characteristics: PIC16C641/661 (Commercial, Industrial, Automotive) PIC16C642/662 (Commercial, Industrial, Automotive) PIC16LC641/661 (Commercial, Industrial) PIC16LC642/662 (Commercial, Industrial)

|              |                            | Standard Operating Conditions (        | unless othe           | erwise             | stated)                           |                 |                                                                                        |

|--------------|----------------------------|----------------------------------------|-----------------------|--------------------|-----------------------------------|-----------------|----------------------------------------------------------------------------------------|

|              |                            |                                        | $\leq$ TA $\leq$ +85  |                    | for industrial,                   |                 |                                                                                        |

|              |                            | 0°C                                    | $\leq$ TA $\leq$ +70  | -                  | commercial, a                     | and             |                                                                                        |

|              |                            |                                        | $\leq$ TA $\leq$ +12  |                    | automotive                        |                 |                                                                                        |

|              |                            | Operating voltage VDD range as         |                       | 1                  | -                                 |                 |                                                                                        |

| Param<br>No. | Sym                        | Characteristic                         | Min                   | Тур<br>†           | Max                               | Unit            | Conditions                                                                             |

|              | VIL                        | Input Low Voltage                      |                       |                    |                                   |                 |                                                                                        |

|              |                            | I/O ports                              |                       |                    |                                   |                 |                                                                                        |

| D030         |                            | with TTL buffer                        | Vss                   | -                  | 0.15Vdd                           | V               | For eptire Voo range                                                                   |

|              |                            |                                        | Vss                   | -                  | 0.8V                              | V               | 4.5√ ≤ √DD ≤ 5.5√                                                                      |

| D031         |                            | with Schmitt Trigger input             | Vss                   | -                  | 0.2Vdd                            | V               |                                                                                        |

| D032         |                            | MCLR, RA4/T0CKI,OSC1 (in               | Vss                   | -                  | 0.2Vdd                            | V~              | (1)                                                                                    |

|              |                            | RC mode)                               |                       |                    |                                   | < ,             | $\sim$                                                                                 |

| D033         |                            | OSC1 (XT and HS modes)                 | Vss                   | -                  | 0.3VDD                            | $ \lambda $     | $\searrow$                                                                             |

|              |                            | OSC1 (LP modes)                        | Vss                   | -                  | 0.6VDD 1.0                        | v \             |                                                                                        |

|              | Viн                        | Input High Voltage                     |                       |                    | $\langle$                         | $\overline{\ }$ |                                                                                        |

|              |                            | I/O ports                              |                       |                    | $\langle $                        | $\land$         |                                                                                        |

| D040         |                            | with TTL buffer                        | 2.0                   | -/                 | VQD                               | ×/              |                                                                                        |

| D041         |                            | with Schmitt Trigger input             | 0.25Vdd               | L- \               | VDD                               | v               |                                                                                        |

|              |                            |                                        | to 0.8V               | $\left[ \right] $  | $\backslash \setminus \checkmark$ |                 |                                                                                        |

| D042         |                            | MCLR RA4/T0CKI                         | 0.8VDD                | ( A )              | VQD                               | V               |                                                                                        |

| D043         |                            | OSC1 (XT, HS, LP modes)                | Q.7VQD                | $\left  - \right $ | VDD                               | V               |                                                                                        |

| D043A        |                            | OSC1 (RC mode)                         | 0.9VDD                | 7)                 | \ <u> </u>                        | V               | (1)                                                                                    |

| D070         | IPURB                      | PORTB weak pull-up current             | 50                    | 200-               | 400                               | μA              | VDD = 5.0V, VPIN = VSS                                                                 |

|              | lı∟                        | Input Leakage Current <sup>(2,3)</sup> | $  \setminus \rangle$ | $\bigvee$          |                                   |                 |                                                                                        |

|              |                            | I/O ports (Except PORTA)               | $  \rangle$           |                    |                                   |                 |                                                                                        |

|              |                            |                                        | $\bigtriangleup$      | -                  | ±1.0                              | μA              | $VSS \leq VPIN \leq VDD,$                                                              |

| Doco         |                            | PORTA                                  |                       |                    |                                   |                 | pin at hi-impedance                                                                    |

| D060         |                            |                                        | -                     | -                  | ±0.5                              | μA              | Vss $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                     |

| D061         |                            | RA4/T0CKI                              |                       | _                  | ±1.0                              |                 | $V_{SS} \leq V_{PIN} \leq V_{DD}$                                                      |

| D063         |                            | OSC1, MCLR                             | -                     |                    | ±1.0<br>±5.0                      | μΑ              | $V_{SS} \leq V_{PIN} \leq V_{DD}$<br>$V_{SS} \leq V_{PIN} \leq V_{DD}$ , XT, HS and LP |

| D063         |                            | USUI, MCLR                             | -                     | -                  | ±5.0                              | μA              | $VSS \leq VPIN \leq VDD, \times 1, HS and LP osc configuration$                        |

|              | Vol                        | Output Low Voltage                     |                       |                    |                                   |                 |                                                                                        |

| D080         |                            | 1/Q ports                              | _                     | _                  | 0.6                               | v               | IOL = 8.5 mA, VDD = 4.5V,                                                              |

| DUUU         | 1                          |                                        | _                     | _                  | 0.0                               | v               | -40° to +85°C                                                                          |

| <            | $\langle \langle \rangle$  | ∤/ ~                                   | -                     | -                  | 0.6                               | v               | $IOL = 7.0 \text{ MA}, \text{VDD} = 4.5\text{V}, +125^{\circ}\text{C}$                 |

| D083         | $ $ $\backslash$ $\rangle$ | OSC2/CLKOUT                            | -                     | -                  | 0.6                               | v               | IOL = 1.6  mA, VDD = 4.5 V,                                                            |

| 2000         |                            | 5                                      |                       |                    | 0.0                               | , v             | -40° to +85°C                                                                          |

|              |                            | (RC only)                              | -                     | -                  | 0.6                               | v               | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                       |

| * -          | Those n                    | arameters are characterized but r      |                       | I                  | - • -                             |                 | , <u> </u>                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C64X & PIC16C66X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

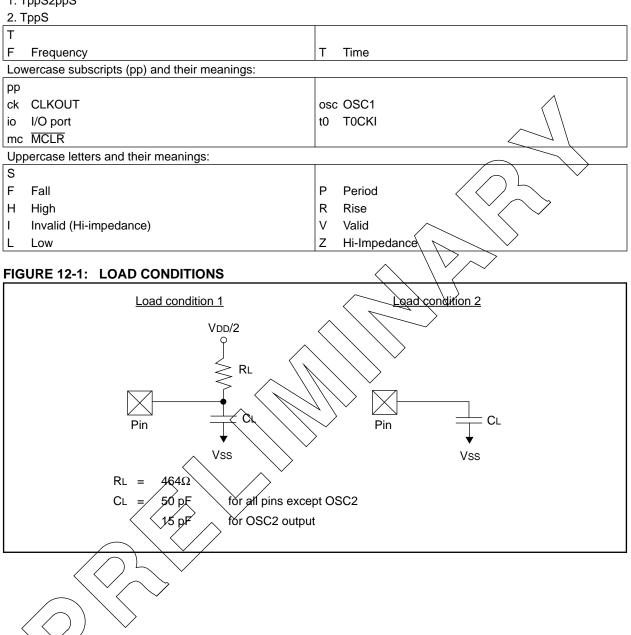

# 12.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

# 12.5 Timing Diagrams and Specifications

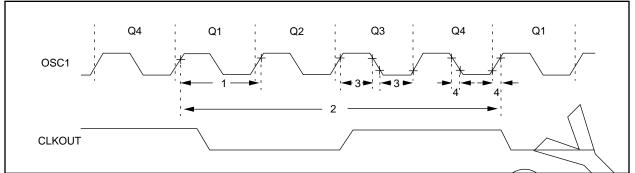

# FIGURE 12-2: EXTERNAL CLOCK TIMING

| <b>TABLE 12-4</b> : | EXTERNAL CLOCK TIMING REQUIREMENTS |  |

|---------------------|------------------------------------|--|

| IADLL IZ=7.         |                                    |  |

| Param<br>No. | Sym   | Characteristic                          | Min         | Тур†                          | Max    | Units          | Conditions              |

|--------------|-------|-----------------------------------------|-------------|-------------------------------|--------|----------------|-------------------------|

|              | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC          | _                             | 4      | Ӎ҉Ӏӡ           | XT and RC osc mode,     |

|              |       |                                         |             |                               |        | $  \setminus $ | VDD = 5.0V              |

|              |       |                                         | DC          | —                             | 20 \   | MHz            | HS osc mode             |

|              |       |                                         | DC          |                               | 200    | kHz '          | LP osc mode             |

|              |       | Oscillator Frequency <sup>(1)</sup>     | DC          | $  - \langle$                 | 4      | MHZ            | ŘC osc mode, VDD = 5.0V |

|              |       |                                         | 0.1         |                               | 4      | MHz            | XT osc mode             |

|              |       |                                         | 4           | $\langle \mathcal{A} \rangle$ | 20     | MHz            | HS osc mode             |

|              |       |                                         | 5 <         | <u> </u>                      | 200    | kHz            | LP osc mode             |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250         | ///                           |        | ns             | XT and RC osc mode      |

|              |       | ( · · · · · · · · · · · · · · · · · · · | 50          | $(\mathcal{H})$               | >      | ns             | HS osc mode             |

|              |       | $\square$                               | 5           | $\searrow$                    | —      | μs             | LP osc mode             |

|              |       | Oscillator Period <sup>(1)</sup>        | 250         | $\searrow$                    | —      | ns             | RC osc mode             |

|              |       |                                         | 250         | -                             | 10,000 | ns             | XT osc mode             |

|              |       |                                         | <u></u> \$0 | —                             | 250    | ns             | HS osc mode             |

|              |       |                                         | 5           | —                             | —      | μs             | LP osc mode             |

| 2            | TCY   | Instruction Cycle Time (1)              | 200         | —                             | DC     | ns             | TCY = FOSC/4            |

| 3*           | TosL, | External Clock in (OSC1)                | 100         | —                             | —      | ns             | XT osc mode             |

|              | TosH  | High or Low Time                        | 2.5         | —                             | _      | μs             | LP osc mode             |

|              |       |                                         | 15          |                               |        | ns             | HS osc mode             |

| 4*           | TosR  | External Clock in (OSC1)                | _           | —                             | 25     | ns             | XT osc mode             |

|              | TosF  | Rise or Fall Time                       | —           | —                             | 50     | ns             | LP osc mode             |

|              |       |                                         |             |                               | 15     | ns             | HS osc mode             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

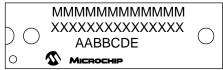

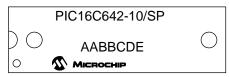

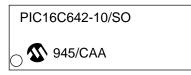

#### 14.1 Package Marking Information

28-Lead SOIC

Example

### Example

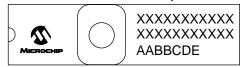

# 28-Lead Side Brazed Skinny Windowed

Example

Legend:

MM...MMicrochip part number information

XX...X

Customer specific information\*

AA

Year code (last 2 digits of calendar year)

BB

Week code (week of January 1 is week '01')

C

Facility code of the plant at which wafer is manufactured

C = Chandler, Arizona, U.S.A.

D

Mask revision number

E

Assembly code of the plant or country of origin in which part was assembled

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\*Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

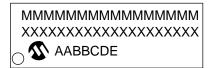

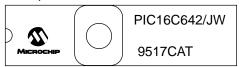

# 14.2 Package Marking Information

#### 40-Lead PDIP

Example

PIC16C662-04/P

9512CAA

Similar Microchip

Example

# Example

Example

| Legend | : MMMMicrochip part number information                    |

|--------|-----------------------------------------------------------|

| XXX    | Customer specific information*                            |

| AA     | Year code (last 2 digits of calendar year)                |

| BB     | Week code (week of January 1 is week '01')                |

| С      | Facility code of the plant at which wafer is manufactured |

|        | C = Chandler, Arizona, U.S.A.                             |

| D      | Mask revision number                                      |

| E      | Assembly code of the plant or country of origin in which  |

|        | part was assembled                                        |

|        |                                                           |

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\*Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1996 Microchip Technology Inc.

NOTES:

# APPENDIX A: ENHANCEMENTS

The following are the list of enhancements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14 bits. This allows larger page sizes both in program memory (4K now as opposed to 512 before) and register file (up to 176 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- 3. Data memory paging is slightly redefined. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Six different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers can be invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. Timer0 clock input, T0CKI pin is also a port pin (RA4/T0CKI) and has a TRIS bit.

- 14. FSR is made a full 8-bit register.

- 15. "In-circuit programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, VSS, VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR), a Brown-out Reset status bit (BOR), a Parity Error Reset (PER), and a Memory Parity Enable (MPEEN) bit.

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- 18. PORTA inputs are now Schmitt Trigger inputs.

- 19. Brown-out Reset circuitry has been added.

# APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

© 1996 Microchip Technology Inc.

# E.8 PIC17CXX Family of Devices

# **ON-LINE SUPPORT**

Microchip provides two methods of on-line support. These are the Microchip BBS and the Microchip World Wide Web (WWW) site.

Use Microchip's Bulletin Board Service (BBS) to get current information and help about Microchip products. Microchip provides the BBS communication channel for you to use in extending your technical staff with microcontroller and memory experts.

To provide you with the most responsive service possible, the Microchip systems team monitors the BBS, posts the latest component data and software tool updates, provides technical help and embedded systems insights, and discusses how Microchip products provide project solutions.

The web site, like the BBS, is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp.mchip.com/biz/mchip

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

#### **Connecting to the Microchip BBS**

Connect worldwide to the Microchip BBS using either the Internet or the CompuServe  $^{\ensuremath{\mathbb{R}}}$  communications network.

#### Internet:

You can telnet or ftp to the Microchip BBS at the address:

#### mchipbbs.microchip.com

#### **CompuServe Communications Network:**

When using the BBS via the Compuserve Network, in most cases, a local call is your only expense. The Microchip BBS connection does not use CompuServe membership services, therefore you do not need CompuServe membership to join Microchip's BBS. There is no charge for connecting to the Microchip BBS. The procedure to connect will vary slightly from country to country. Please check with your local CompuServe agent for details if you have a problem. CompuServe service allow multiple users various baud rates depending on the local point of access.

The following connect procedure applies in most locations.

- 1. Set your modem to 8-bit, No parity, and One stop (8N1). This is not the normal CompuServe setting which is 7E1.

- 2. Dial your local CompuServe access number.

- 3. Depress the <Enter> key and a garbage string will appear because CompuServe is expecting a 7E1 setting.

- 4. Type +, depress the <Enter> key and "Host Name:" will appear.

- 5. Type MCHIPBBS, depress the <Enter> key and you will be connected to the Microchip BBS.

In the United States, to find the CompuServe phone number closest to you, set your modem to 7E1 and dial (800) 848-4480 for 300-2400 baud or (800) 331-7166 for 9600-14400 baud connection. After the system responds with "Host Name:", type NETWORK, depress the <Enter> key and follow CompuServe's directions.

For voice information (or calling from overseas), you may call (614) 723-1550 for your local CompuServe number.

Microchip regularly uses the Microchip BBS to distribute technical information, application notes, source code, errata sheets, bug reports, and interim patches for Microchip systems software products. For each SIG, a moderator monitors, scans, and approves or disapproves files submitted to the SIG. No executable files are accepted from the user community in general to limit the spread of computer viruses.

#### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-602-786-7302 for the rest of the world.

**Trademarks:** The Microchip name, logo, PIC, PICSTART, PICMASTER, and are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB, PRO MATE, and *fuzzy*LAB, are trademarks and SQTP is a service mark of Microchip in the U.S.A.

*fuzzy*TECH is a registered trademark of Inform Software Corporation. IBM, IBM PC-AT are registered trademarks of International Business Machines Corp. Pentium is a trademark of Intel Corporation. Windows is a trademark and MS-DOS, Microsoft Windows are registered trademarks of Microsoft Corporation. CompuServe is a registered trademark of CompuServe Incorporated.

All other trademarks mentioned herein are the property of their respective companies.

NOTES: