Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c642-10i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

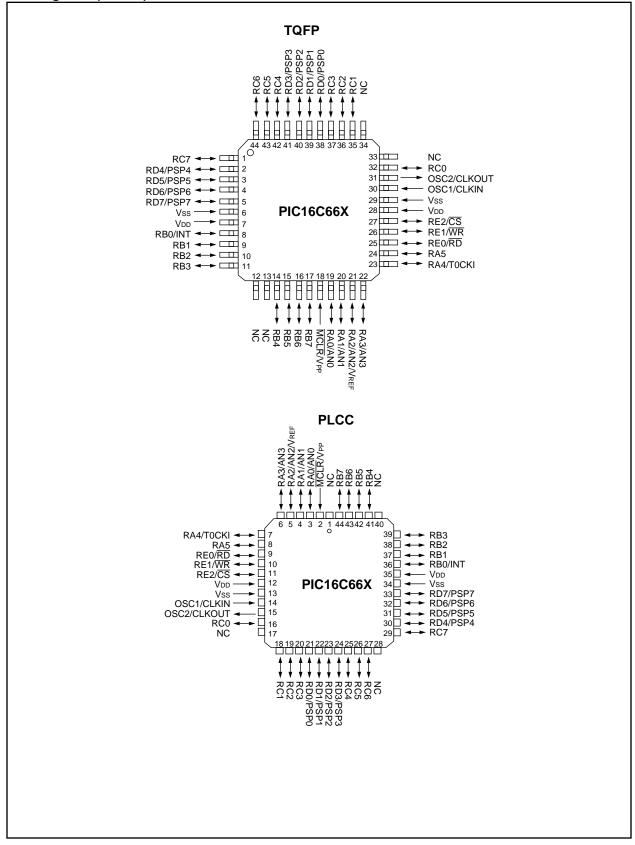

## **PIC16C64X & PIC16C66X**

### Pin Diagrams (Cont.'d)

### **Table of Contents**

| 1.0         | General Description                            | 5    |

|-------------|------------------------------------------------|------|

|             | PIC16C64X & PIC16C66X Device Varieties         |      |

|             | Architectural Overview                         |      |

| 4.0         | Memory Organization                            | .17  |

| 5.0         | I/O Ports                                      | .29  |

| 6.0         | Timer0 Module                                  | . 41 |

| 7.0         | Comparator Module                              | . 47 |

| 8.0         | Voltage Reference Module                       | .53  |

| 9.0         | Special Features of the CPU                    | . 55 |

| 10.0        | Instruction Set Summary                        | .73  |

| 11.0        | Development Support                            | . 87 |

| 12.0        | Electrical Specifications                      | . 91 |

| 13.0        | Device Characterization Information            | 03   |

| 14.0        | Packaging Information 1                        | 105  |

| Appendix    | KA: Enhancements1                              | 15   |

| Appendix    | KB: Compatibility1                             | 115  |

| Appendix    | x C: What's New 1                              | 16   |

| Appendix    | x D: What's Changed1                           | 16   |

| Appendix    | x E: PIC16/17 Microcontrollers 1               | 117  |

| Pin Com     | patibility1                                    | 125  |

| Index       |                                                | 127  |

| List of Ex  | xamples                                        | 129  |

| List of Fig | gures                                          | 129  |

| List of Ta  | ables1                                         | 30   |

| On-Line     | Support                                        | 31   |

|             | Response                                       |      |

| PIC16C6     | 34X & PIC16C66X Product Identification System1 | 135  |

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

| Name         | Pin #  | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|--------------|--------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 9      | I             | ST/CMOS               | Oscillator crystal input or external clock source input.                                                                                                                                                 |

| OSC2/CLKOUT  | 10     | 0             | _                     | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp     | 1      | I/P           | ST                    | Master clear (reset) input or programming voltage input. This pin is<br>an active low reset to the device.                                                                                               |

|              |        |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 2      | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                 |

| RA1/AN1      | 3      | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                 |

| RA2/AN2/VREF | 4      | I/O           | ST                    | Analog comparator input or VREF output.                                                                                                                                                                  |

| RA3/AN3      | 5      | I/O           | ST                    | Analog comparator input or comparator output.                                                                                                                                                            |

| RA4/T0CKI    | 6      | I/O           | ST                    | Can be selected to be the clock input to the Timer0 timer/counter<br>or a comparator output. Output is open drain type.                                                                                  |

| RA5          | 7      | I/O           | ST                    |                                                                                                                                                                                                          |

|              |        |               |                       | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-ups on all inputs.                                                                                      |

| RB0/INT      | 21     | I/O           | TTL/ST(1)             | RB0 can also be selected as an external interrupt pin.                                                                                                                                                   |

| RB1          | 22     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2          | 23     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3          | 24     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4          | 25     | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5          | 26     | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6          | 27     | I/O           | TTL/ST(2)             | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 28     | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

|              |        |               |                       | PORTC is a bi-directional I/O port.                                                                                                                                                                      |

| RC0          | 11     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC1          | 12     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC2          | 13     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC3          | 14     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC4          | 15     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC5          | 16     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC6          | 17     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC7          | 18     | I/O           | ST                    |                                                                                                                                                                                                          |

| Vss          | 8,19   | Р             | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd          | 20     | Р             | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend:      |        | output        |                       | = input/output P = power                                                                                                                                                                                 |

|              | I = in | put           |                       | not used ST = Schmitt Trigger input                                                                                                                                                                      |

## TABLE 3-1:PIC16C641/642 PINOUT DESCRIPTION

TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

## **PIC16C64X & PIC16C66X**

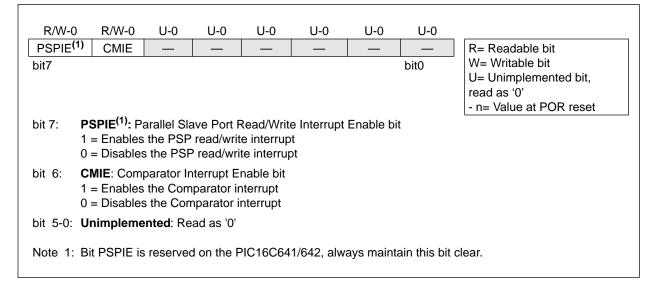

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the comparator and Parallel Slave Port interrupts.

### FIGURE 4-8: PIE1 REGISTER (ADDRESS 8Ch)

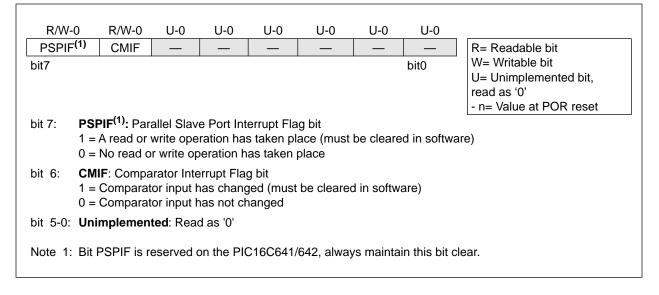

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the comparator and Parallel Slave Port interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 4-9: PIR1 REGISTER (ADDRESS 0Ch)

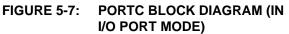

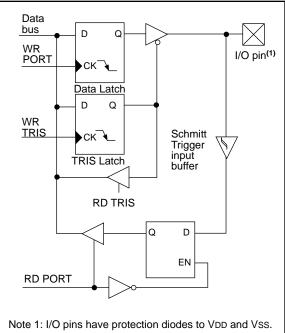

#### 5.3 PORTC and TRISC Registers

PORTC is an 8-bit bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC pins have Schmitt Trigger input buffers.

#### EXAMPLE 5-3: INITIALIZING PORTC

| CLRF  | PORTC       | ; Initialize PORTC by   |

|-------|-------------|-------------------------|

|       |             | ; clearing output       |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | 0xCF        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISC       | ; Set RC<3:0> as inputs |

|       |             | ; RC<5:4> as outputs    |

|       |             | ; RC<7:6> as inputs     |

| Name | Bit# | Buffer Type | Function     |

|------|------|-------------|--------------|

| RC0  | bit0 | ST          | Input/output |

| RC1  | bit1 | ST          | Input/output |

| RC2  | bit2 | ST          | Input/output |

| RC3  | bit3 | ST          | Input/output |

| RC4  | bit4 | ST          | Input/output |

| RC5  | bit5 | ST          | Input/output |

| RC6  | bit6 | ST          | Input/output |

| RC7  | bit7 | ST          | Input/output |

Legend: ST = Schmitt Trigger input

#### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

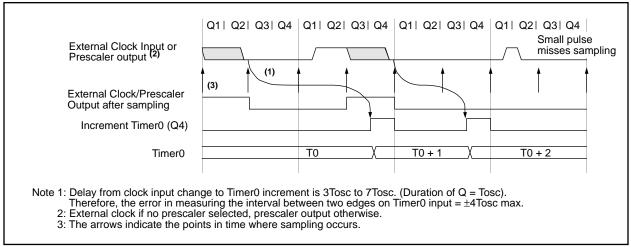

### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41, and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must be followed even if the WDT is disabled.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

|        |             |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2.

## EXAMPLE 6-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

## TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6                    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|--------|--------------------------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------|

| 01h     | TMR0   | Timer0 | Timer0 module's register |        |        |        |        |        |        |                          | uuuu uuuu                 |

| 0Bh/8Bh | INTCON | GIE    | PEIE                     | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h     | OPTION | RBPU   | INTEDG                   | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h     | TRISA  | —      | _                        | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

| Address | Name   | Bit 7                | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|----------------------|-------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT                | C1OUT | _      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                 | 00 0000                         |

| 9Fh     | VRCON  | VREN                 | VROE  | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000               | 000- 0000                       |

| 0Bh/8Bh | INTCON | GIE                  | PEIE  | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | CMIF  | —      | —      |        |        | _      | _      | 00                      | 00                              |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | CMIE  | _      |        | —      | _      | _      | _      | 00                      | 00                              |

| 85h     | TRISA  | _                    | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

Note 1: These bits are reserved on the PIC16C641/642, always maintain these bits clear.

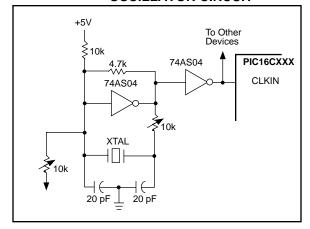

#### 9.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 9-4 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 9-4: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

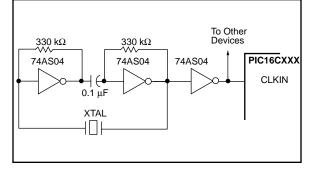

Figure 9-5 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 9-5: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

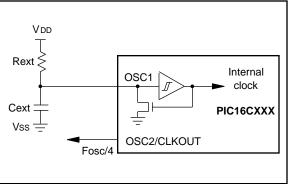

### 9.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-6 shows how the R/C combination is connected to the PIC16CXXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-3 for waveform).

### FIGURE 9-6: RC OSCILLATOR MODE

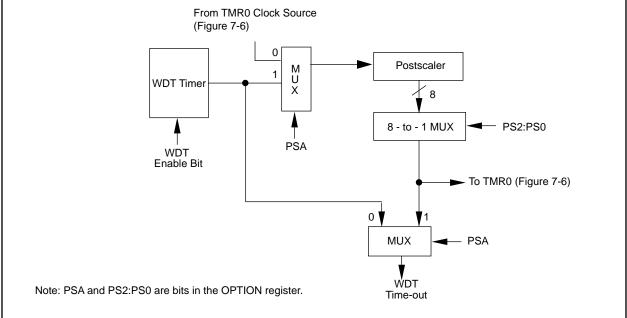

## 9.7 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. The block diagram is shown in Figure 9-17. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. This means that the WDT will run, even if the clock on the OSC1 and OSC2 pins has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation, this is known as a WDT wake-up. The WDT can be permanently disabled by clearing configuration bit WDTE (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out period varies with temperature, VDD and process variations from part to part (see DC specs). If longer time-outs are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT, under software control, by writing to the OPTION register. Thus, time-out periods of up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out (WDT Reset and WDT wake-up).

9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When the prescaler is assigned to the WDT, always execute a CLRWDT instruction before changing the prescale value, otherwise a WDT reset may occur.

## FIGURE 9-17: WATCHDOG TIMER BLOCK DIAGRAM

### FIGURE 9-18: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | MPEEN | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 9-1 for details of the operation of these bits.

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | Э    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0000   | 0011 | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL AI | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   |        |      | Z        |       |

#### TABLE 10-2: INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## **PIC16C64X & PIC16C66X**

| NOP              | No Operation  |      |      |      |  |  |

|------------------|---------------|------|------|------|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |

| Operands:        | None          |      |      |      |  |  |

| Operation:       | No operation  |      |      |      |  |  |

| Status Affected: | None          |      |      |      |  |  |

| Encoding:        | 00            | 0000 | 0xx0 | 0000 |  |  |

| Description:     | No operation. |      |      |      |  |  |

| Words:           | 1             |      |      |      |  |  |

| Cycles:          | 1             |      |      |      |  |  |

| Example          | NOP           |      |      |      |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                    |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                   |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by set-<br>ting Global Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                   |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                   |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                              |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                              |  |  |  |  |

|                                                                                                    |                                                                                                                                                                    | gister                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                             |  |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [ label ]                                                                                          | OPTION                                                                                                                                                             | ١                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                             |  |  |

| None                                                                                               |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

| $(W) \rightarrow OPTION$                                                                           |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

| None                                                                                               |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

| 00                                                                                                 | 0000                                                                                                                                                               | 0110                                                                                                                                                                                                                                             | 0010                                                                                                                                                                                                                                                                                        |  |  |

| loaded in t<br>instruction<br>patibility w<br>Since OPT                                            | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a                                                                                                                     | DN register<br>ted for coo<br>C5X produ<br>readable/v                                                                                                                                                                                            | r. This<br>de com-<br>ucts.<br>vritable                                                                                                                                                                                                                                                     |  |  |

| 1                                                                                                  |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

|                                                                                                    |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

| To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction. |                                                                                                                                                                    |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |  |  |

|                                                                                                    | None<br>(W) → OI<br>None<br>00<br>The conter<br>loaded in t<br>instruction<br>patibility w<br>Since OPT<br>register, th<br>it.<br>1<br>1<br>To mainta<br>with futu | None<br>(W) → OPTION<br>None<br>00 0000<br>The contents of the<br>loaded in the OPTIC<br>instruction is suppor<br>patibility with PIC16<br>Since OPTION is a<br>register, the user ca<br>it.<br>1<br>1<br>To maintain upwa<br>with future PIC166 | None (W) → OPTION None 00 0000 0110 The contents of the W register loaded in the OPTION register instruction is supported for cod patibility with PIC16C5X produ Since OPTION is a readable/w register, the user can directly a it. 1 1 To maintain upward compa with future PIC16CXX produ |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $\begin{array}{l} k \rightarrow (W);\\ TOS \rightarrow PC \end{array}$                                                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |  |  |  |  |  |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                   |  |  |  |  |  |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>. ;W now has table value                                                                                                           |  |  |  |  |  |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                              |  |  |  |  |  |

|                  |                                                                                                                                                                                     |  |  |  |  |  |

# **PIC16C64X & PIC16C66X**

| SWAPF            | Swap Nibbles in f                                                                                                                                                       |           |        |            |      |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------------|------|--|--|

| Syntax:          | [label]                                                                                                                                                                 | SWAPF     | f,d    |            |      |  |  |

| Operands:        | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                          | 7         |        |            |      |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>),$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                               |           |        |            |      |  |  |

| Status Affected: | None                                                                                                                                                                    |           |        |            |      |  |  |

| Encoding:        | 00                                                                                                                                                                      | 1110      | dff    | f          | ffff |  |  |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0 the<br>result is placed in W register. If 'd' is 1<br>the result is placed in register 'f'. |           |        |            |      |  |  |

| Words:           | 1                                                                                                                                                                       |           |        |            |      |  |  |

| Cycles:          | 1                                                                                                                                                                       |           |        |            |      |  |  |

| Example          | SWAPF                                                                                                                                                                   | REG,      | 0      |            |      |  |  |

|                  | Before In                                                                                                                                                               | struction |        |            |      |  |  |

|                  |                                                                                                                                                                         | REG1      | =      | 0xA        | \$   |  |  |

|                  | After Inst                                                                                                                                                              | ruction   |        |            |      |  |  |

|                  |                                                                                                                                                                         | REG1<br>W | =<br>= | 0xA<br>0x5 |      |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                       |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] XORLW k                                                                                                   |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                 |  |  |  |  |  |

| Encoding:        | 11 1010 kkkk kkkk                                                                                                 |  |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| Words:           | 1                                                                                                                 |  |  |  |  |  |

| Cycles:          | 1                                                                                                                 |  |  |  |  |  |

| Example:         | XORLW 0xAF                                                                                                        |  |  |  |  |  |

|                  | Before Instruction                                                                                                |  |  |  |  |  |

|                  | W = 0xB5                                                                                                          |  |  |  |  |  |

|                  | After Instruction                                                                                                 |  |  |  |  |  |

|                  | W = 0x1A                                                                                                          |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |  |  |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |  |  |  |  |  |

| Example          |                                                                                                                                                                                     |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f    |                          |                       |              |  |  |

|------------------|--------------------------|--------------------------|-----------------------|--------------|--|--|

| Syntax:          | [ label ]                | XORWF                    | f,d                   |              |  |  |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1] |                          |                       |              |  |  |

| Operation:       | (W) .XOF                 | $R.(f) \to (f)$          | dest)                 |              |  |  |

| Status Affected: | Z                        |                          |                       |              |  |  |

| Encoding:        | 00                       | 0110                     | dff                   | f ffff       |  |  |

| Description:     | is 1 the res<br>'f'.     | th registe<br>ored in th | r 'f'. If '<br>e W re |              |  |  |

| Words:           | 1                        |                          |                       |              |  |  |

| Cycles:          | 1                        |                          |                       |              |  |  |

| Example          | XORWF                    | REG                      | 1                     |              |  |  |

|                  | Before In                | struction                |                       |              |  |  |

|                  |                          | REG<br>W                 | =<br>=                | 0xAF<br>0xB5 |  |  |

|                  | After Inst               | ruction                  |                       |              |  |  |

|                  |                          | REG<br>W                 | =<br>=                | 0x1A<br>0xB5 |  |  |

### 12.1 DC Characteristics: PIC16C641/642/661/662-04 (Commercial, Industrial, Automotive) PIC16C641/642/661/662-10 (Commercial, Industrial, Automotive) PIC16C641/642/661/662-20 (Commercial, Industrial, Automotive)

|               |                | Standard Operating Conditions (                                  | unless                | otherwi                                | se sta     | ted)     |                                                                                                      |  |

|---------------|----------------|------------------------------------------------------------------|-----------------------|----------------------------------------|------------|----------|------------------------------------------------------------------------------------------------------|--|

|               |                | Operating temperature -40°C                                      | ≤ Ta ≤                | +85°C                                  | for        | industr  | ial,                                                                                                 |  |

|               |                | 0°C                                                              |                       | $\leq$ TA $\leq$ +70°C commercial, and |            |          |                                                                                                      |  |

|               | 1              |                                                                  |                       | +125°C                                 |            | tomotiv  |                                                                                                      |  |

| Param<br>No.  | Sym            | Characteristic                                                   | Min                   | Тур†                                   | Мах        | Units    | Conditions                                                                                           |  |

| D001<br>D001A | Vdd            | Supply Voltage                                                   | 4.0<br>4.5            | -                                      | 6.0<br>5.5 | V<br>V   | XT, RC and LP osc configuration<br>HS osc configuration                                              |  |

| D002*         | Vdr            | RAM Data Retention Voltage <sup>(1)</sup>                        | 1.5                   | _                                      | _          | V        | Device in SLEEP mode                                                                                 |  |

| D003          | VPOR           | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | -                     | Vss                                    | -          | V        | See section on Power-on Reset for details                                                            |  |

| D004*         | SVDD           | VDD rise rate to ensure internal<br>Power-on Reset signal        | 0.05                  | _                                      | _          | V/ms     | See section on Power-on Reset for details                                                            |  |

| D005          | VBOR           | Brown-out Reset Voltage                                          | 3.7                   | 4.0                                    | 4.3        | V        | BODEN configuration bit is clear                                                                     |  |

|               |                |                                                                  | 3.7                   | 4.0                                    | 4.4        | V        | Automotive                                                                                           |  |

| D010          | IDD            | Supply Current <sup>(2)</sup>                                    | _                     | 2.7                                    | 5          | mA       | XT and RC ose configuration<br>Fose = $4$ MHz, VDD = 5.5V,<br>WDT disabled <sup>(4)</sup>            |  |

| D010A         |                |                                                                  | -                     | 35                                     | 70         | TRA      | LP osc configuration,<br>PIC16C64X & PIC16C66X-04 only<br>Fosc = 32 kHz, VDD = 4.0V,<br>WDT disabled |  |

| D013          |                |                                                                  |                       | 13.5                                   | 30         | mA       | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V,<br>WDT disabled                                   |  |

|               |                | Module Differential Current (5)                                  | $\setminus$           | $\sim$                                 |            |          |                                                                                                      |  |

| D015          | ΔIBOR          | Brown-out Reset Current                                          |                       | 350                                    | 425        | μA       | BODEN bit is clear, VDD = 5.0V                                                                       |  |

| D016          |                | Comparator Current for each Comparator                           | $\left \right\rangle$ | _                                      | 100        | μA       | VDD = 4.0V                                                                                           |  |

| D017          | $\Delta$ IVREF | VREF Current                                                     | K -                   | _                                      | 300        | μA       | VDD = 4.0V                                                                                           |  |

| D021          | ΔIWDT          | WDT Current                                                      | -                     | 6.0<br>—                               | 20<br>25   | μΑ<br>μΑ | VDD = 4.0V<br>Automotive                                                                             |  |

| D021          | IPD            | Power-down Current (3)                                           | -                     | 1.5<br>2.5                             | 21<br>24   | μΑ<br>μΑ | VDD = 4.0V, WDT disabled<br>Automotive                                                               |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1; This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated<sup>TM</sup>, pulled to VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kΩ.

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

NOTES:

## APPENDIX A: ENHANCEMENTS

The following are the list of enhancements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14 bits. This allows larger page sizes both in program memory (4K now as opposed to 512 before) and register file (up to 176 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- 3. Data memory paging is slightly redefined. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Six different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers can be invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. Timer0 clock input, T0CKI pin is also a port pin (RA4/T0CKI) and has a TRIS bit.

- 14. FSR is made a full 8-bit register.

- 15. "In-circuit programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR), a Brown-out Reset status bit (BOR), a Parity Error Reset (PER), and a Memory Parity Enable (MPEEN) bit.

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- 18. PORTA inputs are now Schmitt Trigger inputs.

- 19. Brown-out Reset circuitry has been added.

## APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

© 1996 Microchip Technology Inc.

## **APPENDIX E: PIC16/17 MICROCONTROLLERS**

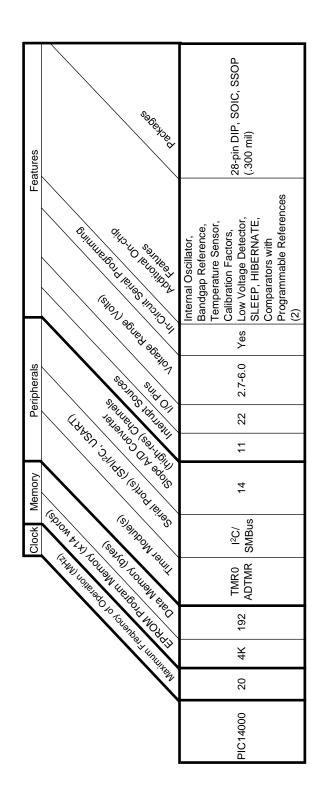

## E.1 PIC14000 Devices

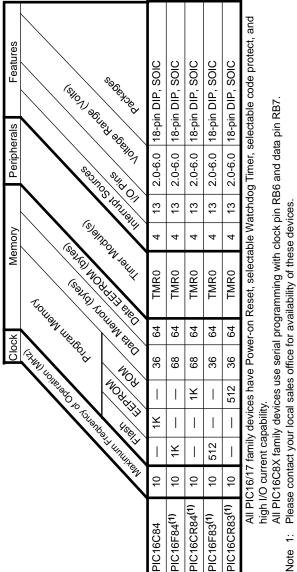

#### E.6 **PIC16C8X Family of Devices**

÷ Note NOTES: