Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c642-20-sp |

#### 4.0 MEMORY ORGANIZATION

#### 4.1 **Program Memory Organization**

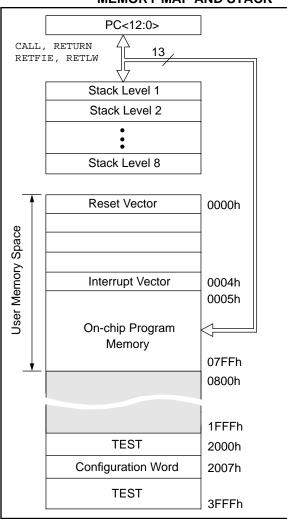

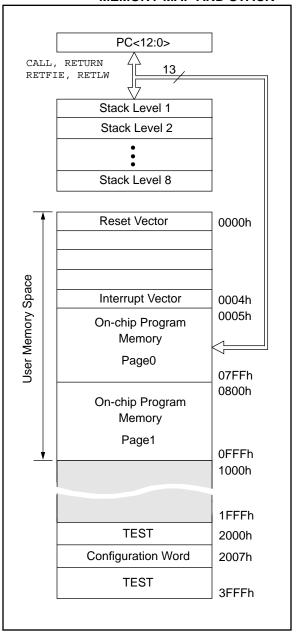

The PIC16C64X & PIC16C66X have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16C641 and PIC16C661 only the first 2K x 14 (0000h - 07FFh) is physically implemented. For the PIC16C642 and PIC16C662 only the first 4K x 14 (0000h - 0FFh) is physically implemented. Accessing a location above the 2K or 4K boundary will cause a wrap-around. The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1 and Figure 4-2). See Section 4.4 for Program Memory paging.

FIGURE 4-1: PIC16C641/661 PROGRAM MEMORY MAP AND STACK

FIGURE 4-2: PIC16C642/662 PROGRAM MEMORY MAP AND STACK

#### 4.2 **Data Memory Organization**

The data memory (Figure 4-4) is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected when bit RP0 (STATUS<5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations A0h-EFh (Bank 1) are general purpose registers implemented as static RAM. Some special function registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 176 x 8 for the PIC16C642/662, and 128 x8 for the PIC16C641/661. Each is accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

FIGURE 4-3: PIC16C641/661 DATA **MEMORY MAP**

| MEMORY MAP       |                                         |                      |                 |  |  |  |  |  |  |

|------------------|-----------------------------------------|----------------------|-----------------|--|--|--|--|--|--|

| File<br>Address  | <b>S</b>                                |                      | File<br>Address |  |  |  |  |  |  |

| 00h              | INDF <sup>(1)</sup>                     | INDF <sup>(1)</sup>  | 80h             |  |  |  |  |  |  |

| 01h              | TMR0                                    | OPTION               | 81h             |  |  |  |  |  |  |

| 02h              | PCL                                     | PCL                  | 82h             |  |  |  |  |  |  |

| 03h              | STATUS                                  | STATUS               | 83h             |  |  |  |  |  |  |

| 04h              | FSR                                     | FSR                  | 84h             |  |  |  |  |  |  |

| 05h              | PORTA                                   | TRISA                | 85h             |  |  |  |  |  |  |

| 06h              | PORTB                                   | TRISB                | 86h             |  |  |  |  |  |  |

| 07h              | PORTC                                   | TRISC                | 87h             |  |  |  |  |  |  |

| 08h              | PORTD <sup>(2)</sup>                    | TRISD <sup>(2)</sup> | 88h             |  |  |  |  |  |  |

| 09h              | PORTE <sup>(2)</sup>                    | TRISE <sup>(2)</sup> | 89h             |  |  |  |  |  |  |

| 0Ah              | PCLATH                                  | PCLATH               | - 8Ah           |  |  |  |  |  |  |

| 0Bh              | INTCON                                  | INTCON               | -<br>8Bh        |  |  |  |  |  |  |

| 0Ch              | PIR1                                    | PIE1                 | 8Ch             |  |  |  |  |  |  |

| 0Dh              |                                         |                      | 8Dh             |  |  |  |  |  |  |

| 0Eh              |                                         | PCON                 | 8Eh             |  |  |  |  |  |  |

| 0Fh              |                                         |                      | 8Fh             |  |  |  |  |  |  |

| 10h              |                                         |                      | 90h             |  |  |  |  |  |  |

| 11h              |                                         |                      | 91h             |  |  |  |  |  |  |

| 12h              |                                         |                      | 92h             |  |  |  |  |  |  |

| 13h              |                                         |                      | 93h             |  |  |  |  |  |  |

| 14h              |                                         |                      | 94h             |  |  |  |  |  |  |

| 15h              |                                         |                      | 95h             |  |  |  |  |  |  |

| 16h              |                                         |                      | 96h             |  |  |  |  |  |  |

| 17h              |                                         |                      | 97h             |  |  |  |  |  |  |

| 18h              |                                         |                      | 98h             |  |  |  |  |  |  |

| 19h              |                                         |                      | 99h             |  |  |  |  |  |  |

| 1Ah              |                                         |                      | 9Ah             |  |  |  |  |  |  |

| 1Bh              |                                         |                      | 9Bh             |  |  |  |  |  |  |

| 1Ch              |                                         |                      | 9Ch             |  |  |  |  |  |  |

| 1Dh              |                                         |                      | 9Dh             |  |  |  |  |  |  |

| 1Eh              |                                         |                      | 9Eh             |  |  |  |  |  |  |

| 1Fh              | CMCON                                   | VRCON                | 9Fh             |  |  |  |  |  |  |

| 20h              | General                                 | General              | A0h             |  |  |  |  |  |  |

|                  | Purpose                                 | Purpose              |                 |  |  |  |  |  |  |

|                  | Register                                | Register             | BFh             |  |  |  |  |  |  |

|                  |                                         |                      | COh             |  |  |  |  |  |  |

|                  |                                         |                      |                 |  |  |  |  |  |  |

|                  |                                         |                      | EFh             |  |  |  |  |  |  |

|                  |                                         | Mapped               | F0h             |  |  |  |  |  |  |

| 756              |                                         | in Page 0            | _<br>□ FFh      |  |  |  |  |  |  |

| 7Fh <sup>l</sup> | Bank 0                                  | Bank 1               | <b>→</b> FFII   |  |  |  |  |  |  |

|                  | lemented data mer<br>lot a physical reg |                      | ad as '0'.      |  |  |  |  |  |  |

|                  | lot a physical reg                      |                      | 641.            |  |  |  |  |  |  |

|                  |                                         |                      |                 |  |  |  |  |  |  |

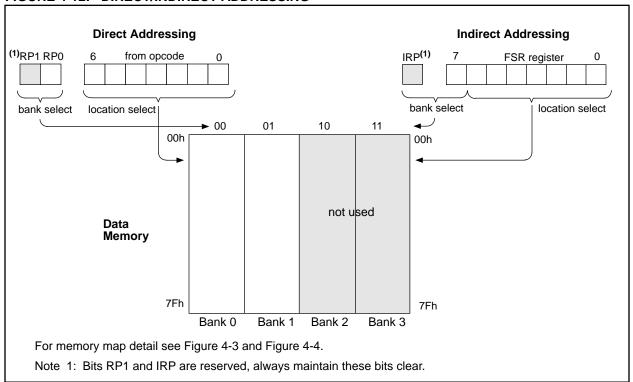

## 4.5 <u>Indirect Addressing, INDF, and FSR</u> Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a nooperation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-12. However, bit IRP is not used in the PIC16C64X & PIC16C66X.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

#### **EXAMPLE 4-1: INDIRECT ADDRESSING**

movlw 0x20 ;initialize pointer

movwf FSR ;to RAM

NEXT clrf INDF ;clear INDF register

incf FSR ;inc pointer

btfss FSR,4 ;all done?

goto NEXT ;no goto next

;yes continue

CONTINUE:

#### FIGURE 4-12: DIRECT/INDIRECT ADDRESSING

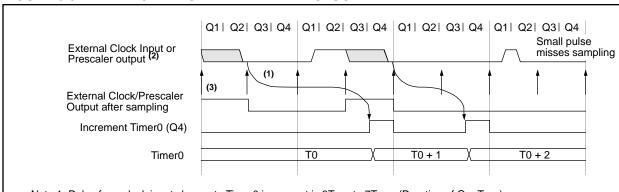

#### 6.2 <u>Using Timer0 with External Clock</u>

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41, and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMERO TIMING WITH EXTERNAL CLOCK

- Note 1: Delay from clock input change to Timer0 increment is 3Tosc to 7Tosc. (Duration of Q = Tosc). Therefore, the error in measuring the interval between two edges on Timer0 input =  $\pm$ 4Tosc max.

- 2: External clock if no prescaler selected, prescaler output otherwise.

- 3: The arrows indicate the points in time where sampling occurs.

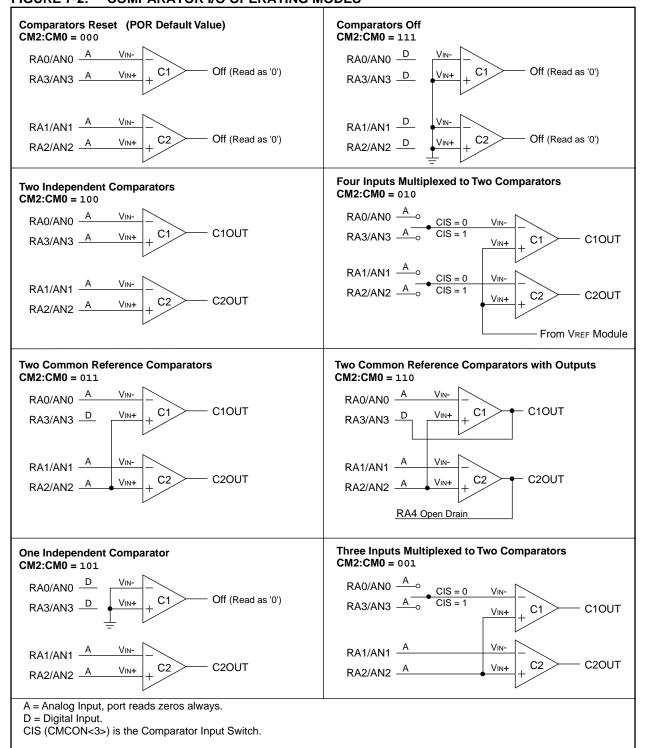

#### 7.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 7-2 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 12-2.

**Note:** Comparator interrupts should be disabled during a comparator mode change otherwise a false interrupt may occur.

### FIGURE 7-2: COMPARATOR I/O OPERATING MODES

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. User software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit (PIR1<6>), is the comparator interrupt flag and must be cleared in user software.

To enable the Comparator interrupt the following bits must be set:

- CMIE (PIE1<6>)

- PEIE (INTCON<6>)

- GIE (INTCON<7>)

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

#### 7.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake up the device from SLEEP mode when enabled. While the comparator is powered up, higher sleep currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the

comparators, CM2:CM0 = 111, before entering sleep. If the device wakes up from sleep, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered down during the reset interval.

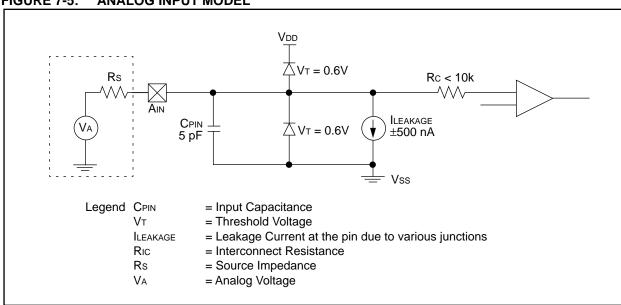

#### 7.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 7-5. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 kΩ recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 7-5: ANALOG INPUT MODEL

**TABLE 10-2: INSTRUCTION SET**

| Mnemonic, |         | Description                  | Cycles |     | 14-Bit | Opcode | )    | Status   | Notes |

|-----------|---------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands  |         |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE | NTED    | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF     | f, d    | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d    | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF      | f       | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW      | -       | Clear W                      | 1      | 00  | 0001   | 0000   | 0011 | Z        |       |

| COMF      | f, d    | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF      | f, d    | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ    | f, d    | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF      | f, d    | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ    | f, d    | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF     | f, d    | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF      | f, d    | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF     | f       | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP       | -       | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF       | f, d    | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF       | f, d    | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF     | f, d    | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d    | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF     | f, d    | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIEN | ΓED FIL | E REGISTER OPERATIONS        |        | •   |        |        |      |          |       |

| BCF       | f, b    | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF       | f, b    | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC     | f, b    | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS     | f, b    | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL A | ND CO   | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW     | k       | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW     | k       | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL      | k       | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT    | -       | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO      | k       | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW     | k       | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW     | k       | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE    | -       | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW     | k       | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN    | -       | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP     | -       | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW     | k       | Subtract W from literal      | 1      | 11  | 110x   | kkkk   |      | C,DC,Z   |       |

| XORLW     | k       | Exclusive OR literal with W  | 1      | 11  | 1010   | kkkk   | kkkk | Z        |       |

|           |         |                              |        | l . |        |        |      |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

<sup>3:</sup> If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                |                                             |                      |      |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|------|--|--|--|--|

| Syntax:          | [ label ] B                                                                                                                                                                                                                                            | TFSS f,b                                    | )                    |      |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                                                     |                                             |                      |      |  |  |  |  |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                                                                                                                |                                             |                      |      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                   |                                             |                      |      |  |  |  |  |

| Encoding:        | 01                                                                                                                                                                                                                                                     | 11bb                                        | bfff                 | ffff |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the next instruction is skipped.  If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a 2 cycle instruction. |                                             |                      |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                      |                                             |                      |      |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                   |                                             |                      |      |  |  |  |  |

| Example          | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                  |                                             | - *                  |      |  |  |  |  |

|                  | Before Ins                                                                                                                                                                                                                                             |                                             |                      |      |  |  |  |  |

|                  | After Instr<br>i<br>F<br>i                                                                                                                                                                                                                             | ruction<br>f FLAG<1><br>PC = 4<br>f FLAG<1> | • = 0,<br>address F. |      |  |  |  |  |

| CLRF             | Clear f                                                               |         |        |        |         |  |

|------------------|-----------------------------------------------------------------------|---------|--------|--------|---------|--|

| Syntax:          | [ label ](                                                            | CLRF f  |        |        |         |  |

| Operands:        | $0 \le f \le 12$                                                      | 27      |        |        |         |  |

| Operation:       | $\begin{array}{c} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ | )       |        |        |         |  |

| Status Affected: | Z                                                                     |         |        |        |         |  |

| Encoding:        | 00                                                                    | 0001    | 1fi    | ££     | ffff    |  |

| Description:     | The conte                                                             | •       | ster ' | f' are | cleared |  |

| Words:           | 1                                                                     |         |        |        |         |  |

| Cycles:          | 1                                                                     |         |        |        |         |  |

| Example          | CLRF                                                                  | FLAG    | E_RE   | G      |         |  |

|                  | Before Instruction  FLAG_REG = 0x5  After Instruction                 |         |        |        |         |  |

|                  |                                                                       | FLAG_RE | ĒĠ     | =      | 0x00    |  |

|                  |                                                                       | Z       |        | =      | 1       |  |

|                  |                                                                       |         |        |        |         |  |

|                  |                                                                       |         |        |        |         |  |

|                  |                                                                       |         |        |        |         |  |

|                  |                                                                       |         |        |        |         |  |

|                  |                                                                       |         |        |        |         |  |

| CALL             | Call Subroutine                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] CALL k                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Operation:       | $ \begin{array}{l} (PC)+\ 1\rightarrow TOS, \\ k\rightarrow PC<10:0>, \\ (PCLATH<4:3>)\rightarrow PC<12:11> \end{array} $                                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:     | Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two cycle instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | Before Instruction PC = Address HERE After Instruction PC = Address THERE TOS = Address HERE+1                                                                                                                            |  |  |  |  |  |  |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Encoding:        | 00 0001 0000 0011                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| Words:           | 1                                                                     |

| Cycles:          | 1                                                                     |

| Example          | CLRW                                                                  |

|                  | Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ $Z = 1$    |

TABLE 11-1: DEVELOPMENT TOOLS FROM MICROCHIP

| PICSTART® Plus<br>Low-Cost<br>Universal<br>Dev. Kit       | DV003001              | DV003001              | DV003001                              | DV003001              | DV003001              | DV003001                  | DV003001              | DV003001                               | DV003001                  | DV003001              | DV003001              | DV003001              | DV003001              | DV003001              | DV003001              | DV003001              | DV003001                 | clude                                                                                                                                                                                                                      | rity Eval/Demo Kit                   |                                          |           |

|-----------------------------------------------------------|-----------------------|-----------------------|---------------------------------------|-----------------------|-----------------------|---------------------------|-----------------------|----------------------------------------|---------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------|-----------|

| PICSTART® Lite<br>Ultra Low-Cost<br>Dev. Kit              | I                     | I                     | DV162003                              | I                     | DV162003              | DV162002                  | DV162003              | DV162002                               | DV162002                  | DV162003              | DV162003              | DV162002              | DV162003              | DV162003              | DV162003              | I                     | 1                        | ***All PICMASTER and PICMASTER-CE ordering part numbers above include PRO MATE II programmer ****PRO MATE socket modules are ordered separately. See development systems ordering guide for specific ordering part numbers | Hopping Code Security Eval/Demo Kit  | N/A                                      | V/N       |

| ****PRO MATETM<br>II Universal<br>Microchip<br>Programmer | DV007003              | DV007003              | DV007003                              | DV007003              | DV007003              | DV007003                  | DV007003              | DV007003                               | DV007003                  | DV007003              | DV007003              | DV007003              | DV007003              | DV007003              | DV007003              | DV007003              | DV007003                 | II PICMASTER and PICMASTER-CE ordering pa<br>PRO MATE II programmer<br>RO MATE socket modules are ordered separately<br>ordering guide for specific ordering part numbers                                                  |                                      |                                          |           |

| ICEPIC<br>Low-Cost<br>In-Circuit<br>Emulator              | I                     | I                     | EM167201                              | İ                     | EM167205              | EM167203                  | EM167202              | EM167204                               | i                         | EM167205              | I                     | I                     | I                     | EM167206              | I                     | I                     | I                        | and PICMAS<br>rogrammer<br>et modules ar<br>or specific orc                                                                                                                                                                | Security Prog                        | N/A                                      | N/A       |

| *** PICMASTER®/<br>PICMASTER-CE<br>In-Circuit<br>Emulator | EM167015/<br>EM167101 | EM147001/<br>EM147101 | EM167015/<br>EM167101                 | EM167033/<br>EM167113 | EM167021/<br>N/A      | EM167025/<br>EM167103     | EM167023/<br>EM167109 | EM167025/<br>EM167103                  | EM167035/<br>EM167105     | EM167027/<br>EM167105 | EM167027/<br>EM167105 | EM167025/<br>EM167103 | EM167029/<br>EM167107 | EM167029/<br>EM167107 | EM167029/<br>EM167107 | EM167031/<br>EM167111 | EM177007/<br>EM177107    | ***All PICMASTER and PICMA PRO MATE II programmer ***PRO MATE socket modules ordering guide for specific ordering guide.                                                                                                   | Hopping Code Security Programmer Kit |                                          |           |

| fuzzyTECH®-MP Texplorer/Edition Fuzzy Logic Dev. Tool     | I                     | 1                     | DV005001/<br>DV005002                 | DV005001/<br>DV005002 | DV005001/<br>DV005002 | DV005001/<br>DV005002     | DV005001/<br>DV005002 | DV005001/<br>DV005002                  | 1                         | DV005001/<br>DV005002 | DV005001/<br>DV005002 | I                     | DV005001/<br>DV005002 | DV005001/<br>DV005002 | DV005001/<br>DV005002 | DV005001/<br>DV005002 | DV005001/<br>DV005002    |                                                                                                                                                                                                                            | SEEVAL® Designers Kit                | DV243001                                 | δ/N       |

| MP-DriveWay<br>Applications<br>Code<br>Generator          | I                     | 1                     | SW006006                              | I                     | SW006006              | SW006006                  | SW006006              | SW006006                               | 1                         | SW006006                 | MPLAB-SIM Simulator and                                                                                                                                                                                                    | H                                    |                                          |           |

| MPLAB™ C N Compiler /                                     | SW006005              | SW006005              | SW006005                              | SW006005              | SW006005              | SW006005                  | SW006005              | SW006005                               | SW006005                  | SW006005              | SW006005              | SW006005              | SW006005              | SW006005              | SW006005              | SW006005              | SW006005                 |                                                                                                                                                                                                                            | TRUEGAUGE® Development Kit           | N/A                                      | DV114001  |

| ** MPLAB™ Integrated Development Environment              | SW007002              | SW007002              | SW007002                              | SW007002              | SW007002              | SW007002                  | SW007002              | SW007002                               | SW007002                  | SW007002              | SW007002              | SW007002              | SW007002              | SW007002              | SW007002              | SW007002              | SW007002                 | nnology for availa<br>elopment Enviror                                                                                                                                                                                     | TRUEGAUGE                            |                                          | ć         |

| Product                                                   | PIC12C508, 509        | PIC14000              | PIC16C52, 54, 54A,<br>55, 56, 57, 58A | PIC16C554, 556, 558   | PIC16C61              | PIC16C62, 62A,<br>64, 64A | PIC16C620, 621, 622   | PIC16C63, 65, 65A,<br>73, 73A, 74, 74A | PIC16C641, 642, 661, 662* | PIC16C71              | PIC16C710, 711        | PIC16C72              | PIC16F83              | PIC16C84              | PIC16F84              | PIC16C923, 924*       | PIC17C42,<br>42A, 43, 44 | *Contact Microchip Technology for availability date **MPLAB Integrated Development Environment includes MPASM Assembler                                                                                                    | Product                              | All 2 wire and 3 wire<br>Serial EEPROM's | MTA11200B |

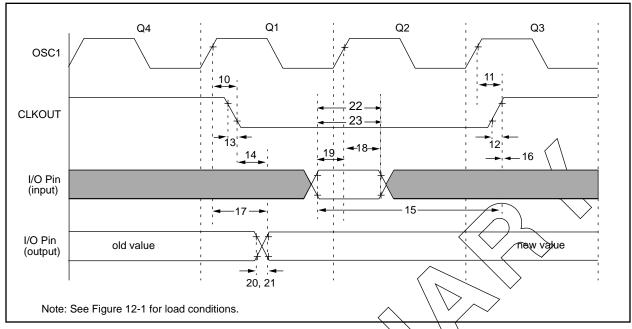

FIGURE 12-3: CLKOUT AND I/O TIMING

TABLE 12-5: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter | Sym      | Characteristic                        |                    | Min        | Typt | Max         | Units | Conditions |

|-----------|----------|---------------------------------------|--------------------|------------|------|-------------|-------|------------|

| No.       |          |                                       |                    |            |      |             |       |            |

| 10*       | TosH2ckL | OSC1↑ to CLKOUT↓                      |                    |            | 75   | 200         | ns    | Note 1     |

| 11*       | TosH2ckH | OSC1↑ to CLKOUT↑                      |                    | >-         | 75   | 200         | ns    | Note 1     |

| 12*       | TckR     | CLKOUT rise time                      |                    |            | 35   | 100         | ns    | Note 1     |

| 13*       | TckF     | CLKOUT fall time                      | / // // /          |            | 35   | 100         | ns    | Note 1     |

| 14*       | TckL2ioV | CLKOUT ↓ to Port out valid            |                    | _          | _    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*       | TioV2ckH | Port in valid before CLKOU            | TY                 | Tosc + 200 | _    | _           | ns    | Note 1     |

| 16*       | TckH2ioI | Port in hold after CLKOUT             | $\wedge$           | 0          | _    |             | ns    | Note 1     |

| 17*       | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid | $\nearrow$         | _          | 50   | 150         | ns    |            |

| 18*       | TosH2iol | OSC11 (Q2-cycle) to                   | PIC16C64X/66X      | 100        | _    |             | ns    |            |

|           |          | Port input invalid (I/O in hold time) | PIC16LC64X/66X     | 200        | _    | _           | ns    |            |

| 19*       | TioV2osH | Rort input valid to OSC1↑ (           | I/O in setup time) | 0          | _    | 1           | ns    |            |

| 20*       | TioR     | Port output rise time                 | PIC16C64X/66X      | _          | 10   | 40          | ns    |            |

|           |          | $\langle \rangle$                     | PIC16LC64X/66X     | _          | _    | 80          | ns    |            |

| 21*       | TioF     | Port output fall time                 | PIC16C64X/66X      | _          | 10   | 40          | ns    |            |

|           |          | $\triangleright$                      | PIC16LC64X/66X     | _          | _    | 80          | ns    |            |

| 22++      | Tirip    | INT pin high or low time              |                    | TCY        | _    | ı           | ns    |            |

| 23††*     | Trbp     | RB7:RB4 change INT high               | or low time        | Tcy        | _    | _           | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Datá in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

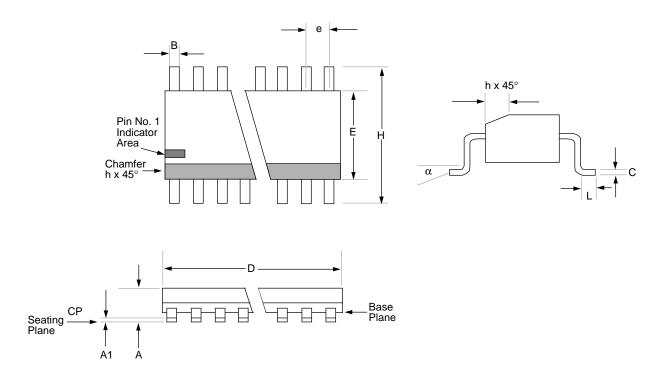

### Package Type: 28-Lead Plastic Small Outline (SO) - Wide, 300 mil Body

|        |        | Package (   | Group: Plastic | SOIC (SO) |        |       |

|--------|--------|-------------|----------------|-----------|--------|-------|

|        |        | Millimeters |                |           | Inches |       |

| Symbol | Min    | Max         | Notes          | Min       | Max    | Notes |

| α      | 0°     | 8°          |                | 0°        | 8°     |       |

| Α      | 2.362  | 2.642       |                | 0.093     | 0.104  |       |

| A1     | 0.101  | 0.300       |                | 0.004     | 0.012  |       |

| В      | 0.355  | 0.483       |                | 0.014     | 0.019  |       |

| С      | 0.241  | 0.318       |                | 0.009     | 0.013  |       |

| D      | 17.703 | 18.085      |                | 0.697     | 0.712  |       |

| Е      | 7.416  | 7.595       |                | 0.292     | 0.299  |       |

| е      | 1.270  | 1.270       | BSC            | 0.050     | 0.050  | BSC   |

| Н      | 10.007 | 10.643      |                | 0.394     | 0.419  |       |

| h      | 0.381  | 0.762       |                | 0.015     | 0.030  |       |

| L      | 0.406  | 1.143       |                | 0.016     | 0.045  |       |

| СР     | _      | 0.102       |                | _         | 0.004  |       |

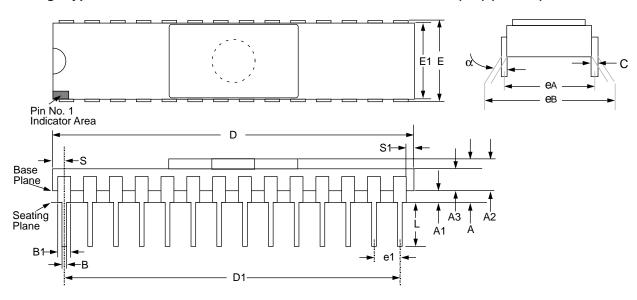

### Package Type: 28-Lead Ceramic Side Brazed Dual In-Line with Window (JW) (300 mil)

|        | Package Group: Ceramic Side Brazed Dual In-Line (CER) |             |         |        |       |       |  |  |  |  |

|--------|-------------------------------------------------------|-------------|---------|--------|-------|-------|--|--|--|--|

| Combal |                                                       | Millimeters |         | Inches |       |       |  |  |  |  |

| Symbol | Min                                                   | Max         | Notes   | Min    | Max   | Notes |  |  |  |  |

| α      | 0°                                                    | 10°         |         | 0°     | 10°   |       |  |  |  |  |

| А      | 3.937                                                 | 5.030       |         | 0.155  | 0.198 |       |  |  |  |  |

| A1     | 1.016                                                 | 1.524       |         | 0.040  | 0.060 |       |  |  |  |  |

| A2     | 2.921                                                 | 3.506       |         | 0.115  | 0.138 |       |  |  |  |  |

| A3     | 1.930                                                 | 2.388       |         | 0.076  | 0.094 |       |  |  |  |  |

| В      | 0.406                                                 | 0.508       |         | 0.016  | 0.020 |       |  |  |  |  |

| B1     | 1.219                                                 | 1.321       | Typical | 0.048  | 0.052 |       |  |  |  |  |

| С      | 0.228                                                 | 0.305       | Typical | 0.009  | 0.012 |       |  |  |  |  |

| D      | 35.204                                                | 35.916      |         | 1.386  | 1.414 |       |  |  |  |  |

| D1     | 32.893                                                | 33.147      | BSC     | 1.295  | 1.305 |       |  |  |  |  |

| Е      | 7.620                                                 | 8.128       |         | 0.300  | 0.320 |       |  |  |  |  |

| E1     | 7.366                                                 | 7.620       |         | 0.290  | 0.300 |       |  |  |  |  |

| e1     | 2.413                                                 | 2.667       | Typical | 0.095  | 0.105 |       |  |  |  |  |

| eA     | 7.366                                                 | 7.874       | BSC     | 0.290  | 0.310 |       |  |  |  |  |

| eВ     | 7.594                                                 | 8.179       |         | 0.299  | 0.322 |       |  |  |  |  |

| L      | 3.302                                                 | 4.064       |         | 0.130  | 0.160 |       |  |  |  |  |

| S      | 1.143                                                 | 1.397       |         | 0.045  | 0.055 |       |  |  |  |  |

| S1     | 0.533                                                 | 0.737       |         | 0.021  | 0.029 |       |  |  |  |  |

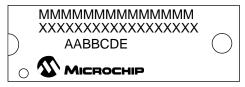

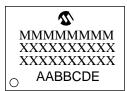

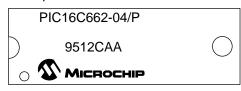

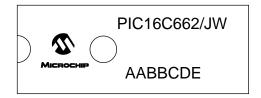

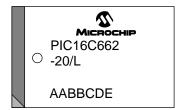

#### 14.2 Package Marking Information

40-Lead PDIP

40-Lead CERDIP Windowed

44-Lead PLCC

44-Lead TQFP

#### Example

Example

#### Example

#### Example

**Legend:** MM...MMicrochip part number information

XX...X Customer specific information\*

AA Year code (last 2 digits of calendar year)

BB Week code (week of January 1 is week '01')

C Facility code of the plant at which wafer is manufactured

C = Chandler, Arizona, U.S.A.

D Mask revision number

E Assembly code of the plant or country of origin in which

part was assembled

**Note**:In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

<sup>\*</sup>Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

| 1                                           |     | PORTB Change                              | 32 |

|---------------------------------------------|-----|-------------------------------------------|----|

| I/O Ports                                   | 20  | PSP Read-Write                            |    |

| PORTA                                       | _   | RB0/INT                                   | 66 |

| PORTB                                       | -   | Section                                   | 66 |

| PORTC                                       |     | Timer0                                    | 41 |

| PORTD                                       | _   | Timer0, Timing                            | 42 |

| PORTE                                       |     | IORLW Instruction                         | 80 |

| I/O Programming Considerations              |     | IORWF Instruction                         | 81 |

| ICEPIC In-Circuit Emulator                  |     | NA                                        |    |

| ID Locations                                |     | M                                         |    |

| INCF Instruction                            |     | MOVF Instruction                          | 81 |

| INCFSZ Instruction                          |     | MOVLW Instruction                         | 81 |

|                                             |     | MOVWF Instruction                         | 81 |

| In-Circuit Serial Programming               |     | MPASM Assembler 87,                       | 88 |

| Indirect Addressing, INDF and FSR Registers |     | MPLAB-C C Compiler                        | 89 |

| Instruction Flow/Pipelining                 |     | MPLAB-SIM Software Simulator87,           | 89 |

| Instruction Format Instruction Set          | / 3 | N                                         |    |

|                                             | 70  |                                           |    |

| ADDLW                                       |     | NOP Instruction                           | 82 |

| ADDWF                                       | _   | 0                                         |    |

| ANDLW                                       | -   |                                           |    |

| ANDWF                                       |     | One-Time-Programmable (OTP) Devices       |    |

| BCF                                         |     | Opcode                                    |    |

| BSF                                         |     | OPTION Instruction                        |    |

| BTFSC                                       |     | OPTION Register                           |    |

| BTFSS                                       |     | Oscillator Configurations                 |    |

| CALL                                        | -   | Oscillator Start-up Timer (OST)           | 60 |

| CLRF                                        |     | Р                                         |    |

| CLRW                                        | _   | •                                         |    |

| CLRWDT                                      | _   | Package Marking Information112, 1         |    |

| COMF                                        |     | Packaging Information1                    |    |

| DECF                                        |     | Parallel Slave Port                       |    |

| DECFSZ                                      | -   | Section                                   |    |

| GOTO                                        |     | Parity Error Reset (PER)60,               |    |

| INCF                                        |     | PCL                                       |    |

| INCFSZ                                      | 80  | PCL and PCLATH                            |    |

| IORLW                                       |     | PCON Register26,                          |    |

| IORWF                                       | 81  | PICDEM-1 Low-Cost PIC16/17 Demo Board 87, |    |

| MOVF                                        | 81  | PICDEM-2 Low-Cost PIC16CXX Demo Board 87, |    |

| MOVLW                                       | 81  | PICDEM-3 Low-Cost PIC16C9XX Demo Board    | 88 |

| MOVWF                                       | 81  | PICDEM-3 PIC16C9XX Low-Cost Demonstration |    |

| NOP                                         | 82  | Board                                     | 87 |

| OPTION                                      | 82  | PICMASTER® High Performance               |    |

| RETFIE                                      | 82  | In-Circuit Emulator                       | 87 |

| RETLW                                       | 82  | PICSTART® Plus Entry Level Development    |    |

| RETURN                                      | 83  | System                                    | 87 |

| RLF                                         | 83  | PICSTART® Plus Entrvel Prototype          |    |

| RRF                                         | 83  | Programmer                                | 87 |

| SLEEP                                       | 83  | PIE1 Register                             | 24 |

| SUBLW                                       | 84  | Pin Compatible Devices1                   |    |

| SUBWF                                       |     | Pin Functions                             |    |

| SWAPF                                       |     | RD7/PSP7:RD0/PSP0                         | 14 |

| TRIS                                        |     | RE0/RD14,                                 |    |

| XORLW                                       |     | RE1/WR14,                                 |    |

| XORWF                                       |     | RE2/ <del>CS</del> 14,                    |    |

| Section                                     |     | PIR1 Register                             |    |

| Summary Table                               |     | Port RB Interrupt                         |    |

| INT Interrupt                               |     | PORTA                                     |    |

| INTCON Register                             |     | PORTB                                     |    |

| Interrupts                                  |     | PORTC Register                            |    |

| Comparator                                  |     | PORTD Register                            |    |

|                                             |     |                                           | -  |

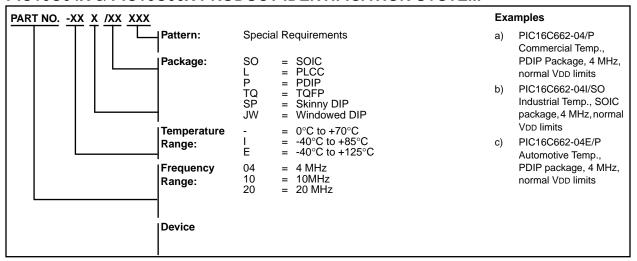

#### PIC16C64X & PIC16C66X PRODUCT IDENTIFICATION SYSTEM

Please contact your local sales office for exact ordering procedures.

JW devices are UV erasable and can be programmed to any device configuration. JW devices meet the electrical requirements of each oscillator type (including LC devices).

#### Sales and Support

Products supported by a preliminary Data Sheet may possibly have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office (see below)

- 2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277

- 3. The Microchip's Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

For latest version information and upgrade kits for Microchip Development Tools, please call 1-800-755-2345 or 1-602-786-7302.

#### Note the following details of the code protection feature on PICmicro® MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELO® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.