#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc642-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C64X & PIC16C66X devices can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C64X & PIC16C66X use a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than an 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches, which require two cycles.

The PIC16C641 and PIC16C661 both address  $2K \times 14$  on-chip program memory while the PIC16C642 and PIC16C662 address  $4K \times 14$ . All program memory is internal.

PIC16C64X & PIC16C66X devices can directly or indirectly address their register files or data memory. All special function registers including the program counter are mapped in the data memory. These devices have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C64X & PIC16C66X simple yet efficient. In addition, the learning curve is reduced significantly. PIC16C64X & PIC16C66X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

## 4.2 Data Memory Organization

The data memory (Figure 4-4) is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected when bit RP0 (STATUS<5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations A0h-EFh (Bank 1) are general purpose registers implemented as static RAM. Some special function registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $176 \times 8$  for the PIC16C642/662, and 128 x8 for the PIC16C641/661. Each is accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

#### FIGURE 4-3: PIC16C641/661 DATA MEMORY MAP

| MEMORY MAP                                                                                                                    |                      |                      |                 |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-----------------|--|--|--|--|--|--|

| File<br>Address                                                                                                               | 5                    |                      | File<br>Address |  |  |  |  |  |  |

| 00h                                                                                                                           | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup>  | 80h             |  |  |  |  |  |  |

| 01h                                                                                                                           | TMR0                 | OPTION               | 81h             |  |  |  |  |  |  |

| 02h                                                                                                                           | PCL                  | PCL                  |                 |  |  |  |  |  |  |

| 03h                                                                                                                           | STATUS               | STATUS               |                 |  |  |  |  |  |  |

| 04h                                                                                                                           | FSR                  | FSR                  |                 |  |  |  |  |  |  |

| 05h                                                                                                                           | PORTA                | TRISA                | 85h             |  |  |  |  |  |  |

| 06h                                                                                                                           | PORTB                | TRISB                | 86h             |  |  |  |  |  |  |

| 07h                                                                                                                           | PORTC                | TRISC                | 87h             |  |  |  |  |  |  |

| 08h                                                                                                                           | PORTD <sup>(2)</sup> | TRISD <sup>(2)</sup> | 88h             |  |  |  |  |  |  |

| 09h                                                                                                                           | PORTE <sup>(2)</sup> | TRISE <sup>(2)</sup> | 89h             |  |  |  |  |  |  |

| 0Ah                                                                                                                           | PCLATH               | PCLATH               | 8Ah             |  |  |  |  |  |  |

| 0Bh                                                                                                                           | INTCON               | INTCON               | 8Bh             |  |  |  |  |  |  |

| 0Ch                                                                                                                           | PIR1                 | PIE1                 | 8Ch             |  |  |  |  |  |  |

| 0Dh                                                                                                                           |                      |                      | 8Dh             |  |  |  |  |  |  |

| 0Eh                                                                                                                           |                      | PCON                 | 8Eh             |  |  |  |  |  |  |

| 0Fh                                                                                                                           |                      |                      | 8Fh             |  |  |  |  |  |  |

| 10h                                                                                                                           |                      |                      | 90h             |  |  |  |  |  |  |

| 11h                                                                                                                           |                      |                      | 91h             |  |  |  |  |  |  |

| 12h                                                                                                                           |                      |                      | 92h             |  |  |  |  |  |  |

| 13h                                                                                                                           |                      |                      | 93h             |  |  |  |  |  |  |

| 14h                                                                                                                           |                      |                      | 94h             |  |  |  |  |  |  |

| 15h                                                                                                                           |                      |                      | 95h             |  |  |  |  |  |  |

| 16h                                                                                                                           |                      |                      | 96h             |  |  |  |  |  |  |

| 17h                                                                                                                           |                      |                      | 97h             |  |  |  |  |  |  |

| 18h                                                                                                                           |                      |                      | 98h             |  |  |  |  |  |  |

| 19h                                                                                                                           |                      |                      | 99h             |  |  |  |  |  |  |

| 1Ah<br>1Ph                                                                                                                    |                      |                      | 9Ah<br>9Bh      |  |  |  |  |  |  |

| 1Bh<br>1Ch                                                                                                                    |                      |                      | 960<br>9Ch      |  |  |  |  |  |  |

| 1Dh                                                                                                                           |                      |                      | 90h             |  |  |  |  |  |  |

| 1Eh                                                                                                                           |                      |                      | 9Eh             |  |  |  |  |  |  |

| 1Fh                                                                                                                           | CMCON                | VRCON                | 9Eh             |  |  |  |  |  |  |

| 20h                                                                                                                           | CIVICOIN             | VICON                |                 |  |  |  |  |  |  |

| 2011                                                                                                                          | General<br>Purpose   | General<br>Purpose   | A0h             |  |  |  |  |  |  |

|                                                                                                                               | Register             | Register             | BFh             |  |  |  |  |  |  |

|                                                                                                                               |                      |                      | C0h             |  |  |  |  |  |  |

|                                                                                                                               |                      |                      | EFh             |  |  |  |  |  |  |

|                                                                                                                               |                      | Mapped               | F0h             |  |  |  |  |  |  |

|                                                                                                                               |                      | in Page 0            |                 |  |  |  |  |  |  |

| 7Fh <sup>l</sup>                                                                                                              | Bank 0               | Bank 1               | _ FFh           |  |  |  |  |  |  |

| Unimplemented data memory locations, read as '0'.<br>Note 1: Not a physical register.<br>2: Not implemented on the PIC16C641. |                      |                      |                 |  |  |  |  |  |  |

|                                                                                                                               |                      |                      |                 |  |  |  |  |  |  |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all non-peripheral interrupt sources.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

## FIGURE 4-7: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| GIE    | PEIE                                                                                                                                                                                               | TOIE                                        | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0     | R/W-x<br>RBIF | R= Readable bit                                                                    |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|---------------|---------------|-----------|---------------|------------------------------------------------------------------------------------|--|--|

| bit7   |                                                                                                                                                                                                    |                                             |               |               |               |           | bitO          | W= Writable bit<br>U= Unimplemented bit,<br>read as '0'<br>- n= Value at POR reset |  |  |

| bit 7: | GIE: Global Interrupt Enable bit<br>1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                                            |                                             |               |               |               |           |               |                                                                                    |  |  |

| bit 6: | 1 = Enabl                                                                                                                                                                                          | ripheral Int<br>les all un-r<br>les all per | nasked pe     | eripheral ir  | nterrupts     |           |               |                                                                                    |  |  |

| bit 5: | 1 = Enabl                                                                                                                                                                                          | R0 Overflo<br>les the TM<br>les the TM      | R0 interru    | ıpt           | bit           |           |               |                                                                                    |  |  |

| bit 4: | 1 = Enabl                                                                                                                                                                                          | 0/INT Exte<br>les the RB<br>les the RE      | 0/INT exte    | ernal interi  | rupt          |           |               |                                                                                    |  |  |

| bit 3: | 1 = Enabl                                                                                                                                                                                          | Port Cha<br>les the RB<br>les the RE        | port char     | ige interru   | pt            |           |               |                                                                                    |  |  |

| bit 2: | 1 = TMRC                                                                                                                                                                                           | R0 Overflo<br>) register o<br>) register o  | verflowed     | l (must be    | cleared in    | software) |               |                                                                                    |  |  |

| bit 1: | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                         |                                             |               |               |               |           |               |                                                                                    |  |  |

| bit 0: | <b>RBIF</b> : RB Port Change Interrupt Flag bit<br>1 = When at least one of the RB7:RB4 pins changed state (See Section 5.2 to clear interrupt)<br>0 = None of the RB7:RB4 pins have changed state |                                             |               |               |               |           |               |                                                                                    |  |  |

# **PIC16C64X & PIC16C66X**

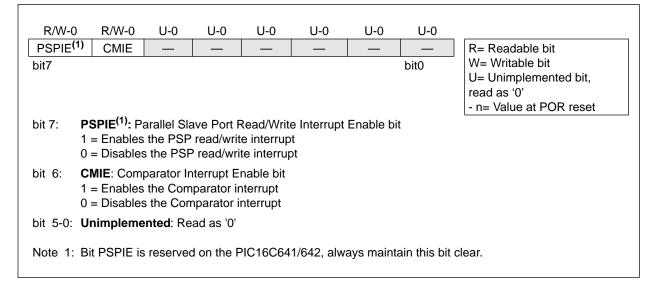

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the comparator and Parallel Slave Port interrupts.

## FIGURE 4-8: PIE1 REGISTER (ADDRESS 8Ch)

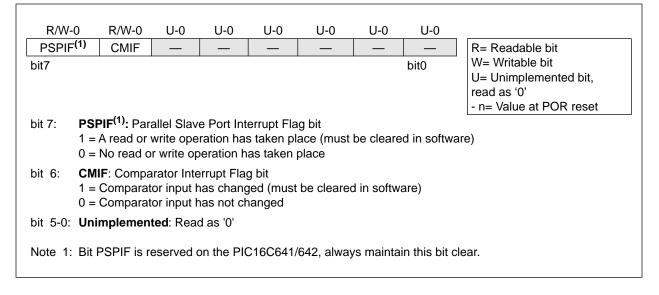

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the comparator and Parallel Slave Port interrupts.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 4-9: PIR1 REGISTER (ADDRESS 0Ch)

#### EXAMPLE 5-2: INITIALIZING PORTB

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|-------|-------------|---|-----------------------|

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPO | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

## TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data pin.  |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

## TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx                | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111                | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, shaded cells are not used by PORTB.

### 5.5 <u>PORTE and TRISE Register</u> (PIC16C661 and PIC16C662 only)

PORTE has three pins RE0/ $\overline{RD}$ , RE1/ $\overline{WR}$ , and RE2/ $\overline{CS}$ , which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). In this mode the input buffers are TTL.

FIGURE 5-9: TRISE REGISTER (ADDRESS 89h)

Г

| R-0         | R-0 R/W-0 R/W-0 U-0 R/W-1 R/W-1 R/W-1                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| IBF<br>bit7 | OBF       IBOV       PSPMODE       TRISE2       TRISE1       TRISE0       R       = Readable bit         bit0       W       = Writable bit       U       = Unimplemented bit, read as '0'       - n       = Value at POR reset |  |  |  |  |  |  |  |  |

| bit 7:      |                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| bit 6:      | <b>OBF</b> : Output Buffer Full Status bit<br>1 = The output buffer still holds a previously written word<br>0 = The output buffer has been read                                                                               |  |  |  |  |  |  |  |  |

| bit 5:      | <b>IBOV</b> : Input Buffer Overflow Detect bit (in microprocessor mode)<br>1 = A write occurred when a previously input word has not been read (must be cleared in software)<br>0 = No overflow occurred                       |  |  |  |  |  |  |  |  |

| bit 4:      | <b>PSPMODE</b> : Parallel Slave Port Mode Select bit<br>1 = Parallel slave port mode<br>0 = General purpose I/O mode                                                                                                           |  |  |  |  |  |  |  |  |

| bit 3:      | Unimplemented: Read as '0'                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| bit 2:      | TRISE2: Direction control bit for pin RE2/CS<br>1 = Input<br>0 = Output                                                                                                                                                        |  |  |  |  |  |  |  |  |

| bit 1:      | <b>TRISE1</b> : Direction control bit for pin RE1/WR<br>1 = Input<br>0 = Output                                                                                                                                                |  |  |  |  |  |  |  |  |

| bit 0:      | <b>TRISE0</b> : Direction control bit for pin RE0/RD<br>1 = Input<br>0 = Output                                                                                                                                                |  |  |  |  |  |  |  |  |

Figure 5-9 shows the TRISE register, which also controls the parallel slave port operation.

| Address | Name   | Bit 7                | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|----------------------|-------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT                | C1OUT | _      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                 | 00 0000                         |

| 9Fh     | VRCON  | VREN                 | VROE  | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000               | 000- 0000                       |

| 0Bh/8Bh | INTCON | GIE                  | PEIE  | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | CMIF  | —      | —      |        |        | _      | _      | 00                      | 00                              |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | CMIE  | _      |        | —      | _      | _      | _      | 00                      | 00                              |

| 85h     | TRISA  | _                    | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

Note 1: These bits are reserved on the PIC16C641/642, always maintain these bits clear.

#### 8.1 <u>Configuring the Voltage Reference</u>

The Voltage Reference Module can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

If VRR = 1 Then VREF = (VR3:VR0/24) • VDD If VRR = 0 Then VREF = (VDD • 1/4) + (VR3:VR0/32) • VDD

The settling time of the Voltage Reference must be considered when changing the VREF output (Table 12-2). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

#### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02             | ; | 4 inputs muxed     |

|-------|------------------|---|--------------------|

| MOVWF | CMCON            | ; | to 2 comparators   |

| BSF   | STATUS, RPO      | ; | Select Bank 1      |

| MOVLW | 0x07             | ; | RA3:RA0 to outputs |

| MOVWF | TRISA            | ; |                    |

| MOVLW | 0xA6             | ; | enable Vref low    |

| MOVWF | VRCON            | ; | range, VR3:VR0 = 6 |

| BCF   | STATUS, RPO      | ; | Select Bank 0      |

| CALL  | DELAY_10 $\mu s$ |   | ; 10 µs delay      |

#### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-2) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 12-3.

## 8.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference Module should be disabled.

### 8.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

## 8.5 <u>Connection Considerations</u>

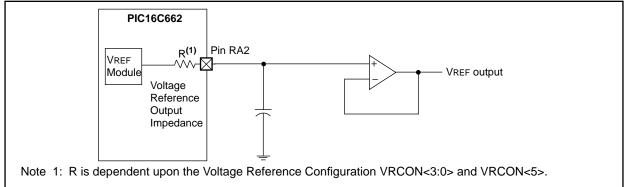

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and bit VROE is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 8-3 shows an example buffering technique.

## FIGURE 8-3: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

## TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|-------|-------|-------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000               | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | -      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                 | 00 0000                         |

| 85h     | TRISA |       |       | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

# 9.0 SPECIAL FEATURES OF THE CPU

What sets apart a microcontroller from other processors are special circuits to deal with the needs of real-time applications. The PIC16C64X & PIC16C66X families have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. Oscillator selection

- 2. Resets

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR) Parity Error Reset (PER)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16C64X & PIC16C66X has a Watchdog Timer which is enabled by a configuration bit (WDTE). It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. Circuitry has been provided for checking program memory parity with a reset when an error is indicated. There is also circuitry to reset the device if a brown-out occurs which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 9.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt e.g. W register and STATUS register. This will have to be implemented in software.

Example 9-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x70 - 0x7F in Bank 0). The user register, STATUS\_TEMP, must be defined in Bank 0.

Example 9-1:

- Stores the W register regardless of current bank

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit

register)

- register)Restores the W register

# EXAMPLE 9-1: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP          | ;  | Copy W to a Temporary Register regardless of current bank             |

|-------|-----------------|----|-----------------------------------------------------------------------|

| SWAPF | STATUS,W        | ;  | Swap STATUS nibbles and place into W register                         |

| BCF   | STATUS, RPO     | ;  | Change to Bank 0 regardless of current bank                           |

| MOVWF | STATUS_TEMP     | ;  | Save STATUS to a Temporary register in Bank 0                         |

| :     |                 |    |                                                                       |

| :     | Interrupt Servi | ce | Routine)                                                              |

| :     |                 |    |                                                                       |

| SWAPF | STATUS_TEMP,W   | ;  | Swap original STATUS register value into W (restores original bank)   |

| MOVWF | STATUS          | ;  | Restore STATUS register from W register                               |

| SWAPF | W_TEMP,F        | ;  | Swap W_Temp nibbles and return value to W_Temp                        |

| SWAPF | W_TEMP,W        | ;  | Swap W_Temp to W to restore original W value without affecting STATUS |

#### 9.9 <u>Code Protection</u>

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |

|-------|------------------------------|------|-----|-----------|------|

|       | protecting windowed devices. |      |     |           |      |

#### 9.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the least significant 4 bits of the ID locations are used.

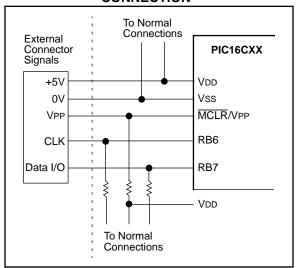

#### 9.11 In-Circuit Serial Programming

The PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 9-20.

#### FIGURE 9-20: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# **PIC16C64X & PIC16C66X**

| SUBLW        | Subtract W from Literal                                                                                                              | SUBWF                     | Subtract W from f                                                                                                                            |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                                                                             | Syntax:                   | [ label ] SUBWF f,d                                                                                                                          |  |  |

| Operands:    | $0 \le k \le 255$                                                                                                                    | Operands:                 | $0 \le f \le 127$                                                                                                                            |  |  |

| Operation:   | $k \text{ - } (W) \to (W)$                                                                                                           |                           | d ∈ [0,1]                                                                                                                                    |  |  |

| Status       | C, DC, Z                                                                                                                             | Operation:                | (f) - (W) $\rightarrow$ (dest)                                                                                                               |  |  |

| Affected:    |                                                                                                                                      | Status<br>Affected:       | C, DC, Z                                                                                                                                     |  |  |

| Encoding:    | 11 110x kkkk kkkk                                                                                                                    |                           |                                                                                                                                              |  |  |

| Description: | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. | Encoding:<br>Description: | 00         0010         dfff         ffff           Subtract (2's complement method) W register from register 'f'. If 'd' is 0 the result is |  |  |

| Words:       | 1                                                                                                                                    |                           | stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                             |  |  |

| Cycles:      | 1                                                                                                                                    | Words:                    | 1                                                                                                                                            |  |  |

| Example 1:   | SUBLW 0x02                                                                                                                           | Cycles:                   | 1                                                                                                                                            |  |  |

|              | Before Instruction                                                                                                                   | Example 1:                | SUBWF REG1,1                                                                                                                                 |  |  |

|              | W = 1                                                                                                                                |                           | Before Instruction                                                                                                                           |  |  |

|              | C = ?                                                                                                                                |                           | REG1 = 3                                                                                                                                     |  |  |

|              | After Instruction                                                                                                                    |                           | W = 2                                                                                                                                        |  |  |

|              | W = 1<br>C = 1; result is positive                                                                                                   |                           | C = ?                                                                                                                                        |  |  |

| Example 2:   | Before Instruction                                                                                                                   |                           | After Instruction                                                                                                                            |  |  |

|              | W = 2                                                                                                                                |                           | REG1 = 1<br>W = 2                                                                                                                            |  |  |

|              | C = ?                                                                                                                                |                           | C = 2<br>C = 1; result is positive                                                                                                           |  |  |

|              | After Instruction                                                                                                                    | Example 2:                | Before Instruction                                                                                                                           |  |  |

|              | W = 0                                                                                                                                |                           | REG1 = 2                                                                                                                                     |  |  |

|              | C = 1; result is zero                                                                                                                |                           | W = 2 $C = 2$                                                                                                                                |  |  |

| Example 3:   | Before Instruction                                                                                                                   |                           | After Instruction                                                                                                                            |  |  |

|              | W = 3 $C = ?$                                                                                                                        |                           | REG1 = 0                                                                                                                                     |  |  |

|              | After Instruction                                                                                                                    |                           | W = 2                                                                                                                                        |  |  |

|              | W = 0 x FF                                                                                                                           |                           | C = 1; result is zero                                                                                                                        |  |  |

|              | C = 0; result is nega-                                                                                                               | Example 3:                | Before Instruction                                                                                                                           |  |  |

|              | tive                                                                                                                                 |                           | REG1 = 1                                                                                                                                     |  |  |

|              |                                                                                                                                      |                           | $ \begin{array}{cccc} W & = & 2 \\ C & = & ? \end{array} $                                                                                   |  |  |

|              |                                                                                                                                      |                           | After Instruction                                                                                                                            |  |  |

|              |                                                                                                                                      |                           | REG1 = 0xEE                                                                                                                                  |  |  |

| REG1 | = | 0xFF                  |

|------|---|-----------------------|

| W    | = | 2                     |

| С    | = | 0; result is negative |

NOTES:

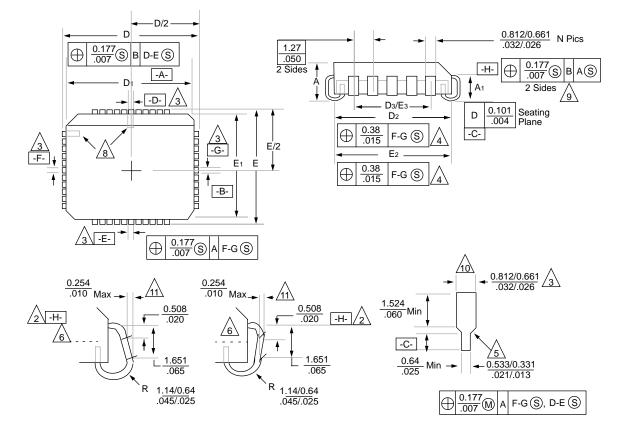

## Package Type: 44-Lead Plastic Leaded Chip Carrier (L) - Square

| Package Group: Plastic Leaded Chip Carrier (PLCC) |             |        |       |       |       |       |

|---------------------------------------------------|-------------|--------|-------|-------|-------|-------|

|                                                   | Millimeters |        |       |       |       |       |

| Symbol                                            | Min         | Мах    | Notes | Min   | Max   | Notes |

| А                                                 | 4.191       | 4.572  |       | 0.165 | 0.180 |       |

| A1                                                | 2.413       | 2.921  |       | 0.095 | 0.115 |       |

| D                                                 | 17.399      | 17.653 |       | 0.685 | 0.695 |       |

| D1                                                | 16.510      | 16.663 |       | 0.650 | 0.656 |       |

| D2                                                | 15.494      | 16.002 |       | 0.610 | 0.630 |       |

| D3                                                | 12.700      | 12.700 | BSC   | 0.500 | 0.500 | BSC   |

| E                                                 | 17.399      | 17.653 |       | 0.685 | 0.695 |       |

| E1                                                | 16.510      | 16.663 |       | 0.650 | 0.656 |       |

| E2                                                | 15.494      | 16.002 |       | 0.610 | 0.630 |       |

| E3                                                | 12.700      | 12.700 | BSC   | 0.500 | 0.500 | BSC   |

| CP                                                | —           | 0.102  |       |       | 0.004 |       |

| LT                                                | 0.203       | 0.381  |       | 0.008 | 0.015 |       |

# **APPENDIX C: WHAT'S NEW**

New Data Sheet

# APPENDIX D: WHAT'S CHANGED

New Data Sheet

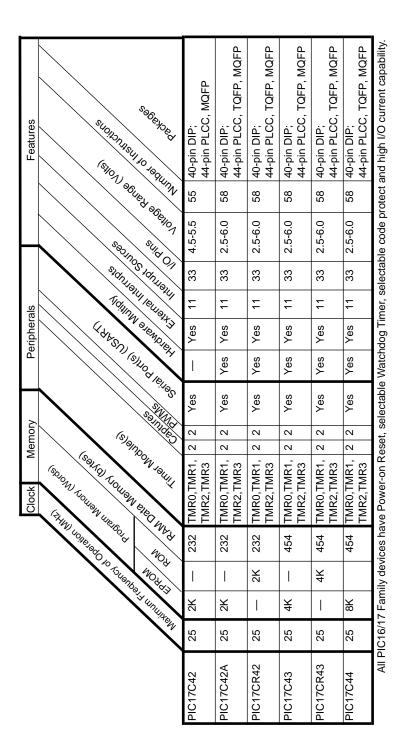

## E.8 PIC17CXX Family of Devices

## **PIN COMPATIBILITY**

Devices that have the same package type and VDD, Vss and MCLR pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

| Pin Compatible Devices                                                                                                                                                                                                                                      | Package          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| PIC12C508, PIC12C509                                                                                                                                                                                                                                        | 8-pin            |

| PIC16C54, PIC16C54A,<br>PIC16CR54A,<br>PIC16C56,<br>PIC16C58A, PIC16CR58A,<br>PIC16C61,<br>PIC16C554, PIC16C556, PIC16C558<br>PIC16C620, PIC16C621, PIC16C622,<br>PIC16C710, PIC16C71, PIC16C711,<br>PIC16F83, PIC16CR83,<br>PIC16C84, PIC16F84A, PIC16CR84 | 18-pin<br>20-pin |

| PIC16C55,<br>PIC16C57, PIC16CR57B                                                                                                                                                                                                                           | 28-pin           |

| PIC16C62, PIC16CR62, PIC16C62A, PIC16C63,<br>PIC16C72, PIC16C73, PIC16C73A                                                                                                                                                                                  | 28-pin           |

| PIC16C64, PIC16CR64, PIC16C64A,<br>PIC16C65, PIC16C65A,<br>PIC16C74, PIC16C74A                                                                                                                                                                              | 40-pin           |

| PIC17C42, PIC17CR42, PIC17C42A,<br>PIC17C43, PIC17CR43, PIC17C44                                                                                                                                                                                            | 40-pin           |

| PIC16C923, PIC16C924                                                                                                                                                                                                                                        | 64/68-pin        |

#### TABLE E-1: PIN COMPATIBLE DEVICES

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:       | Technical Publications Manager Total Pages Sent                                            |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| RE:       | Reader Response                                                                            |  |  |  |  |  |

| From      | n: Name                                                                                    |  |  |  |  |  |

|           | Company                                                                                    |  |  |  |  |  |

|           | Address                                                                                    |  |  |  |  |  |

|           | City / State / ZIP / Country                                                               |  |  |  |  |  |

|           | Telephone: () FAX: ()                                                                      |  |  |  |  |  |

| Appli     | ication (optional):                                                                        |  |  |  |  |  |

| Woul      | ld you like a reply?YN                                                                     |  |  |  |  |  |

| Devi      | CE: PIC16C64X & Literature Number: DS30559A<br>PIC16C66X                                   |  |  |  |  |  |

| Ques      | stions:                                                                                    |  |  |  |  |  |

| 1. V      | What are the best features of this document?                                               |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| 2. H      | 2. How does this document meet your hardware and software development needs?               |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| 3. E      | B. Do you find the organization of this data sheet easy to follow? If not, why?            |  |  |  |  |  |

| -         |                                                                                            |  |  |  |  |  |

| 4. V      | What additions to the data sheet do you think would enhance the structure and subject?     |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| 5. V      | What deletions from the data sheet could be made without affecting the overall usefulness? |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| 6. I      | s there any incorrect or misleading information (what and where)?                          |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| -<br>7. ⊦ | How would you improve this document?                                                       |  |  |  |  |  |

| _         |                                                                                            |  |  |  |  |  |

| -<br>8. F | How would you improve our software, systems, and silicon products?                         |  |  |  |  |  |

NOTES: