Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 176 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc642t-04-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

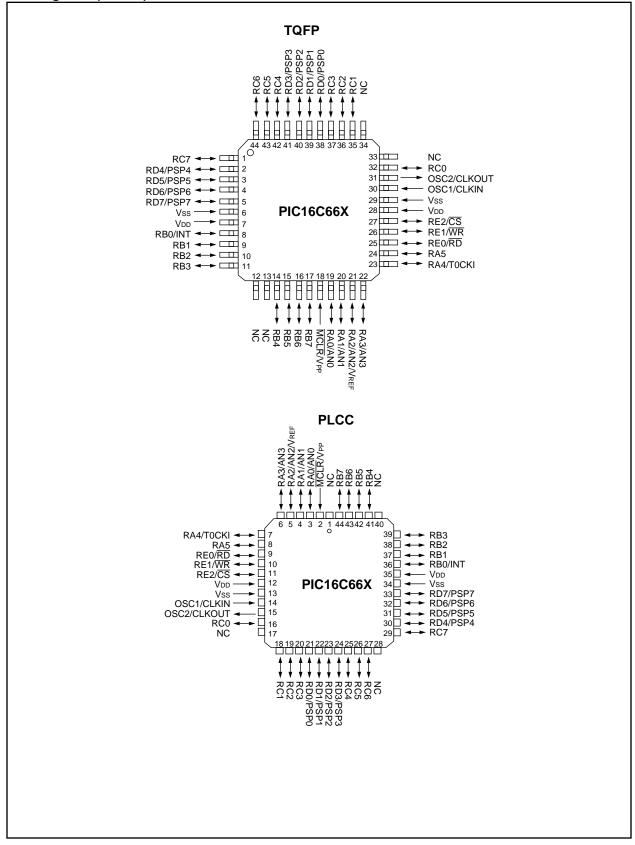

#### Pin Diagrams (Cont.'d)

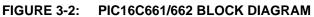

### 2.0 PIC16C64X & PIC16C66X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the Product Identification System page at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C64X & PIC16C66X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 4.2 Data Memory Organization

The data memory (Figure 4-4) is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected when bit RP0 (STATUS<5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations A0h-EFh (Bank 1) are general purpose registers implemented as static RAM. Some special function registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $176 \times 8$  for the PIC16C642/662, and 128 x8 for the PIC16C641/661. Each is accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

#### FIGURE 4-3: PIC16C641/661 DATA MEMORY MAP

| MEMORY MAP       |                                                                                       |                      |                 |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------|----------------------|-----------------|--|--|--|--|

| File<br>Address  | 5                                                                                     |                      | File<br>Address |  |  |  |  |

| 00h              | INDF <sup>(1)</sup>                                                                   | INDF <sup>(1)</sup>  | 80h             |  |  |  |  |

| 01h              | TMR0                                                                                  | OPTION               | 81h             |  |  |  |  |

| 02h              | PCL                                                                                   | PCL                  |                 |  |  |  |  |

| 03h              | STATUS                                                                                | STATUS               |                 |  |  |  |  |

| 04h              | FSR                                                                                   | FSR                  |                 |  |  |  |  |

| 05h              | PORTA                                                                                 | TRISA                | 85h             |  |  |  |  |

| 06h              | PORTB                                                                                 | TRISB                | 86h             |  |  |  |  |

| 07h              | PORTC                                                                                 | TRISC                | 87h             |  |  |  |  |

| 08h              | PORTD <sup>(2)</sup>                                                                  | TRISD <sup>(2)</sup> | 88h             |  |  |  |  |

| 09h              | PORTE <sup>(2)</sup>                                                                  | TRISE <sup>(2)</sup> | 89h             |  |  |  |  |

| 0Ah              | PCLATH                                                                                | PCLATH               | 8Ah             |  |  |  |  |

| 0Bh              | INTCON                                                                                | INTCON               | 8Bh             |  |  |  |  |

| 0Ch              | PIR1                                                                                  | PIE1                 | 8Ch             |  |  |  |  |

| 0Dh              |                                                                                       |                      | 8Dh             |  |  |  |  |

| 0Eh              |                                                                                       | PCON                 | 8Eh             |  |  |  |  |

| 0Fh              |                                                                                       |                      | 8Fh             |  |  |  |  |

| 10h              |                                                                                       |                      | 90h             |  |  |  |  |

| 11h              |                                                                                       |                      | 91h             |  |  |  |  |

| 12h              |                                                                                       |                      | 92h             |  |  |  |  |

| 13h              |                                                                                       |                      | 93h             |  |  |  |  |

| 14h              |                                                                                       |                      | 94h             |  |  |  |  |

| 15h              |                                                                                       |                      | 95h             |  |  |  |  |

| 16h              |                                                                                       |                      | 96h             |  |  |  |  |

| 17h              |                                                                                       |                      | 97h             |  |  |  |  |

| 18h              |                                                                                       |                      | 98h             |  |  |  |  |

| 19h              |                                                                                       |                      | 99h             |  |  |  |  |

| 1Ah<br>1Ph       |                                                                                       |                      | 9Ah<br>9Bh      |  |  |  |  |

| 1Bh<br>1Ch       |                                                                                       |                      | 960<br>9Ch      |  |  |  |  |

| 1Dh              |                                                                                       |                      | 90h             |  |  |  |  |

| 1Eh              |                                                                                       |                      | 9Eh             |  |  |  |  |

| 1Fh              | CMCON                                                                                 | VRCON                | 9Eh             |  |  |  |  |

| 20h              | CIVICOIN                                                                              | VICON                |                 |  |  |  |  |

| 2011             | General<br>Purpose                                                                    | General<br>Purpose   | A0h             |  |  |  |  |

|                  | Register                                                                              | Register             | BFh             |  |  |  |  |

|                  |                                                                                       |                      | C0h             |  |  |  |  |

|                  |                                                                                       |                      | EFh             |  |  |  |  |

|                  |                                                                                       | Mapped               | F0h             |  |  |  |  |

|                  |                                                                                       | in Page 0            |                 |  |  |  |  |

| 7Fh <sup>l</sup> | Bank 0                                                                                | Bank 1               | _ FFh           |  |  |  |  |

| Note 1: N        | Unimplemented data memory locations, read as '0'.<br>Note 1: Not a physical register. |                      |                 |  |  |  |  |

|                  |                                                                                       |                      |                 |  |  |  |  |

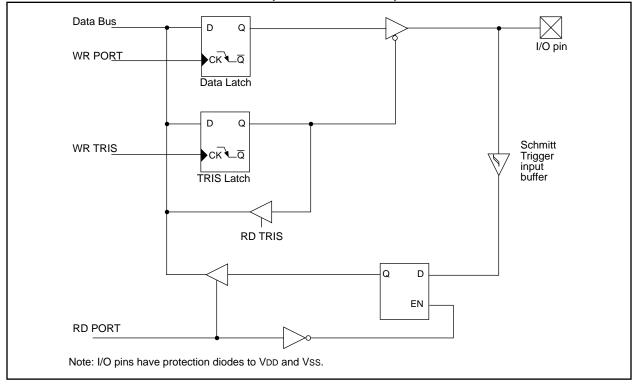

#### FIGURE 5-10: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

### TABLE 5-9: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                      |

|--------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode:<br>RD                                                                                                |

|        |      |                       | 1 = Not a read operation                                                                                                                                                      |

|        |      |                       | 0 = Read operation. Reads PORTD register (if chip selected)                                                                                                                   |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

#### TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|--------|--------|--------|--------------------------|---------------------------|

| 09h     | PORTE | —     | _     | —     | —       |       | RE2    | RE1    | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must be followed even if the WDT is disabled.

# EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

|        |             |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2.

# EXAMPLE 6-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                    | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|--------------------------|--------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------|

| 01h     | TMR0   | Timer0 module's register |        |        |        |        |        |        |        | xxxx xxxx                | uuuu uuuu                 |

| 0Bh/8Bh | INTCON | GIE                      | PEIE   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h     | OPTION | RBPU                     | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h     | TRISA  | —                        | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

# 9.0 SPECIAL FEATURES OF THE CPU

What sets apart a microcontroller from other processors are special circuits to deal with the needs of real-time applications. The PIC16C64X & PIC16C66X families have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. Oscillator selection

- 2. Resets

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR) Parity Error Reset (PER)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16C64X & PIC16C66X has a Watchdog Timer which is enabled by a configuration bit (WDTE). It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. Circuitry has been provided for checking program memory parity with a reset when an error is indicated. There is also circuitry to reset the device if a brown-out occurs which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 9.3 <u>Reset</u>

The PIC16CXXX differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) Brown-out Reset (BOR)

- f) Parity Error Reset (PER)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR, WDT reset, Brown-out Reset, Parity Error Reset, and on MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the reset. See Table 9-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 9-7.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 12-6 for pulse width specification.

#### FIGURE 9-7: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Status | Notes |          |       |

|------------|--------|------------------------------|--------|-----|--------|--------|-------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb   | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |       |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff  | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0000   | 0011  | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff  | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff  | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff  |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff  | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff  |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff  | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff  | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff  |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000  |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff  | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff  | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff  |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff  | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |       |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff  |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff  |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff  |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff  |          | 3     |

| LITERAL AI | ND CO  | NTROL OPERATIONS             |        |     |        |        |       |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk  | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk  | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk  |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk  | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001  |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk  |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000  |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011  | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk  | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   |        |       | Z        |       |

#### TABLE 10-2: INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the next<br>instruction is skipped.<br>If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and a NOP is<br>executed instead, making this a 2 cycle<br>instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                  | if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| CLRF             | Clear f                                                                                |      |       |   |      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------|------|-------|---|------|--|--|--|--|--|

| Syntax:          | [label] CLRF f                                                                         |      |       |   |      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                      |      |       |   |      |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                  |      |       |   |      |  |  |  |  |  |

| Status Affected: | Z                                                                                      |      |       |   |      |  |  |  |  |  |

| Encoding:        | 00                                                                                     | 0001 | 1ff   | f | ffff |  |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.                         |      |       |   |      |  |  |  |  |  |

| Words:           | 1                                                                                      |      |       |   |      |  |  |  |  |  |

| Cycles:          | 1                                                                                      |      |       |   |      |  |  |  |  |  |

| Example          | CLRF                                                                                   | FLAG | G_REG | 3 |      |  |  |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction<br>FLAG_REG = 0x00<br>Z = 1 |      |       |   |      |  |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                               |  |  |  |  |  |  |  |  |

| CLRW             | Clear W                                                               |                              |                   |        |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|------------------------------|-------------------|--------|--|--|--|--|--|

| Syntax:          | [label] CLRW                                                          |                              |                   |        |  |  |  |  |  |

| Operands:        | None                                                                  |                              |                   |        |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                              |                   |        |  |  |  |  |  |

| Status Affected: | Z                                                                     |                              |                   |        |  |  |  |  |  |

| Encoding:        | 00                                                                    | 0001                         | 0000              | 0011   |  |  |  |  |  |

| Description:     | W register set.                                                       | is cleare                    | d. Zero bit       | (Z) is |  |  |  |  |  |

| Words:           | 1                                                                     |                              |                   |        |  |  |  |  |  |

| Cycles:          | 1                                                                     |                              |                   |        |  |  |  |  |  |

| Example          | CLRW                                                                  |                              |                   |        |  |  |  |  |  |

|                  | Before In                                                             | struction                    | 1                 |        |  |  |  |  |  |

|                  | After Inst                                                            | W =<br>ruction<br>W =<br>Z = | 0x5A<br>0x00<br>1 |        |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                  |               |      |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                               | RETUR         | N    |      |  |  |  |

| Operands:        | None                                                                                                                                                    |               |      |      |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                              |               |      |      |  |  |  |

| Status Affected: | None                                                                                                                                                    |               |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                      | 0000          | 0000 | 1000 |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |               |      |      |  |  |  |

| Words:           | 1                                                                                                                                                       |               |      |      |  |  |  |

| Cycles:          | 2                                                                                                                                                       |               |      |      |  |  |  |

| Example          | RETURN                                                                                                                                                  |               |      |      |  |  |  |

|                  | After Inte                                                                                                                                              | rrupt<br>PC = | TOS  |      |  |  |  |

| RRF              | Rotate R                                                                                                                                                                                                     | ight f th      | roug        | gh Ca             | rry  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                    | RRF f,         | d           |                   |      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                    | 7              |             |                   |      |  |  |  |

| Operation:       | See description below                                                                                                                                                                                        |                |             |                   |      |  |  |  |

| Status Affected: | С                                                                                                                                                                                                            |                |             |                   |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                           | 1100           | dfi         | Ef                | ffff |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                |             |                   |      |  |  |  |

|                  |                                                                                                                                                                                                              |                | Regis       | tert              |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                            |                |             |                   |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                            |                |             |                   |      |  |  |  |

| Example          | RRF                                                                                                                                                                                                          |                | REG1        | ,0                |      |  |  |  |

|                  |                                                                                                                                                                                                              | REG1<br>C      | =           | 1110<br>0         | 0110 |  |  |  |

|                  | ,                                                                                                                                                                                                            | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |      |  |  |  |

| RLF              | Rotate Left f through Carry                                                        | SLEEP            |                                                                      |

|------------------|------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                           | Syntax:          | [label] SLEEP                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                 | Operands:        | None                                                                 |

| Operation:       | See description below                                                              | Operation:       | 00h $\rightarrow$ WDT,<br>0 $\rightarrow$ WDT prescaler,             |

| Status Affected: | С                                                                                  |                  | $1 \rightarrow \overline{TO}$ ,                                      |

| Encoding:        | 00 1101 dfff ffff                                                                  |                  | $0 \rightarrow \overline{PD}$                                        |

| Description:     | The contents of register 'f' are rotated                                           | Status Affected: | TO, PD                                                               |

|                  | one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in | Encoding:        | 00 0000 0110 0011                                                    |

|                  | the W register. If 'd' is 1 the result is                                          | Description:     | The power-down status bit, PD is cleared. Time-out status bit, TO is |

|                  | stored back in register 'f'.                                                       |                  | set. Watchdog Timer and its pres-                                    |

|                  | C Register f                                                                       |                  | caler are cleared.<br>The processor is put into SLEEP                |

| Words:           | 1                                                                                  |                  | mode with the oscillator stopped.                                    |

| Cycles:          | 1                                                                                  |                  | See Power-Down Mode (SLEEP) for<br>more details.                     |

| Example          | RLF REG1,0                                                                         | Words:           | 1                                                                    |

|                  | Before Instruction                                                                 | Cycles:          | 1                                                                    |

|                  | <b>REG1</b> = 1110 0110<br><b>C</b> = 0                                            | Example:         | SLEEP                                                                |

|                  | After Instruction                                                                  |                  |                                                                      |

|                  | REG1 = 1110 0110<br>W = 1100 1100                                                  |                  |                                                                      |

|                  | C = 1                                                                              |                  |                                                                      |

#### 11.6 <u>PICDEM-1 Low-Cost PIC16/17</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-16B programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 11.7 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-16C, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

#### 11.8 <u>PICDEM-3 Low-Cost PIC16CXX</u> Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals. PICDEM-3 will be available in the 3rd guarter of 1996.

#### 11.9 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- · Customizable tool bar and key mapping

- A status bar with project information

- Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 11.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers. MPASM allows full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 11.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 11.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

#### 11.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 11.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 11.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 11.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

#### 11.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

#### 12.2 DC Characteristics: PIC16LC641/642/661/662-04 (Commercial, Industrial)

|                                                                                 |                | Standard Operating Conditions (                                  | unless                                           | otherwi                       | se sta       | ted)   |                                                                                   |

|---------------------------------------------------------------------------------|----------------|------------------------------------------------------------------|--------------------------------------------------|-------------------------------|--------------|--------|-----------------------------------------------------------------------------------|

| Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and |                |                                                                  |                                                  |                               |              |        |                                                                                   |

|                                                                                 |                | 0°C                                                              | $\leq$ TA $\leq$                                 | +70°C                         | COI          | nmerci | al                                                                                |

| Param<br>No.                                                                    | Sym            | Characteristic                                                   | Min                                              | Тур†                          | Max          | Units  | Conditions                                                                        |

| D001                                                                            | Vdd            | Supply Voltage                                                   | 3.0                                              | _                             | 6.0          | V      | XT, RC, and LP osc configuration                                                  |

| D002*                                                                           | Vdr            | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5                                              | _                             | -            | V      | Device in SLEEP mode                                                              |

| D003                                                                            | VPOR           | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | -                                                | Vss                           | -            | V      | See section on Power-on Reset for details                                         |

| D004*                                                                           | SVDD           | VDD rise rate to ensure internal Power-on Reset signal           | 0.05                                             | _                             | _            | V/ms   | See section on Power-on Reset for details                                         |

| D005                                                                            | VBOR           | Brown-out Reset Voltage                                          | 3.7                                              | 4.0                           | 4.3          | V      | BODEN configuration bit is clear                                                  |

| D010                                                                            | IDD            | Supply Current <sup>(2)</sup>                                    | _                                                | 2.0                           | 3.8          | mA     | XT and RC osc configuration<br>Fosc = 4.0 MHz, $VDD = 3.0V$ ,<br>WDT disabled (4) |

| D010A                                                                           |                |                                                                  | _                                                | 22.5                          | 48           | μΑ     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V,<br>WD7 disabled                |

|                                                                                 |                | Module Differential Current (5)                                  |                                                  | $\square$                     | $\checkmark$ |        |                                                                                   |

| D015                                                                            | $\Delta$ IBOR  | Brown-out Reset Current                                          |                                                  | 350                           | 425          | μA     | BODEN bit is clear, VDD = 5.0V                                                    |

| D016                                                                            |                | Comparator Current for<br>each Comparator                        | $\left  \begin{array}{c} \\ \end{array} \right $ |                               | 100          | μA     | VDD = 3.0V                                                                        |

| D017                                                                            | $\Delta$ IVREF | VREF Current                                                     |                                                  | $\langle \mathcal{L} \rangle$ | 300          | μA     | VDD = 3.0V                                                                        |

| D021                                                                            | ΔIWDT          | WDT Current                                                      |                                                  | 6.0>                          | 20           | μA     | VDD = 3.0V                                                                        |

| D021                                                                            | IPD            | Power-down Current (3)                                           | $\left  \right\rangle$                           | Ø.9                           | 5            | μA     | VDD = 3.0V, WDT disabled                                                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which Voo can be Jowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the surrent consumption.

The test conditions for all Job measurements in active operation mode are:

OSC1=external square wave, from rail to rail; all I/O pins tristated, pulled to VDD,

$\overline{\text{MCLR}} = \sqrt{\text{DD}}$ ;  $\overline{\text{WRT}}$  enabled/disabled as specified.

The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

For RC osc configuration, current through Rext is not included. The current through the resistor can be

< estimated by the formula Ir = VDD/2Rext (mA) with Rext in k $\Omega$ . 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be

added to the base IDD or IPD measurement.

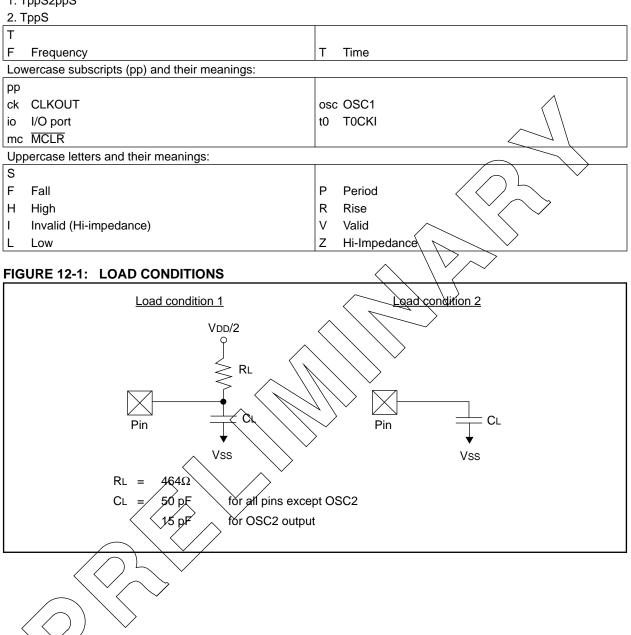

### 12.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

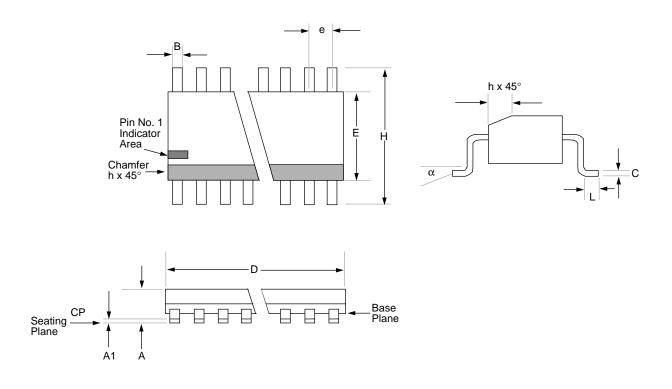

### Package Type: 28-Lead Plastic Small Outline (SO) - Wide, 300 mil Body

|        | Package Group: Plastic SOIC (SO) |             |       |        |            |       |  |

|--------|----------------------------------|-------------|-------|--------|------------|-------|--|

|        |                                  | Millimeters |       | Inches |            |       |  |

| Symbol | Min                              | Max         | Notes | Min    | Max        | Notes |  |

| α      | 0°                               | <b>8</b> °  |       | 0°     | <b>8</b> ° |       |  |

| А      | 2.362                            | 2.642       |       | 0.093  | 0.104      |       |  |

| A1     | 0.101                            | 0.300       |       | 0.004  | 0.012      |       |  |

| В      | 0.355                            | 0.483       |       | 0.014  | 0.019      |       |  |

| С      | 0.241                            | 0.318       |       | 0.009  | 0.013      |       |  |

| D      | 17.703                           | 18.085      |       | 0.697  | 0.712      |       |  |

| E      | 7.416                            | 7.595       |       | 0.292  | 0.299      |       |  |

| е      | 1.270                            | 1.270       | BSC   | 0.050  | 0.050      | BSC   |  |

| Н      | 10.007                           | 10.643      |       | 0.394  | 0.419      |       |  |

| h      | 0.381                            | 0.762       |       | 0.015  | 0.030      |       |  |

| L      | 0.406                            | 1.143       |       | 0.016  | 0.045      |       |  |

| CP     | —                                | 0.102       |       | —      | 0.004      |       |  |

D1 D D/2 PinNo. 1 Indicato<del>r</del> Area REFERERE E1 E Ė/2 8 Places A /11/13° 0° min. Detail B A2 | Datum Plane 0.25 0.08 R min. Å1 . 0-7° with Lead Finish Gauge Plane 0.20 min-0.09/0.2 0.09/0.16 1.00 ref. **▲** b1 Base Metal DETAIL B

Package Type: 44-Lead Thin Plastic Quad Flatpack (PT/TQ) - 10x10x1 mm Body 1.0/0.10 mm Lead Form

|        | Package Group: Plastic TQFP |             |       |        |            |       |  |  |

|--------|-----------------------------|-------------|-------|--------|------------|-------|--|--|

|        |                             | Millimeters |       | Inches |            |       |  |  |

| Symbol | Min                         | Max         | Notes | Min    | Max        | Notes |  |  |

| α      | 0°                          | <b>7</b> °  |       | 0°     | <b>7</b> ° |       |  |  |

| А      |                             | 1.200       |       | _      | 0.047      |       |  |  |

| A1     | 0.050                       | 0.150       |       | 0.002  | 0.006      |       |  |  |

| A2     | 0.950                       | 1.050       |       | 0.037  | 0.041      |       |  |  |

| b      | 0.300                       | 0.450       |       | 0.012  | 0.018      |       |  |  |

| b1     | 0.300                       | 0.400       |       | 0.012  | 0.016      |       |  |  |

| D      | 12.0                        | 12.0        | BSC   | 0.472  | 0.0472     | BSC   |  |  |

| D1     | 10.0                        | 10.0        | BSC   | 0.394  | 0.394      | BSC   |  |  |

| Е      | 12.0                        | 12.0        | BSC   | 0.472  | 0.472      | BSC   |  |  |

| E1     | 10.0                        | 10.0        | BSC   | 0.394  | 0.394      | BSC   |  |  |

| е      | 0.8                         | 0.8         | BSC   | 0.031  | 0.031      | BSC   |  |  |

| L      | 0.450                       | 0.750       |       | 0.018  | 0.030      |       |  |  |

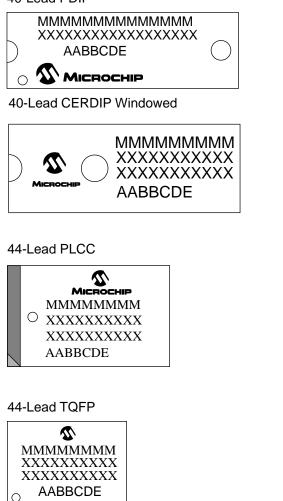

#### 14.2 Package Marking Information

#### 40-Lead PDIP

Example

PIC16C662-04/P

9512CAA

Similar Microchip

Example

#### Example

Example

| Legend | : MMMMicrochip part number information                    |

|--------|-----------------------------------------------------------|

| XXX    | Customer specific information*                            |

| AA     | Year code (last 2 digits of calendar year)                |

| BB     | Week code (week of January 1 is week '01')                |

| С      | Facility code of the plant at which wafer is manufactured |

|        | C = Chandler, Arizona, U.S.A.                             |

| D      | Mask revision number                                      |

| E      | Assembly code of the plant or country of origin in which  |

|        | part was assembled                                        |

|        |                                                           |

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\*Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

© 1996 Microchip Technology Inc.

| i |          |  |       |            |       |                               |                               |                               |                               |                               |                               |                                    |                                    |

|---|----------|--|-------|------------|-------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|------------------------------------|------------------------------------|

|   | Features |  | 135   | Saber 10.0 |       | 18-pin DIP, SOIC; 20-pin SSOP | 28-pin PDIP, SOIC<br>Windowed CDIP | 28-pin PDIP, SOIC<br>Windowed CDIP |

|   |          |  | TV of | S Ino. C   | Stc.  | I                             | I                             | I                             | Yes                           | Yes                           | Yes                           | Yes                                | Yes                                |

|   | s        |  |       | -0         | eilon | -6.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                               | -6.0                               |

2.5-6.0 2.5-6.0 2.5-6.0 2.5-6.0 2.5-6.0 3.0-6.0

33 33

> ო ო

I I

I

128

80

512

PIC16C620 PIC16C621 PIC16C622

13 33 13 13 22

4

4 4

128

80

¥ З Ж

128

PIC16C641

2

4

Yes Yes Yes Yes

N 2 N

2.5-6.0

ო

TMR0 **TMR0** TMR0 TMR0 TMR0 TMR0 TMR0

80 80

512

20 20 20 20 20 20 20

PIC16C554 PIC16C556 PIC16C558

¥ Я

<sup>\$UI</sup>OJ

estros idniejuj

(s)logeredulos

(S)OULOUNOUN

(Seyla) Trouten ered

CETHIN LOIRE BES DO TO TOUR I UNITUREN

SEELION SOLISISTER TELLSULT

Aousw usion

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6XXX Family devices use serial programming with clock pin RB6 and data pin RB7.

#### E.3 **PIC16CXXX Family of Devices**

Peripherals

Memory

Clock

40-pin PDIP, Windowed CDIP;

Yes

3.0-6.0

33

ß

Yes

2

TMR0

176

¥

20

PIC16C662

44-pin PLCC, MQFP

40-pin PDIP, Windowed CDIP; 44-pin PLCC, MQFP

Yes

3.0-6.0

33

ŝ

Yes

2

**TMR0**

128

З

20

PIC16C661

3.0-6.0

22

4

Yes

2

**TMR0**

176

¥

20

PIC16C642

#### I

| I/O Ports                                   | 29 |

|---------------------------------------------|----|

| PORTA                                       | 29 |

| PORTB                                       |    |

| PORTC                                       |    |

| PORTD                                       |    |

| PORTE                                       |    |

| I/O Programming Considerations              |    |

| ICEPIC In-Circuit Emulator                  |    |

|                                             |    |

| ID Locations                                |    |

| INCF Instruction                            |    |

| INCFSZ Instruction                          |    |

| In-Circuit Serial Programming               | 71 |

| Indirect Addressing, INDF and FSR Registers |    |

| Instruction Flow/Pipelining                 |    |

| Instruction Format                          | 73 |

| Instruction Set                             |    |

| ADDLW                                       | 76 |

| ADDWF                                       | 76 |

| ANDLW                                       | 76 |

| ANDWF                                       | 76 |

| BCF                                         |    |

| BSF                                         |    |

| BTFSC                                       |    |

| BTFSCBTFSS                                  |    |

|                                             |    |

| CALL                                        |    |

| CLRF                                        |    |

| CLRW                                        |    |

| CLRWDT                                      |    |

| COMF                                        |    |

| DECF                                        | 79 |

| DECFSZ                                      | 79 |

| GOTO                                        |    |

| INCF                                        | 80 |

| INCFSZ                                      |    |

| IORLW                                       |    |

| IORWF                                       |    |

| MOVF                                        | -  |

|                                             |    |

|                                             |    |

| MOVWF                                       |    |

| NOP                                         | -  |

| OPTION                                      |    |

| RETFIE                                      |    |

| RETLW                                       |    |

| RETURN                                      | 83 |

| RLF                                         |    |

| RRF                                         |    |

| SLEEP                                       |    |

| SUBLW                                       |    |

| SUBWF                                       |    |

| SWAPF                                       |    |

| TRIS                                        |    |

| XORLW                                       |    |

| XORWF                                       |    |

|                                             |    |

| Section                                     |    |

| Summary Table                               |    |

| INT Interrupt                               |    |