Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 176 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc662-04-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

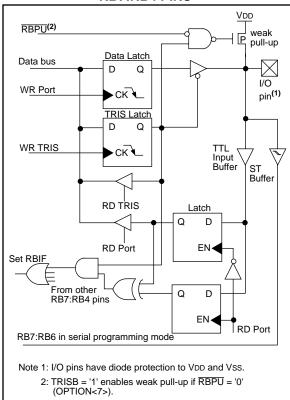

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{\text{RBPU}}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in (INTCON<0>)).

### FIGURE 5-5: BLOCK DIAGRAM OF RB7:RB4 PINS

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

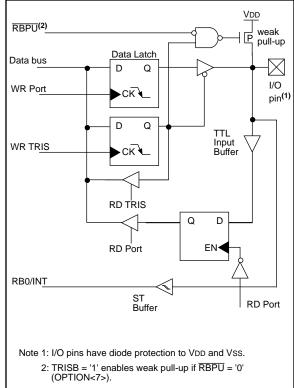

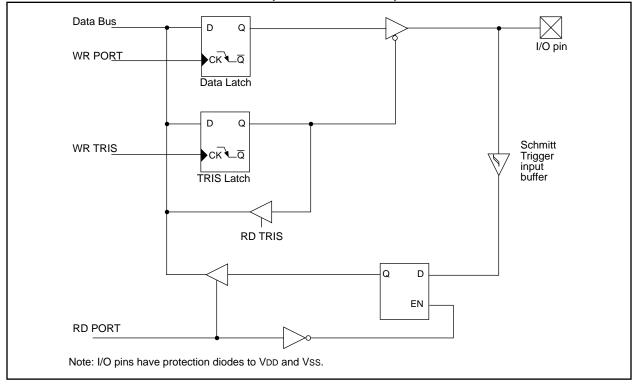

### 5.5 <u>PORTE and TRISE Register</u> (PIC16C661 and PIC16C662 only)

PORTE has three pins RE0/ $\overline{RD}$ , RE1/ $\overline{WR}$ , and RE2/ $\overline{CS}$ , which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). In this mode the input buffers are TTL.

FIGURE 5-9: TRISE REGISTER (ADDRESS 89h)

Г

| R-0         | R-0 R/W-0 R/W-0 U-0 R/W-1 R/W-1 R/W-1                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IBF<br>bit7 | OBF       IBOV       PSPMODE       TRISE2       TRISE1       TRISE0       R       = Readable bit         bit0       W       = Writable bit       U       = Unimplemented bit, read as '0'       - n       = Value at POR reset          |

| bit 7:      | <b>IBF:</b> Input Buffer Full Status bit<br>1 = A word has been received and waiting to be read by the CPU<br>0 = No word has been received                                                                                             |

| bit 6:      | <b>OBF</b> : Output Buffer Full Status bit<br>1 = The output buffer still holds a previously written word<br>0 = The output buffer has been read                                                                                        |

| bit 5:      | <ul> <li><b>IBOV</b>: Input Buffer Overflow Detect bit (in microprocessor mode)</li> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |

| bit 4:      | <b>PSPMODE</b> : Parallel Slave Port Mode Select bit<br>1 = Parallel slave port mode<br>0 = General purpose I/O mode                                                                                                                    |

| bit 3:      | Unimplemented: Read as '0'                                                                                                                                                                                                              |

| bit 2:      | TRISE2: Direction control bit for pin RE2/CS<br>1 = Input<br>0 = Output                                                                                                                                                                 |

| bit 1:      | TRISE1: Direction control bit for pin RE1/WR<br>1 = Input<br>0 = Output                                                                                                                                                                 |

| bit 0:      | <b>TRISE0</b> : Direction control bit for pin RE0/RD<br>1 = Input<br>0 = Output                                                                                                                                                         |

Figure 5-9 shows the TRISE register, which also controls the parallel slave port operation.

### FIGURE 5-10: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

## TABLE 5-9: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                      |

|--------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode:<br>RD                                                                                                |

|        |      |                       | 1 = Not a read operation                                                                                                                                                      |

|        |      |                       | 0 = Read operation. Reads PORTD register (if chip selected)                                                                                                                   |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

### TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|--------|--------|--------|--------------------------|---------------------------|

| 09h     | PORTE | —     | _     | —     | —       |       | RE2    | RE1    | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must be followed even if the WDT is disabled.

# EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

|        |             |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2.

## EXAMPLE 6-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

### TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|--------|-------------|--------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------|

| 01h     | TMR0   | Timer0 | module's re |        | xxxx xxxx | uuuu uuuu |        |        |        |                          |                           |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | TOIE   | INTE      | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h     | OPTION | RBPU   | INTEDG      | TOCS   | TOSE      | PSA       | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h     | TRISA  | —      | _           | TRISA5 | TRISA4    | TRISA3    | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

| Address | Name   | Bit 7                | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|--------|----------------------|-------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT                | C1OUT | _      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                 | 00 0000                         |

| 9Fh     | VRCON  | VREN                 | VROE  | VRR    | —      | VR3    | VR2    | VR1    | VR0    | 000- 0000               | 000- 0000                       |

| 0Bh/8Bh | INTCON | GIE                  | PEIE  | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | CMIF  | —      | —      |        |        | _      | _      | 00                      | 00                              |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | CMIE  | _      |        | —      | _      | _      | _      | 00                      | 00                              |

| 85h     | TRISA  | _                    | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

Note 1: These bits are reserved on the PIC16C641/642, always maintain these bits clear.

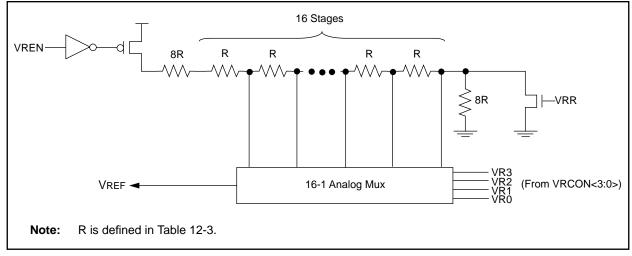

## 8.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference module is not being used. The VRCON register, shown in Figure 8-1, controls the operation of the Voltage Reference Module. The block diagram is given in Figure 8-2.

## FIGURE 8-1: VRCON REGISTER (ADDRESS 9Fh)

| R/W-0    | R/W-0                                                                                              | R/W-0      | U-0      | R/W-0         | R/W-0      | R/W-0 | R/W-0 |                                                                                    |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------|------------|----------|---------------|------------|-------|-------|------------------------------------------------------------------------------------|--|--|--|--|--|

| VREN     | VROE                                                                                               | VRR        |          | VR3           | VR2        | VR1   | VR0   | R =Readable bit                                                                    |  |  |  |  |  |

| bit7     |                                                                                                    |            |          |               |            |       | bit0  | W =Writable bit<br>U =Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |  |  |  |  |

| bit 7:   | VREN: VRE<br>1 = VREF ci<br>0 = VREF ci                                                            | rcuit powe |          | n, no Idd     | drain      |       |       |                                                                                    |  |  |  |  |  |

| bit 6:   | VROE: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |            |          |               |            |       |       |                                                                                    |  |  |  |  |  |

| bit 5:   | <b>VRR:</b> VREF<br>1 = Low Ra<br>0 = High Ra                                                      | inge       | lection  |               |            |       |       |                                                                                    |  |  |  |  |  |

| bit 4:   | Unimplem                                                                                           | ented: Rea | ad as '0 | I             |            |       |       |                                                                                    |  |  |  |  |  |

| bit 3-0: | VR3:VR0:                                                                                           | VREF value | selecti  | on $0 \le VR$ | 3:VR0 ≤ 15 | 5     |       |                                                                                    |  |  |  |  |  |

|          | When: VRF<br>Then: VREF                                                                            |            | R0/ 24)  | • Vdd         |            |       |       |                                                                                    |  |  |  |  |  |

|          | When: VRF<br>Then: VREF                                                                            |            | D + (VI  | R3:VR0/ 32    | 2) • Vdd   |       |       |                                                                                    |  |  |  |  |  |

### 9.1 <u>Configuration Bits</u>

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

## FIGURE 9-1: CONFIGURATION WORD

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h–3FFFh), which can be accessed only during programming.

| CP1     | CPO | CP1                  | CP0     | CP1      | CP0     | MPEEN               | BODEN       | CP1     | CP0      | PWRTE       | WDTE       | FOSC1       | FOSC0        | CONFIG           | Address |

|---------|-----|----------------------|---------|----------|---------|---------------------|-------------|---------|----------|-------------|------------|-------------|--------------|------------------|---------|

| bit13   |     |                      |         |          |         |                     |             |         |          |             |            |             | bit0         | REGISTER:        | 2007h   |

| bit 13- |     | CP1:CF               |         |          |         | oits <sup>(2)</sup> |             |         |          |             |            |             |              |                  |         |

| 5-4     | 4:  | 11 = Co<br>10 = Up   |         |          |         | emory cod           | le protecte | d       |          |             |            |             |              |                  |         |

|         |     | 01 = Up              | per 3/4 | th of pr | ogram i | memory co           |             |         |          |             |            |             |              |                  |         |

|         |     | 00 = All             |         | ,        | •       |                     |             |         |          |             |            |             |              |                  |         |

| bit 7:  |     | MPEEN                |         |          |         | Enable<br>s enabled |             |         |          |             |            |             |              |                  |         |

|         |     |                      |         |          |         | s disabled          |             |         |          |             |            |             |              |                  |         |

| bit 6:  |     |                      |         |          | eset En | able bit (1)        |             |         |          |             |            |             |              |                  |         |

|         |     | 1 = BOF<br>0 = BOF   |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

| bit 3:  |     |                      |         |          |         | ble bit (1)         |             |         |          |             |            |             |              |                  |         |

| DIL 3.  |     | 1 = PWI              |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

|         |     | 0 = PWI              | RT enal | oled     |         |                     |             |         |          |             |            |             |              |                  |         |

| bit 2:  |     | <b>WDTE</b> : 1 = WD |         |          | er Enat | ole bit             |             |         |          |             |            |             |              |                  |         |

|         |     | 1 = WD<br>0 = WD     |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

| bit 1-0 | D:  | FOSC1:               | FOSCO   | : Oscill | ator Se | lection bits        | 6           |         |          |             |            |             |              |                  |         |

|         |     | 11 = RC              |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

|         |     | 10 = HS<br>01 = XT   |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

|         |     | 00 = LP              |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

| Note    | 1:  | Enabling             | Brown   | n-out Ré | eset au | tomatically         | enables t   | ne Pov  | /er-up T | imer (P\V/F | RT) regar  | tless of th | e value of l | bit PWRTE. Ens   | ure the |

| NOIG    |     |                      |         |          |         | iytime Bro          |             |         |          |             | (i) iogait |             |              | SICT WITTE. EIIS |         |

|         | 2:  | All of the           | e CP1:0 | CP0 pai  | rs have | to be give          | n the sam   | e value | e to ena | ble the coo | de protect | ion schen   | ne listed.   |                  |         |

|         |     |                      |         |          |         |                     |             |         |          |             |            |             |              |                  |         |

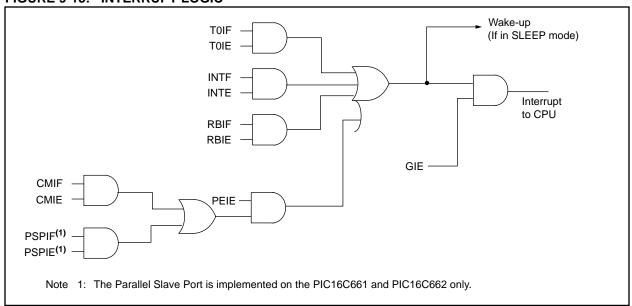

### 9.5 Interrupts

The PIC16C641 and PIC16C642 have four sources of interrupt, while the PIC16C661 and PIC16C662 have five sources:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

- · Comparator interrupt

- Parallel Slave Port interrupt (PIC16C661/662)

The interrupt control register, (INTCON), records individual core interrupt requests in flag bits. It also has various individual enable bits and the global interrupt enable bit.

The global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which allows any pending interrupt to execute.

Those interrupts associated with the "core" have their flag and enable bits in the INTCON register. The core interrupts are: RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt. The INTCON register also contains the Peripheral Interrupt Enable bit, PEIE. Bit PEIE will enable/mask the peripheral interrupts (CM and PSP) from vectoring when bit PEIE is set/cleared.

Flag bits PSPIF and CMIF are contained in special function register PIR1. The corresponding interrupt enable bits (PSPIE and CMIE) are contained in special function register PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the RB0/INT or Port RB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 9-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

## FIGURE 9-15: INTERRUPT LOGIC

| Mnemonic,  |        | Description                  | Cycles |     | 14-Bit | Opcode | Э    | Status   | Notes |

|------------|--------|------------------------------|--------|-----|--------|--------|------|----------|-------|

| Operands   |        |                              |        | MSb |        |        | LSb  | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |      |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00  | 0001   | 0000   | 0011 | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff |          |       |

| NOP        | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000 |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |      |          |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff |          | 3     |

| LITERAL AI | ND CO  | NTROL OPERATIONS             |        |     |        |        |      |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000 |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW      | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW      | k      | Exclusive OR literal with W  | 1      | 11  | 1010   |        |      | Z        |       |

### TABLE 10-2: INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# **PIC16C64X & PIC16C66X**

| SUBLW        | Subtract W from Literal                                                                                                              | SUBWF                     | Subtract W from f                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:      | [ <i>label</i> ] SUBLW k                                                                                                             | Syntax:                   | [ label ] SUBWF f,d                                                                                                                          |

| Operands:    | $0 \le k \le 255$                                                                                                                    | Operands:                 | $0 \le f \le 127$                                                                                                                            |

| Operation:   | $k \text{ - } (W) \to (W)$                                                                                                           |                           | d ∈ [0,1]                                                                                                                                    |

| Status       | C, DC, Z                                                                                                                             | Operation:                | (f) - (W) $\rightarrow$ (dest)                                                                                                               |

| Affected:    |                                                                                                                                      | Status<br>Affected:       | C, DC, Z                                                                                                                                     |

| Encoding:    | 11 110x kkkk kkkk                                                                                                                    |                           |                                                                                                                                              |

| Description: | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. | Encoding:<br>Description: | 00         0010         dfff         ffff           Subtract (2's complement method) W register from register 'f'. If 'd' is 0 the result is |

| Words:       | 1                                                                                                                                    |                           | stored in the W register. If 'd' is 1 the result is stored back in register 'f'.                                                             |

| Cycles:      | 1                                                                                                                                    | Words:                    | 1                                                                                                                                            |

| Example 1:   | SUBLW 0x02                                                                                                                           | Cycles:                   | 1                                                                                                                                            |

|              | Before Instruction                                                                                                                   | Example 1:                | SUBWF REG1,1                                                                                                                                 |

|              | W = 1                                                                                                                                |                           | Before Instruction                                                                                                                           |

|              | C = ?                                                                                                                                |                           | REG1 = 3                                                                                                                                     |

|              | After Instruction                                                                                                                    |                           | W = 2                                                                                                                                        |

|              | W = 1<br>C = 1; result is positive                                                                                                   |                           | C = ?                                                                                                                                        |

| Example 2:   | Before Instruction                                                                                                                   |                           | After Instruction                                                                                                                            |

|              | W = 2                                                                                                                                |                           | REG1 = 1<br>W = 2                                                                                                                            |

|              | C = ?                                                                                                                                |                           | C = 2<br>C = 1; result is positive                                                                                                           |

|              | After Instruction                                                                                                                    | Example 2:                | Before Instruction                                                                                                                           |

|              | W = 0                                                                                                                                |                           | REG1 = 2                                                                                                                                     |

| <b>-</b>     | C = 1; result is zero                                                                                                                |                           | W = 2 $C = ?$                                                                                                                                |

| Example 3:   | Before Instruction                                                                                                                   |                           | After Instruction                                                                                                                            |

|              | W = 3 $C = ?$                                                                                                                        |                           | REG1 = 0                                                                                                                                     |

|              | After Instruction                                                                                                                    |                           | W = 2                                                                                                                                        |

|              | W = 0xFF                                                                                                                             |                           | C = 1; result is zero                                                                                                                        |

|              | C = 0; result is nega-                                                                                                               | Example 3:                | Before Instruction                                                                                                                           |

|              | tive                                                                                                                                 |                           | REG1 = 1<br>W = 2                                                                                                                            |

|              |                                                                                                                                      |                           | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                        |

|              |                                                                                                                                      |                           | After Instruction                                                                                                                            |

|              |                                                                                                                                      |                           | REG1 = 0xEE                                                                                                                                  |

| REG1 | = | 0xFF                  |

|------|---|-----------------------|

| W    | = | 2                     |

| С    | = | 0; result is negative |

# **PIC16C64X & PIC16C66X**

1

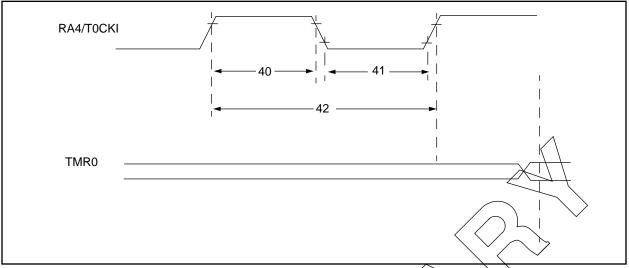

### FIGURE 12-6: TIMER0 CLOCK TIMING

| <b>TABLE 12-7:</b> | TIMER0 CLOCK REQUIREMENTS |

|--------------------|---------------------------|

|--------------------|---------------------------|

|              | _    |                        |                |                 | $\langle \rangle$ |     | <hr/> |                          |

|--------------|------|------------------------|----------------|-----------------|-------------------|-----|-------|--------------------------|

| Param<br>No. | Sym  | Characteris            | stic           | Min             | Турт              | Max | Units | Conditions               |

| 40*          | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY+20       |                   |     | ns    |                          |

|              |      |                        | With Prescaler | 10              | $\rightarrow$     | _   | ns    |                          |

| 41*          | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5TcX + 20     | _                 |     | ns    |                          |

|              |      |                        | With Prescaler |                 |                   |     | ns    |                          |

| 42*          | Tt0P | T0CKI Period           |                | <u>Ter + 40</u> | _                 | —   | ns    | N = prescale             |

|              |      |                        |                | N N             |                   |     |       | value (1, 2, 4,,<br>256) |

\* These parameters are characterized but not tested

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 13.0 DEVICE CHARACTERIZATION INFORMATION

NOT AVAILABLE AT THIS TIME.

© 1996 Microchip Technology Inc.

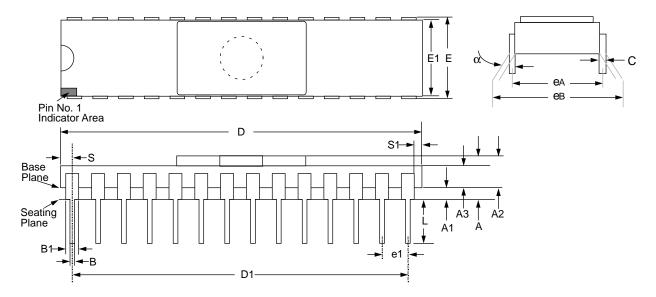

Package Type: 28-Lead Ceramic Side Brazed Dual In-Line with Window (JW) (300 mil)

| Package Group: Ceramic Side Brazed Dual In-Line (CER) |        |             |         |       |        |       |

|-------------------------------------------------------|--------|-------------|---------|-------|--------|-------|

| O makes l                                             |        | Millimeters |         |       | Inches |       |

| Symbol                                                | Min    | Max         | Notes   | Min   | Max    | Notes |

| α                                                     | 0°     | 10°         |         | 0°    | 10°    |       |

| А                                                     | 3.937  | 5.030       |         | 0.155 | 0.198  |       |

| A1                                                    | 1.016  | 1.524       |         | 0.040 | 0.060  |       |

| A2                                                    | 2.921  | 3.506       |         | 0.115 | 0.138  |       |

| A3                                                    | 1.930  | 2.388       |         | 0.076 | 0.094  |       |

| В                                                     | 0.406  | 0.508       |         | 0.016 | 0.020  |       |

| B1                                                    | 1.219  | 1.321       | Typical | 0.048 | 0.052  |       |

| С                                                     | 0.228  | 0.305       | Typical | 0.009 | 0.012  |       |

| D                                                     | 35.204 | 35.916      |         | 1.386 | 1.414  |       |

| D1                                                    | 32.893 | 33.147      | BSC     | 1.295 | 1.305  |       |

| E                                                     | 7.620  | 8.128       |         | 0.300 | 0.320  |       |

| E1                                                    | 7.366  | 7.620       |         | 0.290 | 0.300  |       |

| e1                                                    | 2.413  | 2.667       | Typical | 0.095 | 0.105  |       |

| eA                                                    | 7.366  | 7.874       | BSC     | 0.290 | 0.310  |       |

| eB                                                    | 7.594  | 8.179       |         | 0.299 | 0.322  |       |

| L                                                     | 3.302  | 4.064       |         | 0.130 | 0.160  |       |

| S                                                     | 1.143  | 1.397       |         | 0.045 | 0.055  |       |

| S1                                                    | 0.533  | 0.737       |         | 0.021 | 0.029  |       |

D1 D D/2 PinNo. 1 Indicato<del>r</del> Area REFERERE E1 E Ė/2 8 Places А /11/13° 0° min. Detail B A2 | Datum Plane 0.25 0.08 R min. Å1 . 0-7° with Lead Finish Gauge Plane 0.20 min-0.09/0.2 0.09/0.16 1.00 ref. **▲** b1 Base Metal DETAIL B

Package Type: 44-Lead Thin Plastic Quad Flatpack (PT/TQ) - 10x10x1 mm Body 1.0/0.10 mm Lead Form

|        |       | Packag      | je Group: Plast | ic TQFP |            |       |

|--------|-------|-------------|-----------------|---------|------------|-------|

|        |       | Millimeters |                 |         | Inches     |       |

| Symbol | Min   | Max         | Notes           | Min     | Max        | Notes |

| α      | 0°    | <b>7</b> °  |                 | 0°      | <b>7</b> ° |       |

| А      |       | 1.200       |                 | _       | 0.047      |       |

| A1     | 0.050 | 0.150       |                 | 0.002   | 0.006      |       |

| A2     | 0.950 | 1.050       |                 | 0.037   | 0.041      |       |

| b      | 0.300 | 0.450       |                 | 0.012   | 0.018      |       |

| b1     | 0.300 | 0.400       |                 | 0.012   | 0.016      |       |

| D      | 12.0  | 12.0        | BSC             | 0.472   | 0.0472     | BSC   |

| D1     | 10.0  | 10.0        | BSC             | 0.394   | 0.394      | BSC   |

| Е      | 12.0  | 12.0        | BSC             | 0.472   | 0.472      | BSC   |

| E1     | 10.0  | 10.0        | BSC             | 0.394   | 0.394      | BSC   |

| е      | 0.8   | 0.8         | BSC             | 0.031   | 0.031      | BSC   |

| L      | 0.450 | 0.750       |                 | 0.018   | 0.030      |       |

## APPENDIX A: ENHANCEMENTS

The following are the list of enhancements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14 bits. This allows larger page sizes both in program memory (4K now as opposed to 512 before) and register file (up to 176 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- 3. Data memory paging is slightly redefined. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Six different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers can be invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. Timer0 clock input, T0CKI pin is also a port pin (RA4/T0CKI) and has a TRIS bit.

- 14. FSR is made a full 8-bit register.

- 15. "In-circuit programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR), a Brown-out Reset status bit (BOR), a Parity Error Reset (PER), and a Memory Parity Enable (MPEEN) bit.

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- 18. PORTA inputs are now Schmitt Trigger inputs.

- 19. Brown-out Reset circuitry has been added.

## APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

© 1996 Microchip Technology Inc.

#### E.4 **PIC16C6X Family of Devices**

|                          |                 |                  |                    |                   | Clock                                                                                                                                                                           | Mer           | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          | ľ                     | Peripherals       | erals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |          | Features                                                                                                                                                                                                                         |

|--------------------------|-----------------|------------------|--------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                 |                  | Tol and            |                   | LOCALD ROLL COLORIDA                                                                                                                                                            | T. C. S.      | CANADA CONTRACTOR CONT | Contrate South Anoluties | 100 July 100 July 100 | Sal Shi to and    | All Contract of the series of | - Clarker | S. COL   |                                                                                                                                                                                                                                  |

|                          | 1 SAN           | LUNUUT           | NOPASI             | 4NOL              | JII SAN ERES                                                                                                                                                                    | Lifter Callut | Capital S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A la                     | Alle I                | idnii ai          | × \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Jan Se    | Citcult. | ann antag                                                                                                                                                                                                                        |

| PIC16C62                 | 20              | 2K               |                    | 128               | TMR0,<br>TMR1, TMR2                                                                                                                                                             | 32 1          | SPI/I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          | 7                     | 22                | 3.0-6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Yes       | I        | 28-pin SDIP, SOIC, SSOP                                                                                                                                                                                                          |

| PIC16C62A <sup>(1)</sup> | 20              | 2K               | Ι                  | 128               | TMR0,<br>TMR1, TMR2                                                                                                                                                             | 32 1          | SPI/I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I                        | 7                     | 22                | 2.5-6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Yes       | Yes      | 28-pin SDIP, SOIC, SSOP                                                                                                                                                                                                          |