Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc662-04-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0         | General Description                            | 5    |

|-------------|------------------------------------------------|------|

|             | PIC16C64X & PIC16C66X Device Varieties         |      |

|             | Architectural Overview                         |      |

| 4.0         | Memory Organization                            | .17  |

| 5.0         | I/O Ports                                      | .29  |

| 6.0         | Timer0 Module                                  | . 41 |

| 7.0         | Comparator Module                              | . 47 |

| 8.0         | Voltage Reference Module                       | .53  |

| 9.0         | Special Features of the CPU                    | . 55 |

| 10.0        | Instruction Set Summary                        | .73  |

| 11.0        | Development Support                            | . 87 |

| 12.0        | Electrical Specifications                      | . 91 |

| 13.0        | Device Characterization Information            | 03   |

| 14.0        | Packaging Information 1                        | 105  |

| Appendix    | KA: Enhancements1                              | 15   |

| Appendix    | KB: Compatibility1                             | 115  |

| Appendix    | x C: What's New 1                              | 16   |

| Appendix    | x D: What's Changed1                           | 16   |

| Appendix    | x E: PIC16/17 Microcontrollers 1               | 117  |

| Pin Com     | patibility1                                    | 125  |

| Index       |                                                | 127  |

| List of Ex  | xamples                                        | 129  |

| List of Fig | gures                                          | 129  |

| List of Ta  | ables1                                         | 30   |

| On-Line     | Support                                        | 31   |

|             | Response                                       |      |

| PIC16C6     | 34X & PIC16C66X Product Identification System1 | 135  |

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

# 2.0 PIC16C64X & PIC16C66X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the Product Identification System page at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C64X & PIC16C66X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

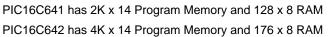

# FIGURE 3-1: PIC16C641/642 BLOCK DIAGRAM

| Name         | Pin #  | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|--------------|--------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 9      | I             | ST/CMOS               | Oscillator crystal input or external clock source input.                                                                                                                                                 |

| OSC2/CLKOUT  | 10     | 0             | _                     | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp     | 1      | I/P           | ST                    | Master clear (reset) input or programming voltage input. This pin is<br>an active low reset to the device.                                                                                               |

|              |        |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 2      | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                 |

| RA1/AN1      | 3      | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                 |

| RA2/AN2/VREF | 4      | I/O           | ST                    | Analog comparator input or VREF output.                                                                                                                                                                  |

| RA3/AN3      | 5      | I/O           | ST                    | Analog comparator input or comparator output.                                                                                                                                                            |

| RA4/T0CKI    | 6      | I/O           | ST                    | Can be selected to be the clock input to the Timer0 timer/counter<br>or a comparator output. Output is open drain type.                                                                                  |

| RA5          | 7      | I/O           | ST                    |                                                                                                                                                                                                          |

|              |        |               |                       | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-ups on all inputs.                                                                                      |

| RB0/INT      | 21     | I/O           | TTL/ST(1)             | RB0 can also be selected as an external interrupt pin.                                                                                                                                                   |

| RB1          | 22     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2          | 23     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3          | 24     | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4          | 25     | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5          | 26     | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6          | 27     | I/O           | TTL/ST(2)             | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 28     | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

|              |        |               |                       | PORTC is a bi-directional I/O port.                                                                                                                                                                      |

| RC0          | 11     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC1          | 12     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC2          | 13     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC3          | 14     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC4          | 15     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC5          | 16     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC6          | 17     | I/O           | ST                    |                                                                                                                                                                                                          |

| RC7          | 18     | I/O           | ST                    |                                                                                                                                                                                                          |

| Vss          | 8,19   | Р             | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd          | 20     | Р             | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend:      |        | output        |                       | = input/output P = power                                                                                                                                                                                 |

|              | I = in | put           |                       | not used ST = Schmitt Trigger input                                                                                                                                                                      |

### TABLE 3-1:PIC16C641/642 PINOUT DESCRIPTION

TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all non-peripheral interrupt sources.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### FIGURE 4-7: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| GIE    | PEIE                                                                                                                                                                                                       | TOIE                                         | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0 | R/W-x<br>RBIF | R= Readable bit                                                                    |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------|---------------|---------------|-------|---------------|------------------------------------------------------------------------------------|--|--|

| bit7   |                                                                                                                                                                                                            |                                              |               |               |               |       | bitO          | W= Writable bit<br>U= Unimplemented bit,<br>read as '0'<br>- n= Value at POR reset |  |  |

| bit 7: | 1 = Enabl                                                                                                                                                                                                  | oal Interrup<br>les all un-r<br>les all inte | nasked in     |               |               |       |               |                                                                                    |  |  |

| bit 6: | <ul> <li>it 6: PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all un-masked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul>                                   |                                              |               |               |               |       |               |                                                                                    |  |  |

| bit 5: | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                                      |                                              |               |               |               |       |               |                                                                                    |  |  |

| bit 4: | 1 = Enabl                                                                                                                                                                                                  | 0/INT Exte<br>les the RB<br>les the RE       | 0/INT exte    | ernal interi  | rupt          |       |               |                                                                                    |  |  |

| bit 3: | 1 = Enabl                                                                                                                                                                                                  | Port Cha<br>les the RB<br>les the RE         | port char     | ige interru   | pt            |       |               |                                                                                    |  |  |

| bit 2: |                                                                                                                                                                                                            |                                              |               |               |               |       |               |                                                                                    |  |  |

| bit 1: | <ul> <li>INTF: RB0/INT External Interrupt Flag bit</li> <li>1 = The RB0/INT external interrupt occurred (must be cleared in software)</li> <li>0 = The RB0/INT external interrupt did not occur</li> </ul> |                                              |               |               |               |       |               |                                                                                    |  |  |

| bit 0: |                                                                                                                                                                                                            |                                              | ne of the     | RB7:RB4       | pins chang    |       | See Section   | 5.2 to clear interrupt)                                                            |  |  |

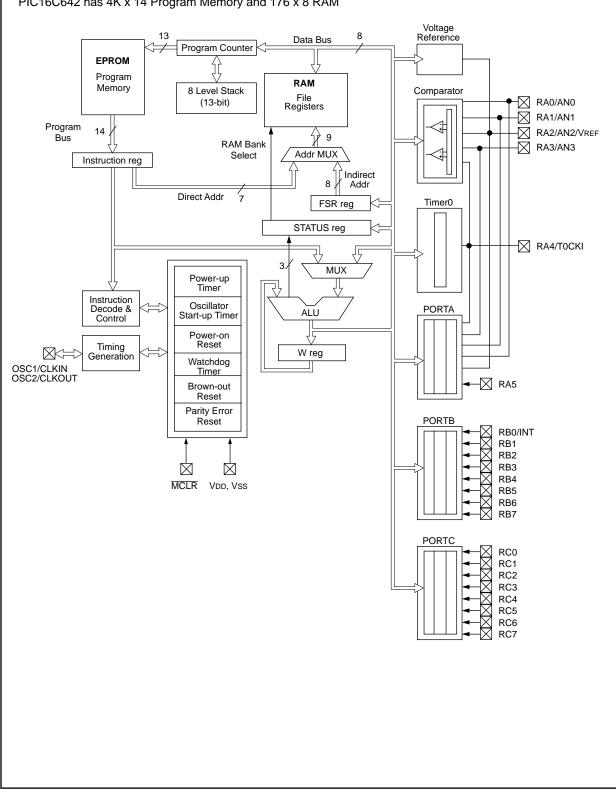

#### 4.5 Indirect Addressing, INDF, and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a nooperation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-12. However, bit IRP is not used in the PIC16C64X & PIC16C66X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

#### EXAMPLE 4-1: INDIRECT ADDRESSING

|           | movlw | 0x20  | ;initialize pointer  |

|-----------|-------|-------|----------------------|

|           | movwf | FSR   | ;to RAM              |

| NEXT      | clrf  | INDF  | ;clear INDF register |

|           | incf  | FSR   | ;inc pointer         |

|           | btfss | FSR,4 | ;all done?           |

|           | goto  | NEXT  | ;no goto next        |

|           |       |       | ;yes continue        |

| CONTINUE: |       |       |                      |

# FIGURE 4-12: DIRECT/INDIRECT ADDRESSING

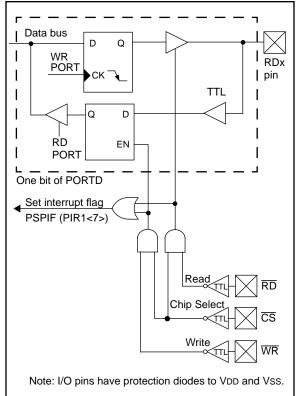

#### 5.7 <u>Parallel Slave Port</u> (PIC16C661 and PIC16C662 only)

PORTD operates as an 8-bit wide parallel slave port, or as a microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin (RE0/ $\overline{RD}$ ) and  $\overline{WR}$  control input pin (RE1/ $\overline{WR}$ ).

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set).

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored since the microprocessor is controlling the direction of data flow.

Input Buffer Full Status Flag bit IBF (TRISE<7>) is set if a received word is waiting to be read by the CPU. Once the PORTD input latch is read, bit IBF is cleared. IBF is a read only status bit. Output Buffer Full Status Flag bit OBF (TRISE<6>) is set if a word written to PORTD latch is waiting to be read by the external bus. Once the PORTD output latch is read by the microprocessor, bit OBF is cleared. Input Buffer Overflow Status flag bit IBOV (TRISE<5>) is set if a second write to the microprocessor port is attempted when the previous word has not been read by the CPU (the first word is retained in the buffer).

When not in Parallel Slave Port mode, bits IBF and OBF are held clear. However, if flag bit IBOV was previously set, it must be cleared in software. An interrupt is generated and latched into flag bit PSPIF (PIR1<7>) when a read or a write operation is completed. Flag bit PSPIF must be cleared by user software. The interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-12: PORTD AND PORTE AS A PARALLEL SLAVE PORT

| Address | Name  | Bit 7                | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|----------------------|-------|-------|---------|-------|--------|--------|--------|--------------------------|---------------------------|

| 08h     | PORTD | PSP7                 | PSP6  | PSP5  | PSP4    | PSP3  | PSP2   | PSP1   | PSP0   | xxxx xxxx                | uuuu uuuu                 |

| 09h     | PORTE |                      | _     | _     | _       | _     | RE2    | RE1    | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF                  | OBF   | IBOV  | PSPMODE | _     | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | CMIF  | _     | _       | _     | _      | _      | _      | 00                       | 00                        |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | CMIE  | _     | —       | —     | _      | _      | _      | 00                       | 00                        |

# TABLE 5-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by the PSP.

Note 1: These bits are reserved on the PIC16C641/642, always maintain these bits clear.

# **PIC16C64X & PIC16C66X**

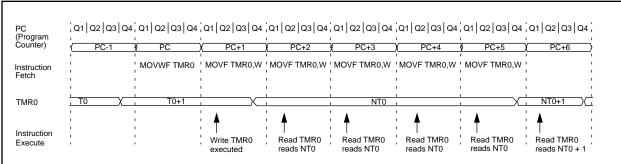

# FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

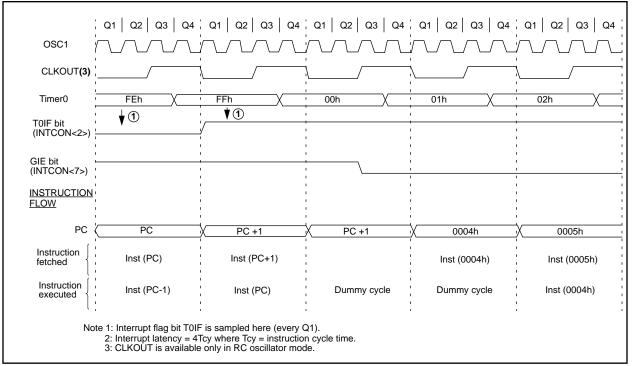

### FIGURE 6-4: TIMER0 INTERRUPT TIMING

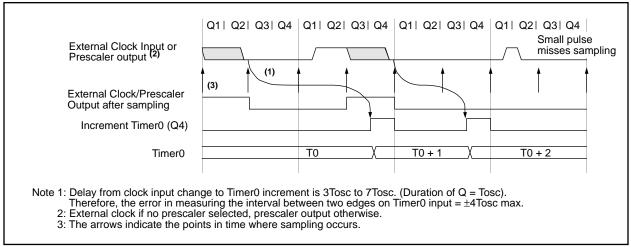

#### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41, and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

NOTES:

#### 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is guaranteed to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-2 and Table 12-3).

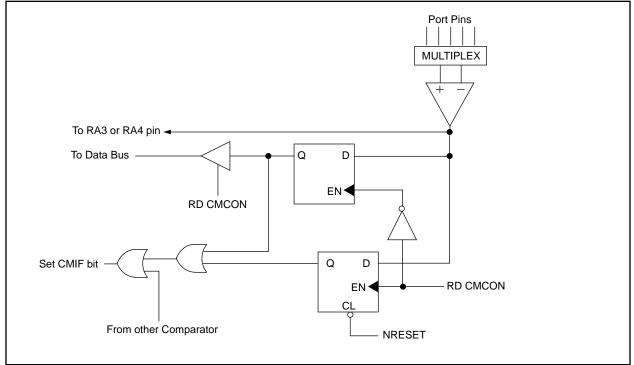

### 7.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When CM2:CM0 = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-4 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORTA register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- **Note 2:** Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 7-4: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 9.4.5 PARITY ERROR RESET (PER)

PIC16C64X & PIC16C66X devices have on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit in the PCON register is set. This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure of the Program Memory. This flag can only be cleared in software or by a POR.

The parity array is user selectable during programming. Bit7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity checking. If left unprogrammed (read as '1'), parity checking is enabled.

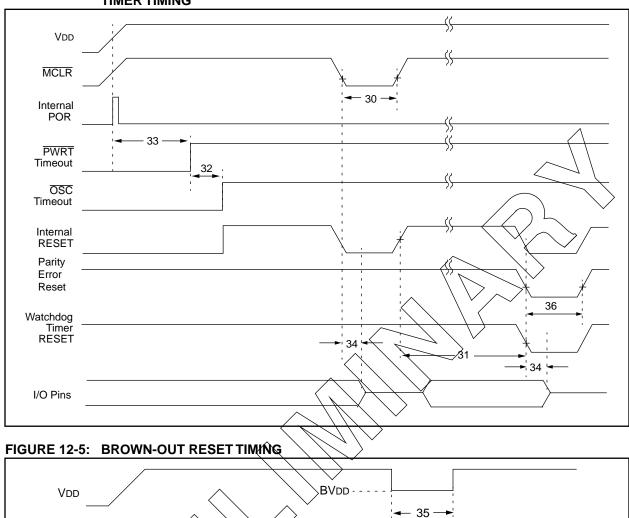

#### 9.4.6 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with the <u>PWRTE</u> bit set (PWRT disabled), there will be no time-out at all. Figure 9-9, Figure 9-10 and Figure 9-11 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-10). This is useful for testing purposes or to synchronize more than one device operating in parallel.

Table 9-5 shows the reset conditions for some special registers, while Table 9-6 shows the reset conditions for all the registers.

#### TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

#### 9.4.7 POWER CONTROL/STATUS REGISTER (PCON)

The power control/status register, PCON (address 8Eh) has four bits. See Figure 4-10 for register.

Bit0 is  $\overline{BOR}$  (Brown-out Reset).  $\overline{BOR}$  is unknown on a Power-on-reset. It must initially be set by the user and checked on subsequent resets to see if  $\overline{BOR} = '0'$ indicating that a Brown-out Reset has occurred. The  $\overline{BOR}$  status bit is a "don't care" bit and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

Bit1 is POR (Power-on Reset). It is cleared on a Power-on Reset and is unaffected otherwise. The user set this bit following a Power-on Reset. On subsequent resets if POR is '0', it will indicate that a Power-on Reset must have occurred.

Bit2 is PER (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

Bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset or interrupt.

| Oscillator Configuration | Powe              | er-up            | Brown-out Reset   | Wake-up    |  |

|--------------------------|-------------------|------------------|-------------------|------------|--|

|                          | <b>PWRTE</b> = 0  | <b>PWRTE</b> = 1 | Brown-out Reset   | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| RC                       | 72 ms             | _                | 72 ms             | —          |  |

#### TABLE 9-6: INITIALIZATION CONDITION FOR REGISTERS

| Register             | Address | Power-on Reset<br>Brown-out Reset<br>Parity Error Reset | MCLR Reset during:<br>- normal operation<br>- SLEEP or<br>WDT Reset | Wake up from SLEEP<br>through:<br>- interrupt<br>- WDT time-out |

|----------------------|---------|---------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|

| W                    | -       | xxxx xxxx                                               | นนนน นนนน                                                           | นนนน นนนน                                                       |

| INDF                 | 00h     | -                                                       | -                                                                   | -                                                               |

| TMR0                 | 01h     | xxxx xxxx                                               | นนนน นนนน                                                           | นนนน นนนน                                                       |

| PCL                  | 02h     | 0000 0000                                               | 0000 0000                                                           | PC + 1 <sup>(2)</sup>                                           |

| STATUS               | 03h     | 0001 1xxx                                               | 000q quuu <sup>(3)</sup>                                            | uuuq quuu <sup>(3)</sup>                                        |

| FSR                  | 04h     | xxxx xxxx                                               | uuuu uuuu                                                           | นนนน นนนน                                                       |

| PORTA                | 05h     | xx 0000                                                 | xu 0000                                                             | uu uuuu                                                         |

| PORTB                | 06h     | xxxx xxxx                                               | นนนน นนนน                                                           | นนนน นนนน                                                       |

| PORTC                | 07h     | xxxx xxxx                                               | นนนน นนนน                                                           | นนนน นนนน                                                       |

| PORTD <sup>(4)</sup> | 08h     | XXXX XXXX                                               | uuuu uuuu                                                           | นนนน นนนน                                                       |

| PORTE <sup>(4)</sup> | 09h     | xxx                                                     | uuu                                                                 | uuu                                                             |

| CMCON                | 1Fh     | 00 0000                                                 | 00 0000                                                             | uu uuuu                                                         |

| PCLATH               | 0Ah     | 0 0000                                                  | 0 0000                                                              | u uuuu                                                          |

| INTCON               | 0Bh     | 0000 000x                                               | 0000 000u                                                           | uuuu uuuu <sup>(1)</sup>                                        |

| PIR1                 | 0Ch     | 00                                                      | 00                                                                  | uu <sup>(1)</sup>                                               |

| OPTION               | 81h     | 1111 1111                                               | 1111 1111                                                           | นนนน นนนน                                                       |

| TRISA                | 85h     | 11 1111                                                 | 11 1111                                                             | uu uuuu                                                         |

| TRISB                | 86h     | 1111 1111                                               | 1111 1111                                                           | นนนน นนนน                                                       |

| TRISC                | 87h     | 1111 1111                                               | 1111 1111                                                           | นนนน นนนน                                                       |

| TRISD <sup>(4)</sup> | 88h     | 1111 1111                                               | 1111 1111                                                           | นนนน นนนน                                                       |

| TRISE <sup>(4)</sup> | 89h     | 0000 -111                                               | 0000 -111                                                           | นนนน -นนน                                                       |

| PIE1                 | 8Ch     | 00                                                      | 00                                                                  | uu                                                              |

| PCON                 | 8Eh     | uqqq                                                    | uuuu                                                                | uuuu                                                            |

| VRCON                | 9Fh     | 000- 0000                                               | 000- 0000                                                           | uuu- uuuu                                                       |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 9-5 for reset value for specific condition.

4: These registers are associated with the Parallel Slave Port and are not implemented on the PIC16C641/642.

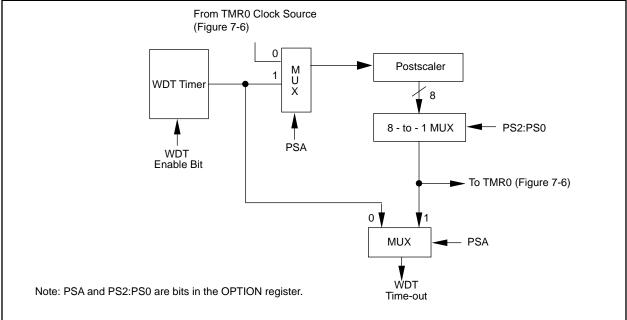

### 9.7 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator which does not require any external components. The block diagram is shown in Figure 9-17. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. This means that the WDT will run, even if the clock on the OSC1 and OSC2 pins has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation, this is known as a WDT wake-up. The WDT can be permanently disabled by clearing configuration bit WDTE (Section 9.1).

#### 9.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out period varies with temperature, VDD and process variations from part to part (see DC specs). If longer time-outs are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT, under software control, by writing to the OPTION register. Thus, time-out periods of up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out (WDT Reset and WDT wake-up).

9.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When the prescaler is assigned to the WDT, always execute a CLRWDT instruction before changing the prescale value, otherwise a WDT reset may occur.

# FIGURE 9-17: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 9-18: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | MPEEN | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 9-1 for details of the operation of these bits.

# **PIC16C64X & PIC16C66X**

| BCF              | Bit Clear                                                                     | f             |            |      |  |  |  |

|------------------|-------------------------------------------------------------------------------|---------------|------------|------|--|--|--|

| Syntax:          | [ label ] B                                                                   | CF f,t        | )          |      |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                             |               |            |      |  |  |  |

| Operation:       | $0 \rightarrow (f < b;$                                                       | >)            |            |      |  |  |  |

| Status Affected: | None                                                                          |               |            |      |  |  |  |

| Encoding:        | 01                                                                            | 00bb          | bfff       | ffff |  |  |  |

| Description:     | Bit 'b' in re                                                                 | gister 'f' is | s cleared. |      |  |  |  |

| Words:           | 1                                                                             |               |            |      |  |  |  |

| Cycles:          | 1                                                                             |               |            |      |  |  |  |

| Example          | BCF                                                                           | FLAG_         | REG, 7     |      |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |               |            |      |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0' then the next<br>instruction is skipped.<br>If bit 'b' is '0' then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a 2 cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                            |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                                                                                                       |  |  |  |  |  |

| BSF              | Bit Set f                                                                     |               |        |      |  |  |

|------------------|-------------------------------------------------------------------------------|---------------|--------|------|--|--|

| Syntax:          | [ <i>label</i> ] B                                                            | SF f,b        |        |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |               |        |      |  |  |

| Operation:       | $1 \rightarrow (f < b;$                                                       | >)            |        |      |  |  |

| Status Affected: | None                                                                          |               |        |      |  |  |

| Encoding:        | 01                                                                            | 01bb          | bfff   | ffff |  |  |

| Description:     | Bit 'b' in re                                                                 | gister 'f' is | s set. |      |  |  |

| Words:           | 1                                                                             |               |        |      |  |  |

| Cycles:          | 1                                                                             |               |        |      |  |  |

| Example          | BSF                                                                           | FLAG_F        | REG, 7 |      |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |               |        |      |  |  |

# **PIC16C64X & PIC16C66X**

| CLRWDT           | Clear Watchdog Timer                                                                                                                                    |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$      |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                       |  |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set.                        |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                       |  |  |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                  |  |  |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = $1$<br>PD = $1$                       |  |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                            |  |  |  |  |  |  |

| Syntax:          | [label] COMF f,d                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                      |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>W. If 'd' is 1 the result is stored back in<br>register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                       |  |  |  |  |  |  |

| - ·              |                                                                                                                                                         |  |  |  |  |  |  |

| 1          |           |      |      |

|------------|-----------|------|------|

| COMF       | REC       | 31,0 |      |

| Before In  | struction | 1    |      |

|            | REG1      | =    | 0x13 |

| After Inst | ruction   |      |      |

|            | REG1      | =    | 0x13 |

|            | W         | =    | 0xEC |

| DECF             | Decrement f                                                                                                                        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                          |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                  |  |  |  |  |  |

|                  | d ∈ [0,1]                                                                                                                          |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                  |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                  |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                  |  |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                        |  |  |  |  |  |

|                  | Before Instruction                                                                                                                 |  |  |  |  |  |

|                  | CNT = 0x01 $Z = 0$                                                                                                                 |  |  |  |  |  |

|                  | Z = 0<br>After Instruction                                                                                                         |  |  |  |  |  |

|                  | CNT = 0x00                                                                                                                         |  |  |  |  |  |

|                  | Z = 1                                                                                                                              |  |  |  |  |  |

|                  |                                                                                                                                    |  |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                             |  |  |  |  |  |

| Syntax:          | [label] DECFSZ f,d                                                                                                                 |  |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded. A<br>NOP is executed instead making it a two<br>cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                  | $\begin{array}{rcl} Before \ Instruction \\ PC &= & address \ {}_{HERE} \\ After \ Instruction \\ CNT &= & CNT - 1 \\ if \ CNT &= & 0, \\ PC &= & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC &= & address \ HERE + 1 \\ \end{array}$                                                                                       |  |  |  |  |  |

Cycles:

Example

# FIGURE 12-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, AND POWER-UP TIMER TIMING

TABLE 12-6:

RESET, WATCHOOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Мах | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | Tmcl  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | -     | Tosc = OSC1 period        |

| 33*              | Towrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | TIOZ  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | —        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | —        | —   | μs    | Vdd ≤ Bvdd (D005)         |

| 36               | TPER  | Parity Error Reset                                     | —   | TBD      | _   | μs    |                           |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

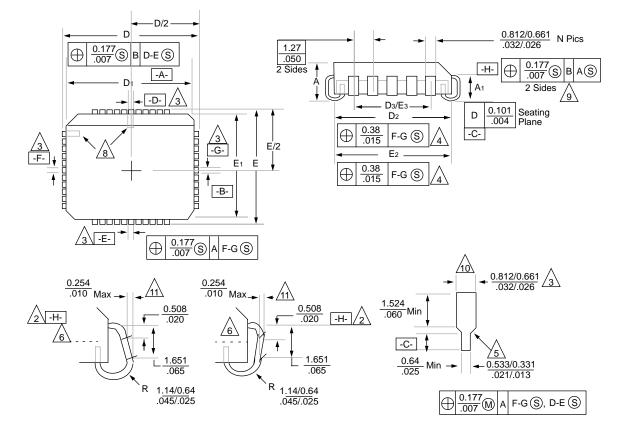

### Package Type: 44-Lead Plastic Leaded Chip Carrier (L) - Square

| Package Group: Plastic Leaded Chip Carrier (PLCC) |        |             |       |       |        |       |  |

|---------------------------------------------------|--------|-------------|-------|-------|--------|-------|--|

|                                                   |        | Millimeters |       |       | Inches |       |  |

| Symbol                                            | Min    | Мах         | Notes | Min   | Max    | Notes |  |

| А                                                 | 4.191  | 4.572       |       | 0.165 | 0.180  |       |  |

| A1                                                | 2.413  | 2.921       |       | 0.095 | 0.115  |       |  |

| D                                                 | 17.399 | 17.653      |       | 0.685 | 0.695  |       |  |

| D1                                                | 16.510 | 16.663      |       | 0.650 | 0.656  |       |  |

| D2                                                | 15.494 | 16.002      |       | 0.610 | 0.630  |       |  |

| D3                                                | 12.700 | 12.700      | BSC   | 0.500 | 0.500  | BSC   |  |

| E                                                 | 17.399 | 17.653      |       | 0.685 | 0.695  |       |  |

| E1                                                | 16.510 | 16.663      |       | 0.650 | 0.656  |       |  |

| E2                                                | 15.494 | 16.002      |       | 0.610 | 0.630  |       |  |

| E3                                                | 12.700 | 12.700      | BSC   | 0.500 | 0.500  | BSC   |  |

| CP                                                | —      | 0.102       |       |       | 0.004  |       |  |

| LT                                                | 0.203  | 0.381       |       | 0.008 | 0.015  |       |  |

# **APPENDIX C: WHAT'S NEW**

New Data Sheet

# APPENDIX D: WHAT'S CHANGED

New Data Sheet

# **APPENDIX E: PIC16/17 MICROCONTROLLERS**

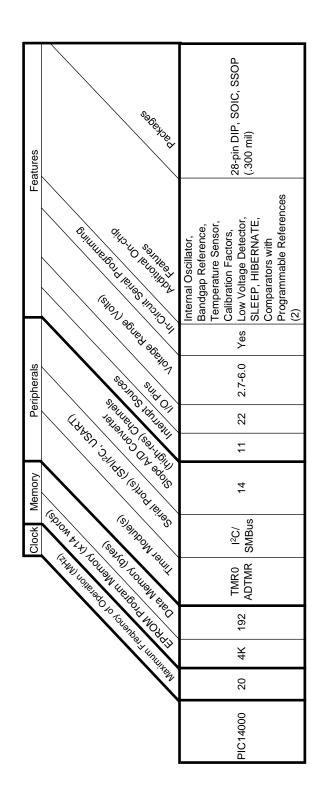

# E.1 PIC14000 Devices