Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 176 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                    |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                   |

| Supplier Device Package    | 40-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc662-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

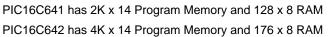

#### FIGURE 3-1: PIC16C641/642 BLOCK DIAGRAM

PIC16C642/662 PROGRAM

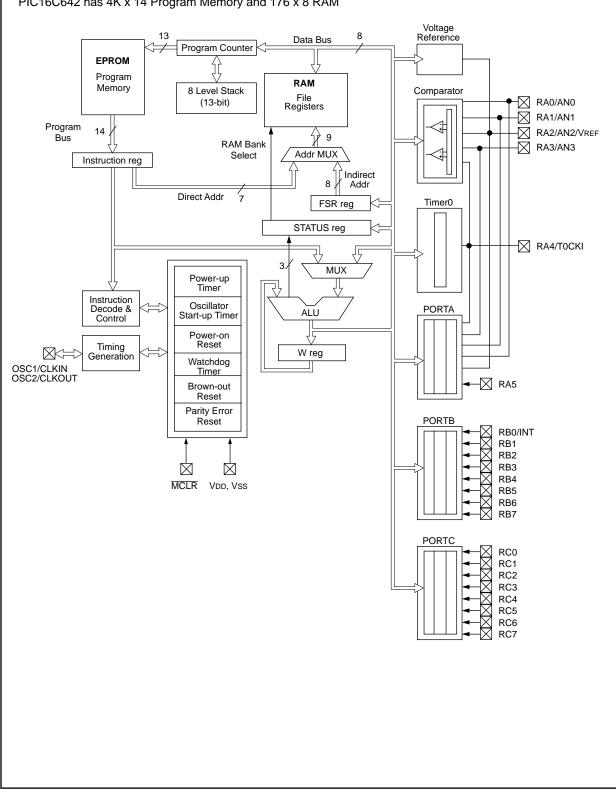

FIGURE 4-2:

#### 4.0 MEMORY ORGANIZATION

#### 4.1 Program Memory Organization

The PIC16C64X & PIC16C66X have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16C641 and PIC16C661 only the first 2K x 14 (0000h - 07FFh) is physically implemented. For the PIC16C642 and PIC16C662 only the first 4K x 14 (0000h - 0FFh) is physically implemented. Accessing a location above the 2K or 4K boundary will cause a wrap-around. The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1 and Figure 4-2). See Section 4.4 for Program Memory paging.

#### FIGURE 4-1: PIC16C641/661 PROGRAM MEMORY MAP AND STACK

### MEMORY MAP AND STACK PC<12:0> CALL, RETURN 13 RETFIE, RETLW Stack Level 1 Stack Level 2 Stack Level 8 **Reset Vector** 0000h Memory Space Interrupt Vector 0004h 0005h On-chip Program Memory User Page0 07FFh 0800h **On-chip Program** Memory Page1 0FFFh 1000h 1FFFh TEST 2000h Configuration Word 2007h TEST 3FFFh

#### © 1996 Microchip Technology Inc.

#### 4.2 Data Memory Organization

The data memory (Figure 4-4) is partitioned into two banks which contain the general purpose registers and the special function registers. Bank 0 is selected when bit RP0 (STATUS<5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations A0h-EFh (Bank 1) are general purpose registers implemented as static RAM. Some special function registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $176 \times 8$  for the PIC16C642/662, and 128 x8 for the PIC16C641/661. Each is accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

#### FIGURE 4-3: PIC16C641/661 DATA MEMORY MAP

|                  | MEMORY                                                     |                      |                 |

|------------------|------------------------------------------------------------|----------------------|-----------------|

| File<br>Address  | 5                                                          |                      | File<br>Address |

| 00h              | INDF <sup>(1)</sup>                                        | INDF <sup>(1)</sup>  | 80h             |

| 01h              | TMR0                                                       | OPTION               | 81h             |

| 02h              | PCL                                                        | PCL                  |                 |

| 03h              | STATUS                                                     | STATUS               |                 |

| 04h              | FSR                                                        | FSR                  |                 |

| 05h              | PORTA                                                      | TRISA                | 85h             |

| 06h              | PORTB                                                      | TRISB                | 86h             |

| 07h              | PORTC                                                      | TRISC                | 87h             |

| 08h              | PORTD <sup>(2)</sup>                                       | TRISD <sup>(2)</sup> | 88h             |

| 09h              | PORTE <sup>(2)</sup>                                       | TRISE <sup>(2)</sup> | 89h             |

| 0Ah              | PCLATH                                                     | PCLATH               | 8Ah             |

| 0Bh              | INTCON                                                     | INTCON               | 8Bh             |

| 0Ch              | PIR1                                                       | PIE1                 | 8Ch             |

| 0Dh              |                                                            |                      | 8Dh             |

| 0Eh              |                                                            | PCON                 | 8Eh             |

| 0Fh              |                                                            |                      | 8Fh             |

| 10h              |                                                            |                      | 90h             |

| 11h              |                                                            |                      | 91h             |

| 12h              |                                                            |                      | 92h             |

| 13h              |                                                            |                      | 93h             |

| 14h              |                                                            |                      | 94h             |

| 15h              |                                                            |                      | 95h             |

| 16h              |                                                            |                      | 96h             |

| 17h              |                                                            |                      | 97h             |

| 18h              |                                                            |                      | 98h             |

| 19h              |                                                            |                      | 99h             |

| 1Ah<br>1Ph       |                                                            |                      | 9Ah<br>9Bh      |

| 1Bh<br>1Ch       |                                                            |                      | 960<br>9Ch      |

| 1Dh              |                                                            |                      | 90h             |

| 1Eh              |                                                            |                      | 9Eh             |

| 1Fh              | CMCON                                                      | VRCON                | 9Eh             |

| 20h              | CIVICOIN                                                   | VICON                |                 |

| 2011             | General<br>Purpose                                         | General<br>Purpose   | A0h             |

|                  | Register                                                   | Register             | BFh             |

|                  |                                                            |                      | C0h             |

|                  |                                                            |                      | EFh             |

|                  |                                                            | Mapped               | F0h             |

|                  |                                                            | in Page 0            |                 |

| 7Fh <sup>l</sup> | Bank 0                                                     | Bank 1               | _ FFh           |

| Note 1: N        | lemented data mer<br>lot a physical reg<br>lot implemented | gister.              |                 |

|                  |                                                            |                      |                 |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all non-peripheral interrupt sources.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### FIGURE 4-7: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| GIE    | PEIE      | TOIE                                                                                                                  | R/W-0<br>INTE | R/W-0<br>RBIE | R/W-0<br>T0IF | R/W-0     | R/W-x<br>RBIF | R= Readable bit                                                                    |  |  |  |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|-----------|---------------|------------------------------------------------------------------------------------|--|--|--|

| bit7   |           |                                                                                                                       |               |               |               |           | bitO          | W= Writable bit<br>U= Unimplemented bit,<br>read as '0'<br>- n= Value at POR reset |  |  |  |

| bit 7: | 1 = Enabl | oal Interrup<br>les all un-r<br>les all inte                                                                          | nasked in     |               |               |           |               |                                                                                    |  |  |  |

| bit 6: | 1 = Enabl | ripheral Int<br>les all un-r<br>les all per                                                                           | nasked pe     | eripheral ir  | nterrupts     |           |               |                                                                                    |  |  |  |

| bit 5: | 1 = Enabl | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt |               |               |               |           |               |                                                                                    |  |  |  |

| bit 4: | 1 = Enabl | 0/INT Exte<br>les the RB<br>les the RE                                                                                | 0/INT exte    | ernal interi  | rupt          |           |               |                                                                                    |  |  |  |

| bit 3: | 1 = Enabl | Port Cha<br>les the RB<br>les the RE                                                                                  | port char     | ige interru   | pt            |           |               |                                                                                    |  |  |  |

| bit 2: | 1 = TMRC  | R0 Overflo<br>) register o<br>) register o                                                                            | verflowed     | l (must be    | cleared in    | software) |               |                                                                                    |  |  |  |

| bit 1: | 1 = The R | 0/INT Exte<br>8B0/INT ex<br>8B0/INT ex                                                                                | ternal inte   | errupt occu   | urred (must   | be cleare | d in softwar  | e)                                                                                 |  |  |  |

| bit 0: |           |                                                                                                                       | ne of the     | RB7:RB4       | pins chang    |           | See Section   | 5.2 to clear interrupt)                                                            |  |  |  |

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset (POR), an external  $\overline{\text{MCLR}}$  reset, WDT reset, Brown-out Reset (BOR), and Parity Error Reset (PER). The PCON register also contains a status bit, MPEEN, which reflects the value of the MPEEN bit in Configuration Word. See Table 9-4 for status of these bits on various resets.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is cleared, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by programming the BODEN bit in the Configuration word).

#### FIGURE 4-10: PCON REGISTER (ADDRESS 8Eh)

| R-U                                                                                                | U-0                                                      | U-0        | U-0               | U-0        | R/W-1                    | R/W-0       | R/W-u       |                   |  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------|-------------------|------------|--------------------------|-------------|-------------|-------------------|--|

| MPEEN                                                                                              |                                                          | _          | _                 | —          | PER                      | POR         | BOR         | R= Readable bit   |  |

| bit7<br>bit0<br>W= Writable bit<br>U= Unimplemented bit,<br>read as '0'<br>- n= Value at POR reset |                                                          |            |                   |            |                          |             |             |                   |  |

| bit 7:                                                                                             | MPEEN: N<br>Reflects th                                  |            |                   |            | Status bit<br>d bit, MPE | ΞN          |             |                   |  |

| bit 6-3:                                                                                           | Unimplen                                                 | nented: R  | ead as '0'        |            |                          |             |             |                   |  |

| bit 2:                                                                                             | <b>PER</b> : Men<br>1 = No err<br>0 = Program (must be s | or occurre | ed<br>ry fetch pa | rity error |                          | occurs)     |             |                   |  |

| bit 1:                                                                                             | <b>POR</b> : Pow<br>1 = No Po<br>0 = A Pow               | wer-on Re  | eset occur        | red        | e set in sof             | tware afte  | r a Power-c | on Reset occurs)  |  |

| bit 0:                                                                                             | <b>BOR</b> : Bro<br>1 = No Bro<br>0 = A Brov             | own-out R  | eset occu         | rred       | be set in so             | ftware afte | er a Brown- | out Reset occurs) |  |

#### FIGURE 5-10: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

#### TABLE 5-9: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                      |

|--------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode:<br>RD                                                                                                |

|        |      |                       | 1 = Not a read operation                                                                                                                                                      |

|        |      |                       | 0 = Read operation. Reads PORTD register (if chip selected)                                                                                                                   |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

#### TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|--------|--------|--------|--------------------------|---------------------------|

| 09h     | PORTE | —     | _     | —     | —       |       | RE2    | RE1    | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

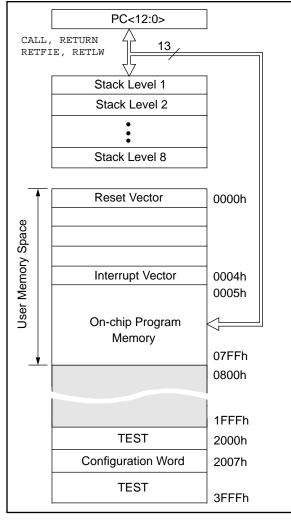

#### 5.6 I/O Programming Considerations

#### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (e.g., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential read-modify-write instructions on an I/O port.

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ;PORTB<7:6> have external pull-ups and are ;not connected to other circuitry

|   | ;               |   | PORT latch | PORT pins |

|---|-----------------|---|------------|-----------|

| , | ;               |   |            |           |

|   | BCF PORTB, 7    | ; | 01pp pppp  | 11pp pppp |

|   | BCF PORTB, 6    | ; | 10pp pppp  | 11pp pppp |

|   | BCF STATUS, RP1 | ; |            |           |

|   | BSF STATUS, RPO | ; |            |           |

|   | BCF TRISB, 7    | ; | 10pp pppp  | 11pp pppp |

|   | BCF TRISB, 6    | ; | 10pp pppp  | 10pp pppp |

|   |                 |   |            |           |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-11). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

|                         | Q1  Q2  Q3  Q4    | Q1  Q2  Q3  Q4                   | Q1 Q2 Q3 Q4                             | Q1  Q2  Q3  Q4 | Note:                                                                                        |

|-------------------------|-------------------|----------------------------------|-----------------------------------------|----------------|----------------------------------------------------------------------------------------------|

| PC                      | X PC              | PC + 1                           | PC + 2                                  | PC + 3         | This example shows a write to PORTB                                                          |

| Instruction fetched     |                   | MOVF PORTB,W                     | NOP                                     | NOP            | followed by a read from PORTB.                                                               |

|                         | write to<br>PORTB | 1                                |                                         |                | Note that:                                                                                   |

| RB7:RB0                 |                   | 1                                | X                                       | · · · · · ·    | data setup time = (0.25TCY - TPD)                                                            |

| ,<br>,<br>,             |                   | 1<br>1<br>1<br>1                 | Port pin<br>sampled here                |                | where Tcy = instruction cycle<br>TPD = propagation delay                                     |

| Instruction<br>executed |                   | MOVWF PORTB<br>write to<br>PORTB | TPD                                     | NOP            | Therefore, at higher clock frequencies,<br>a write followed by a read may be<br>problematic. |

| 1                       |                   | 1                                | 1 I I I I I I I I I I I I I I I I I I I |                |                                                                                              |

#### FIGURE 5-11: SUCCESSIVE I/O OPERATION

#### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must be followed even if the WDT is disabled.

### EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

|        |             |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2.

### EXAMPLE 6-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

#### TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                              | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-----------------------------------|-------|--------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------|

| 01h     | 01h TMR0 Timer0 module's register |       |        |        |        |        |        |        |        |                          | uuuu uuuu                 |

| 0Bh/8Bh | INTCON                            | GIE   | PEIE   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h     | OPTION                            | RBPU  | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h     | TRISA                             | —     | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 7.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with pins RA0 through RA4. The on-chip Voltage Reference (Section 8.0) can also be an input to the comparators.

The CMCON register, shown in Figure 7-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 7-2.

٦

#### FIGURE 7-1: CMCON REGISTER (ADDRESS 1Fh)

| R-0      | R-0              | U-0       | U-0      | R/W-0      | R/W-0      | R/W-0    | R/W-0    |                            |

|----------|------------------|-----------|----------|------------|------------|----------|----------|----------------------------|

| C20U1    | C10UT            | _         | _        | CIS        | CM2        | CM1      | CM0      | R =Readable bit            |

| bit7     | •                |           |          |            |            |          | bit0     | W =Writable bit            |

|          |                  |           |          |            |            |          |          | U =Unimplemented bit, read |

|          |                  |           |          |            |            |          |          | as '0'                     |

|          |                  |           |          |            |            |          |          | - n =Value at POR reset    |

| bit 7:   | C2OUT: Co        |           |          | out        |            |          |          |                            |

|          | $1 = C2 V_{IN+}$ |           |          |            |            |          |          |                            |

|          | 0 = C2 VIN+      | < C2 Vi   | N—       |            |            |          |          |                            |

| bit 6:   | C1OUT: Co        | •         | •        | out        |            |          |          |                            |

|          | 1 = C1 VIN+      |           |          |            |            |          |          |                            |

|          | 0 = C1 VIN+      | < C1 Vi   | N—       |            |            |          |          |                            |

| bit 5-4: | Unimpleme        | ented: R  | ead as   | '0'        |            |          |          |                            |

| bit 3:   | CIS: Compa       | arator In | put Swit | ch         |            |          |          |                            |

|          | When CM2:        | CM0: =    | 001:     |            |            |          |          |                            |

|          | Then:            |           |          |            |            |          |          |                            |

|          | 1 = C1 VIN-      | connec    | ts to RA | 3          |            |          |          |                            |

|          | 0 = C1 VIN-      | connec    | ts to RA | 0          |            |          |          |                            |

|          | When CM2:        | CM0 =     | 010:     |            |            |          |          |                            |

|          | Then:            |           |          |            |            |          |          |                            |

|          | 1 = C1 VIN-      | connec    | ts to RA | .3         |            |          |          |                            |

|          | C2 VIN-          | connec    | ts to RA | 2          |            |          |          |                            |

|          | 0 = C1 VIN-      | connec    | ts to RA | 0          |            |          |          |                            |

|          | C2 VIN-          | connec    | ts to RA | .1         |            |          |          |                            |

| bit 2-0: | CM2:CM0:         | Compar    | ator mo  | de         |            |          |          |                            |

|          | Figure 7-2 s     | howe th   |          | arator mad | loc and CM | DOCMO HI | aattinga |                            |

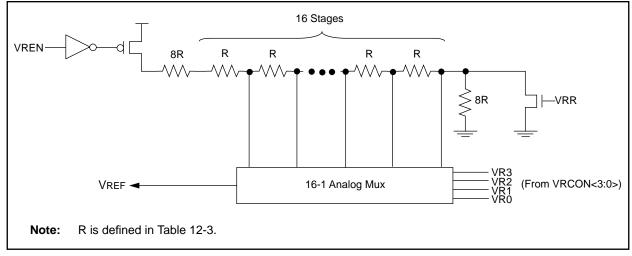

#### 8.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference module is not being used. The VRCON register, shown in Figure 8-1, controls the operation of the Voltage Reference Module. The block diagram is given in Figure 8-2.

#### FIGURE 8-1: VRCON REGISTER (ADDRESS 9Fh)

| R/W-0    | R/W-0                                                                                              | R/W-0      | U-0      | R/W-0         | R/W-0      | R/W-0 | R/W-0 | ¬                                                                                  |  |

|----------|----------------------------------------------------------------------------------------------------|------------|----------|---------------|------------|-------|-------|------------------------------------------------------------------------------------|--|

| VREN     | VROE                                                                                               | VRR        |          | VR3           | VR2        | VR1   | VR0   | R =Readable bit                                                                    |  |

| bit7     |                                                                                                    |            |          |               |            |       | bit0  | W =Writable bit<br>U =Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |  |

| bit 7:   | VREN: VRE<br>1 = VREF ci<br>0 = VREF ci                                                            | rcuit powe |          | n, no Idd     | drain      |       |       |                                                                                    |  |

| bit 6:   | VROE: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |            |          |               |            |       |       |                                                                                    |  |

| bit 5:   | <b>VRR:</b> VREF<br>1 = Low Ra<br>0 = High Ra                                                      | inge       | lection  |               |            |       |       |                                                                                    |  |

| bit 4:   | Unimplem                                                                                           | ented: Rea | ad as '0 | ı             |            |       |       |                                                                                    |  |

| bit 3-0: | VR3:VR0:                                                                                           | VREF value | selecti  | on $0 \le VR$ | 3:VR0 ≤ 15 | 5     |       |                                                                                    |  |

|          | When: VRF<br>Then: VREF                                                                            |            | R0/ 24)  | • Vdd         |            |       |       |                                                                                    |  |

|          | When: VRF<br>Then: VREF                                                                            |            | D + (VI  | R3:VR0/ 32    | 2) • Vdd   |       |       |                                                                                    |  |

# 9.0 SPECIAL FEATURES OF THE CPU

What sets apart a microcontroller from other processors are special circuits to deal with the needs of real-time applications. The PIC16C64X & PIC16C66X families have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. Oscillator selection

- 2. Resets

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-up Timer (OST) Brown-out Reset (BOR) Parity Error Reset (PER)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16C64X & PIC16C66X has a Watchdog Timer which is enabled by a configuration bit (WDTE). It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. Circuitry has been provided for checking program memory parity with a reset when an error is indicated. There is also circuitry to reset the device if a brown-out occurs which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## **PIC16C64X & PIC16C66X**

| GOTO             | Unconditional Branch                                                                                                                                                                          | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0 >$                                                                                                                                                                   |                  | d ∈ [0,1]                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                           | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                          | Status Affected: | None                                                                                                                                                                                                                                                        |  |  |  |  |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                             | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                           |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                             |                  | A NOP is executed instead making it a two cycle instruction.                                                                                                                                                                                                |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                                                           |  |  |  |  |

| Example          | GOTO THERE                                                                                                                                                                                    | Cycles:          | 1(2)                                                                                                                                                                                                                                                        |  |  |  |  |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                       | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                                                                               |                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                     |  |  |  |  |

| INCF             | Increment f                                                                                                                                                         |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                               |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                     |  |  |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                     |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                     |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                            |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                              |  |  |  |  |  |  |  |

After Instruction CNT =

if CNT=

= if CNT≠

=

PC

PC

CNT + 1

address CONTINUE

address HERE +1

0,

0,

NOTES:

## **PIC16C64X & PIC16C66X**

|       |                                                                              | Standard Operating Conditions (    | unless othe          | rwise | stated)    |      |                                    |  |  |  |

|-------|------------------------------------------------------------------------------|------------------------------------|----------------------|-------|------------|------|------------------------------------|--|--|--|

|       | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial, |                                    |                      |       |            |      |                                    |  |  |  |

|       |                                                                              |                                    | $\leq$ TA $\leq$ +70 |       |            |      |                                    |  |  |  |

|       |                                                                              | -40°C                              | $\leq$ TA $\leq$ +12 |       | automotive |      |                                    |  |  |  |

|       | Operating voltage VDD range as described in DC spec Section 12.1 and 12.2    |                                    |                      |       |            |      |                                    |  |  |  |

| Param | Sym                                                                          | Characteristic                     | Min                  | Тур   | Max        | Unit | Conditions                         |  |  |  |

| No.   | -                                                                            |                                    |                      | t     |            |      |                                    |  |  |  |

|       | Vон                                                                          | Output High Voltage <sup>(3)</sup> |                      |       |            |      |                                    |  |  |  |

| D090  |                                                                              | I/O ports (Except RA4)             | Vdd-0.7              | -     | -          | V    | Юн = -3.0 mA, VpD = 4.5V,          |  |  |  |

|       |                                                                              |                                    |                      |       |            |      | -40° to +85°C                      |  |  |  |

|       |                                                                              |                                    | Vdd-0.7              | -     | -          | V    | Юн = -2.5 mA, \                    |  |  |  |

|       |                                                                              |                                    |                      |       |            |      | $VDD = 4.5V, \mp 125^{\circ}C$     |  |  |  |

| D092  |                                                                              | OSC2/CLKOUT                        | VDD-0.7              | -     | -          | V    | Юн = -1.3 mA, VDD=4.5V,            |  |  |  |

|       |                                                                              |                                    |                      |       |            |      | -40° to +85°C                      |  |  |  |

|       |                                                                              |                                    | Vdd-0.7              | -     | -          | V <  | $10 \mu = -1.0 \text{ mA},$        |  |  |  |

|       |                                                                              | (RC only)                          |                      |       |            |      | VDD = 4,5∀, +125°C                 |  |  |  |

|       |                                                                              | Capacitive Loading Specs           |                      |       |            |      |                                    |  |  |  |

|       |                                                                              | on Output Pins                     |                      |       |            |      |                                    |  |  |  |

| D100  | COSC2                                                                        | OSC2 pin                           | -                    | -     | 15 \       | PF,  | In XT, HS and LP modes when        |  |  |  |

|       |                                                                              |                                    |                      |       |            |      | external clock used to drive OSC1. |  |  |  |

| D101  | Сю                                                                           | All I/O pins/OSC2 (in RC mode)     | -                    | -     | 50         |      |                                    |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger nput. It is not recommended that the PIC16C64X & PIC16C66X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin

## **PIC16C64X & PIC16C66X**

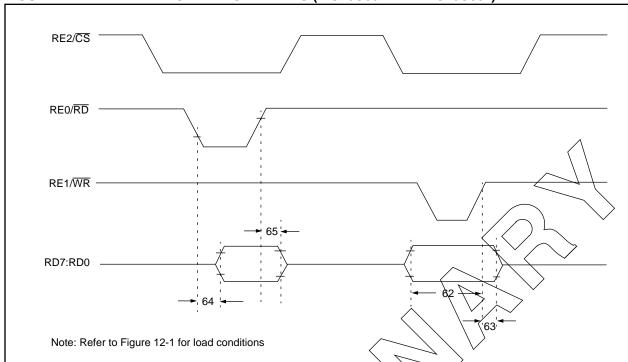

#### FIGURE 12-7: PARALLEL SLAVE PORT TIMING (PIC16C661 AND PIC16C662)

#### TABLE 12-8: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C661 AND PIC16C662)

| Parameter<br>No. | Sym      | Characteristic                                                            | Min | Тур† | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 62               | TdtV2wrH | Data in valid before WR1 or C81 (setup time)                              | 20  | —    | _   | ns    |            |

| 63*              | TwrH2dtl | WR1 or CS1 to data-in invalid (hold time) PIC16C66X                       | 20  |      |     | ns    |            |

|                  |          | PIC16LC66X                                                                | 35  | —    | —   | ns    |            |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data-out valid | _   | _    | 80  | ns    |            |

| 65               | TrdH2dtl | $\overline{RD}$ for $\overline{CS}$ to data out invalid                   | 10  | _    | 30  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

#### E1 Е С Pin No. 1 еΑ Indicator ев Area D $\downarrow$ Base S S1► -Plane Seating Plane B1 À1АЗ Ά A2 e1 В D1

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |        |         |        |       |         |  |  |

|--------------------------------------------------|-------------|--------|---------|--------|-------|---------|--|--|

|                                                  | Millimeters |        |         | Inches |       |         |  |  |

| Symbol                                           | Min         | Max    | Notes   | Min    | Max   | Notes   |  |  |

| α                                                | 0°          | 10°    |         | 0°     | 10°   |         |  |  |

| А                                                | 4.318       | 5.715  |         | 0.170  | 0.225 |         |  |  |

| A1                                               | 0.381       | 1.778  |         | 0.015  | 0.070 |         |  |  |

| A2                                               | 3.810       | 4.699  |         | 0.150  | 0.185 |         |  |  |

| A3                                               | 3.810       | 4.445  |         | 0.150  | 0.175 |         |  |  |

| В                                                | 0.355       | 0.585  |         | 0.014  | 0.023 |         |  |  |

| B1                                               | 1.270       | 1.651  | Typical | 0.050  | 0.065 | Typical |  |  |

| С                                                | 0.203       | 0.381  | Typical | 0.008  | 0.015 | Typical |  |  |

| D                                                | 51.435      | 52.705 |         | 2.025  | 2.075 |         |  |  |

| D1                                               | 48.260      | 48.260 | BSC     | 1.900  | 1.900 | BSC     |  |  |

| E                                                | 15.240      | 15.875 |         | 0.600  | 0.625 |         |  |  |

| E1                                               | 12.954      | 15.240 |         | 0.510  | 0.600 |         |  |  |

| e1                                               | 2.540       | 2.540  | BSC     | 0.100  | 0.100 | BSC     |  |  |

| eA                                               | 14.986      | 16.002 | Typical | 0.590  | 0.630 | Typical |  |  |

| eB                                               | 15.240      | 18.034 |         | 0.600  | 0.710 |         |  |  |

| L                                                | 3.175       | 3.810  |         | 0.125  | 0.150 |         |  |  |

| S                                                | 1.016       | 2.286  |         | 0.040  | 0.090 |         |  |  |

| S1                                               | 0.381       | 1.778  |         | 0.015  | 0.070 |         |  |  |

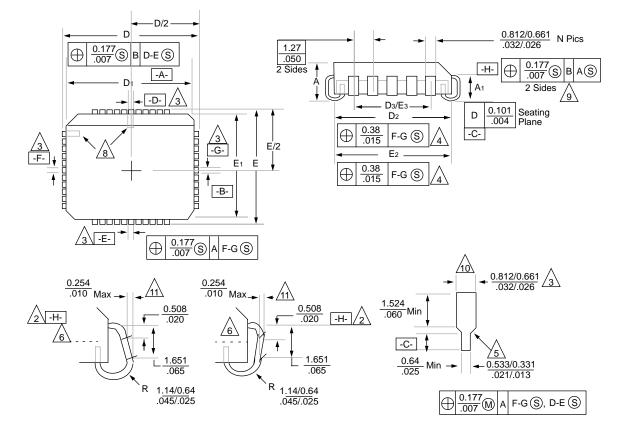

#### Package Type: 44-Lead Plastic Leaded Chip Carrier (L) - Square

| Package Group: Plastic Leaded Chip Carrier (PLCC) |             |        |       |        |       |       |  |  |

|---------------------------------------------------|-------------|--------|-------|--------|-------|-------|--|--|

|                                                   | Millimeters |        |       | Inches |       |       |  |  |

| Symbol                                            | Min         | Max    | Notes | Min    | Max   | Notes |  |  |

| А                                                 | 4.191       | 4.572  |       | 0.165  | 0.180 |       |  |  |

| A1                                                | 2.413       | 2.921  |       | 0.095  | 0.115 |       |  |  |

| D                                                 | 17.399      | 17.653 |       | 0.685  | 0.695 |       |  |  |

| D1                                                | 16.510      | 16.663 |       | 0.650  | 0.656 |       |  |  |

| D2                                                | 15.494      | 16.002 |       | 0.610  | 0.630 |       |  |  |

| D3                                                | 12.700      | 12.700 | BSC   | 0.500  | 0.500 | BSC   |  |  |

| E                                                 | 17.399      | 17.653 |       | 0.685  | 0.695 |       |  |  |

| E1                                                | 16.510      | 16.663 |       | 0.650  | 0.656 |       |  |  |

| E2                                                | 15.494      | 16.002 |       | 0.610  | 0.630 |       |  |  |

| E3                                                | 12.700      | 12.700 | BSC   | 0.500  | 0.500 | BSC   |  |  |

| CP                                                | _           | 0.102  |       | _      | 0.004 |       |  |  |

| LT                                                | 0.203       | 0.381  |       | 0.008  | 0.015 |       |  |  |

NOTES:

#### **PIN COMPATIBILITY**

Devices that have the same package type and VDD, Vss and MCLR pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

| Pin Compatible Devices                                                                                                                                                                                                                                      | Package          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| PIC12C508, PIC12C509                                                                                                                                                                                                                                        | 8-pin            |

| PIC16C54, PIC16C54A,<br>PIC16CR54A,<br>PIC16C56,<br>PIC16C58A, PIC16CR58A,<br>PIC16C61,<br>PIC16C554, PIC16C556, PIC16C558<br>PIC16C620, PIC16C621, PIC16C622,<br>PIC16C710, PIC16C71, PIC16C711,<br>PIC16F83, PIC16CR83,<br>PIC16C84, PIC16F84A, PIC16CR84 | 18-pin<br>20-pin |

| PIC16C55,<br>PIC16C57, PIC16CR57B                                                                                                                                                                                                                           | 28-pin           |

| PIC16C62, PIC16CR62, PIC16C62A, PIC16C63,<br>PIC16C72, PIC16C73, PIC16C73A                                                                                                                                                                                  | 28-pin           |

| PIC16C64, PIC16CR64, PIC16C64A,<br>PIC16C65, PIC16C65A,<br>PIC16C74, PIC16C74A                                                                                                                                                                              | 40-pin           |

| PIC17C42, PIC17CR42, PIC17C42A,<br>PIC17C43, PIC17CR43, PIC17C44                                                                                                                                                                                            | 40-pin           |

| PIC16C923, PIC16C924                                                                                                                                                                                                                                        | 64/68-pin        |

#### TABLE E-1: PIN COMPATIBLE DEVICES