Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 014110                   |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 176 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                     |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-QFP                                                                      |

| Supplier Device Package    | 44-MQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc662t-04-pq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0         | General Description                            | 5    |

|-------------|------------------------------------------------|------|

|             | PIC16C64X & PIC16C66X Device Varieties         |      |

|             | Architectural Overview                         |      |

| 4.0         | Memory Organization                            | .17  |

| 5.0         | I/O Ports                                      | .29  |

| 6.0         | Timer0 Module                                  | . 41 |

| 7.0         | Comparator Module                              | . 47 |

| 8.0         | Voltage Reference Module                       | .53  |

| 9.0         | Special Features of the CPU                    | . 55 |

| 10.0        | Instruction Set Summary                        | .73  |

| 11.0        | Development Support                            | . 87 |

| 12.0        | Electrical Specifications                      | . 91 |

| 13.0        | Device Characterization Information            | 03   |

| 14.0        | Packaging Information 1                        | 105  |

| Appendix    | KA: Enhancements1                              | 15   |

| Appendix    | KB: Compatibility1                             | 115  |

| Appendix    | x C: What's New 1                              | 16   |

| Appendix    | x D: What's Changed1                           | 16   |

| Appendix    | x E: PIC16/17 Microcontrollers 1               | 117  |

| Pin Com     | patibility1                                    | 125  |

| Index       |                                                | 127  |

| List of Ex  | xamples                                        | 129  |

| List of Fig | gures                                          | 129  |

| List of Ta  | ables1                                         | 30   |

| On-Line     | Support                                        | 31   |

|             | Response                                       |      |

| PIC16C6     | 34X & PIC16C66X Product Identification System1 | 135  |

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

## 2.0 PIC16C64X & PIC16C66X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the Product Identification System page at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C64X & PIC16C66X.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround-</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

| TABLE 3-2:   | FICT         | 00001/       |               |               | SCRIPTIO              |                                                                                                                                                                                                                     |

|--------------|--------------|--------------|---------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | DIP<br>Pin # | QFP<br>Pin # | PLCC<br>Pin # | l/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                                         |

| OSC1/CLKIN   | 13           | 30           | 14            | I             | ST/CMOS               | Oscillator crystal input or external clock source input.                                                                                                                                                            |

| OSC2/CLKOUT  | 14           | 31           | 15            | 0             |                       | Oscillator crystal output. Connects to crystal or reso-<br>nator in crystal oscillator mode. In RC mode, OSC2<br>pin outputs CLKOUT which has 1/4 the frequency of<br>OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp     | 1            | 18           | 2             | I/P           | ST                    | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                             |

|              |              |              |               |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                                 |

| RA0/AN0      | 2            | 19           | 3             | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                            |

| RA1/AN1      | 3            | 20           | 4             | I/O           | ST                    | Analog comparator input.                                                                                                                                                                                            |

| RA2/AN2/VREF | 4            | 21           | 5             | I/O           | ST                    | Analog comparator input or VREF output.                                                                                                                                                                             |

| RA3/AN3      | 5            | 22           | 6             | I/O           | ST                    | Analog comparator input or comparator output.                                                                                                                                                                       |

| RA4/T0CKI    | 6            | 23           | 7             | I/O           | ST                    | Can be selected to be the clock input to the Timer0 timer/counter or a comparator output. Output is open drain type.                                                                                                |

| RA5          | 7            | 24           | 8             | I/O           | ST                    |                                                                                                                                                                                                                     |

|              |              |              |               |               |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs.                                                                                                      |

| RB0/INT      | 33           | 8            | 36            | I/O           | TTL/ST <sup>(1)</sup> | RB0 can also be selected as an external interrupt pin.                                                                                                                                                              |

| RB1          | 34           | 9            | 37            | I/O           | TTL                   |                                                                                                                                                                                                                     |

| RB2          | 35           | 10           | 38            | I/O           | TTL                   |                                                                                                                                                                                                                     |

| RB3          | 36           | 11           | 39            | I/O           | TTL                   |                                                                                                                                                                                                                     |

| RB4          | 37           | 14           | 41            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                            |

| RB5          | 38           | 15           | 42            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                            |

| RB6          | 39           | 16           | 43            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                                  |

| RB7          | 40           | 17           | 44            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming data.                                                                                                                                                                   |

|              |              |              |               |               |                       | PORTC is a bi-directional I/O port.                                                                                                                                                                                 |

| RC0          | 15           | 32           | 16            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC1          | 16           | 35           | 18            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC2          | 17           | 36           | 19            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC3          | 18           | 37           | 20            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC4          | 23           | 42           | 25            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC5          | 24           | 43           | 26            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC6          | 25           | 44           | 27            | I/O           | ST                    |                                                                                                                                                                                                                     |

| RC7          | 26           | 1            | 29            | I/O           | ST                    |                                                                                                                                                                                                                     |

#### **TABLE 3-2:** PIC16C661/662 PINOUT DESCRIPTION

I = input - = not used ST = Schmitt Trigger input TTL = TTL input

I/O = input/output

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port Mode (for interfacing to a microprocessor port).

P = power

Legend:

O = output

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset (POR), an external  $\overline{\text{MCLR}}$  reset, WDT reset, Brown-out Reset (BOR), and Parity Error Reset (PER). The PCON register also contains a status bit, MPEEN, which reflects the value of the MPEEN bit in Configuration Word. See Table 9-4 for status of these bits on various resets.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is cleared, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by programming the BODEN bit in the Configuration word).

#### FIGURE 4-10: PCON REGISTER (ADDRESS 8Eh)

| R-U                                                                                                           | U-0                                                                                                                                                                                                                  | U-0       | U-0        | U-0 | R/W-1 | R/W-0 | R/W-u |                 |  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----|-------|-------|-------|-----------------|--|

| MPEEN                                                                                                         |                                                                                                                                                                                                                      | _         | _          | —   | PER   | POR   | BOR   | R= Readable bit |  |

| bit7                                                                                                          |                                                                                                                                                                                                                      |           |            |     |       |       |       |                 |  |

| bit 7: MPEEN: Memory Parity Error Circuitry Status bit<br>Reflects the value of Configuration Word bit, MPEEN |                                                                                                                                                                                                                      |           |            |     |       |       |       |                 |  |

| bit 6-3:                                                                                                      | Unimplen                                                                                                                                                                                                             | nented: R | ead as '0' |     |       |       |       |                 |  |

| bit 2:                                                                                                        | <ul> <li>PER: Memory Parity Error Reset Status bit</li> <li>1 = No error occurred</li> <li>0 = Program memory fetch parity error occurred<br/>(must be set in software after a Parity Error Reset occurs)</li> </ul> |           |            |     |       |       |       |                 |  |

| bit 1:                                                                                                        | <ol> <li>POR: Power-on Reset Status bit</li> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ol>                            |           |            |     |       |       |       |                 |  |

| bit 0:                                                                                                        | <b>BOR</b> : Brown-out Reset Status bit<br>1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)                                                |           |            |     |       |       |       |                 |  |

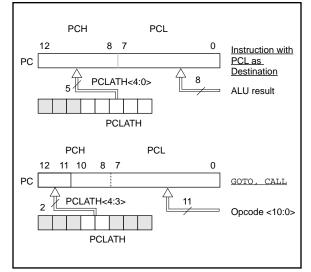

## 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is readable and writable. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-11 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-11: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

## 4.3.2 STACK

PIC16C64X & PIC16C66X devices have an 8 level deep x 13-bit wide hardware stack (Figure 4-2). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no status bits to indicate stack |

|---------|--------------------------------------------|

|         | overflow or stack underflow conditions.    |

Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 Program Memory Paging

PIC16C642 and PIC16C662 devices have 4K of program memory, but the CALL and GOTO instructions only have an 11-bit address range. This 11-bit address range allows a branch within a 2K program memory page size. To allow CALL and GOTO instructions to address the entire 4K program memory address range, there must be another bit to specify the program memory page. This paging bit comes from the PCLATH<3> bit (Figure 4-11). When doing a CALL or GOTO instruction, the user must ensure that this page select bit (PCLATH<3>) is programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions (which POPs the address from the stack).

| Note: | The PIC16C64X & PIC16C66X ignore the       |

|-------|--------------------------------------------|

|       | PCLATH<4> bit, which is used for program   |

|       | memory pages 2 and 3 (1000h - 1FFFh).      |

|       | The use of PCLATH<4> as a general pur-     |

|       | pose read/write bit is not recommended     |

|       | since this may affect upward compatibility |

|       | with future products.                      |

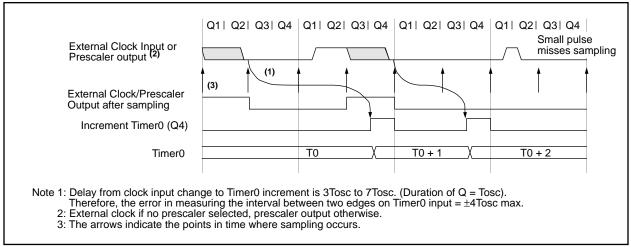

#### 6.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41, and 42 in the electrical specification of the desired device.

#### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### 7.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. User software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit (PIR1<6>), is the comparator interrupt flag and must be cleared in user software.

To enable the Comparator interrupt the following bits must be set:

- CMIE (PIE1<6>)

- PEIE (INTCON<6>)

- GIE (INTCON<7>)

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 7.7 Comparator Operation During SLEEP

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake up the device from SLEEP mode when enabled. While the comparator is powered up, higher sleep currents than shown in the power-down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM2:CM0 = 111, before entering sleep. If the device wakes up from sleep, the contents of the CMCON register are not affected.

#### 7.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM2:CM0 = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered down during the reset interval.

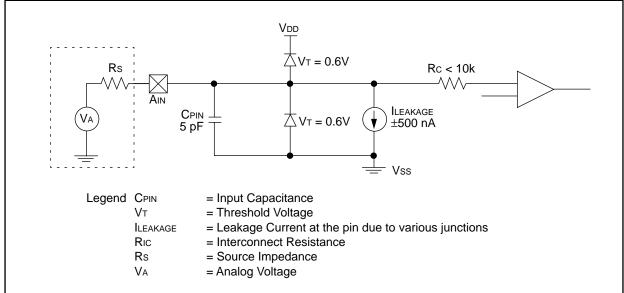

#### 7.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 7-5. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 kΩ is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 7-5: ANALOG INPUT MODEL

#### 8.1 <u>Configuring the Voltage Reference</u>

The Voltage Reference Module can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

If VRR = 1 Then VREF = (VR3:VR0/24) • VDD If VRR = 0 Then VREF = (VDD • 1/4) + (VR3:VR0/32) • VDD

The settling time of the Voltage Reference must be considered when changing the VREF output (Table 12-2). Example 8-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

#### EXAMPLE 8-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02             | ; | 4 inputs muxed     |

|-------|------------------|---|--------------------|

| MOVWF | CMCON            | ; | to 2 comparators   |

| BSF   | STATUS, RPO      | ; | Select Bank 1      |

| MOVLW | 0x07             | ; | RA3:RA0 to outputs |

| MOVWF | TRISA            | ; |                    |

| MOVLW | 0xA6             | ; | enable Vref low    |

| MOVWF | VRCON            | ; | range, VR3:VR0 = 6 |

| BCF   | STATUS, RPO      | ; | Select Bank 0      |

| CALL  | DELAY_10 $\mu s$ |   | ; 10 µs delay      |

#### 8.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 8-2) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 12-3.

#### 8.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference Module should be disabled.

#### 8.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 8.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and bit VROE is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

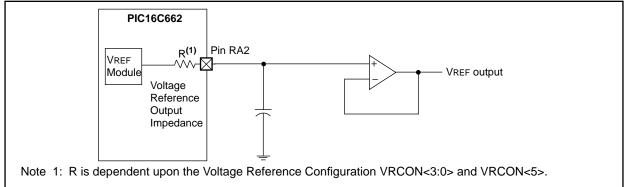

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 8-3 shows an example buffering technique.

#### FIGURE 8-3: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

#### TABLE 8-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR,<br>BOR | Value on<br>all other<br>resets |

|---------|-------|-------|-------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000               | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | -      | _      | CIS    | CM2    | CM1    | CM0    | 00 0000                 | 00 0000                         |

| 85h     | TRISA |       |       | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

#### 9.4.5 PARITY ERROR RESET (PER)

PIC16C64X & PIC16C66X devices have on-chip parity bits that can be used to verify the contents of program memory. Parity bits may be useful in applications in order to increase overall reliability of a system.

There are two parity bits for each word of Program Memory. The parity bits are computed on alternating bits of the program word. One computation is performed using even parity, the other using odd parity. As a program executes, the parity is verified. The even parity bit is XOR'd with the even bits in the program memory word. The odd parity bit is negated and XOR'd with the odd bits in the program memory word. When an error is detected, a reset is generated and the PER flag bit in the PCON register is set. This indication can allow software to act on a failure. However, there is no indication of the program memory location of the failure of the Program Memory. This flag can only be cleared in software or by a POR.

The parity array is user selectable during programming. Bit7 of the configuration word located at address 2007h can be programmed (read as '0') to disable parity checking. If left unprogrammed (read as '1'), parity checking is enabled.

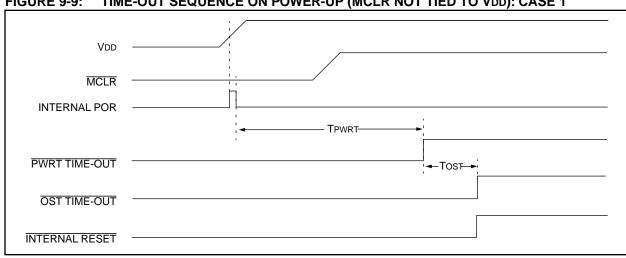

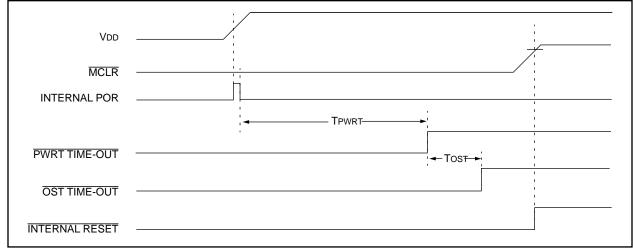

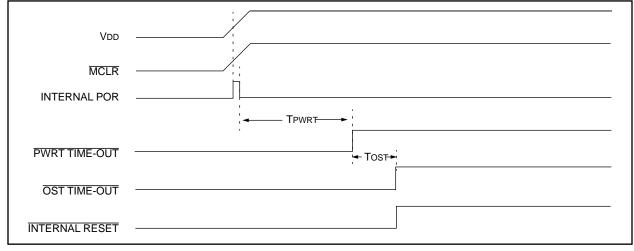

#### 9.4.6 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired. Then the OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with the <u>PWRTE</u> bit set (PWRT disabled), there will be no time-out at all. Figure 9-9, Figure 9-10 and Figure 9-11 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 9-10). This is useful for testing purposes or to synchronize more than one device operating in parallel.

Table 9-5 shows the reset conditions for some special registers, while Table 9-6 shows the reset conditions for all the registers.

#### TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

#### 9.4.7 POWER CONTROL/STATUS REGISTER (PCON)

The power control/status register, PCON (address 8Eh) has four bits. See Figure 4-10 for register.

Bit0 is  $\overline{BOR}$  (Brown-out Reset).  $\overline{BOR}$  is unknown on a Power-on-reset. It must initially be set by the user and checked on subsequent resets to see if  $\overline{BOR} = '0'$ indicating that a Brown-out Reset has occurred. The  $\overline{BOR}$  status bit is a "don't care" bit and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

Bit1 is POR (Power-on Reset). It is cleared on a Power-on Reset and is unaffected otherwise. The user set this bit following a Power-on Reset. On subsequent resets if POR is '0', it will indicate that a Power-on Reset must have occurred.

Bit2 is PER (Parity Error Reset). It is cleared on a Parity Error Reset and must be set by user software. It will also be set on a Power-on Reset.

Bit7 is MPEEN (Memory Parity Error Enable). This bit reflects the status of the MPEEN bit in configuration word. It is unaffected by any reset or interrupt.

| Oscillator Configuration | Powe              | er-up            | Brown-out Reset   | Wake-up    |  |

|--------------------------|-------------------|------------------|-------------------|------------|--|

|                          | <b>PWRTE</b> = 0  | <b>PWRTE</b> = 1 | Brown-out Reset   | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc        | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| RC                       | 72 ms             | _                | 72 ms             | —          |  |

# **PIC16C64X & PIC16C66X**

#### FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

## FIGURE 9-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### FIGURE 9-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 10.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC16C64X & PIC16C66X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

10.1.1 STATUS AS DESTINATION

If an instruction writes to STATUS, the Z, C, and DC bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

10.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $\text{PCL} \rightarrow \text{dest}$                                                          |

|--------------------|-----------------------------------------------------------------------------------------------|

| Write PCL:         | $\begin{array}{l} PCLATH \to PCH;\\ \text{8-bit destination value} \to PCL \end{array}$       |

| Read-Modify-Write: | $PCL \rightarrow ALU$ operand<br>$PCLATH \rightarrow PCH$ ;<br>8-bit result $\rightarrow PCL$ |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

10.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

| Mnemonic,<br>Operands |        | Description                  | Cycles |     | 14-Bit | Status | Notes |          |       |

|-----------------------|--------|------------------------------|--------|-----|--------|--------|-------|----------|-------|

|                       |        |                              |        | MSb |        |        | LSb   | Affected |       |

| BYTE-ORIE             | NTED   | FILE REGISTER OPERATIONS     |        |     |        |        |       |          |       |

| ADDWF                 | f, d   | Add W and f                  | 1      | 00  | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF                 | f, d   | AND W with f                 | 1      | 00  | 0101   | dfff   | ffff  | Z        | 1,2   |

| CLRF                  | f      | Clear f                      | 1      | 00  | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW                  | -      | Clear W                      | 1      | 00  | 0001   | 0000   | 0011  | Z        |       |

| COMF                  | f, d   | Complement f                 | 1      | 00  | 1001   | dfff   | ffff  | Z        | 1,2   |

| DECF                  | f, d   | Decrement f                  | 1      | 00  | 0011   | dfff   | ffff  | Z        | 1,2   |

| DECFSZ                | f, d   | Decrement f, Skip if 0       | 1(2)   | 00  | 1011   | dfff   | ffff  |          | 1,2,3 |

| INCF                  | f, d   | Increment f                  | 1      | 00  | 1010   | dfff   | ffff  | Z        | 1,2   |

| INCFSZ                | f, d   | Increment f, Skip if 0       | 1(2)   | 00  | 1111   | dfff   | ffff  |          | 1,2,3 |

| IORWF                 | f, d   | Inclusive OR W with f        | 1      | 00  | 0100   | dfff   | ffff  | Z        | 1,2   |

| MOVF                  | f, d   | Move f                       | 1      | 00  | 1000   | dfff   | ffff  | Z        | 1,2   |

| MOVWF                 | f      | Move W to f                  | 1      | 00  | 0000   | lfff   | ffff  |          |       |

| NOP                   | -      | No Operation                 | 1      | 00  | 0000   | 0xx0   | 0000  |          |       |

| RLF                   | f, d   | Rotate Left f through Carry  | 1      | 00  | 1101   | dfff   | ffff  | С        | 1,2   |

| RRF                   | f, d   | Rotate Right f through Carry | 1      | 00  | 1100   | dfff   | ffff  | С        | 1,2   |

| SUBWF                 | f, d   | Subtract W from f            | 1      | 00  | 0010   | dfff   | ffff  | C,DC,Z   | 1,2   |

| SWAPF                 | f, d   | Swap nibbles in f            | 1      | 00  | 1110   | dfff   | ffff  |          | 1,2   |

| XORWF                 | f, d   | Exclusive OR W with f        | 1      | 00  | 0110   | dfff   | ffff  | Z        | 1,2   |

| BIT-ORIENT            | ED FIL | E REGISTER OPERATIONS        |        |     |        |        |       |          |       |

| BCF                   | f, b   | Bit Clear f                  | 1      | 01  | 00bb   | bfff   | ffff  |          | 1,2   |

| BSF                   | f, b   | Bit Set f                    | 1      | 01  | 01bb   | bfff   | ffff  |          | 1,2   |

| BTFSC                 | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb   | bfff   | ffff  |          | 3     |

| BTFSS                 | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb   | bfff   | ffff  |          | 3     |

| LITERAL AI            | ND CO  | NTROL OPERATIONS             |        |     |        |        |       |          |       |

| ADDLW                 | k      | Add literal and W            | 1      | 11  | 111x   | kkkk   | kkkk  | C,DC,Z   |       |

| ANDLW                 | k      | AND literal with W           | 1      | 11  | 1001   | kkkk   | kkkk  | Z        |       |

| CALL                  | k      | Call subroutine              | 2      | 10  | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT                | -      | Clear Watchdog Timer         | 1      | 00  | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO                  | k      | Go to address                | 2      | 10  | 1kkk   | kkkk   | kkkk  |          |       |

| IORLW                 | k      | Inclusive OR literal with W  | 1      | 11  | 1000   | kkkk   | kkkk  | Z        |       |

| MOVLW                 | k      | Move literal to W            | 1      | 11  | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE                | -      | Return from interrupt        | 2      | 00  | 0000   | 0000   | 1001  |          |       |

| RETLW                 | k      | Return with literal in W     | 2      | 11  | 01xx   | kkkk   | kkkk  |          |       |

| RETURN                | -      | Return from Subroutine       | 2      | 00  | 0000   | 0000   | 1000  |          |       |

| SLEEP                 | -      | Go into standby mode         | 1      | 00  | 0000   | 0110   | 0011  | TO,PD    |       |

| SUBLW                 | k      | Subtract W from literal      | 1      | 11  | 110x   | kkkk   | kkkk  | C,DC,Z   |       |

| XORLW                 | k      | Exclusive OR literal with W  | 1      | 11  | 1010   |        |       | Z        |       |

#### TABLE 10-2: INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## 11.0 DEVELOPMENT SUPPORT

## 11.1 Development Tools

The PIC16/17 microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB-SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy logic development system (fuzzyTECH<sup>®</sup>–MP)

#### 11.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>TM</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 11.3 ICEPIC: Low-cost PIC16CXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 11.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC16C5X, PIC16CXX, PIC17CXX and PIC14000 devices. It can also set configuration and code-protect bits in this mode.

## 11.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12C5XX, PIC14000, PIC16C5X, PIC16CXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket. MPASM allows full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

## 11.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 11.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

#### 11.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 11.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 11.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 11.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

#### 11.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# **PIC16C64X & PIC16C66X**

#### 12.3 DC Characteristics: PIC16C641/661 (Commercial, Industrial, Automotive) PIC16C642/662 (Commercial, Industrial, Automotive) PIC16LC641/661 (Commercial, Industrial) PIC16LC642/662 (Commercial, Industrial)

|              |                            | Standard Operating Conditions (        | unless othe           | erwise                            | stated)                           |                 |                                                                                        |

|--------------|----------------------------|----------------------------------------|-----------------------|-----------------------------------|-----------------------------------|-----------------|----------------------------------------------------------------------------------------|

|              |                            |                                        | $\leq$ TA $\leq$ +85  |                                   | for industrial,                   |                 |                                                                                        |

|              |                            | 0°C                                    | $\leq$ TA $\leq$ +70  | -                                 | commercial, a                     | and             |                                                                                        |

|              |                            |                                        | $\leq$ TA $\leq$ +12  |                                   | automotive                        |                 |                                                                                        |

|              |                            | Operating voltage VDD range as         |                       | 1                                 | -                                 |                 |                                                                                        |

| Param<br>No. | Sym                        | Characteristic                         | Min                   | Тур<br>†                          | Max                               | Unit            | Conditions                                                                             |

|              | VIL                        | Input Low Voltage                      |                       |                                   |                                   |                 |                                                                                        |

|              |                            | I/O ports                              |                       |                                   |                                   |                 |                                                                                        |

| D030         |                            | with TTL buffer                        | Vss                   | -                                 | 0.15Vdd                           | V               | For eptire Voo range                                                                   |

|              |                            |                                        | Vss                   | -                                 | 0.8V                              | V               | 4.5√ ≤ √DD ≤ 5.5√                                                                      |

| D031         |                            | with Schmitt Trigger input             | Vss                   | -                                 | 0.2Vdd                            | V               |                                                                                        |

| D032         |                            | MCLR, RA4/T0CKI,OSC1 (in               | Vss                   | -                                 | 0.2Vdd                            | V~              | (1)                                                                                    |

|              |                            | RC mode)                               |                       |                                   |                                   | < ,             | $\sim$                                                                                 |

| D033         |                            | OSC1 (XT and HS modes)                 | Vss                   | -                                 | 0.3VDD                            | $ \lambda $     | $\searrow$                                                                             |

|              |                            | OSC1 (LP modes)                        | Vss                   | -                                 | 0.6VDD 1.0                        | v \             |                                                                                        |

|              | Viн                        | Input High Voltage                     |                       |                                   | $\langle$                         | $\overline{\ }$ |                                                                                        |

|              |                            | I/O ports                              |                       |                                   | $\langle $                        | $\land$         |                                                                                        |

| D040         |                            | with TTL buffer                        | 2.0                   | -/                                | VQD                               | ×/              |                                                                                        |

| D041         |                            | with Schmitt Trigger input             | 0.25Vdd               | L- \                              | VDD                               | v               |                                                                                        |

|              |                            |                                        | to 0.8V               | $\left[ \right] $                 | $\backslash \setminus \checkmark$ |                 |                                                                                        |

| D042         |                            | MCLR RA4/T0CKI                         | 0.8VDD                | ( A )                             | VQD                               | V               |                                                                                        |

| D043         |                            | OSC1 (XT, HS, LP modes)                | Q.7VQD                | $\left  \right  - \left  \right $ | VDD                               | V               |                                                                                        |

| D043A        |                            | OSC1 (RC mode)                         | 0.9VDD                | 7)                                | \ <u> </u>                        | V               | (1)                                                                                    |

| D070         | IPURB                      | PORTB weak pull-up current             | 50                    | 200-                              | 400                               | μA              | VDD = 5.0V, VPIN = VSS                                                                 |

|              | lı∟                        | Input Leakage Current <sup>(2,3)</sup> | $  \setminus \rangle$ | $\bigvee$                         |                                   |                 |                                                                                        |

|              |                            | I/O ports (Except PORTA)               | $  \rangle$           |                                   |                                   |                 |                                                                                        |

|              |                            |                                        | $\wedge$              | -                                 | ±1.0                              | μA              | $VSS \leq VPIN \leq VDD,$                                                              |

| Doco         |                            | PORTA                                  |                       |                                   |                                   |                 | pin at hi-impedance                                                                    |

| D060         |                            |                                        | -                     | -                                 | ±0.5                              | μA              | Vss $\leq$ VPIN $\leq$ VDD,<br>pin at hi-impedance                                     |

| D061         |                            |                                        |                       | _                                 | ±1.0                              |                 | $V_{SS} \leq V_{PIN} \leq V_{DD}$                                                      |

| D063         |                            | OSC1, MCLR                             | -                     |                                   | ±1.0<br>±5.0                      | μΑ              | $V_{SS} \leq V_{PIN} \leq V_{DD}$<br>$V_{SS} \leq V_{PIN} \leq V_{DD}$ , XT, HS and LP |

| D063         |                            | USUI, MCLR                             | -                     | -                                 | ±5.0                              | μA              | $VSS \leq VPIN \leq VDD, \times 1, HS and LP osc configuration$                        |

|              | Vol                        | Output Low Voltage                     |                       |                                   |                                   |                 |                                                                                        |

| D080         |                            | 1/O ports                              | _                     | _                                 | 0.6                               | v               | IOL = 8.5 mA, VDD = 4.5V,                                                              |

| DUUU         | 1                          |                                        | _                     | _                                 | 0.0                               | v               | -40° to +85°C                                                                          |

| <            | $\langle \langle \rangle$  | ∤/ ~                                   | -                     | -                                 | 0.6                               | v               | $IOL = 7.0 \text{ MA}, \text{VDD} = 4.5\text{V}, +125^{\circ}\text{C}$                 |

| D083         | $ $ $\backslash$ $\rangle$ | OSC2/CLKOUT                            | -                     | -                                 | 0.6                               | v               | IOL = 1.6  mA, VDD = 4.5 V,                                                            |

| 2000         |                            | 5                                      |                       |                                   | 0.0                               | , v             | -40° to +85°C                                                                          |

|              |                            | (RC only)                              | -                     | -                                 | 0.6                               | v               | IOL = 1.2 mA, VDD = 4.5V, +125°C                                                       |

| * -          | Those n                    | arameters are characterized but r      |                       | I                                 | - • -                             |                 | , <u> </u>                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C64X & PIC16C66X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

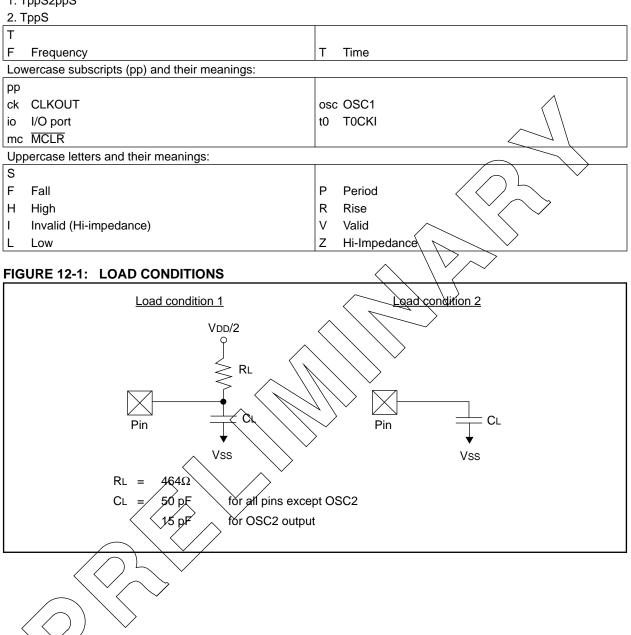

## 12.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

# **PIC16C64X & PIC16C66X**

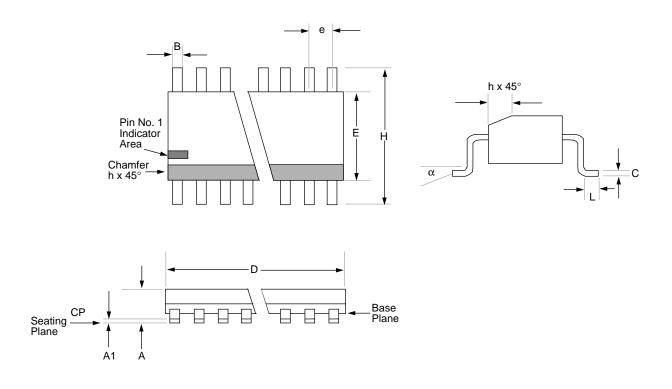

## Package Type: 28-Lead Plastic Small Outline (SO) - Wide, 300 mil Body

| Package Group: Plastic SOIC (SO) |             |            |       |        |            |       |  |  |  |

|----------------------------------|-------------|------------|-------|--------|------------|-------|--|--|--|

|                                  | Millimeters |            |       | Inches |            |       |  |  |  |

| Symbol                           | Min         | Max        | Notes | Min    | Max        | Notes |  |  |  |

| α                                | 0°          | <b>8</b> ° |       | 0°     | <b>8</b> ° |       |  |  |  |

| А                                | 2.362       | 2.642      |       | 0.093  | 0.104      |       |  |  |  |

| A1                               | 0.101       | 0.300      |       | 0.004  | 0.012      |       |  |  |  |

| В                                | 0.355       | 0.483      |       | 0.014  | 0.019      |       |  |  |  |

| С                                | 0.241       | 0.318      |       | 0.009  | 0.013      |       |  |  |  |

| D                                | 17.703      | 18.085     |       | 0.697  | 0.712      |       |  |  |  |

| E                                | 7.416       | 7.595      |       | 0.292  | 0.299      |       |  |  |  |

| е                                | 1.270       | 1.270      | BSC   | 0.050  | 0.050      | BSC   |  |  |  |

| Н                                | 10.007      | 10.643     |       | 0.394  | 0.419      |       |  |  |  |

| h                                | 0.381       | 0.762      |       | 0.015  | 0.030      |       |  |  |  |

| L                                | 0.406       | 1.143      |       | 0.016  | 0.045      |       |  |  |  |

| CP                               | —           | 0.102      |       |        | 0.004      |       |  |  |  |

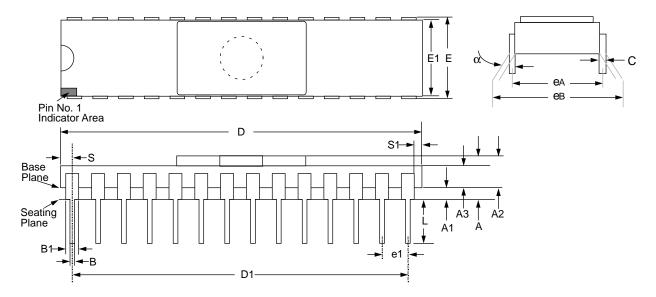

Package Type: 28-Lead Ceramic Side Brazed Dual In-Line with Window (JW) (300 mil)

| Package Group: Ceramic Side Brazed Dual In-Line (CER) |             |        |         |        |       |       |  |  |

|-------------------------------------------------------|-------------|--------|---------|--------|-------|-------|--|--|

| Symbol                                                | Millimeters |        |         | Inches |       |       |  |  |

|                                                       | Min         | Max    | Notes   | Min    | Max   | Notes |  |  |

| α                                                     | 0°          | 10°    |         | 0°     | 10°   |       |  |  |

| А                                                     | 3.937       | 5.030  |         | 0.155  | 0.198 |       |  |  |

| A1                                                    | 1.016       | 1.524  |         | 0.040  | 0.060 |       |  |  |

| A2                                                    | 2.921       | 3.506  |         | 0.115  | 0.138 |       |  |  |

| A3                                                    | 1.930       | 2.388  |         | 0.076  | 0.094 |       |  |  |

| В                                                     | 0.406       | 0.508  |         | 0.016  | 0.020 |       |  |  |

| B1                                                    | 1.219       | 1.321  | Typical | 0.048  | 0.052 |       |  |  |

| С                                                     | 0.228       | 0.305  | Typical | 0.009  | 0.012 |       |  |  |

| D                                                     | 35.204      | 35.916 |         | 1.386  | 1.414 |       |  |  |

| D1                                                    | 32.893      | 33.147 | BSC     | 1.295  | 1.305 |       |  |  |

| E                                                     | 7.620       | 8.128  |         | 0.300  | 0.320 |       |  |  |

| E1                                                    | 7.366       | 7.620  |         | 0.290  | 0.300 |       |  |  |

| e1                                                    | 2.413       | 2.667  | Typical | 0.095  | 0.105 |       |  |  |

| eA                                                    | 7.366       | 7.874  | BSC     | 0.290  | 0.310 |       |  |  |

| eB                                                    | 7.594       | 8.179  |         | 0.299  | 0.322 |       |  |  |

| L                                                     | 3.302       | 4.064  |         | 0.130  | 0.160 |       |  |  |

| S                                                     | 1.143       | 1.397  |         | 0.045  | 0.055 |       |  |  |

| S1                                                    | 0.533       | 0.737  |         | 0.021  | 0.029 |       |  |  |

NOTES:

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit Tri-Atria Office Building

32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

# 2767 S. Albright Road

Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387 Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335 San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

#### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza

223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc. India Liaison Office **Divvasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### EUROPE

Denmark

Microchip Technology Nordic ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### United Kinadom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02