Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, LED, POR, WDT                                        |

| Number of I/O              | 33                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 176 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 6V                                                                      |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc662t-04i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

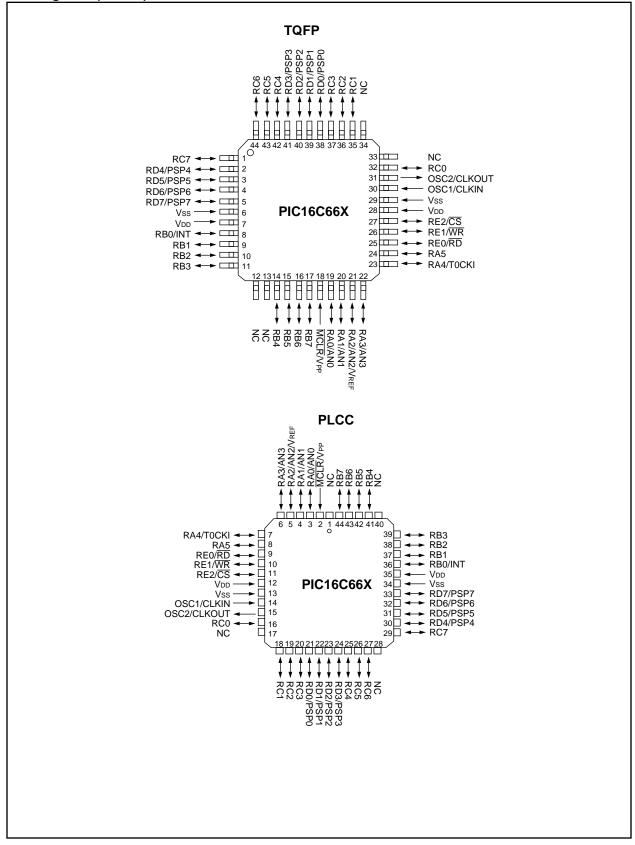

### Pin Diagrams (Cont.'d)

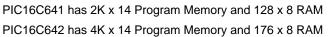

### FIGURE 3-1: PIC16C641/642 BLOCK DIAGRAM

| Name     | DIP<br>Pin #    | QFP<br>Pin #    | PLCC<br>Pin # | l/O/P<br>Type        | Buffer<br>Type        | Description                                                                                            |

|----------|-----------------|-----------------|---------------|----------------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|          |                 |                 |               |                      |                       | PORTD can be a bi-directional I/O port or parallel slave port for interfacing to a microprocessor bus. |

| RD0/PSP0 | 19              | 38              | 21            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD1/PSP1 | 20              | 39              | 22            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2 | 21              | 40              | 23            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3 | 22              | 41              | 24            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4 | 27              | 2               | 30            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5 | 28              | 3               | 31            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6 | 29              | 4               | 32            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7 | 30              | 5               | 33            | I/O                  | ST/TTL <sup>(3)</sup> |                                                                                                        |

|          |                 |                 |               |                      |                       | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD   | 8               | 25              | 9             | I/O                  | ST/TTL <sup>(3)</sup> | RE0/RD read control for parallel slave port.                                                           |

| RE1/WR   | 9               | 26              | 10            | I/O                  | ST/TTL <sup>(3)</sup> | RE1/WR write control for parallel slave port.                                                          |

| RE2/CS   | 10              | 27              | 11            | I/O                  | ST/TTL <sup>(3)</sup> | RE2/CS select control for parallel slave port.                                                         |

| Vss      | 12,31           | 6,29            | 13,34         | Р                    |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd      | 11,32           | 7,28            | 12,35         | Р                    |                       | Positive supply for logic and I/O pins.                                                                |

| NC       | —               | 12,13,<br>33,34 | 1,17<br>28,40 | _                    | —                     | Not Connected.                                                                                         |

| Legend:  | 0 = 0<br>l = in | output<br>put   |               | I/O = inp<br>— = not | ut/output<br>used     | P = power<br>ST = Schmitt Trigger input                                                                |

ST = Schmitt Trigger input

TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as a general purpose I/O and a TTL input when used in the Parallel Slave Port Mode (for interfacing to a microprocessor port).

### 5.0 I/O PORTS

The PIC16C641 and PIC16C642 have three ports, PORTA, PORTB, and PORTC. PIC16C661 and PIC16C662 devices have five ports, PORTA through PORTE. Some pins for these I/O ports are multiplexed with alternate functions for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

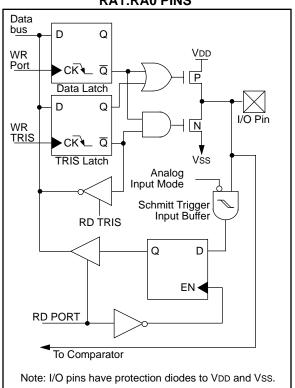

### 5.1 PORTA and TRISA Registers

PORTA is a 6-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Pin RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

Setting a bit in the TRISA register puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (comparator control register) register and the VRCON (voltage reference control) register. When selected as comparator inputs, these pins will read as '0's.

### FIGURE 5-1: BLOCK DIAGRAM OF RA1:RA0 PINS

**Note:** On reset, the TRISA register is set to all inputs. The digital inputs are disabled and the comparator inputs are forced to ground to reduce excess current consumption.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very hi-impedance output. The user must set the TRISA<2> bit and use hi-impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

### EXAMPLE 5-1: INITIALIZING PORTA

| CLRF  | PORTA       | ;Initialize PORTA by     |

|-------|-------------|--------------------------|

|       |             | ;clearing output latches |

| MOVLW | 0x07        | ;Turn comparators off,   |

| MOVWF | CMCON       | ;enable pins for I/O     |

| BSF   | STATUS, RPO | ;Select bank1            |

| MOVLW | 0x1F        | ;Value to initialize     |

|       |             | ;data direction          |

| MOVWF | TRISA       | ;Set RA<4:0> as inputs   |

|       |             | ;TRISA<7:5> are clear    |

PORTD BLOCK DIAGRAM (IN

FIGURE 5-8:

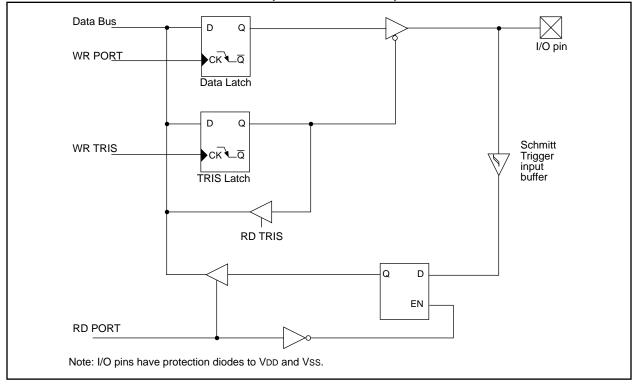

### 5.4 <u>PORTD and TRISD Registers</u> (PIC16C661 and PIC16C662 only)

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

### I/O PORT MODE) Data bus D Q WR I/O pin<sup>(1)</sup> PORT СКЪ Data Latch D Q WR Schmitt Trigger input buffer <u>TRIS</u> ►ск 🔪 TRIS Latch **RD TRIS** D Q ΕN **RD PORT** Note 1: I/O pins have protection diodes to VDD and Vss.

| Bit# | Buffer Type                                          | Function                                                                                                                                                                                                                                             |

|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit0 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit0                                                                                                                                                                                                    |

| bit1 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit1                                                                                                                                                                                                    |

| bit2 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit2                                                                                                                                                                                                    |

| bit3 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit3                                                                                                                                                                                                    |

| bit4 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit4                                                                                                                                                                                                    |

| bit5 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit5                                                                                                                                                                                                    |

| bit6 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit6                                                                                                                                                                                                    |

| bit7 | ST/TTL <sup>(1)</sup>                                | Input/output port pin or parallel slave port bit7                                                                                                                                                                                                    |

|      | bit0<br>bit1<br>bit2<br>bit3<br>bit4<br>bit5<br>bit6 | bit0         ST/TTL <sup>(1)</sup> bit1         ST/TTL <sup>(1)</sup> bit2         ST/TTL <sup>(1)</sup> bit3         ST/TTL <sup>(1)</sup> bit4         ST/TTL <sup>(1)</sup> bit5         ST/TTL <sup>(1)</sup> bit6         ST/TTL <sup>(1)</sup> |

### TABLE 5-7: PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|--------|--------|--------|---------|--------|--------|--------|--------|--------------------------|---------------------------|

| 08h     | PORTD | RD7    | RD6    | RD5    | RD4     | RD3    | RD2    | RD1    | RD0    | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | TRISD7 | TRISD6 | TRISD5 | TRISD4  | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF    | OBF    | IBOV   | PSPMODE | —      | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

### FIGURE 5-10: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

### TABLE 5-9: PORTE FUNCTIONS

| Name   | Bit# | Buffer Type           | Function                                                                                                                                                                      |

|--------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode:<br>RD                                                                                                |

|        |      |                       | 1 = Not a read operation                                                                                                                                                      |

|        |      |                       | 0 = Read operation. Reads PORTD register (if chip selected)                                                                                                                   |

| RE1/WR | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

### TABLE 5-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-------|-------|---------|-------|--------|--------|--------|--------------------------|---------------------------|

| 09h     | PORTE | —     | _     | —     | —       |       | RE2    | RE1    | RE0    | xxx                      | uuu                       |

| 89h     | TRISE | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2 | TRISE1 | TRISE0 | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

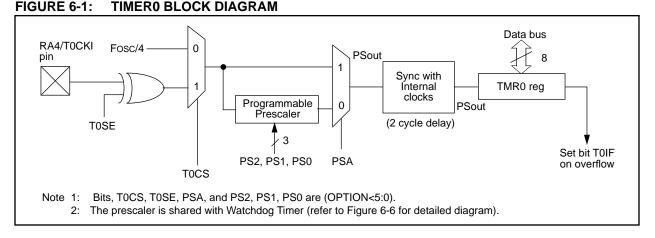

### 6.0 TIMER0 MODULE

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Read and write capability

- Interrupt on overflow from FFh to 00h

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

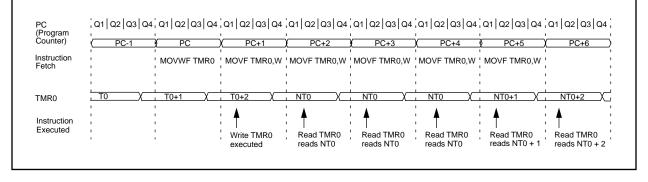

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS. In this mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge select bit T0SE

(OPTION<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 6.3 details the operation of the prescaler.

### 6.1 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the register (TMR0) overflows from FFh to 00h. This overflow sets interrupt flag bit T0IF (INTCON<2>). The interrupt can be masked by clearing enable bit T0IE (INTCON<5>). Flag bit T0IF must be cleared in software by the Timer0 interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. Figure 6-4 displays the Timer0 interrupt timing.

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALER

·4 D

101

1

### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

**Note:** To avoid an unintended device RESET, the following instruction sequence (shown in Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This precaution must be followed even if the WDT is disabled.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BCF    | STATUS, RPO | ;Bank 0                 |

|--------|-------------|-------------------------|

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler |

| BSF    | STATUS, RPO | ;Bank 1                 |

| CLRWDT |             | ;Clears WDT             |

| MOVLW  | b'xxxx1xxx' | ;Select new prescale    |

| MOVWF  | OPTION_REG  | ;value & WDT            |

| BCF    | STATUS, RPO | ;Bank 0                 |

|        |             |                         |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2.

### EXAMPLE 6-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RPO | ;Bank 1             |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

| MOVWF  | OPTION_REG  | ;clock source       |

| BCF    | STATUS, RPO | ;Bank 0             |

### TABLE 6-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                    | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|--------------------------|--------|--------|--------|--------|--------|--------|--------|--------------------------|---------------------------|

| 01h     | TMR0   | Timer0 module's register |        |        |        |        |        |        |        | xxxx xxxx                | uuuu uuuu                 |

| 0Bh/8Bh | INTCON | GIE                      | PEIE   | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 81h     | OPTION | RBPU                     | INTEDG | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111                | 1111 1111                 |

| 85h     | TRISA  | —                        | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

NOTES:

### 7.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is guaranteed to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-2 and Table 12-3).

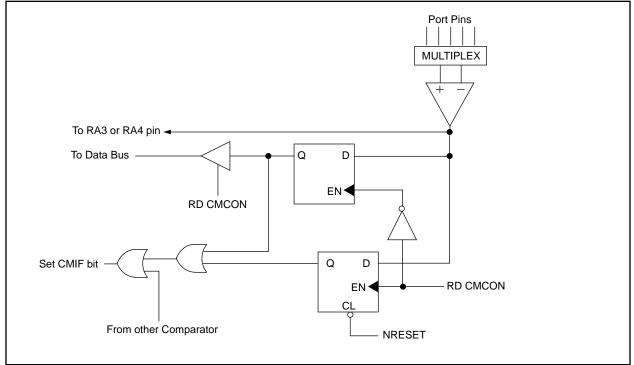

### 7.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When CM2:CM0 = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 7-4 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORTA register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- **Note 2:** Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 7-4: COMPARATOR OUTPUT BLOCK DIAGRAM

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Encoding:        | 01 11bb bfff ffff                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the next<br>instruction is skipped.<br>If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and a NOP is<br>executed instead, making this a 2 cycle<br>instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                  | if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| CLRF             | Clear f                                                                                    |      |         |       |         |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|------|---------|-------|---------|--|--|--|--|

| Syntax:          | [label] CLRF f                                                                             |      |         |       |         |  |  |  |  |

| Operands:        | $0 \le f \le 12$                                                                           | 27   |         |       |         |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$                      |      |         |       |         |  |  |  |  |

| Status Affected: | Z                                                                                          |      |         |       |         |  |  |  |  |

| Encoding:        | 00                                                                                         | 0001 | 1ff     | f     | ffff    |  |  |  |  |

| Description:     | The conter<br>and the Z                                                                    | 0    | ster 'f | ' are | cleared |  |  |  |  |

| Words:           | 1                                                                                          |      |         |       |         |  |  |  |  |

| Cycles:          | 1                                                                                          |      |         |       |         |  |  |  |  |

| Example          | CLRF                                                                                       | FLAG | G_REG   | 3     |         |  |  |  |  |

|                  | Before Instruction<br>$FLAG_REG = 0x5A$<br>After Instruction<br>$FLAG_REG = 0x00$<br>Z = 1 |      |         |       |         |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two cycle instruction. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                               |  |  |  |  |  |  |  |  |  |

| CLRW             | Clear W                                                               |           |      |      |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|-----------|------|------|--|--|--|--|--|--|

| Syntax:          | [label] CLRW                                                          |           |      |      |  |  |  |  |  |  |

| Operands:        | None                                                                  |           |      |      |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |           |      |      |  |  |  |  |  |  |

| Status Affected: | Z                                                                     |           |      |      |  |  |  |  |  |  |

| Encoding:        | 00                                                                    | 0001      | 0000 | 0011 |  |  |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |           |      |      |  |  |  |  |  |  |

| Words:           | 1                                                                     |           |      |      |  |  |  |  |  |  |

| Cycles:          | 1                                                                     |           |      |      |  |  |  |  |  |  |

| Example          | CLRW                                                                  |           |      |      |  |  |  |  |  |  |

|                  | Before In                                                             | struction | 1    |      |  |  |  |  |  |  |

|                  | W = 0x5A After Instruction $W = 0x00$ $Z = 1$                         |           |      |      |  |  |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                          | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                           |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0 >$                                                                                                                                                                   |                  | d ∈ [0,1]                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                  | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                           | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                            |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                          | Status Affected: | None                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Encoding:        | 10 1kkk kkkk kkkk                                                                                                                                                                             | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                           |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                             |                  | A NOP is executed instead making it a two cycle instruction.                                                                                                                                                                                                |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                             | Words:           | 1                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Example          | GOTO THERE                                                                                                                                                                                    | Cycles:          | 1(2)                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                  | After Instruction<br>PC = Address THERE                                                                                                                                                       | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                          |  |  |  |  |  |

|                  |                                                                                                                                                                                               |                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                     |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                               |  |  |  |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                     |  |  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                     |  |  |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                            |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                              |  |  |  |  |  |  |  |  |  |

After Instruction CNT =

if CNT=

= if CNT≠

=

PC

PC

CNT + 1

address CONTINUE

address HERE +1

0,

0,

| RETURN           | Return from Subroutine                                                                                                                                  |               |      |      |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                          |               |      |      |  |  |  |  |  |

| Operands:        | None                                                                                                                                                    |               |      |      |  |  |  |  |  |

| Operation:       | $\text{TOS} \rightarrow \text{P}$                                                                                                                       | C             |      |      |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                    |               |      |      |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                      | 0000          | 0000 | 1000 |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. |               |      |      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                       |               |      |      |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                       |               |      |      |  |  |  |  |  |

| Example          | RETURN                                                                                                                                                  |               |      |      |  |  |  |  |  |

|                  | After Inte                                                                                                                                              | rrupt<br>PC = | TOS  |      |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                 |                |             |                   |      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------------|------|--|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                    | RRF f,         | d           |                   |      |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                            |                |             |                   |      |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                        |                |             |                   |      |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                            |                |             |                   |      |  |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                           | 1100           | dfi         | Ef                | ffff |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                |             |                   |      |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                              |                | Regis       | tert              |      |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                            |                |             |                   |      |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                            |                |             |                   |      |  |  |  |  |  |  |

| Example          | RRF                                                                                                                                                                                                          |                | REG1        | ,0                |      |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                              | REG1<br>C      | =           | 1110<br>0         | 0110 |  |  |  |  |  |  |

|                  | l                                                                                                                                                                                                            | REG1<br>W<br>C | =<br>=<br>= | 1110<br>0111<br>0 |      |  |  |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                        | SLEEP                     |                                                                                                              |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                           | Syntax:                   | [label] SLEEP                                                                                                |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                 | Operands:                 | None                                                                                                         |  |  |  |  |  |

| Operation:       | See description below                                                              | Operation:                | 00h $\rightarrow$ WDT,<br>0 $\rightarrow$ WDT prescaler,                                                     |  |  |  |  |  |

| Status Affected: | С                                                                                  |                           | $1 \rightarrow \overline{TO}$ ,                                                                              |  |  |  |  |  |

| Encoding:        | 00 1101 dfff ffff                                                                  |                           | $0 \rightarrow \overline{PD}$                                                                                |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated                                           | Status Affected:          |                                                                                                              |  |  |  |  |  |

|                  | one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in | Encoding:<br>Description: | 00 0000 0110 0011                                                                                            |  |  |  |  |  |

|                  | the W register. If 'd' is 1 the result is                                          |                           | The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres- |  |  |  |  |  |

|                  | stored back in register 'f'.                                                       |                           |                                                                                                              |  |  |  |  |  |

|                  | C Register f                                                                       |                           | caler are cleared.<br>The processor is put into SLEEP                                                        |  |  |  |  |  |

| Words:           | 1                                                                                  |                           | mode with the oscillator stopped.                                                                            |  |  |  |  |  |

| Cycles:          | 1                                                                                  |                           | See Power-Down Mode (SLEEP) for<br>more details.                                                             |  |  |  |  |  |

| Example          | RLF REG1,0                                                                         | Words:                    | 1                                                                                                            |  |  |  |  |  |

|                  | Before Instruction                                                                 | Cycles:                   | 1                                                                                                            |  |  |  |  |  |

|                  | $\begin{array}{rcl} REG1 & = & 1110 & 0110 \\ C & = & 0 \end{array}$               | Example:                  | SLEEP                                                                                                        |  |  |  |  |  |

|                  | After Instruction                                                                  |                           |                                                                                                              |  |  |  |  |  |

|                  | REG1 = 1110 0110<br>W = 1100 1100                                                  |                           |                                                                                                              |  |  |  |  |  |

|                  | C = 1                                                                              |                           |                                                                                                              |  |  |  |  |  |

|                                                                           |                                                      | Standard Operating Conditions (    | unless othe | rwise | stated)         |      |                                    |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------|------------------------------------|-------------|-------|-----------------|------|------------------------------------|--|--|--|--|

|                                                                           |                                                      | Operating temperature -40°C        |             |       | for industrial, |      |                                    |  |  |  |  |

|                                                                           |                                                      | 0°C                                | and         |       |                 |      |                                    |  |  |  |  |

|                                                                           | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ automotive |                                    |             |       |                 |      |                                    |  |  |  |  |

| Operating voltage VDD range as described in DC spec Section 12.1 and 12.2 |                                                      |                                    |             |       |                 |      |                                    |  |  |  |  |

| Param                                                                     | Sym                                                  | Characteristic                     | Min         | Тур   | Max             | Unit | Conditions                         |  |  |  |  |

| No.                                                                       | -                                                    |                                    |             | t     |                 |      |                                    |  |  |  |  |

|                                                                           | Vон                                                  | Output High Voltage <sup>(3)</sup> |             |       |                 |      |                                    |  |  |  |  |

| D090                                                                      |                                                      | I/O ports (Except RA4)             | Vdd-0.7     | -     | -               | V    | Юн = -3.0 mA, VpD = 4.5V,          |  |  |  |  |

|                                                                           |                                                      |                                    |             |       |                 |      | -40° to +85°C                      |  |  |  |  |

|                                                                           |                                                      |                                    | Vdd-0.7     | -     | -               | V    | Юн = -2.5 mA, \                    |  |  |  |  |

|                                                                           |                                                      |                                    |             |       |                 |      | $VDD = 4.5V, \mp 125^{\circ}C$     |  |  |  |  |

| D092                                                                      |                                                      | OSC2/CLKOUT                        | VDD-0.7     | -     | -               | V    | Юн = -1.3 mA, VDD=4.5V,            |  |  |  |  |

|                                                                           |                                                      |                                    |             |       |                 |      | -40° to +85°C                      |  |  |  |  |

|                                                                           |                                                      |                                    | Vdd-0.7     | -     | -               | V <  | $10 \mu = -1.0 \text{ mA},$        |  |  |  |  |

|                                                                           |                                                      | (RC only)                          |             |       |                 |      | VDD = 4,5∀, +125°C                 |  |  |  |  |

|                                                                           |                                                      | Capacitive Loading Specs           |             |       |                 |      |                                    |  |  |  |  |

|                                                                           |                                                      | on Output Pins                     |             |       |                 |      |                                    |  |  |  |  |

| D100                                                                      | COSC2                                                | OSC2 pin                           | -           | -     | 15 \            | PF.  | In XT, HS and LP modes when        |  |  |  |  |

|                                                                           |                                                      |                                    |             |       |                 |      | external clock used to drive OSC1. |  |  |  |  |

| D101                                                                      | Сю                                                   | All I/O pins/OSC2 (in RC mode)     | -           | -     | 50              |      |                                    |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger nput. It is not recommended that the PIC16C64X & PIC16C66X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as coming out of the pin

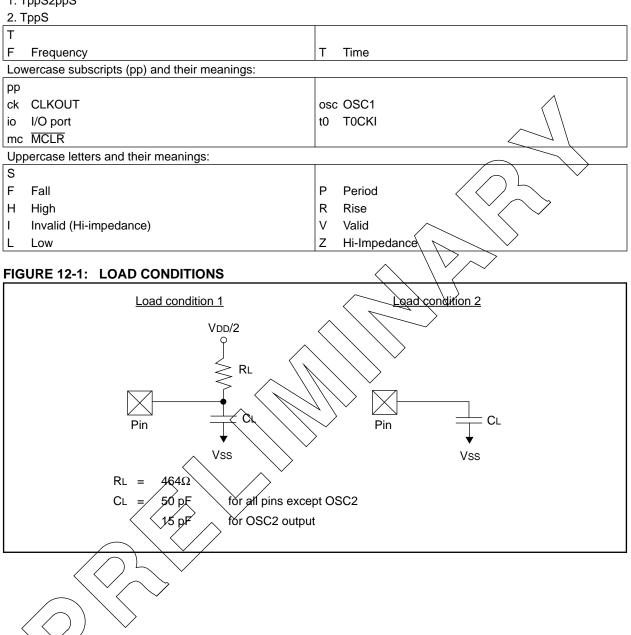

### 12.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created with one of the following formats:

1. TppS2ppS

# 13.0 DEVICE CHARACTERIZATION INFORMATION

NOT AVAILABLE AT THIS TIME.

© 1996 Microchip Technology Inc.

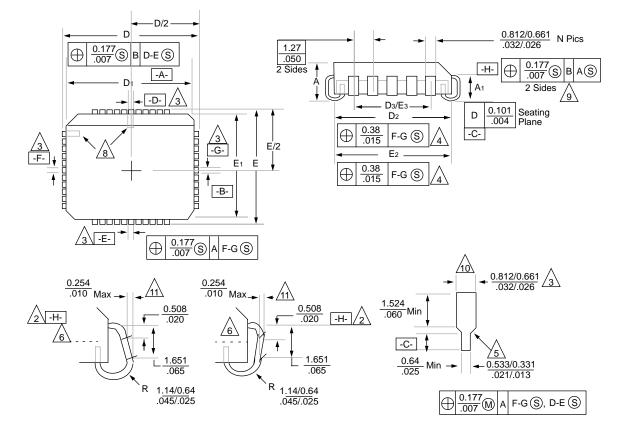

### Package Type: 44-Lead Plastic Leaded Chip Carrier (L) - Square

| Package Group: Plastic Leaded Chip Carrier (PLCC) |        |             |       |       |       |       |  |  |  |

|---------------------------------------------------|--------|-------------|-------|-------|-------|-------|--|--|--|

|                                                   |        | Millimeters |       |       |       |       |  |  |  |

| Symbol                                            | Min    | Max         | Notes | Min   | Max   | Notes |  |  |  |

| А                                                 | 4.191  | 4.572       |       | 0.165 | 0.180 |       |  |  |  |

| A1                                                | 2.413  | 2.921       |       | 0.095 | 0.115 |       |  |  |  |

| D                                                 | 17.399 | 17.653      |       | 0.685 | 0.695 |       |  |  |  |

| D1                                                | 16.510 | 16.663      |       | 0.650 | 0.656 |       |  |  |  |

| D2                                                | 15.494 | 16.002      |       | 0.610 | 0.630 |       |  |  |  |

| D3                                                | 12.700 | 12.700      | BSC   | 0.500 | 0.500 | BSC   |  |  |  |

| E                                                 | 17.399 | 17.653      |       | 0.685 | 0.695 |       |  |  |  |

| E1                                                | 16.510 | 16.663      |       | 0.650 | 0.656 |       |  |  |  |

| E2                                                | 15.494 | 16.002      |       | 0.610 | 0.630 |       |  |  |  |

| E3                                                | 12.700 | 12.700      | BSC   | 0.500 | 0.500 | BSC   |  |  |  |

| CP                                                | _      | 0.102       |       | _     | 0.004 |       |  |  |  |

| LT                                                | 0.203  | 0.381       |       | 0.008 | 0.015 |       |  |  |  |

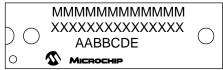

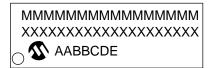

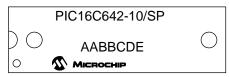

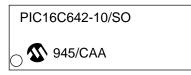

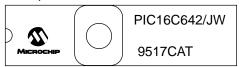

### 14.1 Package Marking Information

28-Lead SOIC

Example

### Example

### 28-Lead Side Brazed Skinny Windowed

Example

Legend:

MM...MMicrochip part number information

XX...X

Customer specific information\*

AA

Year code (last 2 digits of calendar year)

BB

Week code (week of January 1 is week '01')

C

Facility code of the plant at which wafer is manufactured

C = Chandler, Arizona, U.S.A.

D

Mask revision number

E

Assembly code of the plant or country of origin in which part was assembled

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\*Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

### **APPENDIX C: WHAT'S NEW**

New Data Sheet

### APPENDIX D: WHAT'S CHANGED

New Data Sheet

| Features |  |                | 16       | - du ``  | or the states | 18-pin DIP, SOIC; 20-pin SSOP | 28-pin PDIP, SOIC<br>Windowed CDIP | 28-pin PDIP, SOIC<br>Windowed CDIP |  |

|----------|--|----------------|----------|----------|---------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|------------------------------------|------------------------------------|--|

|          |  | $\overline{)}$ | ٣<br>روت | Souley 6 | UNOIS GEIION  |                               | 1                             | I                             | Yes                           | Yes                           | Yes                           | Yes                                | Yes                                |  |

| s        |  |                |          |          | ellon         | -9.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                          | -6.0                               | -6.0                               |  |

2.5-6.0 2.5-6.0 2.5-6.0 2.5-6.0 2.5-6.0 3.0-6.0

33 33

> ო ო

I I

I

128

80

512

PIC16C620 PIC16C621 PIC16C622

13 33 13 13 22

4

4 4

128

80

¥ З Ж

128

PIC16C641

2

4

Yes Yes Yes Yes

N 2 N

2.5-6.0

ო

TMR0 **TMR0** TMR0 TMR0 TMR0 TMR0 TMR0

80 80

512

20 20 20 20 20 20 20

PIC16C554 PIC16C556 PIC16C558

¥ Я

<sup>\$UI</sup>OJ

estros idniejuj

(s)logeredulos

(S)OULOUNOUN

(Seyla) CIOLIEN ENEQ

CETHIN LOIRE BES DO TO TOUR I UNITUREN

SEELION SOLISISTER TELLSULT

Aousw usion

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C6XXX Family devices use serial programming with clock pin RB6 and data pin RB7.

#### E.3 **PIC16CXXX Family of Devices**

Peripherals

Memory

Clock

40-pin PDIP, Windowed CDIP;

Yes

3.0-6.0

33

ß

Yes

2

TMR0

176

¥

20

PIC16C662

44-pin PLCC, MQFP

40-pin PDIP, Windowed CDIP; 44-pin PLCC, MQFP

Yes

3.0-6.0

33

ŝ

Yes

2

**TMR0**

128

З

20

PIC16C661

3.0-6.0

22

4

Yes

2

**TMR0**

176

¥

20

PIC16C642