Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 68K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205rbt6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.         | Compatible board design between STM32F10x and STM32F2xx for LQFP64 package | 18   |

|-------------------|----------------------------------------------------------------------------|------|

| Figure 2.         | Compatible board design between STM32F10x and STM32F2xx                    |      |

|                   | for LQFP100 package.                                                       | . 19 |

| Figure 3.         | Compatible board design between STM32F10x and STM32F2xx                    | 40   |

| Figure 4.         | for LQFP144 package.                                                       |      |

| -                 | STM32F20x block diagram                                                    |      |

| Figure 5.         |                                                                            |      |

| Figure 6.         | Regulator OFF/internal reset ON                                            |      |

| Figure 7.         | Regulator OFF/internal reset OFF                                           | 29   |

| Figure 8.         | Startup in regulator OFF: slow V <sub>DD</sub> slope,                      | 20   |

|                   | power-down reset risen after $V_{CAP_1}/V_{CAP_2}$ stabilization           | . 30 |

| Figure 9.         | Startup in regulator OFF: fast $V_{DD}$ slope,                             | 20   |

| <b>E</b> ioura 10 | power-down reset risen before $V_{CAP_1}/V_{CAP_2}$ stabilization.         |      |

| Figure 10.        | STM32F20x LQFP64 pinout                                                    |      |

| Figure 11.        | STM32F20x WLCSP64+2 ballout                                                |      |

| Figure 12.        | STM32F20x LQFP100 pinout                                                   |      |

| Figure 13.        | STM32F20x LQFP144 pinout                                                   |      |

| Figure 14.        | STM32F20x LQFP176 pinout                                                   |      |

| Figure 15.        | STM32F20x UFBGA176 ballout                                                 |      |

| Figure 16.        | Memory map                                                                 |      |

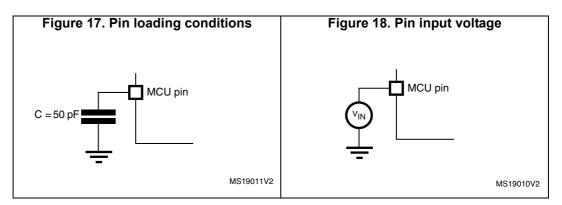

| Figure 17.        | Pin loading conditions                                                     | . 69 |

| Figure 18.        | Pin input voltage                                                          | . 69 |

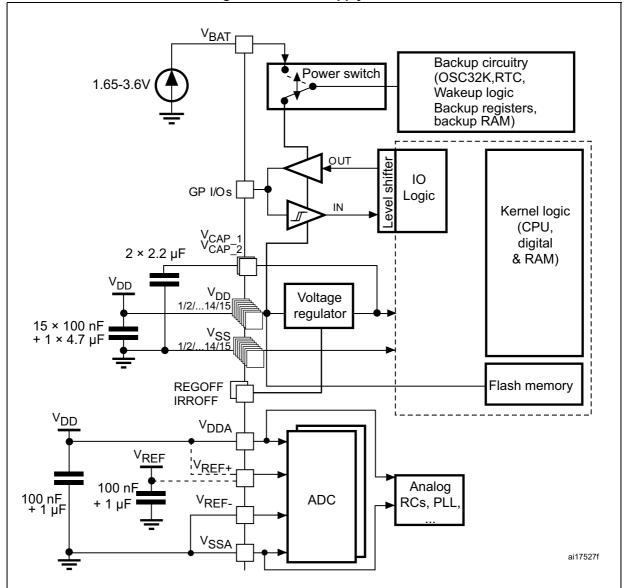

| Figure 19.        | Power supply scheme                                                        | 70   |

| Figure 20.        | Current consumption measurement scheme                                     |      |

| Figure 21.        | Number of wait states versus f <sub>CPU</sub> and V <sub>DD</sub> range    |      |

| Figure 22.        | External capacitor C <sub>FXT</sub>                                        |      |

| Figure 23.        | Typical current consumption vs. temperature, Run mode, code with data      |      |

| 0                 | processing running from RAM, and peripherals ON                            | . 81 |

| Figure 24.        | Typical current consumption vs. temperature, Run mode, code with data      |      |

|                   | processing running from RAM, and peripherals OFF                           | 81   |

| Figure 25.        | Typical current consumption vs. temperature, Run mode, code with data      |      |

| 1 iguro 20.       | processing running from Flash, ART accelerator OFF, peripherals ON         | 82   |

| Figure 26.        | Typical current consumption vs. temperature, Run mode, code with data      | . 02 |

| rigure 20.        | processing running from Flash, ART accelerator OFF, peripherals OFF        | 82   |

| Figure 27.        | Typical current consumption vs. temperature in Sleep mode,                 | . 02 |

| rigure zr.        | peripherals ON                                                             | 84   |

| Figure 28.        | Typical current consumption vs. temperature in Sleep mode,                 | . 04 |

| Figure 20.        | peripherals OFF                                                            | 01   |

| Figure 29.        | Typical current consumption vs. temperature in Stop mode                   |      |

| 0                 |                                                                            |      |

| Figure 30.        | High-speed external clock source AC timing diagram                         |      |

| Figure 31.        | Low-speed external clock source AC timing diagram.                         |      |

| Figure 32.        | Typical application with an 8 MHz crystal                                  |      |

| Figure 33.        | Typical application with a 32.768 kHz crystal                              |      |

| Figure 34.        | ACC <sub>HSI</sub> versus temperature                                      |      |

| Figure 35.        | ACC <sub>LSI</sub> versus temperature                                      |      |

| Figure 36.        | PLL output clock waveforms in center spread mode                           |      |

| Figure 37.        | PLL output clock waveforms in down spread mode                             | . 99 |

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

#### 3.20.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F20x devices (see *Table 5* for differences).

#### TIM2, TIM3, TIM4, TIM5

The STM32F20x include 4 full-featured general-purpose timers. TIM2 and TIM5 are 32-bit timers, and TIM3 and TIM4 are 16-bit timers. The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

The counters of TIM2, TIM3, TIM4, TIM5 can be frozen in debug mode. Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

#### TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM13 and TIM14 feature one independent channel, whereas TIM12 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases.

#### 3.20.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

DocID15818 Rev 15

The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.26 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F207xx devices.

The STM32F207xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F207xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F207xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) or 50 MHz (RMII) output from the STM32F207xx.

The STM32F207xx includes the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F20x and STM32F21x reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes, that is 4 Kbytes in total

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

#### 3.27 Controller area network (CAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one

DocID15818 Rev 15

#### 3.30 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

### 3.31 Digital camera interface (DCMI)

The camera interface is not available in STM32F205xx devices.

STM32F207xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain up to 27 Mbyte/s at 27 MHz or 48 Mbyte/s at 48 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw Bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

#### 3.32 True random number generator (RNG)

All STM32F2xxx products embed a true RNG that delivers 32-bit random numbers produced by an integrated analog circuit.

#### 3.33 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O alternate function configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

To provide fast I/O handling, the GPIOs are on the fast AHB1 bus with a clock up to 120 MHz that leads to a maximum I/O toggling speed of 60 MHz.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                              |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                          | Additional<br>functions |

| -      | -         | 56      | 78      | 97      | P14      | PD9                                                  | I/O      | FT            | -    | FSMC_D14, USART3_RX,<br>EVENTOUT                                             | -                       |

| -      | -         | 57      | 79      | 98      | N15      | PD10                                                 | I/O      | FT            | -    | FSMC_D15, USART3_CK,<br>EVENTOUT                                             | -                       |

| -      | -         | 58      | 80      | 99      | N14      | PD11                                                 | I/O      | FT            | -    | FSMC_A16,USART3_CTS,<br>EVENTOUT                                             | -                       |

| -      | -         | 59      | 81      | 100     | N13      | PD12                                                 | I/O      | FT            | -    | FSMC_A17,TIM4_CH1,<br>USART3_RTS, EVENTOUT                                   | -                       |

| -      | -         | 60      | 82      | 101     | M15      | PD13                                                 | I/O      | FT            | -    | FSMC_A18,TIM4_CH2,<br>EVENTOUT                                               | -                       |

| -      | -         | -       | 83      | 102     | -        | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| -      | -         | -       | 84      | 103     | J13      | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| -      | -         | 61      | 85      | 104     | M14      | PD14                                                 | I/O      | FT            | -    | FSMC_D0,TIM4_CH3,<br>EVENTOUT                                                | -                       |

| -      | -         | 62      | 86      | 105     | L14      | PD15                                                 | I/O      | FT            | -    | FSMC_D1,TIM4_CH4,<br>EVENTOUT                                                | -                       |

| -      | -         | -       | 87      | 106     | L15      | PG2                                                  | I/O      | FT            | -    | FSMC_A12, EVENTOUT                                                           | -                       |

| -      | -         | -       | 88      | 107     | K15      | PG3                                                  | I/O      | FT            | -    | FSMC_A13, EVENTOUT                                                           | -                       |

| -      | -         | -       | 89      | 108     | K14      | PG4                                                  | I/O      | FT            | -    | FSMC_A14, EVENTOUT                                                           | -                       |

| -      | -         | -       | 90      | 109     | K13      | PG5                                                  | I/O      | FT            | I    | FSMC_A15, EVENTOUT                                                           | -                       |

| -      | -         | -       | 91      | 110     | J15      | PG6                                                  | I/O      | FT            | -    | FSMC_INT2, EVENTOUT                                                          | -                       |

| -      | -         | -       | 92      | 111     | J14      | PG7                                                  | I/O      | FT            | -    | FSMC_INT3 ,USART6_CK,<br>EVENTOUT                                            | -                       |

| -      | -         | -       | 93      | 112     | H14      | PG8                                                  | I/O      | FT            | -    | USART6_RTS,<br>ETH_PPS_OUT,<br>EVENTOUT                                      | -                       |

| -      | -         | -       | 94      | 113     | G12      | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| -      | -         | -       | 95      | 114     | H13      | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| 37     | G2        | 63      | 96      | 115     | H15      | PC6                                                  | I/O      | FT            | -    | I2S2_MCK, TIM8_CH1,<br>SDIO_D6, USART6_TX,<br>DCMI_D0, TIM3_CH1,<br>EVENTOUT | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

# 6 Electrical characteristics

#### 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 17*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 18*.

#### 6.1.6 Power supply scheme

Figure 19. Power supply scheme

1. Each power supply pair must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

2. To connect REGOFF and IRROFF pins, refer to Section 3.16: Voltage regulator.

3. The two 2.2  $\mu\text{F}$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

4. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB, to ensure good device operation. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect device operation.

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Мах  | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| N                                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| M                                       | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

| Table 19. Embedded reset and power control block characteristics (continued) |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

1. Guaranteed by design, not tested in production.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

#### 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 20: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using  ${\sf CoreMark}^{\textcircled{R}}$  code.

| Peripheral <sup>(1)</sup> |                     | Typical consumption at 25 °C | Unit |  |

|---------------------------|---------------------|------------------------------|------|--|

|                           | SDIO                | 0.69                         |      |  |

|                           | TIM1                | 1.06                         |      |  |

|                           | TIM8                | 1.03                         |      |  |

| APB2                      | TIM9                | 0.58                         |      |  |

|                           | TIM10               | 0.37                         |      |  |

|                           | TIM11               | 0.39                         | mA   |  |

| AFDZ                      | ADC1 <sup>(4)</sup> | 2.13                         | ША   |  |

|                           | ADC2 <sup>(4)</sup> | 2.04                         |      |  |

|                           | ADC3 <sup>(4)</sup> | 2.12                         |      |  |

|                           | SPI1                | 1.20                         |      |  |

|                           | USART1              | 0.38                         |      |  |

|                           | USART6              | 0.37                         |      |  |

| Table 26. Peri | pheral current | consumption | (continued) |

|----------------|----------------|-------------|-------------|

|                |                |             | (           |

1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

2. EN1 bit is set in DAC\_CR register.

3. EN2 bit is set in DAC\_CR register.

4.  $f_{ADC} = f_{PCLK2}/2$ , ADON bit set in ADC\_CR2 register.

#### 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                              | Parameter                                                                                    | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|-------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep mode                                                                       | -                  | 1                  | -                  | μs   |

|                                     | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |      |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | us   |

| WUSTOP                              | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | F -  |

| twustdby <sup>(2)(3)</sup>          | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs   |

1. Guaranteed by characterization results, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and -45 °C, respectively.

| Symbol                          | Parameter                                        | Conditions                         | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                                    | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C       | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V            | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | 28 KB) erase time $V_{PP} = 8.5 V$ |                    | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                                    | -                  | 6.9 | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                              | -                                  | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                                  | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                                  | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                                  | -                  | -   | 1                  | hour |

Table 39. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 40. Flash memory endurance and data retention

1. Guaranteed by characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

#### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing  $\text{EEMBC}^{\textcircled{R}}$  code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                  | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |

|------------------|------------|-----------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|------|

|                  |            |                                                                             | nequency band               | 25/120 MHz                                       |      |

|                  |            | $V_{1} = 2.2 V_{1} = 25 \circ C_{1} OED 176$                                | 0.1 to 30 MHz               |                                                  |      |

| S <sub>EMI</sub> | Peak level | $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, LQFP176 package, conforming to SAE J1752/3 | 30 to 130 MHz               | 25                                               | dBµV |

|                  |            |                                                                             | 130 MHz to 1GHz             |                                                  |      |

|                  |            |                                                                             | SAE EMI Level               | 4                                                | -    |

|                  |            |                                                                             | 0.1 to 30 MHz               | 28                                               |      |

|                  |            |                                                                             | 30 to 130 MHz               | 26                                               | dBµV |

|                  |            | EEMBC, code running with ART<br>enabled, PLL spread spectrum                | 130 MHz to 1GHz             | 22                                               |      |

|                  |            | enabled, peripheral clock disabled                                          | SAE EMI level               | 4                                                | -    |

| Table 42. EMI characte | ristics |

|------------------------|---------|

|------------------------|---------|

#### 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | ymbol Ratings Conditions                                 |                                                   | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|---------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model) | $T_A = +25 \ ^{\circ}C$ conforming to JESD22-A114 | 2     | 2000 <sup>(2)</sup>             | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model)    | $T_A = +25 \ ^{\circ}C$ conforming to JESD22-C101 | II    | 500                             | V    |

| Table 43. ESI | ) absolute | maximum | ratings |

|---------------|------------|---------|---------|

|---------------|------------|---------|---------|

1. Guaranteed by characterization results, not tested in production.

2. On  $V_{BAT}$  pin,  $V_{ESD(HBM)}$  is limited to 1000 V.

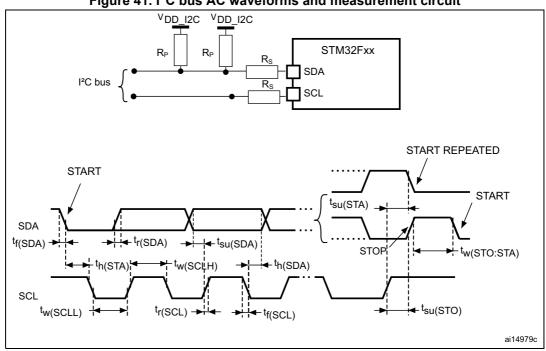

1. R<sub>S</sub>= series protection resistor.

2. R<sub>P</sub> = external pull-up resistor.

3.  $V_{DD \ I2C}$  is the I<sup>2</sup>C bus power supply.

| Table 53. SCL frequency (f <sub>F</sub> | <sub>PCLK1</sub> = 30 MHz.,V <sub>DD</sub> = 3.3 V) <sup>(1)(2)</sup> |

|-----------------------------------------|-----------------------------------------------------------------------|

| f. (kHz)                                | I2C_CCR value                                                         |

| f <sub>SCL</sub> (kHz)                  | R <sub>P</sub> = 4.7 kΩ                                               |

| 400                                     | 0x8019                                                                |

| 300                                     | 0x8021                                                                |

| 200                                     | 0x8032                                                                |

| 100                                     | 0x0096                                                                |

| 50                                      | 0x012C                                                                |

| 20                                      | 0x02EE                                                                |

#### ----... (1)(2)

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

#### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |

Table 56. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym            | bol                                                                   | Parameter                                                 | Conditions                                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|----------------|-----------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|--------------------|------|--------------------|------|

|                | V <sub>DD</sub>                                                       | USB OTG FS operating voltage                              |                                                                  | 3.0 <sup>(2)</sup> | -    | 3.6                | V    |

| Input          | V <sub>DI</sub> <sup>(3)</sup>                                        | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                | -    | -                  |      |

| levels         | V <sub>CM</sub> <sup>(3)</sup>                                        | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                | -    | 2.5                | V    |

|                | $V_{SE}^{(3)}$                                                        | Single ended receiver threshold                           |                                                                  | 1.3                | -    | 2.0                |      |

| Output         | V <sub>OL</sub>                                                       | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 V $^{(4)}$               | -                  | -    | 0.3                | v    |

| levels         | V <sub>OH</sub>                                                       | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                | -    | 3.6                | v    |

| Б              |                                                                       | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V - V                                                            | 17                 | 21   | 24                 |      |

|                | $R_{PD} = V_{IN} = V_{DD}$ $PA9, PB13$ $(OTG_FS_VBUS,$ $OTG_HS_VBUS)$ |                                                           | 0.65                                                             | 1.1                | 2.0  | kΩ                 |      |

|                |                                                                       | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                | 1.8  | 2.1                |      |

| R <sub>F</sub> | νU                                                                    | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25               | 0.37 | 0.55               |      |

#### Table 57. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4.  $R_L$  is the load connected on the USB OTG FS drivers

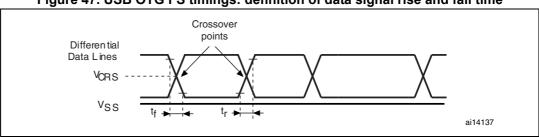

#### Figure 47. USB OTG FS timings: definition of data signal rise and fall time

#### Table 58. USB OTG FS electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                 |                                |     |     |      |  |

|------------------------|---------------------------------|--------------------------------|-----|-----|------|--|

| Symbol                 | Parameter                       | Conditions                     | Min | Max | Unit |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |

| t <sub>rfm</sub>       | Rise/fall time matching         | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |

| V <sub>CRS</sub>       | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |  |

1. Guaranteed by design, not tested in production.

2. Measured from 10% to 90% of the data signal. For more detailed informations, refer to USB Specification - Chapter 7 (version 2.0).

#### **USB HS characteristics**

Table 59 shows the USB HS operating voltage.

#### Table 59. USB HS DC electrical characteristics

| Symbol      |          | Parameter                    | Min <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|-------------|----------|------------------------------|--------------------|--------------------|------|

| Input level | $V_{DD}$ | USB OTG HS operating voltage | 2.7                | 3.6                | V    |

1. All the voltages are measured from the local ground potential.

#### Table 60. Clock timing parameters

| Parameter <sup>(1)</sup>                                                           |                     | Symbol                  | Min   | Nominal | Max   | Unit |

|------------------------------------------------------------------------------------|---------------------|-------------------------|-------|---------|-------|------|

| Frequency (first transition)                                                       | 8-bit ±10%          | F <sub>START_8BIT</sub> | 54    | 60      | 66    | MHz  |

| Frequency (steady state) ±500 ppm                                                  |                     | F <sub>STEADY</sub>     | 59.97 | 60      | 60.03 | MHz  |

| Duty cycle (first transition) 8-bit ±10%                                           |                     | D <sub>START_8BIT</sub> | 40    | 50      | 60    | %    |

| Duty cycle (steady state) ±500                                                     | D <sub>STEADY</sub> | 49.975                  | 50    | 50.025  | %     |      |

| Time to reach the steady state frequency and duty cycle after the first transition |                     | T <sub>STEADY</sub>     | -     | -       | 1.4   | ms   |

| Clock startup time after the                                                       | Peripheral          | T <sub>START_DEV</sub>  | -     | -       | 5.6   | ms   |

| de-assertion of SuspendM                                                           | Host                | T <sub>START_HOST</sub> | -     | -       | -     | 1115 |

| PHY preparation time after the of the input clock                                  | first transition    | T <sub>PREP</sub>       | -     | -       | -     | μs   |

1. Guaranteed by design, not tested in production.

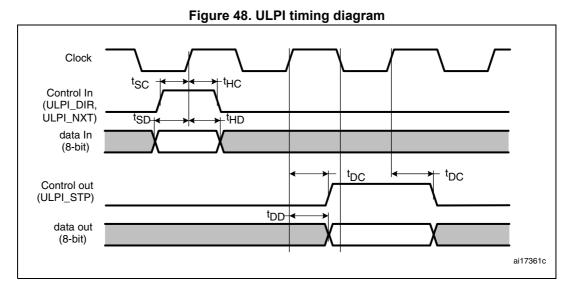

Table 61. ULPI timing

| Symbol          | Parameter                                       | Valu | Unit |      |

|-----------------|-------------------------------------------------|------|------|------|

| Symbol          | Farameter                                       | Min  | Max  | Unit |

| +               | Control in (ULPI_DIR) setup time                | -    | 2.0  |      |

| t <sub>SC</sub> | Control in (ULPI_NXT) setup time                | -    | 1.5  |      |

| t <sub>HC</sub> | Control in (ULPI_DIR, ULPI_NXT) hold time       | 0    | -    |      |

| t <sub>SD</sub> | Data in setup time                              | -    | 2.0  | ns   |

| t <sub>HD</sub> | Data in hold time                               | 0    | -    |      |

| t <sub>DC</sub> | Control out (ULPI_STP) setup time and hold time | -    | 9.2  |      |

| t <sub>DD</sub> | Data out available from clock rising edge       | -    | 10.7 |      |

1.  $V_{DD}$  = 2.7 V to 3.6 V and  $T_A$  = -40 to 85 °C.

#### Ethernet characteristics

Table 62 shows the Ethernet operating voltage.

#### Table 62. Ethernet DC electrical characteristics

| Symb        | ol              | Parameter                  | Min <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|-------------|-----------------|----------------------------|--------------------|--------------------|------|

| Input level | V <sub>DD</sub> | Ethernet operating voltage | 2.7                | 3.6                | V    |

1. All the voltages are measured from the local ground potential.

*Table 63* gives the list of Ethernet MAC signals for the SMI (station management interface) and *Figure 49* shows the corresponding timing diagram.

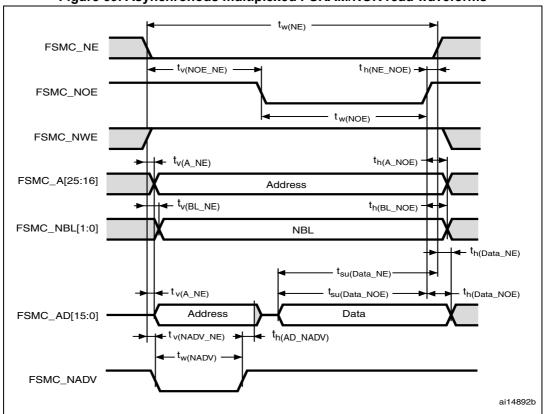

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

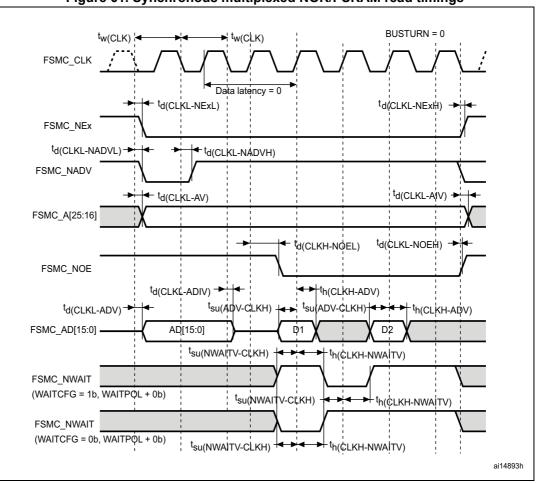

Figure 61. Synchronous multiplexed NOR/PSRAM read timings

| able 76. Synchronous multiplexed NOR/PSRAM read timings <sup>(1)(2)</sup> | (2) |

|---------------------------------------------------------------------------|-----|

| able ro. Oynemonous multiplexed North Orthan read unings                  |     |

| Symbol                     | Parameter                                 | Min                | Мах | Unit |

|----------------------------|-------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                           | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)       | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)     | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low             | -                  | 1.5 | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high            | 2.5                | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)    | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)  | 0                  | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low             | -                  | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high             | 1                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] valid       | -                  | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid 0 - |                    |     |      |

DocID15818 Rev 15

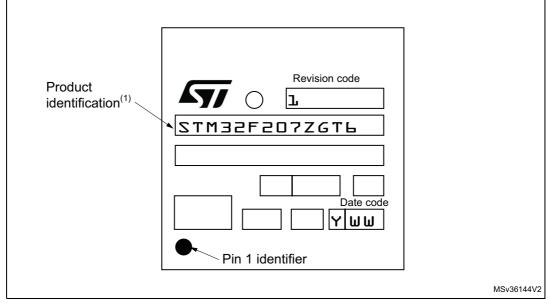

#### **Device marking**

*Figure 86* gives an example of topside marking orientation versus Pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

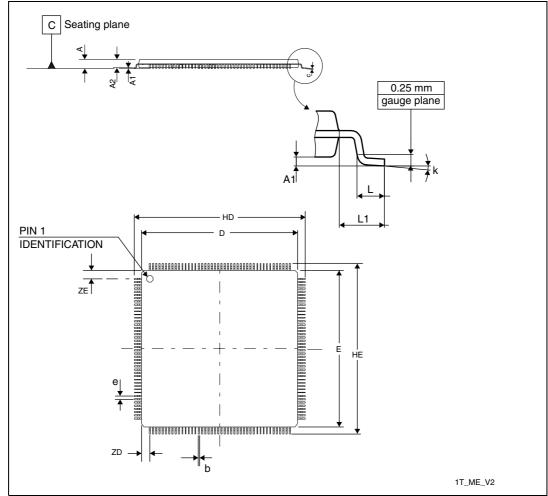

## 7.5 LQFP176 package information

Figure 87. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

| Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

|        | Dimensions  |     |        |                       |     |        |

|--------|-------------|-----|--------|-----------------------|-----|--------|

| Symbol | millimeters |     |        | inches <sup>(1)</sup> |     |        |

|        | Min         | Тур | Мах    | Min                   | Тур | Max    |

| Α      | -           | -   | 1.600  | -                     | -   | 0.0630 |

| A1     | 0.050       | -   | 0.150  | 0.0020                | -   | 0.0059 |

| A2     | 1.350       | -   | 1.450  | 0.0531                | -   | 0.0571 |

| b      | 0.170       | -   | 0.270  | 0.0067                | -   | 0.0106 |

| с      | 0.090       | -   | 0.200  | 0.0035                | -   | 0.0079 |

| D      | 23.900      | -   | 24.100 | 0.9409                | -   | 0.9488 |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |          | In the whole document, updated notes related to WLCSP64+2 usage with IRROFF set to V <sub>DD</sub> . Updated Section 3.14: Power supply schemes, Section 3.15: Power supply supervisor, Section 3.16.1: Regulator ON and Section 3.16.2: Regulator OFF. Added Section 3.16.3: Regulator ON/OFF and internal reset ON/OFF availability. Added note related to WLCSP64+2 package.                                                                              |  |  |

|             |          | Restructured RTC features and added reference clock detection in <i>Section 3.17: Real-time clock (RTC), backup SRAM and backup registers.</i>                                                                                                                                                                                                                                                                                                               |  |  |

|             |          | Added note indicating the package view below <i>Figure 10:</i> STM32F20x<br>LQFP64 pinout, Figure 12: STM32F20x LQFP100 pinout, Figure 13:<br>STM32F20x LQFP144 pinout, and Figure 14: STM32F20x LQFP176<br>pinout.                                                                                                                                                                                                                                          |  |  |

|             |          | Added Table 7: Legend/abbreviations used in the pinout table. Table 8:<br>STM32F20x pin and ball definitions: content reformatted; removed<br>indexes on $V_{SS}$ and $V_{DD}$ ; updated PA4, PA5, PA6, PC4, BOOT0;<br>replaced DCMI_12 by DCMI_D12, TIM8_CHIN by TIM8_CH1N,<br>ETH_MII_RX_D0 by ETH_MII_RXD0, ETH_MII_RX_D1 by<br>ETH_MII_RXD1, ETH_RMII_RX_D0 by ETH_RMII_RXD0,<br>ETH_RMII_RX_D1 by ETH_RMII_RXD1, and RMII_CRS_DV by<br>ETH_RMII_CRS_DV. |  |  |

| 04-Nov-2013 | 11       | <i>Table 10: Alternate function mapping</i> : replaced FSMC_BLN1 by FSMC_NBL1, added EVENTOUT as AF15 alternated function for PC13, PC14, PC15, PH0, PH1, and Pl8.                                                                                                                                                                                                                                                                                           |  |  |

|             |          | Updated Figure 17: Pin loading conditions and Figure 18: Pin input voltage.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|             |          | Added V <sub>IN</sub> in <i>Table 14: General operating conditions</i> .                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|             |          | Removed note applying to V <sub>POR/PDR</sub> minimum value in <i>Table 19:</i><br><i>Embedded reset and power control block characteristics</i> .                                                                                                                                                                                                                                                                                                           |  |  |

|             |          | Updated notes related to $C_{L1}$ and $C_{L2}$ in Section : Low-speed external clock generated from a crystal/ceramic resonator.                                                                                                                                                                                                                                                                                                                             |  |  |

|             |          | Updated conditions in <i>Table 41: EMS characteristics</i> . Updated <i>Table 42: EMI characteristics</i> . Updated $V_{IL}$ , $V_{IH}$ and $V_{Hys}$ in <i>Table 46: I/O static characteristics</i> . Added Section : Output driving currentand updated Figure 39: I/O AC characteristics definition.                                                                                                                                                       |  |  |

|             |          | Updated V <sub>IL(NRST)</sub> and V <sub>IH(NRST)</sub> in <i>Table 49: NRST pin characteristics</i> , updated <i>Figure 39: I/O AC characteristics definition</i> .                                                                                                                                                                                                                                                                                         |  |  |

|             |          | Removed tests conditions in <i>Section : I2C interface characteristics</i> .<br>Updated <i>Table 52: I2C characteristics</i> and <i>Figure 41: I2C bus AC</i><br><i>waveforms and measurement circuit</i> .                                                                                                                                                                                                                                                  |  |  |

|             |          | Updated I <sub>VREF+</sub> and I <sub>VDDA</sub> in <i>Table 66: ADC characteristics</i> . Updated Offset comments in <i>Table 68: DAC characteristics</i> .                                                                                                                                                                                                                                                                                                 |  |  |

|             |          | Updated minimum t <sub>h(CLKH-DV)</sub> value in <i>Table 78: Synchronous non-multiplexed NOR/PSRAM read timings</i> .                                                                                                                                                                                                                                                                                                                                       |  |  |