Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 100K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

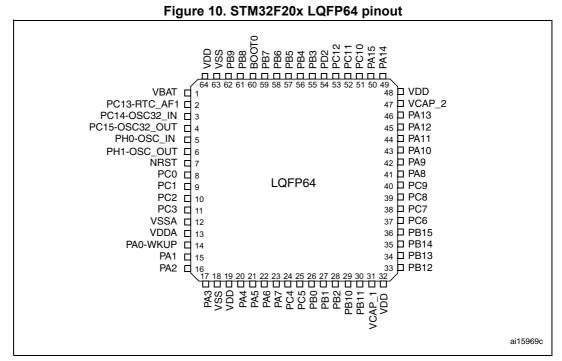

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205rct7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 93. | UFBGA176+25, - 201-ball, 10 x 10 mm, 0.65 mm pitch,          |     |

|-----------|--------------------------------------------------------------|-----|

|           | ultra fine pitch ball grid array package mechanical data     | 166 |

|           | UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA) |     |

| Table 95. | Package thermal characteristics                              | 169 |

| Table 96. | Ordering information scheme                                  | 170 |

| Table 97. | Document revision history                                    | 171 |

|            | recommended footprint                                                    | 161 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 86. | LQFP144 marking (package top view)                                       | 162 |

| Figure 87. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      | 163 |

| Figure 88. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |     |

|            | recommended footprint                                                    | 165 |

| Figure 89. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |     |

|            | ultra fine pitch ball grid array package outline                         | 166 |

| Figure 90. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

|            | grid array package recommended footprint                                 | 167 |

| Figure 91. | UFBGA176+25 marking (package top view)                                   | 168 |

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode

- LPR is used in Stop modes

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost).

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 19: Power supply scheme* and *Table 16: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

## 3.16.2 Regulator OFF

This feature is available only on packages featuring the REGOFF pin. The regulator is disabled by holding REGOFF high. The regulator OFF mode allows to supply externally a V12 voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

The two 2.2 µF ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 19: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset the part of the 1.2 V logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used at power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection at reset or pre-reset is required.

#### **Regulator OFF/internal reset ON**

On WLCSP64+2 package, this mode is activated by connecting REGOFF pin to V<sub>DD</sub> and IRROFF pin to V<sub>SS</sub>. On UFBGA176 package, only REGOFF must be connected to V<sub>DD</sub> (IRROFF not available). In this mode,  $V_{DD}/V_{DDA}$  minimum value is 1.8 V.

The regulator OFF/internal reset ON mode allows to supply externally a 1.2 V voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins, in addition to V<sub>DD</sub>.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or the  $V_{BAT}$  pin.

## 3.18 Low-power modes

The STM32F20x family supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped when the device enters the Stop or Standby mode.

# 3.19 V<sub>BAT</sub> operation

The  $V_{\text{BAT}}$  pin allows to power the device  $V_{\text{BAT}}$  domain from an external battery or an external supercapacitor.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When using WLCSP64+2 package, if IRROFF pin is connected to  $V_{DD}$ , the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

# 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                     | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| purpose              | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM9            | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| purpose              | TIM12           | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 30<br>MHz                 | 60<br>MHz             |

Table 5. Timer feature comparison

## 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

## 3.34 ADCs (analog-to-digital converters)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers TIM1, TIM2, TIM3, TIM4, TIM5 and TIM8 can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

# 3.35 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

DocID15818 Rev 15

# 4 Pinouts and pin description

1. The above figure shows the package top view.

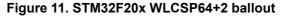

|   | 1    | 2      | 3      | 4   | 5   | 6     | 7      | 8      | 9                |

|---|------|--------|--------|-----|-----|-------|--------|--------|------------------|

| А | PA14 | PA15   | PC12   | PB3 | PB5 | PB7   | PB9    | VDD    | V <sub>BAT</sub> |

| В | VSS  | PA13   | PC10   | PB4 | PB6 | BOOT0 | PB8    | PC13   | PC14             |

| С | PA12 | VCAP_2 | PC11   |     |     |       | PD2    | IRROFF | PC15             |

| D | PC9  | PA11   | PA10   |     |     |       | PC2    | VSS    | VDD              |

| E | VDD  | PA8    | PA9    |     |     |       | PA0    | NRST   | PH0-<br>OSC_IN   |

| F | VSS  | PC7    | PC8    |     |     |       | VREF+  | PC1    | PH1-<br>OSC_OUT  |

| G | PB15 | PC6    | PC5    |     |     |       | PA3    | PC3    | PC0              |

| н | PB14 | PB13   | PB10   | PC4 | PA6 | PA5   | REGOFF | PA1    | VSS_5            |

| J | PB12 | PB11   | VCAP_1 | PB2 | PB1 | PB0   | PA7    | PA4    | PA2              |

|   |      |        |        |     |     |       |        |        |                  |

|   |      |        |        |     |     |       |        |        |                  |

1. The above figure shows the package top view.

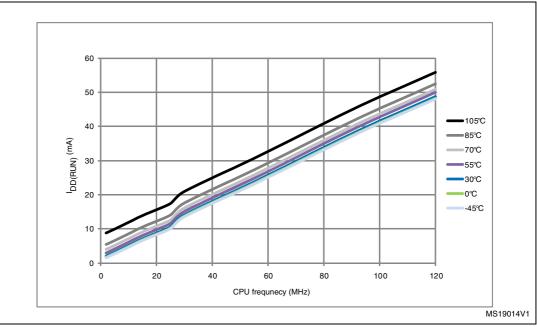

Figure 23. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals ON

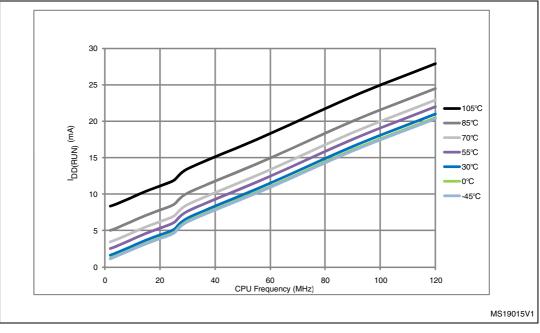

Figure 24. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals OFF

|                      |                                                   |                                                      | Тур                        |                            | Ма                         |                        |                         |      |

|----------------------|---------------------------------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|-------------------------|------|

| Symbol               | Parameter                                         | Conditions                                           | T                          | A = 25 °C                  | C                          | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                      |                                                   |                                                      | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V                 |      |

|                      | Supply current<br>I <sub>DD_STBY</sub> in Standby | Backup SRAM ON, low-speed<br>oscillator and RTC ON   | 3.0                        | 3.4                        | 4.0                        | 15.1                   | 25.8                    |      |

| I <sub>DD_STBY</sub> |                                                   | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                        | 2.7                        | 3.3                        | 12.4                   | 20.5                    | μA   |

| mode                 | Backup SRAM ON, RTC OFF                           | 2.4                                                  | 2.6                        | 3.0                        | 12.5                       | 24.8                   |                         |      |

|                      |                                                   | Backup SRAM OFF, RTC OFF                             | 1.7                        | 1.9                        | 2.2                        | 9.8                    | 19.2                    |      |

| Table 24. Typical and maximum current consumptions in S | Standby mode |

|---------------------------------------------------------|--------------|

|---------------------------------------------------------|--------------|

1. Guaranteed by characterization results, not tested in production.

| Table 2 | 25. Typical and maximum cu | rrent consumptions in | n V <sub>BAT</sub> mode |

|---------|----------------------------|-----------------------|-------------------------|

|         |                            |                       |                         |

|                      |                                                    |                                                     |                            | Тур                        |                            | Ма                     | ıx <sup>(1)</sup>       |      |

|----------------------|----------------------------------------------------|-----------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|-------------------------|------|

| Symbol               | Parameter                                          | Conditions                                          | Т                          | A = 25 °                   | С                          | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                      |                                                    |                                                     | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V                 |      |

|                      | Backup SRAM ON, low-speed<br>oscillator and RTC ON | 1.29                                                | 1.42                       | 1.68                       | 12                         | 19                     |                         |      |

| I <sub>DD_VBAT</sub> | Backup<br>DD_VBAT<br>domain supply<br>current      | Backup SRAM OFF, low-speed<br>oscillator and RTC ON | 0.62                       | 0.73                       | 0.96                       | 8                      | 10                      | μA   |

|                      |                                                    | Backup SRAM ON, RTC OFF                             | 0.79                       | 0.81                       | 0.86                       | 9                      | 16                      |      |

|                      |                                                    | Backup SRAM OFF, RTC OFF                            | 0.10                       | 0.10                       | 0.10                       | 5                      | 7                       |      |

1. Guaranteed by characterization results, not tested in production.

## **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 26*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- The code is running from Flash memory and the Flash memory access time is equal to 3 wait states at 120 MHz

- Prefetch and Cache ON

- When the peripherals are enabled, HCLK = 120MHz,  $f_{PCLK1}$  =  $f_{HCLK}/4,$  and  $f_{PCLK2}$  =  $f_{HCLK}/2$

- The typical values are obtained for V\_{DD} = 3.3 V and T\_A= 25  $^\circ\text{C},$  unless otherwise specified.

| Symbol              | Parameter                   | Conditions                    | Min | Тур  | Max | Unit |  |  |  |  |

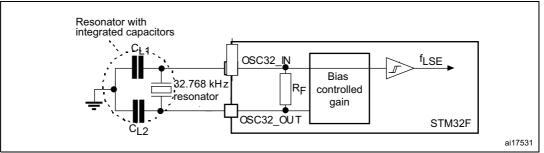

|---------------------|-----------------------------|-------------------------------|-----|------|-----|------|--|--|--|--|

| R <sub>F</sub>      | Feedback resistor           | -                             | -   | 18.4 | -   | MΩ   |  |  |  |  |

| I <sub>DD</sub>     | LSE current consumption     | -                             | -   | -    | 1   | μA   |  |  |  |  |

| 9 <sub>m</sub>      | Oscillator Transconductance | -                             | 2.8 | -    | -   | μA/V |  |  |  |  |

| $t_{SU(LSE)}^{(2)}$ | startup time                | $V_{\text{DD}}$ is stabilized | -   | 2    | -   | S    |  |  |  |  |

Table 31. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 33. Typical application with a 32.768 kHz crystal

## 6.3.9 Internal clock source characteristics

The parameters given in *Table 32* and *Table 33* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user-trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

| 100                                 |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  | Accuracy of the<br>HSI oscillator     | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4.0 | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

Table 32. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

| Symbol                                  | Parameter                                    | Conditions                                                         | Min                                                          | Тур          | Мах  | Unit         |    |

|-----------------------------------------|----------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|--------------|------|--------------|----|

|                                         |                                              | Cycle to cycle at                                                  | RMS                                                          | -            | 90   | -            |    |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                       | peak<br>to<br>peak                                           | -            | ±280 | -            | ps |

| Jitter <sup>(3)</sup>                   |                                              | Average frequency o<br>12.288 MHz<br>N=432, R=5<br>on 1000 samples | f                                                            | -            | 90   | -            | ps |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 k<br>on 1000 samples                          | <hz< td=""><td>-</td><td>400</td><td>-</td><td>ps</td></hz<> | -            | 400  | -            | ps |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                           |                                                              | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                           |                                                              | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA |

## Table 35. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design, not tested in production.

3. Value given with main PLL running.

4. Guaranteed by characterization results, not tested in production.

## 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 42: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 26  | 0000 | noromotoro | aanatraint |

|-----------|------|------------|------------|

| Table 30. | 3366 | parameters | constraint |

1. Guaranteed by design, not tested in production.

#### **Equation 1**

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized}$ % = (250 × 126 × 100 × 5)/ ((2<sup>15</sup> - 1) × 240) = 2.0002%(peak)

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup>    | Symbol                                                                          | Parameter                                                                       | Conditions                                          | Min | Тур | Мах                | Unit |

|--------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|--------------------|------|

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 25                 |      |

|                                                  | f                                                                               |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 12.5               | MHz  |

|                                                  | <sup>I</sup> max(IO)out                                                         |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 50 <sup>(3)</sup>  |      |

| 01                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 |      |

| 01                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> >2.7 V      | -   | -   | 10                 |      |

|                                                  | t <sub>f(IO)out</sub> /                                                         | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 | 20   |

|                                                  | t <sub>r(IO)out</sub>                                                           | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 6                  | ns   |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 10                 |      |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 25                 |      |

|                                                  | f <sub>max(IO)out</sub>                                                         | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 20                 | MHz  |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 100 <sup>(3)</sup> |      |

| 10                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 50 <sup>(3)</sup>  |      |

| 10                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 6                  |      |

|                                                  | t <sub>f(IO)out</sub> /                                                         | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 10                 | ns   |

|                                                  | t <sub>r(IO)out</sub>                                                           |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 4                  |      |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -3  | 6                  |      |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 100 <sup>(3)</sup> | MHz  |

|                                                  | £                                                                               | Marian (2)                                                                      | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 50 <sup>(3)</sup>  |      |

|                                                  | Imax(IO)out                                                                     | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 120 <sup>(3)</sup> |      |

| 11                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 100 <sup>(3)</sup> |      |

| 11                                               |                                                                                 |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 4                  |      |

| t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V                              | -                                                   | -   | 6   |                    |      |

|                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V                             | -                                                   | -   | 2.5 | ns                 |      |

|                                                  |                                                                                 |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 4                  |      |

| -                                                | t <sub>EXTIpw</sub>                                                             | Pulse width of external<br>signals detected by the<br>EXTI controller           | -                                                   | 10  | -   | -                  | ns   |

Table 48. I/O AC characteristics<sup>(1)</sup> (continued)

The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F20/21xxx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

2. The maximum frequency is defined in *Figure 39*.

3. For maximum frequencies above 50 MHz and  $V_{\text{DD}}$  above 2.4 V, the compensation cell should be used.

being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.16 does not affect the ADC accuracy.

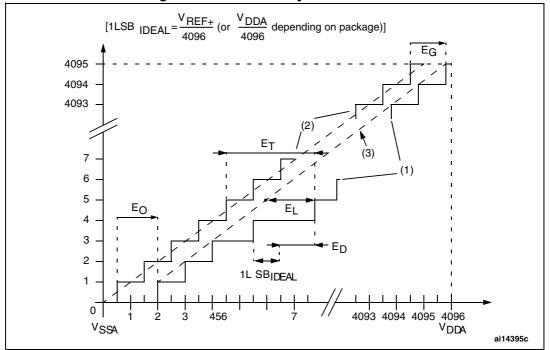

- Example of an actual transfer curve 1.

- 2. Ideal transfer curve

- 3. End point correlation line.

- $E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 4. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

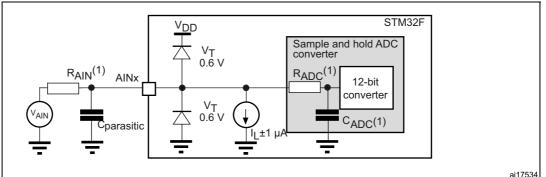

Figure 53. Typical connection diagram using the ADC

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

Refer to Table 66 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

| Symbol                    | Parameter                             | Min                     | Max                  | Unit |

|---------------------------|---------------------------------------|-------------------------|----------------------|------|

| t <sub>h(A_NWE)</sub>     | Address hold time after FSMC_NWE high | T <sub>HCLK</sub> – 0.5 | -                    | ns   |

| t <sub>h(BL_NWE)</sub>    | FSMC_BL hold time after FSMC_NWE high | T <sub>HCLK</sub> - 1   | -                    | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid         | -                       | 0.5                  | ns   |

| t <sub>v(Data_NADV)</sub> | FSMC_NADV high to Data valid          | -                       | T <sub>HCLK</sub> +2 | ns   |

| t <sub>h(Data_NWE)</sub>  | Data hold time after FSMC_NWE high    | Т <sub>НСLК</sub> – 0.5 | -                    | ns   |

Table 75. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

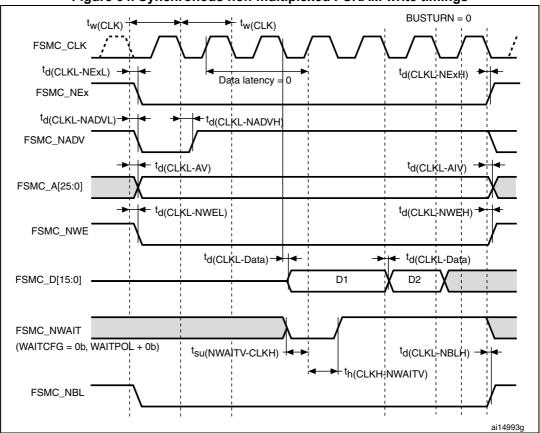

### Synchronous waveforms and timings

*Figure 61* through *Figure 64* represent synchronous waveforms, and *Table 77* through *Table 79* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F20xxx/21xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the  $T_{\mbox{HCLK}}$  is the HCLK clock period.

| -                          |                                              | -   | •   |      |

|----------------------------|----------------------------------------------|-----|-----|------|

| Symbol                     | Parameter                                    | Min | Max | Unit |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high               | 4   | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -   | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 3   | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low                | -   | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                | 1.5 | -   | ns   |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK high | 8   | -   | ns   |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

## Table 78. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

## Figure 64. Synchronous non-multiplexed PSRAM write timings

### Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                             | Min                    | Max | Unit |

|---------------------------|---------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>       | FSMC_CLK period                       | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub> | FSMC_CLK low to FSMC_NEx low (x=02)   | -                      | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub> | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                      | -   | ns   |

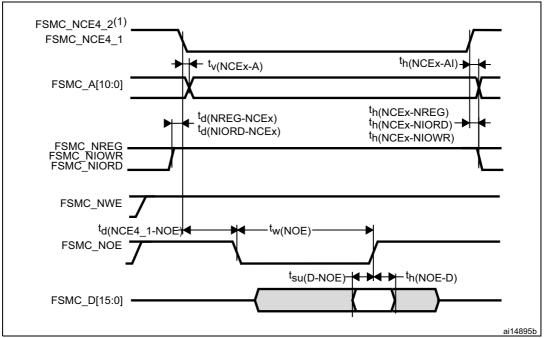

Figure 65. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

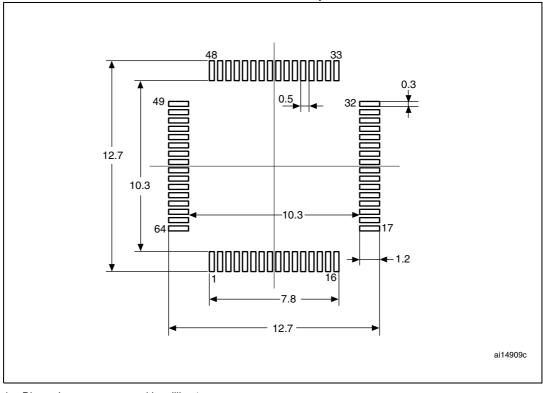

| Symbol | millimeters |        | inches <sup>(1)</sup> |        |        |        |

|--------|-------------|--------|-----------------------|--------|--------|--------|

| Зушьог | Min         | Тур    | Мах                   | Min    | Тур    | Max    |

| С      | 0.090       | -      | 0.200                 | 0.0035 | -      | 0.0079 |

| D      | -           | 12.000 | -                     | -      | 0.4724 | -      |

| D1     | -           | 10.000 | -                     | -      | 0.3937 | -      |

| D3     | -           | 7.500  | -                     | -      | 0.2953 | -      |

| E      | -           | 12.000 | -                     | -      | 0.4724 | -      |

| E1     | -           | 10.000 | -                     | -      | 0.3937 | -      |

| E3     | -           | 7.500  | -                     | -      | 0.2953 | -      |

| е      | -           | 0.500  | -                     | -      | 0.0197 | -      |

| К      | 0°          | 3.5°   | 7°                    | 0°     | 3.5°   | 7°     |

| L      | 0.450       | 0.600  | 0.750                 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -                     | -      | 0.0394 | -      |

| CCC    | -           | -      | 0.080                 | -      | -      | 0.0031 |

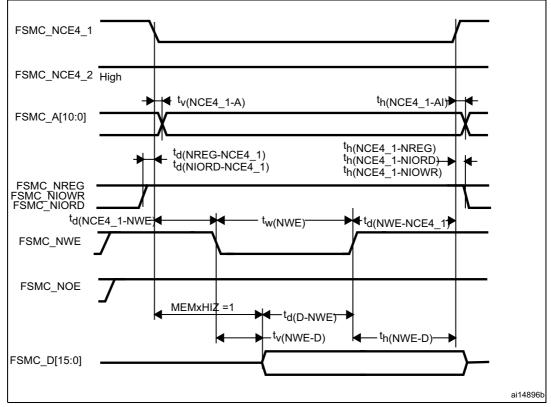

# Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

| Symbol | millimeters |       |       |     |        |        |

|--------|-------------|-------|-------|-----|--------|--------|

| Зуший  | Min         | Тур   | Max   | Min | Тур    | Max    |

| e2     | -           | 3.200 | -     | -   | 0.1260 | -      |

| F      | -           | 0.220 | -     | -   | 0.0087 | -      |

| G      | -           | 0.386 | -     | -   | 0.0152 | -      |

| aaa    | -           | -     | 0.100 | -   | -      | 0.0039 |

| bbb    | -           | -     | 0.100 | -   | -      | 0.0039 |

| CCC    | -           | -     | 0.100 | -   | -      | 0.0039 |

| ddd    | -           | -     | 0.050 | -   | -      | 0.0020 |

| eee    | -           | -     | 0.050 | -   | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

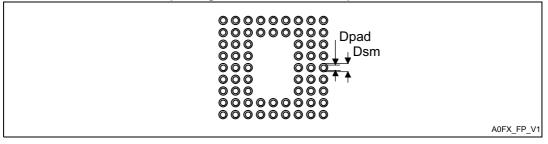

# Figure 80. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 89. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.4                                                              |

| Dpad              | 0.225 mm                                                         |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.250 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

| Table 97. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 14-Jun-2011                                     | 7        | Added SDIO in <i>Table 2: STM32F205xx features and peripheral counts.</i><br>Updated V <sub>IN</sub> for 5V tolerant pins in <i>Table 11: Voltage characteristics.</i><br>Updated jitter parameters description in <i>Table 34: Main PLL characteristics.</i><br>Remove jitter values for system clock in <i>Table 35: PLLI2S (audio PLL) characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Note 2</i> in <i>Table 52: I2C characteristics.</i><br>Updated Avg_Slope typical value and $T_{S\_temp}$ minimum value in <i>Table 69: Temperature sensor characteristics.</i><br>Updated $T_{S\_vbat}$ minimum value in <i>Table 70: VBAT monitoring characteristics.</i><br>Updated $T_{S\_vrefint}$ minimum value in <i>Table 71: Embedded internal reference voltage.</i><br>Added Software option in <i>Section 8: Ordering information.</i><br>In <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers,</i> renamed USB1 and USB2, USB OTG FS and USB OTG HS, respectively; and removed USB OTG HS on 64-pin package; added <i>Note 1</i> and <i>Note 2.</i>                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 20-Dec-2011                                     | 8        | Updated SDIO register addresses in <i>Figure 16: Memory map.</i><br>Updated <i>Figure 3: Compatible board design between STM32F10x and</i><br><i>STM32F2xx for LQFP144 package, Figure 2: Compatible board design</i><br><i>between STM32F10x and STM32F2xx for LQFP100 package, Figure 1:</i><br><i>Compatible board design between STM32F10x and STM32F2xx for</i><br><i>LQFP64 package, and added Figure 4: Compatible board design</i><br><i>between STM32F10xx and STM32F2xx for LQFP176 package.</i><br>Updated <i>Section 3.3: Memory protection unit.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.28: Universal serial bus on-the-go full-speed</i><br>( <i>OTG_FS</i> ) to remove external FS OTG PHY support.<br>In <i>Table 8: STM32F20x pin and ball definitions</i> : changed SPI2_MCK<br>and SPI3_MCK to I2S2_MCK and I2S3_MCK, respectively. Added ETH<br>_RMII_TX_EN alternate function to PG11. Added EVENTOUT in the list<br>of alternate functions for I/O pin/balls. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions.<br>In <i>Table 10: Alternate function mapping</i> : changed I2S3_SCK to<br>I2S3_MCK for PC7/AF6, added FSMC_NCE3 for PG9, FSMC_NE3 for<br>PG10, and FSMC_NCE2 for PD7. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions. Changed<br>I2S3_SCK into I2S3_MCK for PC7/AF6. Updated peripherals<br>corresponding to AF12.<br>Removed CEXT and ESR from <i>Table 14: General operating conditions</i> . |  |

Table 97. Document revision history (continued)