Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 132K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205ret7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

STM32F20xxx Contents

# **Contents**

| 1 | Intro | duction                                                                         | 13 |

|---|-------|---------------------------------------------------------------------------------|----|

| 2 | Desc  | ription                                                                         | 14 |

|   | 2.1   | Full compatibility throughout the family                                        | 18 |

| 3 | Func  | tional overview                                                                 | 21 |

|   | 3.1   | $ARM^{\mathbb{B}}$ Cortex $^{\mathbb{B}}$ -M3 core with embedded Flash and SRAM | 21 |

|   | 3.2   | Adaptive real-time memory accelerator (ART Accelerator™)                        | 21 |

|   | 3.3   | Memory protection unit                                                          | 21 |

|   | 3.4   | Embedded Flash memory                                                           | 22 |

|   | 3.5   | CRC (cyclic redundancy check) calculation unit                                  | 22 |

|   | 3.6   | Embedded SRAM                                                                   | 22 |

|   | 3.7   | Multi-AHB bus matrix                                                            | 22 |

|   | 3.8   | DMA controller (DMA)                                                            | 23 |

|   | 3.9   | Flexible static memory controller (FSMC)                                        | 24 |

|   | 3.10  | Nested vectored interrupt controller (NVIC)                                     | 24 |

|   | 3.11  | External interrupt/event controller (EXTI)                                      | 25 |

|   | 3.12  | Clocks and startup                                                              | 25 |

|   | 3.13  | Boot modes                                                                      | 25 |

|   | 3.14  | Power supply schemes                                                            | 25 |

|   | 3.15  | Power supply supervisor                                                         | 26 |

|   | 3.16  | Voltage regulator                                                               | 26 |

|   |       | 3.16.1 Regulator ON                                                             | 26 |

|   |       | 3.16.2 Regulator OFF                                                            | 27 |

|   |       | 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability                  | 31 |

|   | 3.17  | Real-time clock (RTC), backup SRAM and backup registers                         | 31 |

|   | 3.18  | Low-power modes                                                                 | 32 |

|   | 3.19  | V <sub>BAT</sub> operation                                                      | 32 |

|   | 3.20  | Timers and watchdogs                                                            | 33 |

|   |       | 3.20.1 Advanced-control timers (TIM1, TIM8)                                     | 33 |

|   |       | 3.20.2 General-purpose timers (TIMx)                                            |    |

|   |       | 3.20.3 Basic timers TIM6 and TIM7                                               | 34 |

|   |       |                                                                                 |    |

| Contents | STM32F20xxx |

|----------|-------------|

|----------|-------------|

| 9 | Revi | sion history                    |

|---|------|---------------------------------|

| 8 | Orde | ering information170            |

|   | 7.7  | Thermal characteristics         |

|   | 7.6  | UFBGA176+25 package information |

|   | 7.5  | LQFP176 package information     |

|   | 7.4  | LQFP144 package information     |

|   |      |                                 |

List of figures STM32F20xxx

# **List of figures**

| Figure 1.  | Compatible board design between STM32F10x and STM32F2xx                            |    |

|------------|------------------------------------------------------------------------------------|----|

|            | for LQFP64 package                                                                 | 18 |

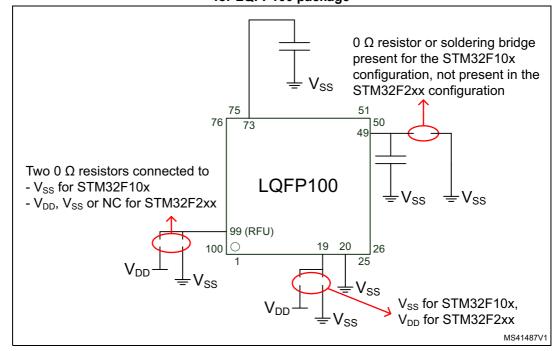

| Figure 2.  | Compatible board design between STM32F10x and STM32F2xx for LQFP100 package        | 10 |

| Eiguro 3   | Compatible board design between STM32F10x and STM32F2xx                            | 19 |

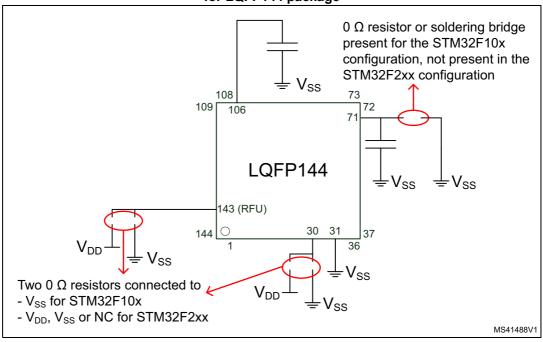

| Figure 3.  | for LQFP144 package                                                                | 10 |

| Figure 4.  | STM32F20x block diagram                                                            |    |

| Figure 5.  | Multi-AHB matrix                                                                   |    |

| Figure 6.  | Regulator OFF/internal reset ON                                                    |    |

| Figure 7.  | Regulator OFF/internal reset OFF                                                   |    |

| Figure 8.  | Startup in regulator OFF: slow V <sub>DD</sub> slope,                              | 20 |

| i iguic o. | power-down reset risen after $V_{CAP}$ $_1/V_{CAP}$ $_2$ stabilization             | 30 |

| Figure 9.  | Startup in regulator OFF: fast $V_{DD}$ slope,                                     | 00 |

| ga. o o.   | power-down reset risen before V <sub>CAP 1</sub> /V <sub>CAP 2</sub> stabilization | 30 |

| Figure 10. | STM32F20x LQFP64 pinout                                                            |    |

| Figure 11. | STM32F20x WLCSP64+2 ballout.                                                       |    |

| Figure 12. | STM32F20x LQFP100 pinout                                                           |    |

| Figure 13. | STM32F20x LQFP144 pinout                                                           |    |

| Figure 14. | STM32F20x LQFP176 pinout                                                           |    |

| Figure 15. | STM32F20x UFBGA176 ballout                                                         |    |

| Figure 16. | Memory map                                                                         |    |

| Figure 17. | Pin loading conditions                                                             |    |

| Figure 18. | Pin input voltage                                                                  |    |

| Figure 19. | Power supply scheme                                                                |    |

| Figure 20. | Current consumption measurement scheme                                             |    |

| Figure 21. | Number of wait states versus f <sub>CPU</sub> and V <sub>DD</sub> range            |    |

| Figure 22. | External capacitor C <sub>FXT</sub>                                                |    |

| Figure 23. | Typical current consumption vs. temperature, Run mode, code with data              |    |

| · ·        | processing running from RAM, and peripherals ON                                    | 81 |

| Figure 24. | Typical current consumption vs. temperature, Run mode, code with data              |    |

|            | processing running from RAM, and peripherals OFF                                   | 81 |

| Figure 25. | Typical current consumption vs. temperature, Run mode, code with data              |    |

| _          | processing running from Flash, ART accelerator OFF, peripherals ON                 | 82 |

| Figure 26. | Typical current consumption vs. temperature, Run mode, code with data              |    |

|            | processing running from Flash, ART accelerator OFF, peripherals OFF                | 82 |

| Figure 27. | Typical current consumption vs. temperature in Sleep mode,                         |    |

|            | peripherals ON                                                                     | 84 |

| Figure 28. | Typical current consumption vs. temperature in Sleep mode,                         |    |

|            | peripherals OFF                                                                    |    |

| Figure 29. | Typical current consumption vs. temperature in Stop mode                           |    |

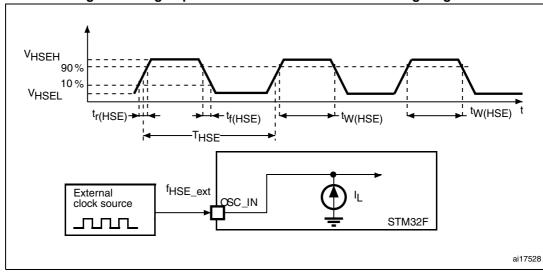

| Figure 30. | High-speed external clock source AC timing diagram                                 |    |

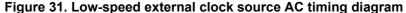

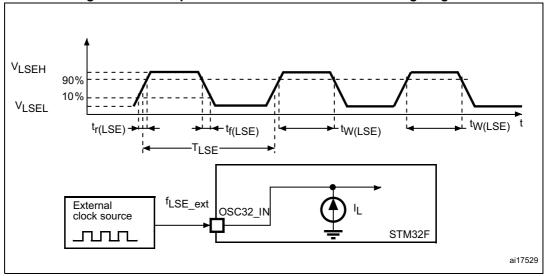

| Figure 31. | Low-speed external clock source AC timing diagram                                  |    |

| Figure 32. | Typical application with an 8 MHz crystal                                          |    |

| Figure 33. | Typical application with a 32.768 kHz crystal                                      |    |

| Figure 34. | ACC <sub>HSI</sub> versus temperature                                              |    |

| Figure 35. | ACC <sub>LSI</sub> versus temperature                                              |    |

| Figure 36. | PLL output clock waveforms in center spread mode                                   |    |

| Figure 37. | PLL output clock waveforms in down spread mode                                     | 99 |

Description STM32F20xxx

## 2 Description

The STM32F20x family is based on the high-performance ARM® Cortex®-M3 32-bit RISC core operating at a frequency of up to 120 MHz. The family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 128 Kbytes of system SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

The devices also feature an adaptive real-time memory accelerator (ART Accelerator™) that allows to achieve a performance equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 120 MHz. This performance has been validated using the CoreMark® benchmark.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true number random generator (RNG). They also feature standard and advanced communication interfaces. New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), and a camera interface for CMOS sensors. The devices also feature standard peripherals.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external PLL to allow synchronization.

- Four USARTs and two UARTs

- A USB OTG high-speed with full-speed capability (with the ULPI)

- A second USB OTG (full-speed)

- Two CANs

- An SDIO interface

- Ethernet and camera interface available on STM32F207xx devices only.

Note:

The STM32F205xx and STM32F207xx devices operate in the -40 to +105 °C temperature range from a 1.8 V to 3.6 V power supply. On devices in WLCSP64+2 package, if IRROFF is set to  $V_{DD}$ , the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

A comprehensive set of power-saving modes allow the design of low-power applications.

STM32F205xx and STM32F207xx devices are offered in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen. These features make the STM32F205xx and STM32F207xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- · Alarm systems, video intercom, and HVAC

- Home audio appliances

Figure 4 shows the general block diagram of the device family.

14/184 DocID15818 Rev 15

| Table 2. STM32F205xx features and peripheral counts (co | continued) |

|---------------------------------------------------------|------------|

|---------------------------------------------------------|------------|

| Peripherals            | STI                                                                                        | W32F205Rx               | C          |                         | STM32F205Vx | STM32F205Zx |  |  |

|------------------------|--------------------------------------------------------------------------------------------|-------------------------|------------|-------------------------|-------------|-------------|--|--|

| Operating temperatures | Ambient temperatures: -40 to +85 °C /-40 to +105 °C  Junction temperature: -40 to + 125 °C |                         |            |                         |             |             |  |  |

| Package                | LQFP64                                                                                     | LQFP64<br>WLCSP64<br>+2 | LQFP6<br>4 | LQFP64<br>WLCSP6<br>4+2 |             | LQFP144     |  |  |

- For the LQFP100 package, only FSMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

- 2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

- On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

### Table 3. STM32F207xx features and peripheral counts

| Peripherals             |                         | STM32F207Vx |                 |     | STM32F207Zx |     |     |     | STM32F207lx      |     |     |     |      |

|-------------------------|-------------------------|-------------|-----------------|-----|-------------|-----|-----|-----|------------------|-----|-----|-----|------|

| Flash memory in Kbytes  |                         | 256         | 512             | 768 | 1024        | 256 | 512 | 768 | 1024             | 256 | 512 | 768 | 1024 |

| SRAM in Kbytes          | System<br>(SRAM1+SRAM2) |             | 128<br>(112+16) |     |             |     |     |     |                  |     |     |     |      |

| -                       | Backup                  |             | 4               |     |             |     |     |     |                  |     |     |     |      |

| FSMC memory co          | ntroller                |             |                 |     |             |     |     | Yes | s <sup>(1)</sup> |     |     |     |      |

| Ethernet                |                         | Yes         |                 |     |             |     |     |     |                  |     |     |     |      |

|                         | General-purpose         | 10          |                 |     |             |     |     |     |                  |     |     |     |      |

|                         | Advanced-control        |             |                 |     |             |     | 2   |     |                  |     |     |     |      |

| Timers                  | Basic                   | 2           |                 |     |             |     |     |     |                  |     |     |     |      |

|                         | IWDG                    | Yes         |                 |     |             |     |     |     |                  |     |     |     |      |

|                         | WWDG                    | Yes         |                 |     |             |     |     |     |                  |     |     |     |      |

| RTC                     |                         | Yes         |                 |     |             |     |     |     |                  |     |     |     |      |

| Random number generator |                         | Yes         |                 |     |             |     |     |     |                  |     |     |     |      |

STM32F20xxx Description

Figure 2. Compatible board design between STM32F10x and STM32F2xx for LQFP100 package

1. RFU = reserved for future use.

Figure 3. Compatible board design between STM32F10x and STM32F2xx for LQFP144 package

1. RFU = reserved for future use.

Functional overview STM32F20xxx

in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock, 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 19: Power supply scheme for more details.

## 3.15 Power supply supervisor

The devices have an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry.

At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR threshold levels, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit. On devices in WLCSP64+2 package, the BOR, POR and PDR features can be disabled by setting IRROFF pin to  $V_{DD}$ . In this mode an external power supply supervisor is required (see Section 3.16).

The devices also feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.16 Voltage regulator

The regulator has five operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

- Regulator OFF/internal reset ON

- Regulator OFF/internal reset OFF

### 3.16.1 Regulator ON

The regulator ON modes are activated by default on LQFP packages. On WLCSP64+2 package, they are activated by connecting both REGOFF and IRROFF pins to V $_{\rm SS}$ , while only REGOFF must be connected to V $_{\rm SS}$  on UFBGA176 package (IRROFF is not available).

V<sub>DD</sub> minimum value is 1.8 V.

577

## Table 10. Alternate function mapping (continued)

|        |      |            |               |                 | 1 -                 |                       | 1                     |                  |                   | 1               |                   |                        |                                      |                          |              |       |          |

|--------|------|------------|---------------|-----------------|---------------------|-----------------------|-----------------------|------------------|-------------------|-----------------|-------------------|------------------------|--------------------------------------|--------------------------|--------------|-------|----------|

|        | Port | AF0<br>SYS | AF1<br>TIM1/2 | AF2<br>TIM3/4/5 | AF3<br>TIM8/9/10/11 | AF4<br>I2C1/I2C2/I2C3 | AF5<br>SPI1/SPI2/I2S2 | AF6<br>SPI3/I2S3 | AF7<br>USART1/2/3 | AF8<br>UART4/5/ | AF9<br>CAN1/CAN2/ | AF10<br>OTG_FS/ OTG_HS | AF11<br>ETH                          | AF12<br>FSMC/SDIO/       | AF13<br>DCMI | AF014 | AF15     |

|        |      | 515        | 1 IIW11/2     | 111/13/4/5      | 1110/9/10/11        | 1201/1202/1203        | 5P11/5P12/1252        | 5PI3/I253        | USAR11/2/3        | USART6          | TIM12/13/14       | OIG_FS/OIG_HS          | EIR                                  | OTG_HS                   | DCMI         |       |          |

|        | PF0  | -          | -             | -               | -                   | I2C2_SDA              | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A0                  | -            | -     | EVENTOUT |

|        | PF1  | -          | -             | -               | -                   | I2C2_SCL              |                       | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A1                  | -            | -     | EVENTOUT |

|        | PF2  | -          | -             | -               | -                   | I2C2_SMBA             | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A2                  | -            | -     | EVENTOUT |

|        | PF3  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A3                  | =            | -     | EVENTOUT |

|        | PF4  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A4                  | -            | -     | EVENTOUT |

|        | PF5  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A5                  | -            | -     | EVENTOUT |

|        | PF6  | -          | -             | -               | TIM10_CH1           | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_NIORD               | -            | -     | EVENTOUT |

| Port F | PF7  | -          | -             | -               | TIM11_CH1           | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_NREG                | -            | -     | EVENTOUT |

| Port F | PF8  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | TIM13_CH1         | -                      | -                                    | FSMC_NIOWR               | -            | -     | EVENTOUT |

|        | PF9  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | TIM14_CH1         | -                      | -                                    | FSMC_CD                  | -            | -     | EVENTOUT |

|        | PF10 | =          | =             | -               | =                   | =                     | -                     | =                | -                 | =               | -                 | -                      | Ξ                                    | FSMC_INTR                | =            | -     | EVENTOUT |

|        | PF11 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | =                                    |                          | DCMI_D12     | -     | EVENTOUT |

|        | PF12 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A6                  | -            | -     | EVENTOUT |

|        | PF13 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A7                  | -            | -     | EVENTOUT |

|        | PF14 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A8                  | -            | -     | EVENTOUT |

|        | PF15 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_A9                  | -            | -     | EVENTOUT |

|        | PG0  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A10                 | =            | -     | EVENTOUT |

|        | PG1  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A11                 | =            | -     | EVENTOUT |

|        | PG2  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A12                 | =            | -     | EVENTOUT |

|        | PG3  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A13                 | =            | -     | EVENTOUT |

|        | PG4  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A14                 | =            | -     | EVENTOUT |

|        | PG5  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | -               | -                 | -                      | =                                    | FSMC_A15                 | =            | -     | EVENTOUT |

|        | PG6  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_INT2                | -            | -     | EVENTOUT |

|        | PG7  | =          | =             | -               | -                   | =                     | -                     | =                | -                 | USART6_CK       | -                 | -                      | =                                    | FSMC_INT3                | =            | -     | EVENTOUT |

| Port G | PG8  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | USART6_RTS      | -                 | -                      | ETH_PPS_OUT                          | -                        | -            | -     | EVENTOUT |

|        | PG9  | -          | -             | -               | -                   | -                     | -                     | -                | -                 | USART6_RX       | -                 | -                      | -                                    | FSMC_NE2/<br>FSMC_NCE3   | -            | -     | EVENTOUT |

|        | PG10 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | -                                    | FSMC_NCE4_1/<br>FSMC_NE3 | =            | -     | EVENTOUT |

|        | PG11 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | -               | -                 | -                      | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | FSMC_NCE4_2              | -            | -     | EVENTOUT |

|        | PG12 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | USART6_RTS      | -                 | -                      | -                                    | FSMC_NE4                 | -            | -     | EVENTOUT |

|        | PG13 | =          | -             | -               | -                   | -                     | -                     | -                | -                 | UART6_CTS       | -                 | -                      | ETH_MII_TXD0<br>ETH_RMII_TXD0        | FSMC_A24                 | =            | -     | EVENTOUT |

|        | PG14 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | USART6_TX       | -                 | -                      | ETH_MII_TXD1<br>ETH_RMII_TXD1        | FSMC_A25                 | -            | -     | EVENTOUT |

|        | PG15 | -          | -             | -               | -                   | -                     | -                     | -                | -                 | USART6_CTS      | -                 | -                      | -                                    | -                        | DCMI_D13     | -     | EVENTOUT |

## 6.1.7 Current consumption measurement

IDD\_VBAT VBAT VDD VDD VDDA

Figure 20. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                       | Min                                                      | Max                | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|------|

| $V_{DD}$ – $V_{SS}$               | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                     | 4.0                |      |

| V <sub>IN</sub>                   | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4 | V    |

|                                   | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3                                     | 4.0                |      |

| $ \Delta V_{DDx} $                | Variations between different V <sub>DD</sub> power pins                       | -                                                        | 50                 | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                              | -                                                        | 50                 | IIIV |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                            | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum            | -    |

Table 11. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to Table 12 for the values of the maximum allowed injected current.

Figure 30. High-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 30*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

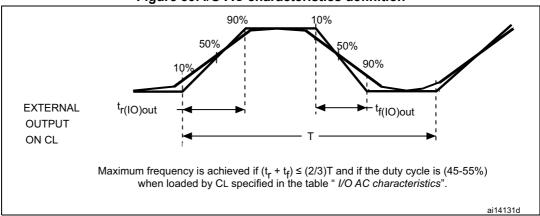

Figure 39. I/O AC characteristics definition

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 49).

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under the ambient temperature and  $\ensuremath{V_{DD}}$  supply voltage conditions summarized in Table 14.

|                                      |                                                 | •                       |     |     |     |      |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

Table 49. NRST pin characteristics

2. Guaranteed by design, not tested in production.

√<u>D</u>D External reset circuit (1) RPU NRST(2) Internal Reset Filter STM32F ai14132c

Figure 40. Recommended NRST pin protection

- The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in Table 49. Otherwise the reset is not taken into account by the device.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

| Symbol                 | Parameter                       | Conditions                                                      | Min    | Max                     | Unit                 |

|------------------------|---------------------------------|-----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>120 MHz | 8.3    | -                       | ns                   |

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 60 MHz                 | 16.7   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            |                                                                 | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXI                   | frequency on CH1 to CH4         |                                                                 | 0      | 60                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                 | -      | 16                      | bit                  |

| +                      | 16-bit counter clock period     | $f_{TIMxCLK} = 120 \text{ MHz}$ $APB2 = 60 \text{ MHz}$         | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | AFB2 = 00 WI 12                                                 | 0.0083 | 546                     | μs                   |

| tury count             | Maximum possible count          |                                                                 | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | IMAXIMUM POSSIDIE COUNT         |                                                                 | -      | 35.79                   | S                    |

Table 51. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

### 6.3.19 Communications interfaces

## I<sup>2</sup>C interface characteristics

STM32F205xx and STM32F207xx  $I^2$ C interface meets the requirements of the standard  $I^2$ C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 52*. Refer also to *Section 6.3.16: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

112/184 DocID15818 Rev 15

<sup>1.</sup> TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

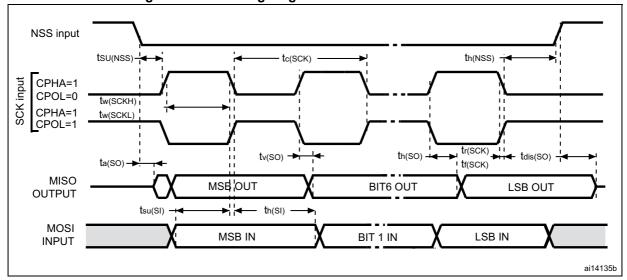

## I<sup>2</sup>S - SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 54* for SPI or in *Table 55* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKX}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 54. SPI characteristics

| Symbol                                               | Parameter                        | Conditions                                                | Min                  | Max                  | Unit |  |

|------------------------------------------------------|----------------------------------|-----------------------------------------------------------|----------------------|----------------------|------|--|

| f <sub>SCK</sub>                                     | SPI clock frequency              | SPI1 master/slave mode                                    | -                    | 30                   | MHz  |  |

| 1/t <sub>c(SCK)</sub>                                | SF1 clock frequency              | SPI2/SPI3 master/slave mode                               | -                    | 15                   |      |  |

| t <sub>r(SCL)</sub>                                  | SPI clock rise and fall time     | Capacitive load: C = 30 pF,<br>f <sub>PCLK</sub> = 30 MHz | -                    | 8                    | ns   |  |

| DuCy(SCK)                                            | SPI slave input clock duty cycle | Slave mode                                                | 30                   | 70                   | %    |  |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time                   | Slave mode                                                | 4t <sub>PCLK</sub>   | -                    |      |  |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                    | Slave mode                                                | 2t <sub>PCLK</sub>   | -                    |      |  |

| t <sub>w(SCLH)</sub> (1)<br>t <sub>w(SCLL)</sub> (1) | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 30 MHz,<br>presc = 2     | t <sub>PCLK</sub> -3 | t <sub>PCLK</sub> +3 |      |  |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time            | Master mode                                               | 5                    | -                    |      |  |

|                                                      | Data input setup time            | Slave mode                                                | 5                    | -                    |      |  |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time             | Master mode                                               | 5                    | -                    |      |  |

| t <sub>h(SI)</sub> (1)                               | Data input noid time             | Slave mode                                                | 4                    | -                    | ns   |  |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                 | Data output access time          | Slave mode, f <sub>PCLK</sub> = 30 MHz                    | 0                    | 3t <sub>PCLK</sub>   |      |  |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time         | Slave mode                                                | 2                    | 10                   |      |  |

| t <sub>v(SO)</sub> (1)                               | Data output valid time           | Slave mode (after enable edge)                            | -                    | 25                   |      |  |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time           | Master mode (after enable edge)                           | -                    | 5                    |      |  |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data output hold time            | Slave mode (after enable edge)                            | 15                   | -                    |      |  |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output noid time            | Master mode (after enable edge)                           | 2                    | -                    |      |  |

<sup>1.</sup> Guaranteed by characterization results, not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

NSS input tc(SCK) th(NSS) <sup>t</sup>SU(NSS) CPHA=0 CPOL=0 <sup>t</sup>w(SCKH) <sup>t</sup>w(SCKL) CPHA=0 CPOL=1 tr(SCK) th(SO) ta(SO) tv(SO) t<sub>dis(SO)</sub> tf(SCK) MISO MSB O UT BIT6 OUT LSB OUT OUTPUT tsu(SI) → MOSI LSB IN MSB IN BIT1 IN INPUT ·th(SI)· ai14134c

Figure 42. SPI timing diagram - slave mode and CPHA = 0

### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

Table 56. USB OTG FS startup time

| Symbol                              | Parameter                           | Max | Unit |  |

|-------------------------------------|-------------------------------------|-----|------|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |

<sup>1.</sup> Guaranteed by design, not tested in production.

Table 57. USB OTG FS DC electrical characteristics

| Symbol          |                                          | Parameter                                                           | Conditions                               | Min <sup>(1)</sup> Typ |      | Max <sup>(1)</sup> | Unit |  |

|-----------------|------------------------------------------|---------------------------------------------------------------------|------------------------------------------|------------------------|------|--------------------|------|--|

|                 | $V_{DD}$                                 | USB OTG FS operating voltage                                        |                                          | 3.0 <sup>(2)</sup>     | -    | 3.6                | V    |  |

| Input           | V <sub>DI</sub> <sup>(3)</sup>           | Differential input sensitivity                                      | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)         | 0.2                    | -    | -                  |      |  |

| levels          | V <sub>CM</sub> <sup>(3)</sup>           | Differential common mode range                                      | Includes V <sub>DI</sub> range           | 0.8                    | -    | 2.5                | V    |  |

|                 | V <sub>SE</sub> <sup>(3)</sup>           | Single ended receiver threshold                                     |                                          | 1.3                    | -    | 2.0                |      |  |

| Output          | V <sub>OL</sub>                          | Static output level low                                             | $R_L$ of 1.5 k $\Omega$ to 3.6 $V^{(4)}$ | -                      | -    | 0.3                | V    |  |

| levels          | V <sub>OH</sub> Static output level high |                                                                     | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$ | 2.8                    | -    | 3.6                | v    |  |

| R <sub>PD</sub> |                                          | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM)           | V <sub>IN</sub> = V <sub>DD</sub>        | 17                     | 21   | 24                 |      |  |

|                 |                                          | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                          | VIN - VDD                                | 0.65                   | 1.1  | 2.0                | kΩ   |  |

|                 |                                          | PA12, PB15 (USB_FS_DP, USB_HS_DP) V <sub>IN</sub> = V <sub>SS</sub> |                                          | 1.5                    | 1.8  | 2.1                |      |  |

|                 |                                          | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                          | V <sub>IN</sub> = V <sub>SS</sub>        | 0.25                   | 0.37 | 0.55               |      |  |

<sup>1.</sup> All the voltages are measured from the local ground potential.

120/184 DocID15818 Rev 15

<sup>2.</sup> The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $\rm V_{DD}$  voltage range.

<sup>3.</sup> Guaranteed by design, not tested in production.

<sup>4.</sup>  $R_L$  is the load connected on the USB OTG FS drivers

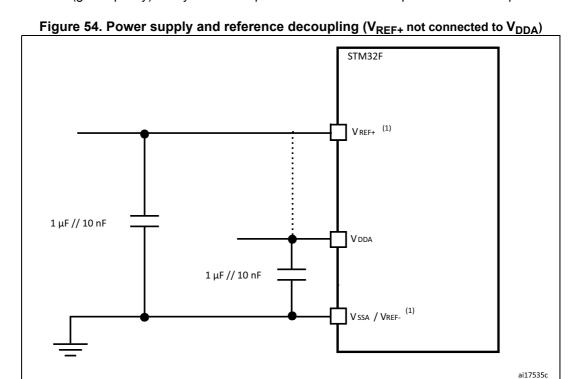

## General PCB design guidelines

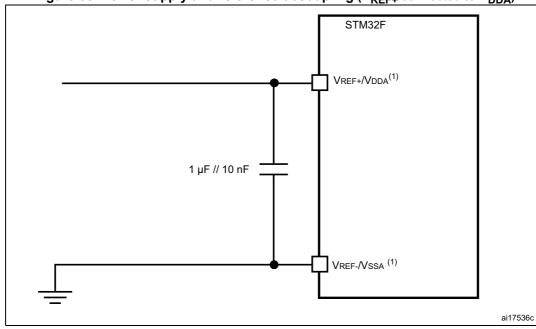

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

Figure 55. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

## 6.3.21 DAC electrical characteristics

**Table 68. DAC characteristics**

| Symbol                           | Parameter                             | Min                | Тур | Max                    | Unit | Comments                                                                                                                             |  |

|----------------------------------|---------------------------------------|--------------------|-----|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| $V_{DDA}$                        | Analog supply voltage                 | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | -                                                                                                                                    |  |

| V <sub>REF+</sub>                | Reference supply voltage              | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                                  |  |

| V <sub>SSA</sub>                 | Ground                                | 0                  | ı   | 0                      | V    | -                                                                                                                                    |  |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer ON         | 5                  | -   | -                      | kΩ   | -                                                                                                                                    |  |

| R <sub>O</sub> <sup>(2)</sup>    | Impedance output with buffer OFF      | -                  | -   | 15                     | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$              |  |

| C <sub>LOAD</sub> <sup>(2)</sup> | Capacitive load                       | -                  | -   | 50                     | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                      |  |

| DAC_OUT                          | Lower DAC_OUT voltage with buffer ON  | 0.2                | -   | -                      | V    | It gives the maximum output excursio of the DAC. It corresponds to 12-bit input code (0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V |  |

| DAC_OUT max <sup>(2)</sup>       | Higher DAC_OUT voltage with buffer ON | -                  | -   | V <sub>DDA</sub> – 0.2 | V    | and (0x1C7) to (0xE38) at V <sub>REF+</sub> = 1.8 V                                                                                  |  |

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

Unit **Symbol Parameter** Min Max T<sub>HCLK</sub>- 0.5 Address hold time after FSMC NWE high ns t<sub>h(A\_NWE)</sub> FSMC BL hold time after FSMC NWE high T<sub>HCLK</sub>- 1 ns t<sub>h(BL NWE)</sub> 0.5 FSMC\_NEx low to FSMC\_BL valid ns t<sub>v(BL NE)</sub> FSMC NADV high to Data valid T<sub>HCLK</sub>+2 ns t<sub>v(Data\_NADV)</sub> Data hold time after FSMC\_NWE high T<sub>HCLK</sub>- 0.5 t<sub>h(Data\_NWE)</sub> ns

Table 75. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup> (continued)

### Synchronous waveforms and timings

*Figure 61* through *Figure 64* represent synchronous waveforms, and *Table 77* through *Table 79* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- BurstAccessMode = FSMC\_BurstAccessMode\_Enable;

- MemoryType = FSMC\_MemoryType\_CRAM;

- WriteBurst = FSMC\_WriteBurst\_Enable;

- CLKDivision = 1; (0 is not supported, see the STM32F20xxx/21xxx reference manual)

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

In all timing tables, the T<sub>HCLK</sub> is the HCLK clock period.

<sup>1.</sup>  $C_L = 30 pF$ .

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

# 7.4 LQFP144 package information

SEATING P<u>LAN</u>E С 0.25 mm □ ccc C **GAUGE PLANE** D D1 D3 109 E3 E1 37 PIN 1 **IDENTIFICATION** 1A\_ME\_V4

Figure 84. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

STM32F20xxx Revision history

# 9 Revision history

Table 97. Document revision history

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Jun-2009   | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 09-Oct-2009   | 2        | Document status promoted from Target specification to Preliminary data.  In Table 8: STM32F20x pin and ball definitions:  - Note 4 updated  - V <sub>DD_SA</sub> and V <sub>DD_3</sub> pins inverted (Figure 12: STM32F20x LQFP100 pinout, Figure 13: STM32F20x LQFP144 pinout and Figure 14: STM32F20x LQFP176 pinout corrected accordingly).  Section: In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark. changed to LQFP with no exposed pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 01-Feb-2010   | 3        | LFBGA144 package removed. STM32F203xx part numbers removed. Part numbers with 128 and 256 Kbyte Flash densities added. Encryption features removed.  PC13-TAMPER-RTC renamed to PC13-RTC_AF1 and PI8-TAMPER-RTC renamed to PI8-RTC_AF2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13-Jul-2010 4 |          | Renamed high-speed SRAM, system SRAM. Removed combination: 128 KBytes Flash memory in LQFP144. Added UFBGA176 package. Added note 1 related to LQFP176 package in Table 2, Figure 14, and Table 96. Added information on ART accelerator and audio PLL (PLLI2S). Added Table 6: USART feature comparison. Several updates on Table 8: STM32F20x pin and ball definitions and Table 10: Alternate function mapping. ADC, DAC, oscillator, RTC_AF, WKUP and VBUS signals removed from alternate functions and moved to the "other functions" column in Table 8: STM32F20x pin and ball definitions. TRACESWO added in Figure 4: STM32F20x block diagram, Table 8: STM32F20x pin and ball definitions, and Table 10: Alternate function mapping. XTAL oscillator frequency updated on cover page, in Figure 4: STM32F20x block diagram and in Section 3.11: External interrupt/event controller (EXTI). Updated list of peripherals used for boot mode in Section 3.13: Boot modes. Added Regulator bypass mode in Section 3.16: Voltage regulator, and Section 6.3.4: Operating conditions at power-up / power-down (regulator OFF). Updated Section 3.17: Real-time clock (RTC), backup SRAM and backup registers. Added Note Note: in Section 3.18: Low-power modes. Added SPI TI protocol in Section 3.23: Serial peripheral interface (SPI). |