#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 114                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 100K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205zct6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 Embedded Flash memory

The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

# 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.6 Embedded SRAM

All STM32F20x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

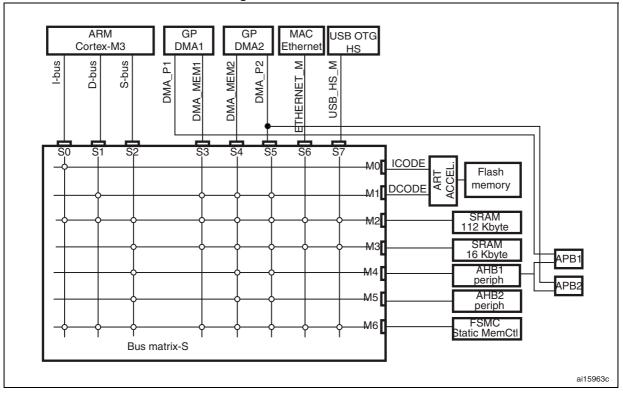

# 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

Figure 5. Multi-AHB matrix

## 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They share some centralized FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.26 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F207xx devices.

The STM32F207xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F207xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F207xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) or 50 MHz (RMII) output from the STM32F207xx.

The STM32F207xx includes the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F20x and STM32F21x reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes, that is 4 Kbytes in total

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

## 3.27 Controller area network (CAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one

DocID15818 Rev 15

## 3.30 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

## 3.31 Digital camera interface (DCMI)

The camera interface is not available in STM32F205xx devices.

STM32F207xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain up to 27 Mbyte/s at 27 MHz or 48 Mbyte/s at 48 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw Bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

## 3.32 True random number generator (RNG)

All STM32F2xxx products embed a true RNG that delivers 32-bit random numbers produced by an integrated analog circuit.

## 3.33 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O alternate function configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

To provide fast I/O handling, the GPIOs are on the fast AHB1 bus with a clock up to 120 MHz that leads to a maximum I/O toggling speed of 60 MHz.

## 3.37 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.38 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F20x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                      |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|----------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                  | Additional<br>functions |

| 54     | С7        | 83      | 116     | 144     | D12      | PD2                                                  | I/O      | FT            | -    | TIM3_ETR,UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                | -                       |

| -      | -         | 84      | 117     | 145     | D11      | PD3                                                  | I/O      | FT            | -    | FSMC_CLK,USART2_CTS,<br>EVENTOUT                                     | -                       |

| -      | -         | 85      | 118     | 146     | D10      | PD4                                                  | I/O      | FT            | -    | FSMC_NOE, USART2_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | 86      | 119     | 147     | C11      | PD5                                                  | I/O      | FT            | -    | FSMC_NWE,USART2_TX,<br>EVENTOUT                                      | -                       |

| -      | -         | -       | 120     | 148     | D8       | V <sub>SS</sub>                                      | S        | -             | ·    |                                                                      | -                       |

| -      | -         | -       | 121     | 149     | C8       | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                    | -                       |

| -      | -         | 87      | 122     | 150     | B11      | PD6                                                  | I/O      | FT            | -    | FSMC_NWAIT,<br>USART2_RX, EVENTOUT                                   | -                       |

| -      | -         | 88      | 123     | 151     | A11      | PD7                                                  | I/O      | FT            | -    | USART2_CK,FSMC_NE1,<br>FSMC_NCE2, EVENTOUT                           | -                       |

| -      | -         | -       | 124     | 152     | C10      | PG9                                                  | I/O      | FT            | -    | USART6_RX,<br>FSMC_NE2,FSMC_NCE3,<br>EVENTOUT                        | -                       |

| -      | -         | -       | 125     | 153     | B10      | PG10                                                 | I/O      | FT            | -    | FSMC_NCE4_1,<br>FSMC_NE3, EVENTOUT                                   | -                       |

| -      | -         | -       | 126     | 154     | В9       | PG11                                                 | I/O      | FT            | -    | FSMC_NCE4_2,<br>ETH_MII_TX_EN,<br>ETH_RMII_TX_EN,<br>EVENTOUT        | -                       |

| -      | -         | -       | 127     | 155     | B8       | PG12                                                 | I/O      | FT            | -    | FSMC_NE4, USART6_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | -       | 128     | 156     | A8       | PG13                                                 | I/O      | FT            | -    | FSMC_A24, USART6_CTS,<br>ETH_MII_TXD0,<br>ETH_RMII_TXD0,<br>EVENTOUT | -                       |

| -      | -         | -       | 129     | 157     | A7       | PG14                                                 | I/O      | FT            | -    | FSMC_A25, USART6_TX,<br>ETH_MII_TXD1,<br>ETH_RMII_TXD1,<br>EVENTOUT  | -                       |

| -      | -         | -       | 130     | 158     | D7       | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                    | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

STM32F20xxx

Pinouts and pin description

|        | Table 10. Alternate function mapping (continued) |     |        |          |              |                |                |           |            |                    |                           |                |                                     |                          |          |       |          |

|--------|--------------------------------------------------|-----|--------|----------|--------------|----------------|----------------|-----------|------------|--------------------|---------------------------|----------------|-------------------------------------|--------------------------|----------|-------|----------|

|        |                                                  | AF0 | AF1    | AF2      | AF3          | AF4            | AF5            | AF6       | AF7        | AF8                | AF9                       | AF10           | AF11                                | AF12                     | AF13     |       |          |

|        | Port                                             | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3 | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ETH                                 | FSMC/SDIO/<br>OTG_HS     | DCMI     | AF014 | AF15     |

|        | PF0                                              | -   | -      | -        | -            | I2C2_SDA       | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A0                  | -        | -     | EVENTOUT |

|        | PF1                                              | -   | -      | -        | -            | I2C2_SCL       |                | -         | -          | -                  | -                         | -              | -                                   | FSMC_A1                  | -        | -     | EVENTOUT |

|        | PF2                                              | -   | -      | -        | -            | I2C2_SMBA      | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A2                  | -        | -     | EVENTOUT |

|        | PF3                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A3                  | -        | -     | EVENTOUT |

|        | PF4                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A4                  | -        | -     | EVENTOUT |

|        | PF5                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A5                  | -        | -     | EVENTOUT |

|        | PF6                                              | -   | -      | -        | TIM10_CH1    | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_NIORD               | -        | -     | EVENTOUT |

|        | PF7                                              | -   | -      | -        | TIM11_CH1    | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_NREG                | -        | -     | EVENTOUT |

| Port F | PF8                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | TIM13_CH1                 | -              | -                                   | FSMC_NIOWR               | -        | -     | EVENTOUT |

|        | PF9                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | TIM14_CH1                 | -              | -                                   | FSMC_CD                  | -        | -     | EVENTOUT |

|        | PF10                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_INTR                | -        | -     | EVENTOUT |

|        | PF11                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   |                          | DCMI_D12 | -     | EVENTOUT |

|        | PF12                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A6                  | -        | -     | EVENTOUT |

|        | PF13                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A7                  | -        | -     | EVENTOUT |

|        | PF14                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A8                  | -        | -     | EVENTOUT |

|        | PF15                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A9                  | -        | -     | EVENTOUT |

|        | PG0                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A10                 | -        | -     | EVENTOUT |

|        | PG1                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A11                 | -        | -     | EVENTOUT |

|        | PG2                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A12                 | -        | -     | EVENTOUT |

|        | PG3                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A13                 | -        | -     | EVENTOUT |

|        | PG4                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A14                 | -        | -     | EVENTOUT |

|        | PG5                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_A15                 | -        | -     | EVENTOUT |

|        | PG6                                              | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_INT2                | -        | -     | EVENTOUT |

|        | PG7                                              | -   | -      | -        | -            | -              | -              | -         | -          | USART6_CK          | -                         | -              | -                                   | FSMC_INT3                | -        | -     | EVENTOUT |

| Port G | PG8                                              | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RTS         | -                         | -              | ETH _PPS_OUT                        | -                        | -        | -     | EVENTOUT |

|        | PG9                                              | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RX          | -                         | -              | -                                   | FSMC_NE2/<br>FSMC_NCE3   | -        | -     | EVENTOUT |

|        | PG10                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                   | FSMC_NCE4_1/<br>FSMC_NE3 | -        | -     | EVENTOUT |

|        | PG11                                             | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | ETH_MII_TX_EN<br>ETH<br>_RMII_TX_EN |                          | -        | -     | EVENTOUT |

|        | PG12                                             | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RTS         | -                         | -              |                                     | FSMC_NE4                 | -        | -     | EVENTOUT |

|        | PG13                                             | -   | -      | -        | -            | -              | -              | -         | -          | UART6_CTS          | -                         | -              | ETH_MII_TXD0<br>ETH_RMII_TXD0       | FSMC_A24                 | -        | -     | EVENTOUT |

|        | PG14                                             | -   | -      | -        | -            | -              | -              | -         | -          | USART6_TX          | -                         | -              | ETH_MII_TXD1<br>ETH_RMII_TXD1       | FSMC_A25                 | -        | -     | EVENTOUT |

|        | PG15                                             | -   | -      | -        | -            | -              | -              | -         | -          | USART6_CTS         | -                         | -              | -                                   | -                        | DCMI_D13 | -     | EVENTOUT |

Table 10. Alternate function mapping (continued)

DocID15818 Rev 15

65/10

5

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

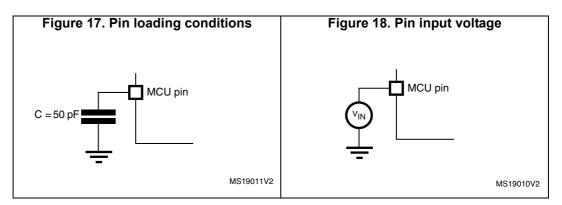

### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 17*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 18*.

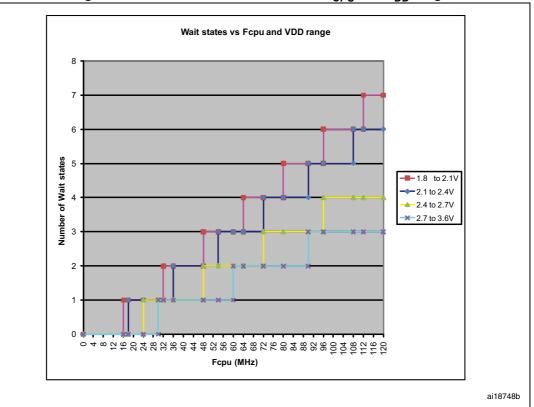

| Operating<br>power<br>supply<br>range            | ADC<br>operation                   | Maximum<br>Flash<br>memory<br>access<br>frequency<br>(f <sub>Flashmax</sub> ) | Number of wait<br>states at<br>maximum CPU<br>frequency<br>(f <sub>CPUmax</sub> =<br>120 MHz) <sup>(1)</sup> | I/O operation                                                                                          | FSMC_CLK<br>frequency for<br>synchronous<br>accesses                                                                                                                                                                                                          | Possible<br>Flash<br>memory<br>operations        |

|--------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.8 to<br>2.1 V <sup>(2)</sup>  | Conversion<br>time up to<br>1 Msps | 16 MHz with<br>no Flash<br>memory wait<br>state                               | 7 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded</li> <li>speed</li> <li>performance</li> <li>No I/O</li> <li>compensation</li> </ul> | Up to 30 MHz                                                                                                                                                                                                                                                  | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1 Msps | 18 MHz with<br>no Flash<br>memory wait<br>state                               | 6 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>                | Up to 30 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2 Msps | 24 MHz with<br>no Flash<br>memory wait<br>state                               | 4 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul>         | Up to 48 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(4)</sup> | Conversion<br>time up to<br>2 Msps | 30 MHz with<br>no Flash<br>memory wait<br>state                               | 3 <sup>(3)</sup>                                                                                             | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>                   | $\begin{array}{l} - \mbox{ Up to } \\ 60 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 3.0 \mbox{ to } 3.6 \mbox{ V} \\ - \mbox{ Up to } \\ 48 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 2.7 \mbox{ to } 3.0 \mbox{ V} \end{array}$ | 32-bit erase<br>and program<br>operations        |

Table 15. Limitations depending on the operating power supply range

1. The number of wait states can be reduced by reducing the CPU frequency (see Figure 21).

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

3. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

4. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70  $^\circ\text{C}$  temperature range and IRROFF is set to V\_DD.

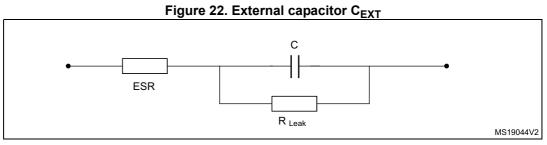

#### 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

#### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

| Symbol                               | Parameter                                   | Conditions                               |                                            | Min          | Тур  | Мах                                                          | Unit |

|--------------------------------------|---------------------------------------------|------------------------------------------|--------------------------------------------|--------------|------|--------------------------------------------------------------|------|

|                                      |                                             |                                          | RMS                                        | -            | 25   | Max<br>-<br>-<br>-<br>-<br>-<br>0.40<br>0.75<br>0.40<br>0.85 |      |

| Jitter <sup>(3)</sup>                | Cycle-to-cycle jitter                       | System clock                             | peak<br>to<br>peak                         | -            | ±150 | -                                                            |      |

|                                      |                                             | 120 MHz                                  | RMS                                        | -            | 15   | -                                                            |      |

|                                      | Period Jitter                               |                                          | peak<br>to<br>peak                         | -            | ±200 | -                                                            | ps   |

|                                      | Main clock output (MCO) for RMII Ethernet   | Cycle to cycle at 50 MHz on 1000 samples |                                            | -            | 32   | -                                                            |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet | Cycle to cycle at 25 MHz on 1000 samples |                                            | -            | 40   | -                                                            |      |

|                                      | Bit Time CAN jitter                         | Cycle to cycle at 1 on 1000 samples      | Cycle to cycle at 1 MHz<br>on 1000 samples |              |      | -                                                            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                | VCO freq = 192 MHz                       |                                            | 0.15         | -    |                                                              | mA   |

|                                      |                                             | VCO freq = 432 MI                        | Hz                                         | 0.45         |      | 0.75                                                         |      |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on<br>VDDA            | VCO freq = 192 MI<br>VCO freq = 432 MI   |                                            | 0.30<br>0.55 | -    |                                                              | mA   |

#### Table 34. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design, not tested in production.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results, not tested in production.

#### Table 35. PLLI2S (audio PLL) characteristics

| Symbol                  | Parameter                         | Conditions         | Min                 | Тур | Мах                 | Unit |

|-------------------------|-----------------------------------|--------------------|---------------------|-----|---------------------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    | -                  | -                   | -   | 216                 | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 | -                  | 192                 | -   | 432                 | MHz  |

| +                       | PLLI2S lock time                  | VCO freq = 192 MHz |                     | -   | 200                 |      |

| <sup>I</sup> LOCK       |                                   | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |

#### 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 42: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 26  | 2222 | noromotoro | aanatraint |

|-----------|------|------------|------------|

| Table 30. | 3366 | parameters | constraint |

1. Guaranteed by design, not tested in production.

#### **Equation 1**

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

#### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized}$ % = (250 × 126 × 100 × 5)/ ((2<sup>15</sup> - 1) × 240) = 2.0002%(peak)

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

Table 39. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 40. Flash memory endurance and data retention

1. Guaranteed by characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

## 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

## 6.3.16 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 14: General operating conditions*.

All I/Os are CMOS and TTL compliant.

|                  |                                          |                                                                 |                                         | _   |                                                                                                                                                                                                                                                                                                                                                                                           |      |

|------------------|------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbol           | Parameter                                | Conditions                                                      | Min                                     | Тур | Мах                                                                                                                                                                                                                                                                                                                                                                                       | Unit |

|                  | FT, TTa and NRST I/O                     |                                                                 |                                         |     | Max         0.35V <sub>DD</sub> -0.04 <sup>(1)</sup> 0.3V <sub>DD</sub> <sup>(2)</sup> 0.1V <sub>DD</sub> +0.1 <sup>(1)</sup> -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |      |

|                  | input low level voltage                  | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | -                                       | -   | 0.3V <sub>DD</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                         |      |

| $V_{\text{IL}}$  | BOOT0 I/O                                | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | -                                       | -   | $ \begin{array}{c} 0.35V_{DD}-0.04^{(1)} \\ 0.3V_{DD}^{(2)} \\ 0.1V_{DD}+0.1^{(1)} \\ - \\ - \\ - \\ - \\ - \\ - \\ - \\ - \\ 1 \\ - \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1 \\ 1$                                                                                                                                                                                                   | V    |

|                  | input low level voltage                  | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | -                                       | -   | 0.1000.0.1                                                                                                                                                                                                                                                                                                                                                                                |      |

|                  | FT, TTa and NRST I/O                     | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> |     |                                                                                                                                                                                                                                                                                                                                                                                           |      |

|                  | input high level voltage <sup>(5)</sup>  | 1.7 v≤vDD≤3.0 v                                                 | 0.7V <sub>DD</sub> <sup>(2)</sup>       | -   | -                                                                                                                                                                                                                                                                                                                                                                                         | v    |

| V <sub>IH</sub>  | ΒΟΟΤ0 Ι/Ο                                | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> | _   | 0.35V <sub>DD</sub> -0.04 <sup>(1)</sup><br>0.3V <sub>DD</sub> <sup>(2)</sup><br>0.1V <sub>DD</sub> +0.1 <sup>(1)</sup><br>-<br>-<br>-<br>-<br>-<br>-<br>-                                                                                                                                                                                                                                |      |

|                  | input high level voltage                 | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.17 00010.7                            | -   |                                                                                                                                                                                                                                                                                                                                                                                           |      |

|                  | FT, TTa and NRST I/O input hysteresis    | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> | -   | _                                                                                                                                                                                                                                                                                                                                                                                         |      |

| V <sub>HYS</sub> | ΒΟΟΤ0 Ι/Ο                                | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | 10%V <sub>DDIO</sub> <sup>(1)(3)</sup>  | -   | -                                                                                                                                                                                                                                                                                                                                                                                         | v    |

|                  | input hysteresis                         | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | 100 <sup>(1)</sup>                      | -   | -                                                                                                                                                                                                                                                                                                                                                                                         |      |

| 1                | I/O input leakage current <sup>(4)</sup> | $V_{SS} \leq V_{IN} \leq V_{DD}$                                | -                                       | -   | ±1                                                                                                                                                                                                                                                                                                                                                                                        |      |

| l <sub>lkg</sub> | I/O FT input leakage current (5)         | $V_{IN} = 5 V$                                                  | -                                       | -   | 0.3V <sub>DD</sub> <sup>(2)</sup><br>0.1V <sub>DD</sub> +0.1 <sup>(1)</sup><br>-<br>-<br>-<br>-<br>-<br>±1                                                                                                                                                                                                                                                                                | μA   |

| Table 46. I/O | static | characteristics |

|---------------|--------|-----------------|

|---------------|--------|-----------------|

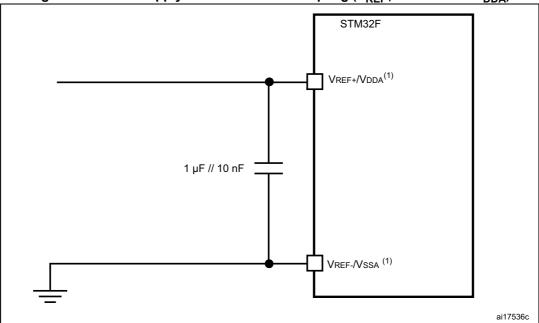

Figure 55. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

|                                  |                                       | Table              |     |                        |      |                                                                                                                                                  |

|----------------------------------|---------------------------------------|--------------------|-----|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                           | Parameter                             | Min                | Тур | Мах                    | Unit | Comments                                                                                                                                         |

| V <sub>DDA</sub>                 | Analog supply voltage                 | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | -                                                                                                                                                |

| V <sub>REF+</sub>                | Reference supply voltage              | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | V <sub>REF+</sub> ⊴V <sub>DDA</sub>                                                                                                              |

| V <sub>SSA</sub>                 | Ground                                | 0                  | -   | 0                      | V    | -                                                                                                                                                |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer<br>ON      | 5                  | -   | -                      | kΩ   | -                                                                                                                                                |

| R <sub>0</sub> <sup>(2)</sup>    | Impedance output with<br>buffer OFF   | -                  | -   | 15                     | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                          |

| C <sub>LOAD</sub> <sup>(2)</sup> | Capacitive load                       | -                  | -   | 50                     | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                                  |

| DAC_OUT<br>min <sup>(2)</sup>    | Lower DAC_OUT voltage with buffer ON  | 0.2                | -   | -                      | v    | It gives the maximum output excursion<br>of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to $(0xF1C)$ at V <sub>REF+</sub> = 3.6 V |

| DAC_OUT<br>max <sup>(2)</sup>    | Higher DAC_OUT voltage with buffer ON | -                  | -   | V <sub>DDA</sub> – 0.2 | V    | and (0x1C7) to (0xE38) at $V_{REF+} = 3.0 \text{ V}$<br>1.8 V                                                                                    |

## 6.3.21 DAC electrical characteristics

Table 68. DAC characteristics

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

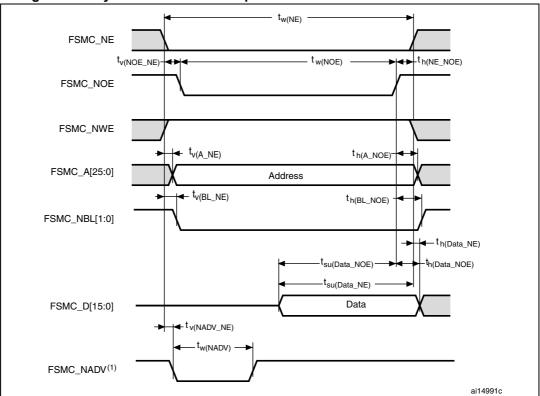

Figure 57. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

## Table 72. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                               | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                      | 2.5                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> - 1   | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                        | 4                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                        | 0.5                      | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> + 0.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                        | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                        | -                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                        | 2.5                      | ns   |

| t <sub>w(NADV</sub> )     | FSMC_NADV low time                      | -                        | T <sub>HCLK</sub> – 0.5  | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

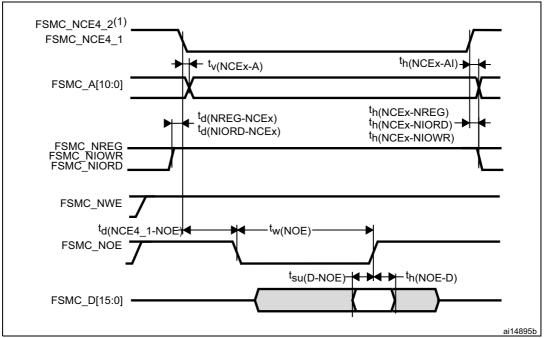

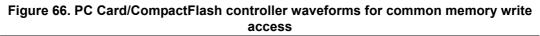

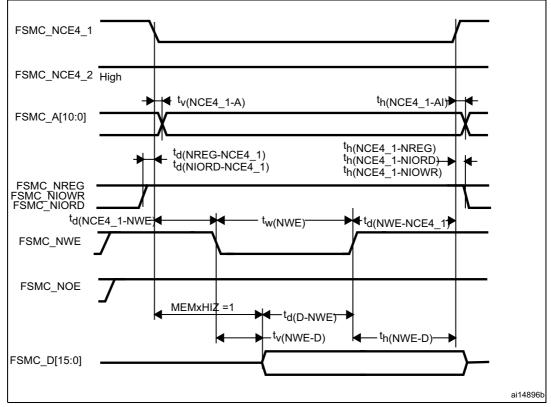

Figure 65. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

| Symbol                       | Parameter                                 | Min                      | Мах                      | Unit |

|------------------------------|-------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NIOWR)</sub>        | FSMC_NIOWR low width                      | 8T <sub>HCLK</sub> - 0.5 | -                        | ns   |

| t <sub>v(NIOWR-D)</sub>      | FSMC_NIOWR low to FSMC_D[15:0] valid      | -                        | 5T <sub>HCLK</sub> - 1   | ns   |

| t <sub>h(NIOWR-D)</sub>      | FSMC_NIOWR high to FSMC_D[15:0] invalid   | 8T <sub>HCLK</sub> - 3   | -                        | ns   |

| t <sub>d(NCE4_1-NIOWR)</sub> | FSMC_NCE4_1 low to FSMC_NIOWR valid       | -                        | 5T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NCEx-NIOWR)</sub>   | FSMC_NCEx high to FSMC_NIOWR invalid      | 5T <sub>HCLK</sub>       | -                        | ns   |

| t <sub>d(NIORD-NCEx)</sub>   | FSMC_NCEx low to FSMC_NIORD valid         | -                        | 5T <sub>HCLK</sub> + 1   | ns   |

| t <sub>h(NCEx-NIORD)</sub>   | FSMC_NCEx high to FSMC_NIORD) valid       | 5Т <sub>НСLК</sub> – 0.5 | -                        | ns   |

| t <sub>w(NIORD)</sub>        | FSMC_NIORD low width                      | 8T <sub>HCLK</sub> + 1   | -                        | ns   |

| t <sub>su(D-NIORD)</sub>     | FSMC_D[15:0] valid before FSMC_NIORD high | 9.5                      | -                        | ns   |

| t <sub>d(NIORD-D)</sub>      | FSMC_D[15:0] valid after FSMC_NIORD high  | 0                        | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

#### NAND controller waveforms and timings

*Figure 71* through *Figure 74* represent synchronous waveforms, together with *Table 82* and *Table 83* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FSMC\_WaitSetupTime = 0x03;

- COM.FSMC\_HoldSetupTime = 0x02;

- COM.FSMC\_HiZSetupTime = 0x01;

- ATT.FSMC SetupTime = 0x01;

- ATT.FSMC\_WaitSetupTime = 0x03;

- ATT.FSMC\_HoldSetupTime = 0x02;

- ATT.FSMC\_HiZSetupTime = 0x01;

- Bank = FSMC\_Bank\_NAND;

- MemoryDataWidth = FSMC\_MemoryDataWidth\_16b;

- ECC = FSMC\_ECC\_Enable;

- ECCPageSize = FSMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

# 8 Ordering information

#### Table 96. Ordering information scheme

| Example:                                                     | STM32 F | 205 R E | ΞΤ | 6 \ | / xxx |

|--------------------------------------------------------------|---------|---------|----|-----|-------|

| Device family                                                |         |         |    |     |       |

| STM32 = ARM-based 32-bit microcontroller                     |         |         |    |     |       |

| Product type                                                 |         |         |    |     |       |

| F = general-purpose                                          |         |         |    |     |       |

| Device subfamily                                             |         |         |    |     |       |

| 205 = STM32F20x, connectivity                                |         |         |    |     |       |

| 207= STM32F20x, connectivity, camera interface, Ethernet     |         |         |    |     |       |

| Pin count                                                    |         |         |    |     |       |

| R = 64 pins or 66 pins <sup>(1)</sup>                        |         |         |    |     |       |

| V = 100 pins                                                 |         |         |    |     |       |

| Z = 144 pins                                                 |         |         |    |     |       |

| I = 176 pins                                                 |         |         |    |     |       |

| Flash memory size                                            |         |         |    |     |       |

| B = 128 Kbytes of Flash memory                               |         |         |    |     |       |

| C = 256 Kbytes of Flash memory                               |         |         |    |     |       |

| E = 512 Kbytes of Flash memory                               |         |         |    |     |       |

| F = 768 Kbytes of Flash memory                               |         |         |    |     |       |

| G = 1024 Kbytes of Flash memory                              |         |         |    |     |       |

| Package                                                      |         |         |    |     |       |

| T = LQFP                                                     |         |         |    |     |       |

| H = UFBGA                                                    |         |         |    |     |       |

| Y = WLCSP                                                    |         |         |    |     |       |

| Temperature range                                            |         |         |    |     |       |

| 6 = Industrial temperature range, -40 to 85 °C.              |         |         |    |     |       |

| 7 = Industrial temperature range, $-40$ to $105 ^{\circ}C$ . |         |         |    |     |       |

| Software option                                              |         |         |    |     |       |

| Internal code or Blank                                       |         |         |    |     | ·     |

| Options                                                      |         |         |    |     |       |

xxx = programmed parts

TR = tape and reel

1. The 66 pins is available on WLCSP package only.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, contact your nearest ST sales office.

| I         |

|-----------|

| Date Revi |

|           |