##

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 82                                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 100-LQFP                                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207vct6tr                 |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Introduction

This datasheet provides the description of the STM32F205xx and STM32F207xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32 family, refer to *Section 2.1: Full compatibility throughout the family*.

The STM32F205xx and STM32F207xx datasheet should be read in conjunction with the STM32F20x/STM32F21x reference manual. They will be referred to as STM32F20x devices throughout the document.

For information on programming, erasing and protection of the internal Flash memory, refer to the STM32F20x/STM32F21x Flash programming manual (PM0059).

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the *www.arm.com* website.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART and UART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Camera interface (DCMI)

- ADC.

## **3.9** Flexible static memory controller (FSMC)

The FSMC is embedded in all STM32F20x devices. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- Maximum frequency (f<sub>HCLK</sub>) for external access is 60 MHz

#### LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

## **3.10** Nested vectored interrupt controller (NVIC)

The STM32F20x devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 81 maskable interrupt channels plus the 16 interrupt lines of the Cortex<sup>®</sup>-M3.

The NVIC main features are the following:

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

## 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                     | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| purpose              | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM9            | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| purpose              | TIM12           | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 30<br>MHz                 | 60<br>MHz             |

Table 5. Timer feature comparison

### 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

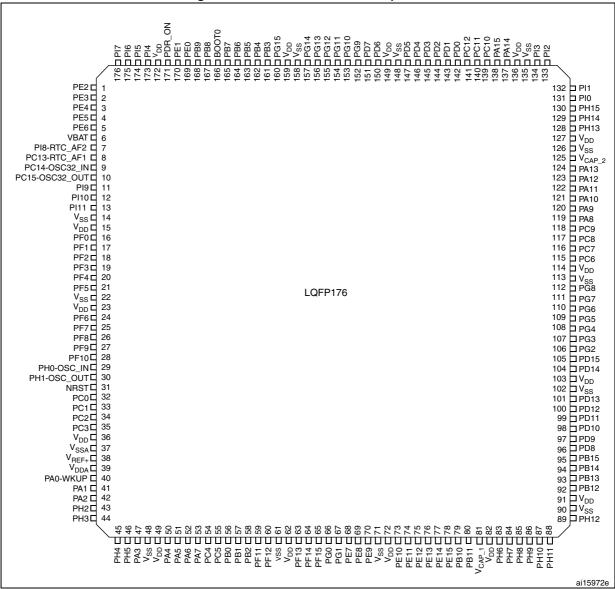

Figure 14. STM32F20x LQFP176 pinout

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          | -                                                    |          |               |      |                                                                                                                             |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                                         | Additional<br>functions |

| -      | -         | -       | 131     | 159     | C7       | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                                                                           | -                       |

| -      | -         | -       | 132     | 160     | B7       | PG15                                                 | I/O      | FT            | -    | USART6_CTS, DCMI_D13,<br>EVENTOUT                                                                                           | -                       |

| 55     | A4        | 89      | 133     | 161     | A10      | PB3<br>(JTDO/TRACESWO)                               | I/O      | FT            | -    | JTDO/ TRACESWO,<br>SPI3_SCK, I2S3_SCK,<br>TIM2_CH2, SPI1_SCK,<br>EVENTOUT                                                   | -                       |

| 56     | В4        | 90      | 134     | 162     | A9       | PB4                                                  | I/O      | FT            | -    | NJTRST, SPI3_MISO,<br>TIM3_CH1, SPI1_MISO,<br>EVENTOUT                                                                      | -                       |

| 57     | A5        | 91      | 135     | 163     | A6       | PB5                                                  | I/O      | FT            | -    | I2C1_SMBA, CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT, TIM3_CH2,<br>SPI1_MOSI, SPI3_MOSI,<br>DCMI_D10, I2S3_SD,<br>EVENTOUT | -                       |

| 58     | B5        | 92      | 136     | 164     | B6       | PB6                                                  | I/O      | FT            | -    | I2C1_SCL,, TIM4_CH1,<br>CAN2_TX,<br>DCMI_D5,USART1_TX,<br>EVENTOUT                                                          | -                       |

| 59     | A6        |         | 137     |         |          | PB7                                                  | I/O      | FT            | -    | I2C1_SDA, FSMC_NL <sup>(6)</sup> ,<br>DCMI_VSYNC,<br>USART1_RX, TIM4_CH2,<br>EVENTOUT                                       | -                       |

| 60     | B6        | 94      | 138     | 166     | D6       | BOOT0                                                | Ι        | В             | I    | -                                                                                                                           | V <sub>PP</sub>         |

| 61     | B7        | 95      | 139     | 167     | A5       | PB8                                                  | I/O      | FT            | -    | TIM4_CH3,SDIO_D4,<br>TIM10_CH1, DCMI_D6,<br>ETH_MII_TXD3, I2C1_SCL,<br>CAN1_RX, EVENTOUT                                    | -                       |

| 62     | A7        | 96      | 140     | 168     | B4       | PB9                                                  | I/O      | FT            | -    | SPI2_NSS, I2S2_WS,<br>TIM4_CH4, TIM11_CH1,<br>SDIO_D5, DCMI_D7,<br>I2C1_SDA, CAN1_TX,<br>EVENTOUT                           | -                       |

| -      | -         | 97      | 141     | 169     | A4       | PE0                                                  | I/O      | FT            | -    | TIM4_ETR, FSMC_NBL0,<br>DCMI_D2, EVENTOUT                                                                                   | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

| Symbol                               | Ratings                                                                 | Max   | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 120   |      |

| I <sub>VSS</sub>                     | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup> | 120   |      |

| I                                    | Output current sunk by any I/O and control pin                          | 25    |      |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                       | 25    | mA   |

| ı (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ±5    |      |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$      | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±25   |      |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 6.3.20: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

4. A positive injection is induced by  $V_{IN}$  >  $V_{DD}$  while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125         | °C   |

## 6.3 Operating conditions

### 6.3.1 General operating conditions

#### Table 14. General operating conditions

| Symbol             | Parameter                     | Conditions | Min | Max | Unit |

|--------------------|-------------------------------|------------|-----|-----|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency  | -          | 0   | 120 |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency | -          | 0   | 30  | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency | -          | 0   | 60  |      |

| Symbol          | Parameter      | Conditions                                                             |                       | Тур                    | Ма                     | Unit                    |      |

|-----------------|----------------|------------------------------------------------------------------------|-----------------------|------------------------|------------------------|-------------------------|------|

| Symbol          | Farameter      | Conditions                                                             | fhclk                 | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                |                                                                        | 120 MHz               | 61                     | 81                     | 93                      |      |

|                 |                |                                                                        | 90 MHz                | 48                     | 68                     | 80                      |      |

|                 |                |                                                                        | 60 MHz                | 33                     | 53                     | 65                      |      |

|                 |                | (2)                                                                    | 30 MHz                | 18                     | 38                     | 50                      |      |

|                 |                | External clock <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup> | 25 MHz                | 14                     | 34                     | 46                      |      |

|                 |                |                                                                        | 16 MHz <sup>(4)</sup> | 10                     | 30                     | 42                      |      |

|                 |                |                                                                        | 8 MHz                 | 6                      | 26                     | 38                      |      |

|                 |                |                                                                        | 4 MHz                 | 4                      | 24                     | 36                      |      |

|                 | Supply current |                                                                        | 2 MHz                 | 3                      | 23                     | 35                      |      |

| I <sub>DD</sub> | in Run mode    |                                                                        | 120 MHz               | 33                     | 54                     | 66                      | mA   |

|                 |                |                                                                        | 90 MHz                | 27                     | 47                     | 59                      |      |

|                 |                |                                                                        | 60 MHz                | 19                     | 39                     | 51                      |      |

|                 |                | 30 MHz 11                                                              | 31                    | 43                     |                        |                         |      |

|                 |                | External clock <sup>(2)</sup> , all peripherals disabled               | 25 MHz                | 8                      | 28                     | 41                      |      |

|                 |                |                                                                        | 16 MHz <sup>(4)</sup> | 6                      | 26                     | 38                      |      |

|                 |                |                                                                        | 8 MHz                 | 4                      | 24                     | 36                      |      |

|                 |                |                                                                        | 4 MHz                 | 3                      | 23                     | 35                      |      |

|                 |                |                                                                        | 2 MHz                 | 2                      | 23                     | 34                      |      |

#### Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{\text{HCLK}}$  > 25 MHz.

When the ADC is on (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

4. In this case HCLK = system clock/2.

| Symbol                                  | Parameter                                    | Conditions                                                          | Min                | Тур          | Мах  | Unit         |    |

|-----------------------------------------|----------------------------------------------|---------------------------------------------------------------------|--------------------|--------------|------|--------------|----|

| Jitter <sup>(3)</sup>                   |                                              | Cycle to cycle at                                                   | RMS                | -            | 90   | -            |    |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                        | peak<br>to<br>peak | -            | ±280 | -            | ps |

|                                         |                                              | Average frequency of<br>12.288 MHz<br>N=432, R=5<br>on 1000 samples |                    | -            | 90   | -            | ps |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 k<br>on 1000 samples                           | -                  | 400          | -    | ps           |    |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA |

#### Table 35. PLLI2S (audio PLL) characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design, not tested in production.

3. Value given with main PLL running.

4. Guaranteed by characterization results, not tested in production.

#### 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 42: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> -1 | -    |

| Table 26  | 2222 | noromotoro | aanatraint |

|-----------|------|------------|------------|

| Table 30. | 3366 | parameters | constraint |

1. Guaranteed by design, not tested in production.

#### **Equation 1**

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]$

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

#### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$md_{guantized}$ % = (250 × 126 × 100 × 5)/ ((2<sup>15</sup> - 1) × 240) = 2.0002%(peak)

DocID15818 Rev 15

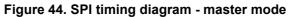

*Table 65* gives the list of Ethernet MAC signals for MII and *Figure 50* shows the corresponding timing diagram.

Figure 51. Ethernet MII timing diagram

| Symbol               | Rating                           | Min | Тур | Мах | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 7.5 | -   | -   | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -   | ns   |

| t <sub>su(DV)</sub>  | Data valid setup time            | 4   | -   | -   | ns   |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 0   | -   | -   | ns   |

| t <sub>su(ER)</sub>  | Error setup time                 | 3.5 | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  | 0   | -   | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | -   | 11  | 14  | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | -   | 11  | 14  | ns   |

#### CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

### 6.3.23 V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                           | Min | Тур | Max | Unit |

|---------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement               | -   | 2   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                          | –1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | C sampling time when reading the V <sub>BAT</sub> 5 |     | -   | μs  |      |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

#### 6.3.24 Embedded reference voltage

The parameters given in *Table 71* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                | Parameter                                                           | Conditions                        | Min  | Тур  | Мах  | Unit   |

|---------------------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub>                 | Internal reference voltage<br>spread over the temperature<br>range  | V <sub>DD</sub> = 3 V             | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                             | -                                 | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                        | -                                 | -    | 6    | 10   | μs     |

Table 71. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

### 6.3.25 FSMC characteristics

#### Asynchronous waveforms and timings

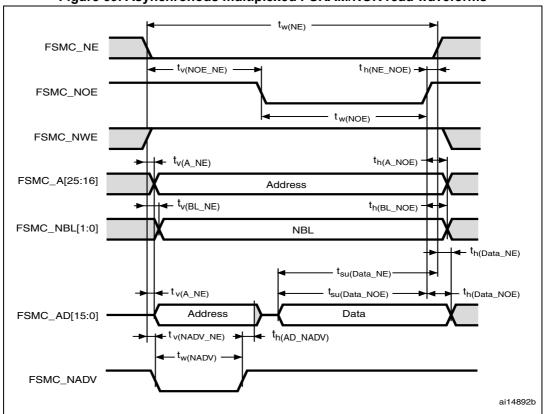

*Figure 57* through *Figure 60* represent asynchronous waveforms and *Table 72* through *Table 75* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- AddressSetupTime = 1

- AddressHoldTime = 1

- DataSetupTime = 1

- BusTurnAroundDuration = 0x0

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

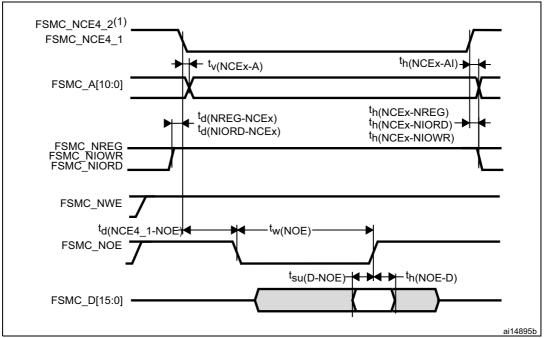

Figure 65. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

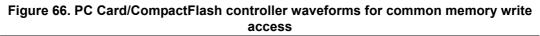

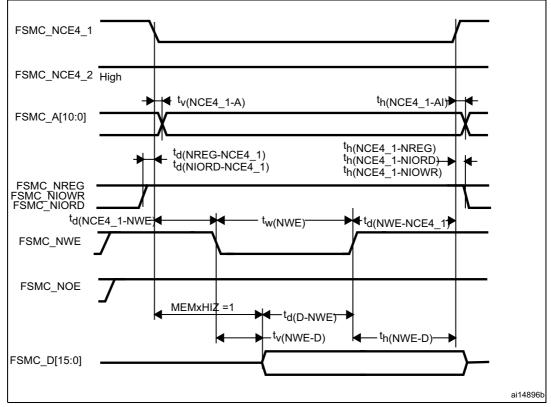

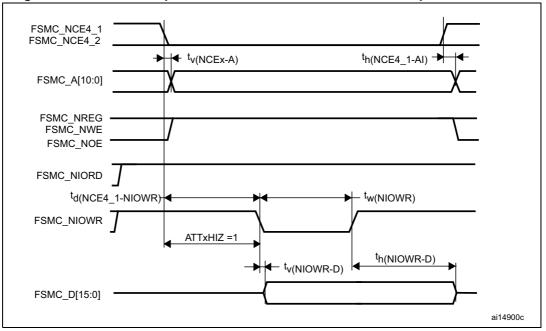

Figure 70. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 80. Switching characteristics for PC Card/CF read and write cycles in attribute/common space<sup>(1)(2)</sup>

| Symbol                    | Parameter                                    | Min                      | Max                    | Unit |

|---------------------------|----------------------------------------------|--------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                        | 0                      | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                        | -                      | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                        | 3.5                    | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> + 4    | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                        | 5T <sub>HCLK</sub>     | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> - 0.5 | 8T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 2.5 | -                      | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4                        | -                      | ns   |

| t <sub>h (N0E-D)</sub>    | FSMC_N0E high to FSMC_D[15:0] invalid        | 2                        | -                      | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 4 | ns   |

| t <sub>d(NWE_NCEx</sub> ) | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 1.5 | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5HCLK+ 1               | ns   |

| t <sub>v (NWE-D)</sub>    | FSMC_NWE low to FSMC_D[15:0] valid           | -                        | 0                      | ns   |

| t <sub>h (NWE-D)</sub>    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub>       | -                      | ns   |

| t <sub>d (D-NWE)</sub>    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub>      | _                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

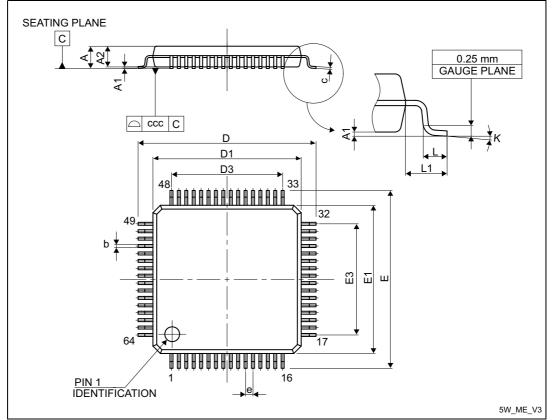

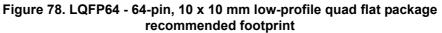

## 7.1 LQFP64 package information

Figure 77. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

## Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| A      | -     | -           | 1.600 | -      | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| E      | -     | 12.000      | -     | -      | 0.4724                | -      |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| CCC    | -     | -           | 0.080 | -      | -                     | 0.0031 |

## Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

## 8 Ordering information

#### Table 96. Ordering information scheme

| Example:                                                                                                                                                                                                                                               | STM32 F | 205 R E | Т | 6 V | xxx |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---|-----|-----|

| Device family                                                                                                                                                                                                                                          |         |         |   |     |     |

| STM32 = ARM-based 32-bit microcontroller                                                                                                                                                                                                               |         |         |   |     |     |

| Product type         F = general-purpose         Device subfamily         205 = STM32F20x, connectivity         207 = STM32F20x, connectivity, camera interface, Ethernet         Pin count         R = 64 pins or 66 pins <sup>(1)</sup> V = 100 pins |         |         |   |     |     |

| F = general-purpose                                                                                                                                                                                                                                    |         |         |   |     |     |

| Device subfamily                                                                                                                                                                                                                                       |         |         |   |     |     |

| 205 = STM32F20x, connectivity                                                                                                                                                                                                                          |         |         |   |     |     |

| 207= STM32F20x, connectivity, camera interface, Ethernet                                                                                                                                                                                               |         |         |   |     |     |

|                                                                                                                                                                                                                                                        |         |         |   |     |     |

| R = 64 pins or 66 pins <sup>(1)</sup>                                                                                                                                                                                                                  |         |         |   |     |     |

| V = 100 pins                                                                                                                                                                                                                                           |         |         |   |     |     |

| Z = 144 pins                                                                                                                                                                                                                                           |         |         |   |     |     |

| I = 176 pins                                                                                                                                                                                                                                           |         |         |   |     |     |

| Flash memory size                                                                                                                                                                                                                                      |         |         |   |     |     |

| B = 128 Kbytes of Flash memory                                                                                                                                                                                                                         |         |         |   |     |     |

| C = 256 Kbytes of Flash memory                                                                                                                                                                                                                         |         |         |   |     |     |

| E = 512 Kbytes of Flash memory                                                                                                                                                                                                                         |         |         |   |     |     |

| F = 768 Kbytes of Flash memory                                                                                                                                                                                                                         |         |         |   |     |     |

| G = 1024 Kbytes of Flash memory                                                                                                                                                                                                                        |         |         |   |     |     |

| Package                                                                                                                                                                                                                                                |         |         |   |     |     |

| T = LQFP                                                                                                                                                                                                                                               |         |         |   |     |     |

| H = UFBGA                                                                                                                                                                                                                                              |         |         |   |     |     |

| Y = WLCSP                                                                                                                                                                                                                                              |         |         |   |     |     |

| Temperature range                                                                                                                                                                                                                                      |         |         |   |     |     |

| 6 = Industrial temperature range, -40 to 85 °C.                                                                                                                                                                                                        |         |         |   | _   |     |

| 7 = Industrial temperature range, -40 to 105 °C.                                                                                                                                                                                                       |         |         |   |     |     |

| Software option                                                                                                                                                                                                                                        |         |         |   |     |     |

| Internal code or Blank                                                                                                                                                                                                                                 |         |         |   |     |     |

| Options                                                                                                                                                                                                                                                |         |         |   |     |     |

xxx = programmed parts

TR = tape and reel

1. The 66 pins is available on WLCSP package only.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, contact your nearest ST sales office.

| Date |

|------|

| Date |

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>22-Apr-2011 | Revision<br>6<br>(continued) | Changes           Changed t <sub>w(SCKH)</sub> to t <sub>w(SCLL)</sub> , t <sub>r(SCK)</sub> to t <sub>r(SCL)</sub> , and t <sub>r(SCK)</sub> to t <sub>r(SCL)</sub> in Table 52: I2C characteristics and in Figure 41: I2C bus AC waveforms and measurement circuit.           Added Table 57: USB OTG FS DC electrical characteristics and updated Table 58: USB OTG FS electrical characteristics.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.           Updated Table 71: Embedded internal reference voltage.           Modified FSMC_NOE waveform in Figure 57: Asynchronous non-<br>multiplexed SRAM/PSRAM/NOR read waveforms. Shifted end of<br>FSMC_NEx/NADV/addresses/NWE/NOE/NWAIT of a half FSMC_CLK           Period, changed t <sub>a</sub> (CLKI-NEH), and t <sub>a</sub> (CLKI-NEH), t <sub>a</sub> (CLKI-NWEH), and updated data latency from 1 to 0 in Figure 61: Synchronous<br>multiplexed NOR/PSRAM read timings, Figure 63: Synchronous mon-<br>multiplexed NOR/PSRAM read timings, and Figure 64: Synchronous<br>non-multiplexed PSRAM write timings,           Changed t <sub>a</sub> (CLKI-NEH), t <sub>a</sub> (CLKI-NEH), to t <sub>a</sub> (CLKI-NEH), and<br>modified t <sub>w</sub> (CLK) minimum value in Table 76, Table 77, Table 78, and<br>Table 79.           Updated note 2 in Table 72, Table 73, Table 74, Table 75, Table 76,<br>Table 77, Table 78, and Table 79.           Modified FSMC_NCEx signal in Figure 71: NAND controller wavefor |

Table 97. Document revision history (continued)